Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 50MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 28                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-HVQFN (5x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1114jhi33-303e |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 32-bit ARM Cortex-M0 microcontroller

| Type number      | Package |                                                                                                  |           |  |  |  |  |  |

|------------------|---------|--------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

|                  | Name    | Description                                                                                      | Version   |  |  |  |  |  |

| LPC1115JBD48/303 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body 7 $\times$ 7 $\times$ 1.4 mm       | SOT313-2  |  |  |  |  |  |

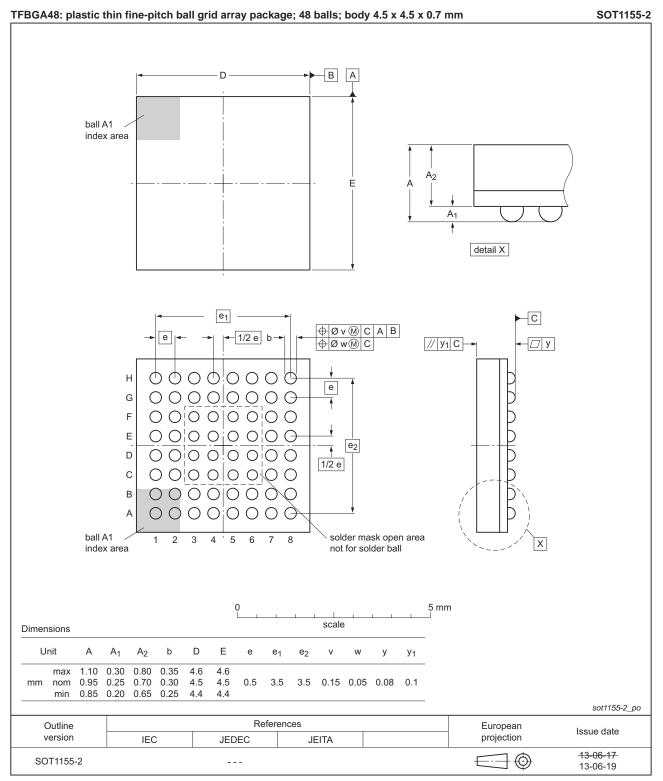

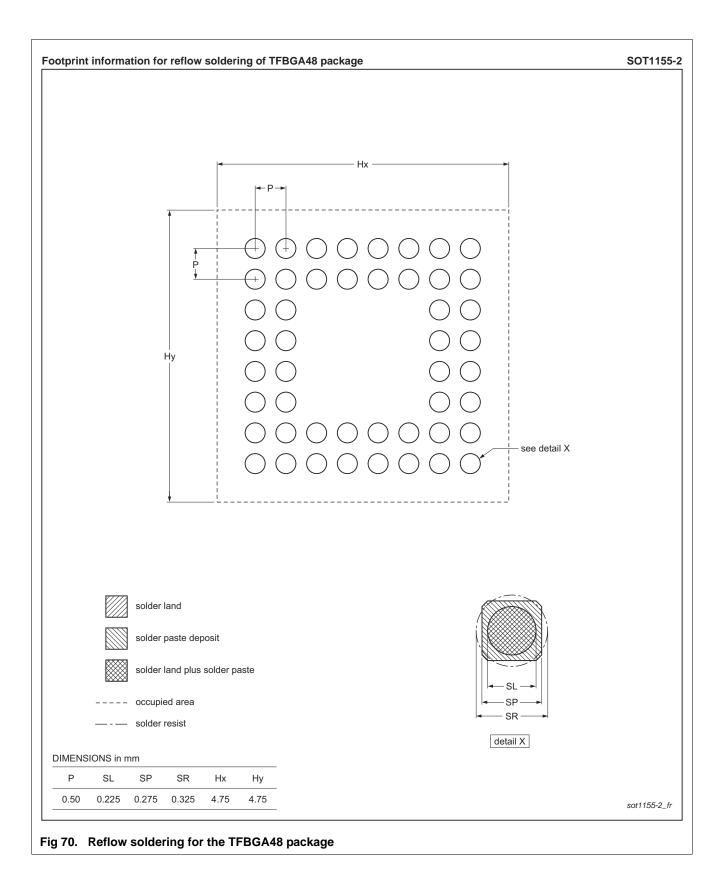

| LPC1115FET48/303 | TFBGA48 | plastic thin fine-pitch ball grid array package; 48 balls; body 4.5 $\times$ 4.5 $\times$ 0.7 mm | SOT1155-2 |  |  |  |  |  |

| LPC1115JET48/303 | TFBGA48 | plastic thin fine-pitch ball grid array package; 48 balls; body 4.5 $\times$ 4.5 $\times$ 0.7 mm | SOT1155-2 |  |  |  |  |  |

#### Table 1. Ordering information ... continued

### 4.1 Ordering options

#### Table 2. Ordering options

| Type number      | Series    | Flash | Total<br>SRAM | Power<br>profiles | UART | l <sup>2</sup> C/<br>Fast+ | SPI | ADC<br>channel | GPIO | Package | Temp <u><sup>[1]</sup></u> |

|------------------|-----------|-------|---------------|-------------------|------|----------------------------|-----|----------------|------|---------|----------------------------|

| LPC1110          |           |       |               |                   |      |                            |     |                |      |         |                            |

| LPC1110FD20      | LPC1100L  | 4 kB  | 1 kB          | 100               | 1    | 1                          | 1   | 5              | 16   | SO20    | F                          |

| LPC1111          | LFCIIUUL  | 4 KD  | IKD           | yes               | I    | I                          | I   | 5              | 10   | 3020    | Г                          |

|                  | LPC1100L  | 0.1-D |               |                   | 4    | 4                          | 4   | 5              | 40   | TSSOP20 | F                          |

| LPC1111FDH20/002 |           | 8 kB  | 2 kB          | yes               | 1    | 1                          | 1   |                | 16   |         |                            |

| LPC1111FHN33/101 | LPC1100   | 8 kB  | 2 kB          | no                | 1    | 1                          | 1   | 8              | 28   |         | F                          |

| LPC1111FHN33/102 | LPC1100L  | 8 kB  | 2 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 |                            |

| LPC1111FHN33/103 | LPC1100XL | 8 kB  | 2 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 |                            |

| LPC1111JHN33/103 | LPC1100XL | 8 kB  | 2 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

| LPC1111FHN33/201 | LPC1100   | 8 kB  | 4 kB          | no                | 1    | 1                          | 1   | 8              | 28   | HVQFN33 |                            |

| LPC1111FHN33/202 | LPC1100L  | 8 kB  | 4 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1111FHN33/203 | LPC1100XL | 8 kB  | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | F                          |

| LPC1111JHN33/203 | LPC1100XL | 8 kB  | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

| LPC1112          |           |       |               |                   |      |                            |     |                |      |         |                            |

| LPC1112FD20/102  | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 5              | 16   | SO20    | F                          |

| LPC1112FDH20/102 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | -                          | 1   | 5              | 14   | TSSOP20 | F                          |

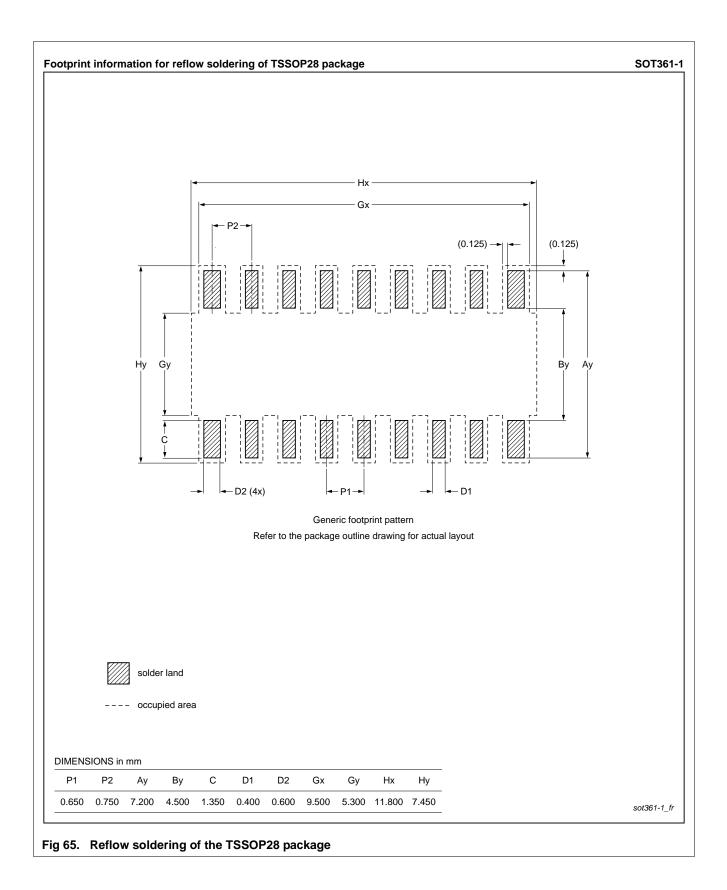

| LPC1112FDH28/102 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 6              | 22   | TSSOP28 | F                          |

| LPC1112FHN24/202 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 6              | 19   | HVQFN24 | F                          |

| LPC1112FHN33/101 | LPC1100   | 16 kB | 2 kB          | no                | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHN33/102 | LPC1100L  | 16 kB | 2 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHN33/103 | LPC1100XL | 16 kB | 2 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | F                          |

| LPC1112JHN33/103 | LPC1100XL | 16 kB | 2 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

| LPC1112FHN33/201 | LPC1100   | 16 kB | 4 kB          | no                | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHN33/202 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHN33/203 | LPC1100XL | 16 kB | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | F                          |

| LPC1112JHN33/203 | LPC1100XL | 16 kB | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

| LPC1112FHI33/102 | LPC1100L  | 16 kB | 2 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHI33/202 | LPC1100L  | 16 kB | 4 kB          | yes               | 1    | 1                          | 1   | 8              | 28   | HVQFN33 | F                          |

| LPC1112FHI33/203 | LPC1100XL | 16 kB | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | F                          |

| LPC1112JHI33/203 | LPC1100XL | 16 kB | 4 kB          | yes               | 1    | 1                          | 2   | 8              | 28   | HVQFN33 | J                          |

### **NXP Semiconductors**

## LPC1110/11/12/13/14/15

32-bit ARM Cortex-M0 microcontroller

LPC111X

17 of 127

32-bit ARM Cortex-M0 microcontroller

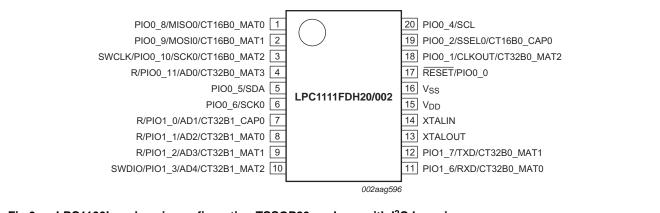

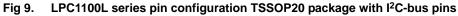

### 6.2 Pin description

## Table 4. LPC1100L series: LPC1110/11/12 pin description table (SO20 and TSSOP20 package with I<sup>2</sup>C-bus pins)

| Cumb al                       |                                              |     | 04                         | T    | Derit                 | Description                                                                                                                                                                                                                                        |

|-------------------------------|----------------------------------------------|-----|----------------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                        | Pin SO20/<br>TSSOP20                         |     | Start<br>logic<br>input    | туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                        |

| PIO0_0 to PIO0_11             |                                              |     |                            | I/O  |                       | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pins depends on the function selected through the IOCONFIG register block.                                       |

| RESET/PIO0_0                  | 17                                           | [2] | yes                        | I    | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |

|                               |                                              |     |                            |      |                       | In deep power-down mode, this pin must be pulled HIGH externally.<br>The RESET pin can be left unconnected or be used as a GPIO pin<br>if an external RESET function is not needed and Deep power-down<br>mode is not used.                        |

|                               |                                              |     |                            | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 18                                           | [3] | yes                        | I/O  | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                     |

|                               |                                              |     |                            | 0    | -                     | CLKOUT — Clockout pin.                                                                                                                                                                                                                             |

|                               |                                              |     |                            | 0    | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                   |

| PIO0_2/SSEL0/                 | 19                                           | [3] | yes                        | I/O  | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_CAP0                   |                                              |     |                            | I/O  | -                     | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                     |

|                               |                                              |     |                            | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                  |

| PIO0_4/SCL                    | 20                                           | [4] | yes                        | I/O  | I; IA                 | PIO0_4 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                    |

|                               |                                              |     |                            | I/O  | -                     | <b>SCL</b> — I <sup>2</sup> C-bus, open-drain clock input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                         |

| PIO0_5/SDA                    | 5                                            | [4] | yes                        | I/O  | I; IA                 | PIO0_5 — General purpose digital input/output pin (open-drain).                                                                                                                                                                                    |

|                               |                                              |     |                            | I/O  | -                     | <b>SDA</b> — I <sup>2</sup> C-bus, open-drain data input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                          |

| PIO0_6/SCK0                   | 6                                            | [3] | yes                        | I/O  | I; PU                 | PIO0_6 — General purpose digital input/output pin.                                                                                                                                                                                                 |

|                               |                                              |     |                            | I/O  | -                     | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                      |

| PIO0_8/MISO0/                 | 1                                            | [3] | yes                        | I/O  | I; PU                 | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT0                   |                                              |     |                            | I/O  | -                     | MISO0 — Master In Slave Out for SPI0.                                                                                                                                                                                                              |

|                               |                                              |     |                            | 0    | -                     | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                                   |

| PIO0_9/MOSI0/                 | 2                                            | [3] | yes                        | I/O  | I; PU                 | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                                 |

| CT16B0_MAT1                   |                                              |     |                            | I/O  | -                     | MOSI0 — Master Out Slave In for SPI0.                                                                                                                                                                                                              |

|                               |                                              |     |                            | 0    | -                     | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                                   |

| SWCLK/PIO0_10/                | 3 [3] yes I I; PU SWCLK — Serial wire clock. |     | SWCLK — Serial wire clock. |      |                       |                                                                                                                                                                                                                                                    |

| SCK0/<br>CT16B0_MAT2          |                                              |     |                            | I/O  | -                     | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                                |

|                               |                                              |     |                            | I/O  | -                     | SCK0 — Serial clock for SPI0.                                                                                                                                                                                                                      |

|                               |                                              |     |                            | 0    | -                     | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                                   |

LPC111X

© NXP Semiconductors N.V. 2014. All rights reserved.

### 32-bit ARM Cortex-M0 microcontroller

| Symbol           | Pin TSSOP20   | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                 |

|------------------|---------------|-------------------------|------|-----------------------|-------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub> | 5             | -                       | I    | -                     | 3.3 V supply voltage to the ADC. Also used as the ADC reference voltage.                                    |

| XTALIN           | 14 <u>[5]</u> | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits. Input voltage must not exceed 1.8 V. |

| XTALOUT          | 13 <u>[5]</u> | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                       |

| V <sub>SS</sub>  | 16            | -                       | I    | -                     | Ground.                                                                                                     |

| V <sub>SSA</sub> | 6             | -                       | I    | -                     | Analog ground.                                                                                              |

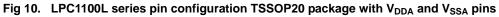

#### Table 5. LPC1100L series: LPC1112 pin description table (TSSOP20 with VDDA and VSSA pins) ... continued

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level ); IA = inactive, no pull-up/down enabled.

[2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

[4] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 51).

[5] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

| Symbol                        | HVQFN<br>pin | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                        |  |  |

|-------------------------------|--------------|-------------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RESET/PIO0_0                  | 1[2]         | yes                     | I    | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |  |  |

|                               |              |                         |      |                       | In deep power- <u>down mode</u> , this pin must be pulled HIGH<br>externally. The RESET pin can be left unconnected or be used<br>as a GPIO pin if an external RESET function is not needed and<br>Deep power-down mode is not used.               |  |  |

|                               |              |                         | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 n glitch filter.                                                                                                                                                                  |  |  |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2 | 2 <u>[3]</u> | yes                     | I/O  | I; PU                 | <b>PIO0_1</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                                                                                                     |  |  |

|                               |              |                         | 0    | -                     | CLKOUT — Clockout pin.                                                                                                                                                                                                                             |  |  |

|                               |              |                         | 0    | -                     | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                                                   |  |  |

| PIO0_2/SSEL0/                 | 7 <u>[3]</u> | yes                     | I/O  | I; PU                 | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                                                 |  |  |

| CT16B0_CAP0                   |              |                         | I/O  | -                     | SSEL0 — Slave Select for SPI0.                                                                                                                                                                                                                     |  |  |

|                               |              |                         | I    | -                     | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                                                  |  |  |

| PIO0_4/SCL                    | 8[4]         | yes                     | I/O  | I; IA                 | <b>PIO0_4</b> — General purpose digital input/output pin (open-drain).                                                                                                                                                                             |  |  |

|                               |              |                         | I/O  | -                     | <b>SCL</b> — I <sup>2</sup> C-bus, open-drain clock input/output. High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                                                         |  |  |

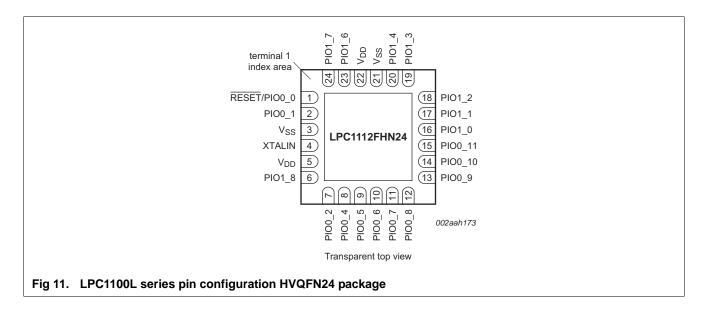

#### Table 6. LPC1100L series: LPC1112 (HVQFN24 package)

Product data sheet

© NXP Semiconductors N.V. 2014. All rights reserved.

#### 32-bit ARM Cortex-M0 microcontroller

| Symbol           | Pin TSSOP28/<br>DIP28 |     | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                    |

|------------------|-----------------------|-----|-------------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------|

| PIO1_5/RTS/      | 14                    | [3] | no                      | I/O  | I; PU                 | PIO1_5 — General purpose digital input/output pin.                                                             |

| CT32B0_CAP0      |                       |     |                         | 0    | -                     | <b>RTS</b> — Request To Send output for UART.                                                                  |

|                  |                       |     |                         | I    | -                     | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                              |

| PIO1_6/RXD/      | 15                    | [3] | no                      | I/O  | I; PU                 | PIO1_6 — General purpose digital input/output pin.                                                             |

| CT32B0_MAT0      |                       |     |                         | I    | -                     | RXD — Receiver input for UART.                                                                                 |

|                  |                       |     |                         | 0    | -                     | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                               |

| PIO1_7/TXD/      |                       |     | no                      | I/O  | I; PU                 | PIO1_7 — General purpose digital input/output pin.                                                             |

| CT32B0_MAT1      |                       |     |                         | 0    | -                     | <b>TXD</b> — Transmitter output for UART.                                                                      |

|                  |                       |     |                         | 0    | -                     | CT32B0_MAT1 — Match output 1 for 32-bit timer 0.                                                               |

| PIO1_8/          | 17                    | [3] | no                      | I/O  | I; PU                 | PIO1_8 — General purpose digital input/output pin.                                                             |

| CT16B1_CAP0      |                       |     |                         | I    | -                     | CT16B1_CAP0 — Capture input 0 for 16-bit timer 1.                                                              |

| PIO1_9/          | 18                    | [3] | no                      | I/O  | I; PU                 | PIO1_9 — General purpose digital input/output pin.                                                             |

| CT16B1_MAT0      |                       |     |                         | 0    | -                     | CT16B1_MAT0 — Match output 0 for 16-bit timer 1.                                                               |

| V <sub>DD</sub>  | 21                    |     | -                       |      | -                     | 3.3 V supply voltage to the internal regulator and the external rail.                                          |

| V <sub>DDA</sub> | 7                     |     | -                       | -    | -                     | 3.3 V supply voltage to the ADC. Also used as the ADC reference voltage.                                       |

| XTALIN           | 20                    | [6] | -                       | I    | -                     | Input to the oscillator circuit and internal clock generator circuits.<br>Input voltage must not exceed 1.8 V. |

| XTALOUT          | 19                    | [6] | -                       | 0    | -                     | Output from the oscillator amplifier.                                                                          |

| V <sub>SS</sub>  | 22                    |     | -                       |      | -                     | Ground.                                                                                                        |

| V <sub>SSA</sub> | 8                     |     | -                       | -    | -                     | Analog ground.                                                                                                 |

#### Table 7. LPC1100L series: LPC1112/14 pin description table (TSSOP28 and DIP28 packages) ... continued

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level ); IA = inactive, no pull-up/down enabled.

[2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode. Use the WAKEUP pin to reset the chip and wake up from Deep power-down mode. An external pull-up resistor is required on this pin for the Deep power-down mode. See Figure 52 for the reset pad configuration.

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 51).

- [4] I<sup>2</sup>C-bus pads compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode and I<sup>2</sup>C Fast-mode Plus. The pin requires an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines. Open-drain configuration applies to all functions on this pin.

- [5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 51).

- [6] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                                | LQFP48        | TFBGA48           | Start<br>logic<br>input | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------|---------------|-------------------|-------------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO1_4/AD5/<br>CT32B1_MAT3/<br>WAKEUP | 40 <u>5</u>   | A6[5]             | no                      | I/O  | I; PU                 | <b>PIO1_4</b> — General purpose digital input/output pin with 10 ns glitch filter. In Deep power-down mode, this pin serves as the Deep power-down mode wake-up pin with 20 ns glitch filter. Pull this pin HIGH externally before entering Deep power-down mode. Pull this pin LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |

|                                       |               |                   |                         | I    | -                     | AD5 — A/D converter, input 5.                                                                                                                                                                                                                                                                                                                                            |

|                                       |               |                   |                         | 0    | -                     | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| PIO1_5/RTS/                           | 45 <u>[3]</u> | A3 <u>[3]</u>     | no                      | I/O  | I; PU                 | PIO1_5 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

| CT32B0_CAP0                           |               |                   |                         | 0    | -                     | <b>RTS</b> — Request To Send output for UART.                                                                                                                                                                                                                                                                                                                            |

|                                       |               |                   |                         | I    | -                     | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                        |

| PIO1_6/RXD/                           | 46 <u>[3]</u> | B3 <u>[3]</u>     | no                      | I/O  | I; PU                 | PIO1_6 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

| CT32B0_MAT0                           |               |                   |                         | I    | -                     | <b>RXD</b> — Receiver input for UART.                                                                                                                                                                                                                                                                                                                                    |

|                                       |               |                   |                         | 0    | -                     | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |

| PIO1_7/TXD/                           | 47 <u>[3]</u> | B2 <sup>[3]</sup> | no                      | I/O  | I; PU                 | PIO1_7 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

| CT32B0_MAT1                           |               |                   |                         | 0    | -                     | TXD — Transmitter output for UART.                                                                                                                                                                                                                                                                                                                                       |

|                                       |               |                   |                         | 0    | -                     | CT32B0_MAT1 — Match output 1 for 32-bit timer 0.                                                                                                                                                                                                                                                                                                                         |

| PIO1_8/                               | 9 <u>[3]</u>  | F2 <sup>[3]</sup> | no                      | I/O  | I; PU                 | PIO1_8 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

| CT16B1_CAP0                           |               |                   |                         | I    | -                     | CT16B1_CAP0 — Capture input 0 for 16-bit timer 1.                                                                                                                                                                                                                                                                                                                        |

| PIO1_9/                               | 17 <u>[3]</u> | G4 <u>[3]</u>     | no                      | I/O  | I; PU                 | PIO1_9 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

| CT16B1_MAT0/                          |               |                   |                         | 0    | -                     | CT16B1_MAT0 — Match output 0 for 16-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

| MOSI1                                 |               |                   |                         | I/O  | -                     | MOSI1 — Master Out Slave In for SPI1.                                                                                                                                                                                                                                                                                                                                    |

| PIO1_10/AD6/                          | 30 <u>[5]</u> | E8[5]             | no                      | I/O  | I; PU                 | PIO1_10 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |

| CT16B1_MAT1/                          |               |                   |                         | I    | -                     | AD6 — A/D converter, input 6.                                                                                                                                                                                                                                                                                                                                            |

| MISO1                                 |               |                   |                         | 0    | -                     | CT16B1_MAT1 — Match output 1 for 16-bit timer 1.                                                                                                                                                                                                                                                                                                                         |

|                                       |               |                   |                         | I/O  | -                     | MISO1 — Master In Slave Out for SPI1.                                                                                                                                                                                                                                                                                                                                    |

| PIO1_11/AD7/                          | 42 <u>[5]</u> | A5 <u>[5]</u>     | no                      | I/O  | I; PU                 | PIO1_11 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                      |

| CT32B1_CAP1                           |               |                   |                         | I    | -                     | AD7 — A/D converter, input 7.                                                                                                                                                                                                                                                                                                                                            |

|                                       |               |                   |                         | I    | -                     | CT32B1_CAP1 — Capture input 1 for 32-bit timer 1.                                                                                                                                                                                                                                                                                                                        |

| PIO2_0 to PIO2_11                     |               |                   |                         | I/O  |                       | <b>Port 2</b> — Port 2 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 2 pins depends on the function selected through the IOCONFIG register block.                                                                                                                                                             |

| PIO2_0/DTR/SSEL1                      | 2 <u>[3]</u>  | B1 <sup>[3]</sup> | no                      | I/O  | I; PU                 | PIO2_0 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |               |                   |                         | 0    | -                     | <b>DTR</b> — Data Terminal Ready output for UART.                                                                                                                                                                                                                                                                                                                        |

|                                       |               |                   |                         | I/O  | -                     | SSEL1 — Slave Select for SPI1.                                                                                                                                                                                                                                                                                                                                           |

| PIO2_1/DSR/SCK1                       | 13 <u>[3]</u> | H1 <sup>[3]</sup> | no                      | I/O  | I; PU                 | PIO2_1 — General purpose digital input/output pin.                                                                                                                                                                                                                                                                                                                       |

|                                       |               |                   |                         | I    | -                     | DSR — Data Set Ready input for UART.                                                                                                                                                                                                                                                                                                                                     |

|                                       |               |                   |                         | I/O  | -                     | SCK1 — Serial clock for SPI1.                                                                                                                                                                                                                                                                                                                                            |

#### Table 10. LPC1100XL series: LPC1113/14/15 pin description table (LQFP48 and TFBGA48 package) ... continued

#### 32-bit ARM Cortex-M0 microcontroller

- On the LPC1100L and LPC1100XL series, all GPIO pins (except PIO0\_4 and PIO0\_5) are pulled up to 3.3 V (V<sub>DD</sub> = 3.3 V) if their pull-up resistor is enabled in the IOCONFIG block.

- Programmable open-drain mode for series LPC1100L and LPC1100XL.

### 7.8 UART

The LPC1110/11/12/13/14/15 contain one UART.

Support for RS-485/9-bit mode allows both software address detection and automatic address detection using 9-bit mode.

The UART includes a fractional baud rate generator. Standard baud rates such as 115200 Bd can be achieved with any crystal frequency above 2 MHz.

#### 7.8.1 Features

- Maximum UART data bit rate of 3.125 MBit/s.

- 16 Byte Receive and Transmit FIFOs.

- Register locations conform to 16C550 industry standard.

- Receiver FIFO trigger points at 1 B, 4 B, 8 B, and 14 B.

- Built-in fractional baud rate generator covering wide range of baud rates without a need for external crystals of particular values.

- FIFO control mechanism that enables software flow control implementation.

- Support for RS-485/9-bit mode.

- Support for modem control.

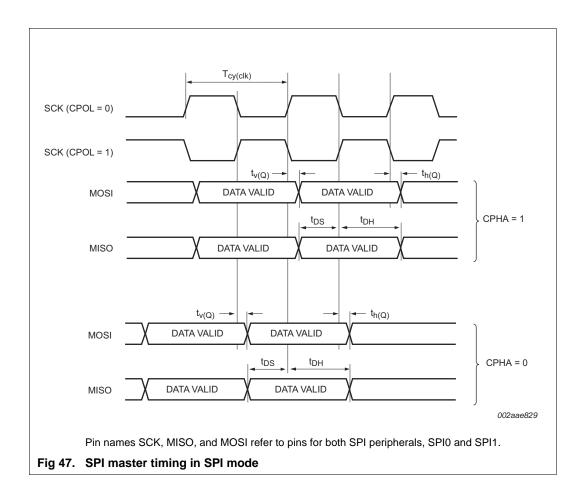

### 7.9 SPI serial I/O controller

The LPC1100 and LPC1100L series contain two SPI controllers on the LQFP48 package and one SPI controller on the HVQFN33/TSSOP28/DIP28/TSSOP20/SO20 packages (SPI0).

The LPC1100XL series contain two SPI controllers.

Both SPI controllers support SSP features.

The SPI controller is capable of operation on a SSP, 4-wire SSI, or Microwire bus. It can interact with multiple masters and slaves on the bus. Only a single master and a single slave can communicate on the bus during a given data transfer. The SPI supports full duplex transfers, with frames of 4 bits to 16 bits of data flowing from the master to the slave and from the slave to the master. In practice, often only one of these data flows carries meaningful data.

### 7.9.1 Features

- Maximum SPI speed of 25 Mbit/s (master) or 4.17 Mbit/s (slave) (in SSP mode)

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses

- Synchronous serial communication

#### 32-bit ARM Cortex-M0 microcontroller

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the Internal RC oscillator (IRC), the Watchdog oscillator, or the main clock. This gives a wide range of potential timing choices of Watchdog operation under different power reduction conditions. It also provides the ability to run the WDT from an entirely internal source that is not dependent on an external crystal and its associated components and wiring for increased reliability.

### 7.15 Windowed WatchDog Timer (LPC1100L and LPC1100XL series)

**Remark:** The windowed watchdog timer is available on the LPC1100L and LPC1100XL series only.

The purpose of the watchdog is to reset the controller if software fails to periodically service it within a programmable time window.

### 7.15.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the IRC or the dedicated watchdog oscillator (WDO). This gives a wide range of potential timing choices of watchdog operation under different power conditions.

### 7.16 Clocking and power control

### 7.16.1 Crystal oscillators

The LPC1110/11/12/13/14/15 include three independent oscillators. These are the system oscillator, the Internal RC oscillator (IRC), and the Watchdog oscillator. Each oscillator can be used for more than one purpose as required in a particular application.

#### 32-bit ARM Cortex-M0 microcontroller

- Default mode corresponding to power configuration after reset.

- CPU performance mode corresponding to optimized processing capability.

- Efficiency mode corresponding to optimized balance of current consumption and CPU performance.

- Low-current mode corresponding to lowest power consumption.

In addition, the power profile includes routines to select the optimal PLL settings for a given system clock and PLL input clock.

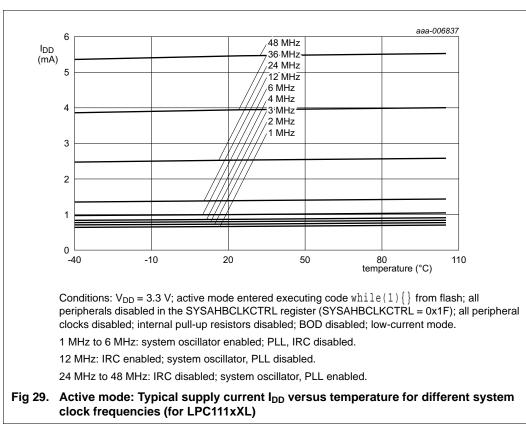

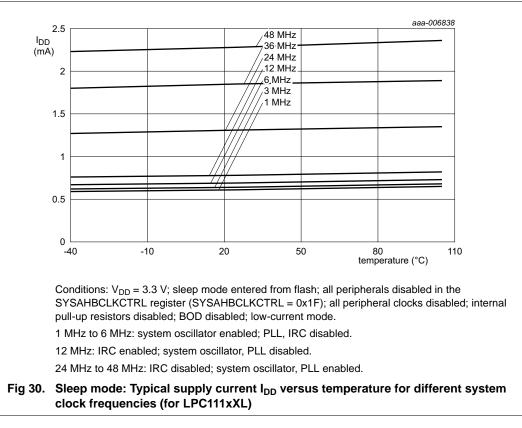

#### 7.16.5.2 Sleep mode

When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence but re-enabling the clock to the ARM core.

In Sleep mode, execution of instructions is suspended until either a reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and may generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

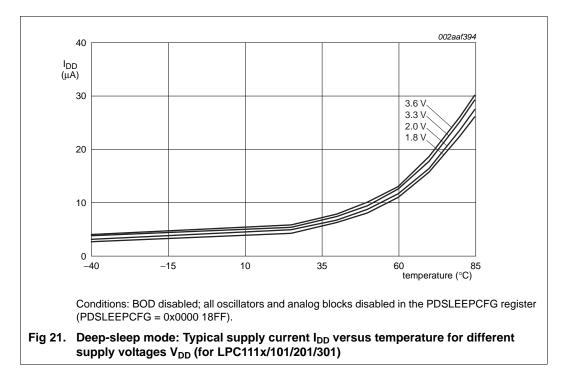

#### 7.16.5.3 Deep-sleep mode

In Deep-sleep mode, the chip is in Sleep mode, and in addition all analog blocks are shut down. As an exception, the user has the option to keep the watchdog oscillator and the BOD circuit running for self-timed wake-up and BOD protection. Deep-sleep mode allows for additional power savings.

Up to 13 pins total serve as external wake-up pins to the start logic to wake up the chip from Deep-sleep mode.

Unless the watchdog oscillator is selected to run in Deep-sleep mode, the clock source should be switched to IRC before entering Deep-sleep mode, because the IRC can be switched on and off glitch-free.

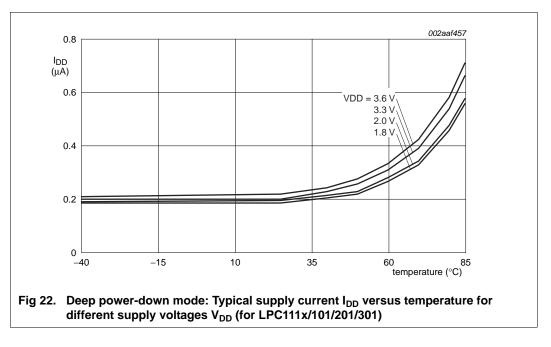

#### 7.16.5.4 Deep power-down mode

In Deep power-down mode, power is shut off to the entire chip with the exception of the WAKEUP pin. The LPC1110/11/12/13/14/15 can wake up from Deep power-down mode via the WAKEUP pin.

A LOW-going pulse as short as 50 ns wakes up the part from Deep power-down mode.

When entering Deep power-down mode, an external pull-up resistor is required on the WAKEUP pin to hold it HIGH. The RESET pin must also be held HIGH to prevent it from floating while in Deep power-down mode.

### 7.17 System control

#### 7.17.1 Start logic

The start logic connects external pins to corresponding interrupts in the NVIC. Each pin shown in <u>Table 8</u> to <u>Table 9</u> as input to the start logic has an individual interrupt in the NVIC interrupt vector table. The start logic pins can serve as external interrupt pins when the chip is running. In addition, an input signal on the start logic pins can wake up the chip from Deep-sleep mode when all clocks are shut down.

#### 32-bit ARM Cortex-M0 microcontroller

### 9. Thermal characteristics

The average chip junction temperature,  $T_{j}\,(^{\circ}C),$  can be calculated using the following equation:

$$T_j = T_{amb} + (P_D \times R_{th(j-a)}) \tag{1}$$

- T<sub>amb</sub> = ambient temperature (°C),

- R<sub>th(j-a)</sub> = the package junction-to-ambient thermal resistance (°C/W)

- P<sub>D</sub> = sum of internal and I/O power dissipation

The internal power dissipation is the product of  $I_{DD}$  and  $V_{DD}$ . The I/O power dissipation of the I/O pins is often small and many times can be negligible. However it can be significant in some applications.

#### Table 13. Thermal characteristics

| Symbol              | Parameter        | Conditions | Min | Тур | Max | Unit |

|---------------------|------------------|------------|-----|-----|-----|------|

| T <sub>j(max)</sub> | maximum junction |            | -   | -   | 125 | °C   |

|                     | temperature      |            |     |     |     |      |

#### Table 14. LPC111x/x01 Thermal resistance value (°C/W): ±15 %

| HVQFN33                            |      | LQFP48                  | LQFP48<br>θja |  |  |  |  |

|------------------------------------|------|-------------------------|---------------|--|--|--|--|

| өја                                |      | θја                     |               |  |  |  |  |

| JEDEC (4.5 in × 4 in)              |      | JEDEC (4.5 in × 4 in)   |               |  |  |  |  |

| 0 m/s                              | 40.4 | 0 m/s                   | 82.1          |  |  |  |  |

| 1 m/s                              | 32.7 | 1 m/s                   | 73.7          |  |  |  |  |

| 2.5 m/s                            | 28.3 | 2.5 m/s                 | 68.2          |  |  |  |  |

| Single-layer (4.5 in $\times$ 3 in | )    | 8-layer (4.5 in × 3 in) |               |  |  |  |  |

| 0 m/s                              | 84.8 | 0 m/s                   | 115.2         |  |  |  |  |

| 1 m/s                              | 61.6 | 1 m/s                   | 94.7          |  |  |  |  |

| 2.5 m/s                            | 53.1 | 2.5 m/s                 | 86.3          |  |  |  |  |

| өјс                                | 20.3 | өјс                     | 29.6          |  |  |  |  |

| θjb                                | 1.1  | θjb                     | 34.2          |  |  |  |  |

32-bit ARM Cortex-M0 microcontroller

LPC111X

74 of 127

32-bit ARM Cortex-M0 microcontroller

All information provided in this document is subject to legal disclaimers

LPC111X

© NXP Semiconductors N.V. 2014. All rights reserved.

32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

### **12.** Application information

### 12.1 ADC usage notes

The following guidelines show how to increase the performance of the ADC in a noisy environment beyond the ADC specifications listed in <u>Table 18</u>:

- The ADC input trace must be short and as close as possible to the LPC1110/11/12/13/14/15 chip.

- The ADC input traces must be shielded from fast switching digital signals and noisy power supply lines.

- Because the ADC and the digital core share the same power supply, the power supply line must be adequately filtered.

- To improve the ADC performance in a very noisy environment, put the device in Sleep mode during the ADC conversion.

### 12.2 Use of ADC input trigger signals

For applications that use trigger signals to start conversions and require a precise sample frequency, ensure that the period of the trigger signal is an integral multiple of the period of the ADC clock.

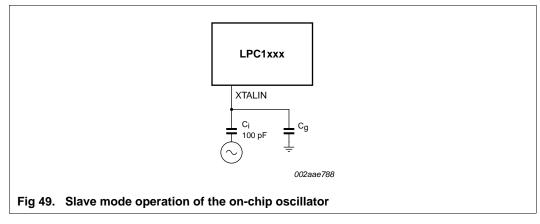

### 12.3 XTAL input

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i = 100 \text{ pF}$ . To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mV (RMS) is needed.

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF (Figure 49), with an amplitude between 200 mV (RMS) and 1000 mV (RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

External components and models used in oscillation mode are shown in <u>Figure 50</u> and in <u>Table 30</u> and <u>Table 31</u>. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of

32-bit ARM Cortex-M0 microcontroller

### 12.8 ADC effective input impedance

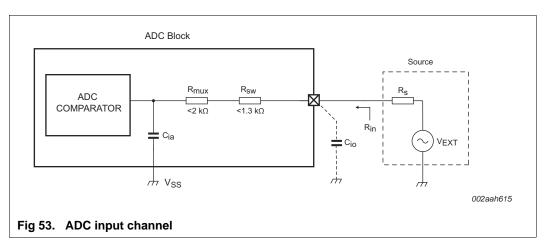

A simplified diagram of the ADC input channels can be used to determine the effective input impedance seen from an external voltage source. See Figure 53.

The effective input impedance,  $R_{in}$ , seen by the external voltage source,  $V_{EXT}$ , is the parallel impedance of ((1/f<sub>s</sub> x C<sub>ia</sub>) + R<sub>mux</sub> + R<sub>sw</sub>) and (1/f<sub>s</sub> x C<sub>io</sub>), and can be calculated using <u>Equation 2</u> with

fs = sampling frequency

$C_{ia} = ADC$  analog input capacitance

R<sub>mux</sub> = analog mux resistance

$R_{sw}$  = switch resistance

$C_{io}$  = pin capacitance

$$R_{in} = \left(\frac{1}{f_s \times C_{ia}} + R_{mux} + R_{sw}\right) \parallel \left(\frac{1}{f_s \times C_{io}}\right)$$

(2)

Under nominal operating condition  $V_{DD} = 3.3$  V and with the maximum sampling frequency fs = 400 kHz, the parameters assume the following values:

$$\begin{split} C_{ia} &= 1 \text{ pF (max)} \\ R_{mux} &= 2 \text{ k}\Omega \text{ (max)} \\ R_{sw} &= 1.3 \text{ k}\Omega \text{ (max)} \\ C_{io} &= 7.1 \text{ pF (max)} \end{split}$$

The effective input impedance with these parameters is  $R_{in} = 308 \text{ k}\Omega$ .

32-bit ARM Cortex-M0 microcontroller

Fig 62. Package outline TFBGA48 (SOT1155-2)

All information provided in this document is subject to legal disclaimers.

### **NXP Semiconductors**

## LPC1110/11/12/13/14/15

#### 32-bit ARM Cortex-M0 microcontroller

32-bit ARM Cortex-M0 microcontroller

#### 32-bit ARM Cortex-M0 microcontroller

| 12.8 | ADC effective input impedance 102 |

|------|-----------------------------------|

| 13   | Package outline 103               |

| 14   | Soldering 112                     |

| 15   | Abbreviations 120                 |

| 16   | References 120                    |

| 17   | Revision history 121              |

| 18   | Legal information 124             |

| 18.1 | Data sheet status 124             |

| 18.2 | Definitions 124                   |

| 18.3 | Disclaimers                       |

| 18.4 | Trademarks 125                    |

| 19   | Contact information 125           |

| 20   | Contents 126                      |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP Semiconductors N.V. 2014.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 26 March 2014 Document identifier: LPC111X