Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 1MHz                                                                     |

| Connectivity               | SPI                                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 2KB (1K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90ls2343-1pc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

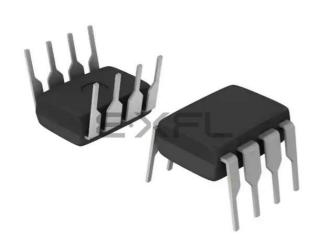

Figure 2. The AT90S/LS2323 Block Diagram

\$2323/2343 provides the following features: 2K bytes of In-System Programsh, 128 bytes EEPROM, 128 bytes SRAM, 3 (AT90S/LS2323)/5 43) general-purpose I/O lines, 32 general-purpose working registers, an 8-c internal and external interrupts, programmable Watchdog Timer with a SPI serial port for Flash Memory downloading and two software-pag modes. The Idle mode stops the CPU while allowing the sort and interrupt system to continue functioning. The sontents but freezes the oscillator, disabling all

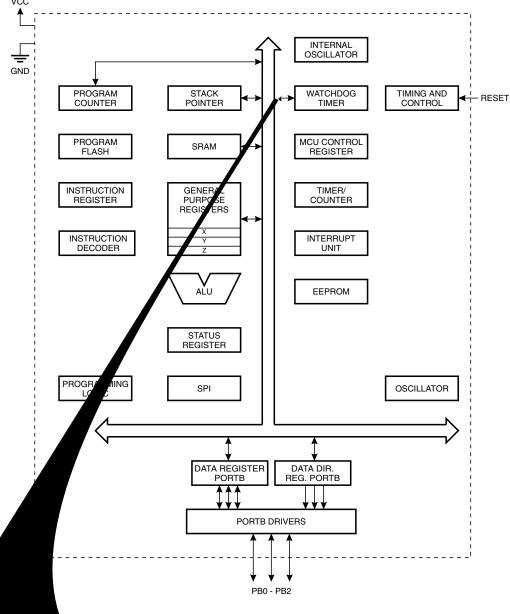

# X-register, Y-register and Z-register

The registers R26..R31 have some added functions to their general-purpose usage. These registers are the address pointers for indirect addressing of the Data Space. The three indirect address registers X, Y, and Z, are defined in Figure 8.

Figure 8. The X-, Y-, and Z-registers

In the different addressing modes, these address registers have functions as fixed displacement, automatic increment and decrement (see the descriptions for the different instructions).

# ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general-purpose working registers. Within a single clock cycle, ALU operations between registers in the register file are executed. The ALU operations are divided into three main categories: arithmetic, logic and bit functions.

# In-System Programmable Flash Program Memory

The AT90S2323/2343 contains 2K bytes On-chip, In-System Programmable Flash memory for program storage. Since all instructions are 16- or 32-bit words, the Flash is organized as 1K x 16. The Flash memory has an endurance of at least 1000 write/erase cycles.

The AT90S2323/2343 Program Counter (PC) is 10 bits wide, hence addressing the 1024 program memory addresses. See page 42 for a detailed description on Flash data programming.

Constant tables must be allocated within the address 0 - 2K (see the LPM – Load Program Memory instruction description on page 60).

See page 12 for the different addressing modes.

## **EEPROM Data Memory**

The AT90S2323/2343 contains 128 bytes of EEPROM data memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described on page 32, specifying the EEPROM address register, the EEPROM data register and the EEPROM control register.

For the SPI data downloading, see page 42 for a detailed description.

**Table 4.** Reset Characteristics ( $V_{CC} = 5.0V$ )

| Symbol            | Parameter                                                      | Min        | Тур                          | Max    | Units                |

|-------------------|----------------------------------------------------------------|------------|------------------------------|--------|----------------------|

| $V_{POT}^{(1)}$   | Power-on Reset Threshold Voltage, rising                       | 1.0        | 1.4                          | 1.8    | V                    |

| V POT`            | Power-on Reset Threshold Voltage, falling                      | 0.4        | 0.6                          | 8.0    | V                    |

| $V_{RST}$         | RESET Pin Threshold Voltage                                    |            | $0.6~\mathrm{V}_\mathrm{CC}$ |        | V                    |

| t <sub>TOUT</sub> | Reset Delay Time-out Period AT90S/LS2323<br>FSTRT Programmed   | 1.0        | 1.1                          | 1.2    | ms                   |

| t <sub>TOUT</sub> | Reset Delay Time-out Period AT90S/LS2323<br>FSTRT Unprogrammed | 11.0       | 16.0                         | 21.0   | ms                   |

| $t_{TOUT}$        | Reset Delay Time-out Period AT90S/LS2343                       | 11.0       | 16.0                         | 21.0   | μs                   |

| Note: 1.          | The Power-on Reset will not work unless the s (falling).       | supply vol | tage has b                   | een be | low V <sub>POT</sub> |

**Table 5.** Reset Characteristics ( $V_{CC} = 3.0V$ )

| Symbol            | Parameter                                                    | Min | Тур                 | Max | Units |

|-------------------|--------------------------------------------------------------|-----|---------------------|-----|-------|

| v (1)             | Power-on Reset Threshold Voltage, rising                     | 1.0 | 1.4                 | 1.8 | V     |

| $V_{POT}^{(1)}$   | Power-on Reset Threshold Voltage, falling                    | 0.4 | 0.6                 | 8.0 | V     |

| $V_{RST}$         | RESET Pin Threshold Voltage                                  |     | 0.6 V <sub>CC</sub> |     | ٧     |

| t <sub>TOUT</sub> | Reset Delay Time-out Period AT90S/LS2323<br>FSTRT Programmed | 2.0 | 2.2                 | 2.4 | ms    |

tTw76.24 41

Note: 1. The Power-on Reset will not work unless the supply voltage has been below  $V_{POT}$  (falling).

#### **Power-on Reset**

The AT90S2323/2343 is designed for use in systems where it can operate from the internal RC oscillator (AT90S/LS2343), on-chip oscillator (AT90S/LS2323), or in applications where a clock signal is provided by an external clock source. After  $V_{CC}$  has reached  $V_{POT}$ , the device will start after the time  $t_{TOUT}$  (see Figure 25). If the clock signal is provided by an external clock source, the clock must not be applied until  $V_{CC}$  has reached the minimum voltage defined for the applied frequency.

For AT90S2323, the user can select the start-up time according to typical oscillator start-up. The number of WDT oscillator cycles used for each time-out is shown in Table 6. For AT90S2343, the start-up time is one Watchdog cycle only. The frequency of the Watchdog oscillator is voltage-dependent as shown in "Typical Characteristics" on page 49.

The Stop condition provides a Timer Enable/Disable funct modes are scaled directly from the CK oscillator clock. If t used for Timer/Counter0, transitions on PB2/(T0) will clock the configured as an output. This feature can give the user software

#### Timer/Counter0 – TCNT0

The Timer/Counter0 is realized as an up-counter with read Timer/Counter0 is written and a clock source is present, the counting in the timer clock cycle following the write operation.

### Watchdog Timer

The Watchdog Timer is clocked from a separate On-chip osci Watchdog Timer prescaler, the Watchdog reset interval can Table 11. See characterization data for typical values at oth (Watchdog Reset) instruction resets the Watchdog Timer. E periods can be selected to determine the reset period. If the researcher Watchdog reset, the AT90S2323/2343 resets and exe tor. For timing details on the Watchdog reset, refer to page 23.

To prevent unintentional disabling of the Watchdog, a special tu followed when the Watchdog is disabled. Refer to the descriptio Control Register for details.

Figure 31. Watchdog Timer

For the EEPROM, an auto-erase cycle is provided within the self-timed Write instruction and there is no need to first execute the Chip Erase instruction. The Chip Erase instruction turns the content of every memory location in both the program and EEPROM arrays into \$FF.

The program and EEPROM memory arrays have separate address spaces: \$0000 to \$03FF for Flash program memory and \$000 to \$07F for EEPROM data memory.

Either an external clock is applied to the XTAL1/PB3 pin or the device must be clocked from the internal RC oscillator (AT90S/LS2343 only). The minimum low and high periods for the serial clock (SCK) input are defined as follows:

Low: > 2 MCU clock cycles High: > 2 MCU clock cycles

# Low-voltage Serial Programming Algorithm

When writing serial data to the AT90S2323/2343, data is clocked on the rising edge of SCK.

When reading data from the AT90S2323/2343, data is clocked on the falling edge of SCK. See Figure 36, Figure 37 and Table 20 for timing details.

To program and verify the AT90S2323/2343 in the low-voltage Serial Programming mode, the following sequence is recommended (see 4-byte instruction formats in Table 19):

1. Power-up sequence:

Apply power between  $V_{\rm CC}$  and GND while RESET and SCK are set to "0". (If the programmer cannot guarantee that SCK is held low during power-up, RESET must be given a positive pulse after SCK has been set to "0".) If the device is programmed for external clocking, apply a 0 - 8 MHz clock to the XTAL1/PB3 pin. If the internal RC oscillator is selected as the clock source, no external clock source needs to be applied (AT90S/LS2343 only).

2. Wait for at least 20 ms and enable serial programming by sending the Program-

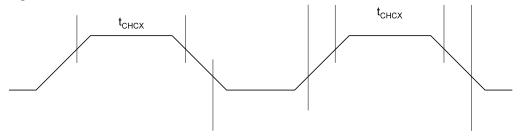

## **External Clock Drive Waveforms**

Figure 38. Waveforms

## **External Clock Drive**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$

|                     |                      | V <sub>CC</sub> : 2.7V to 4.0V |     | V <sub>CC</sub> : 2.7V to 4.0V V <sub>CC</sub> : 4.0V to 6.0V |      | to 6.0V |  |

|---------------------|----------------------|--------------------------------|-----|---------------------------------------------------------------|------|---------|--|

| Symbol              | Parameter            | Min                            | Max | Min                                                           | Max  | Units   |  |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                              | 4.0 | 0                                                             | 10.0 | MHz     |  |

| t <sub>CLCL</sub>   | Clock Period         | 250.0                          |     | 100.0                                                         |      | ns      |  |

| t <sub>CHCX</sub>   | High Time            | 100.0                          |     | 40.0                                                          |      | ns      |  |

| t <sub>CLCX</sub>   | Low Time             | 100.0                          |     | 40.0                                                          |      | ns      |  |

| t <sub>CLCH</sub>   | Rise Time            |                                | 1.6 |                                                               | 0.5  | μs      |  |

| t <sub>CHCL</sub>   | Fall Time            |                                | 1.6 |                                                               | 0.5  | μs      |  |

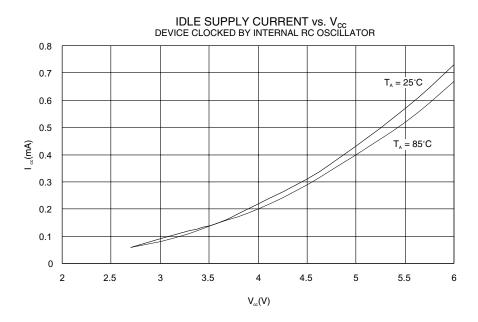

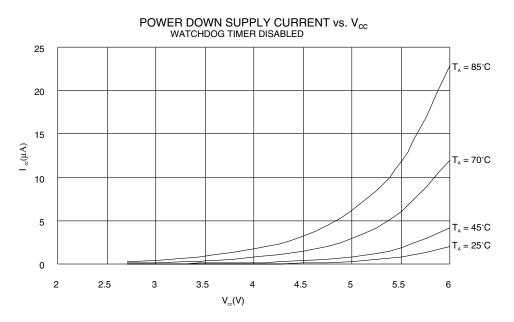

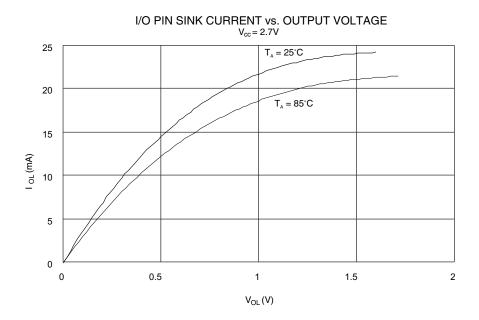

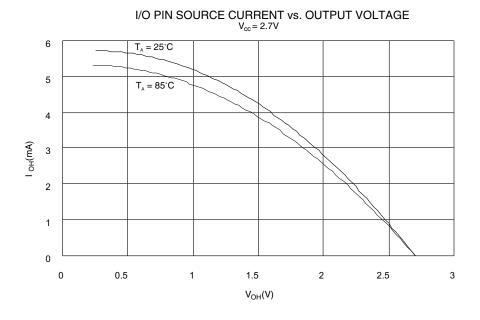

# Typical Characteristics

The following charts show typical behavior. These figures are not tested during manu-

Figure 44. Idle Supply Current vs. V<sub>CC</sub>

Figure 45. Power-down Supply Current vs. V<sub>CC</sub>

Figure 52. I/O Pin Sink Current vs. Output Voltage

Figure 53. I/O Pin Source Current vs. Output voltage

## **Instruction Set Summary**

| Mnemonic       | Operands           | Description                                              | Operation                                             | Flags                  | # Clocks |

|----------------|--------------------|----------------------------------------------------------|-------------------------------------------------------|------------------------|----------|

|                | <u> </u>           | •                                                        | Operation                                             | i iaga                 | # ОЮСКЭ  |

|                | LOGIC INSTRUCTIONS |                                                          | Tay ay a                                              | 7011111                |          |

| ADD            | Rd, Rr             | Add Two Registers                                        | Rd ← Rd + Rr                                          | Z,C,N,V,H              | 1        |

| ADC            | Rd, Rr             | Add with Carry Two Registers                             | Rd ← Rd + Rr + C                                      | Z,C,N,V,H              | 1        |

| ADIW           | Rdl, K             | Add Immediate to Word                                    | Rdh:Rdl ← Rdh:Rdl + K                                 | Z,C,N,V,S              | 2        |

| SUB            | Rd, Rr             | Subtract Two Registers                                   | Rd ← Rd − Rr                                          | Z,C,N,V,H              | 1        |

| SUBI           | Rd, K              | Subtract Constant from Register                          | Rd ← Rd − K                                           | Z,C,N,V,H              | 2        |

| SBIW           | Rdl, K             | Subtract Immediate from Word                             | Rdh:Rdl ← Rdh:Rdl – K                                 | Z,C,N,V,S              | 1        |

| SBC            | Rd, Rr<br>Rd, K    | Subtract with Carry Two Registers                        | Rd ← Rd − Rr − C                                      | Z,C,N,V,H<br>Z,C,N,V,H | 1 1      |

| SBCI           | <u> </u>           | Subtract with Carry Constant from Reg.                   | Rd ← Rd − K − C<br>Rd ← Rd • Rr                       |                        | 1        |

| AND            | Rd, Rr             | Logical AND Registers  Logical AND Register and Constant |                                                       | Z,N,V                  | 1 1      |

| ANDI<br>OR     | Rd, K              | Logical OR Register and Constant  Logical OR Registers   | Rd ← Rd • K                                           | Z,N,V                  | 1        |

| ORI            | Rd, Rr<br>Rd, K    | <u> </u>                                                 | Rd ← Rd v Rr                                          | Z,N,V<br>Z,N,V         | 1 1      |

| EOR            | Rd, Rr             | Logical OR Register and Constant                         | Rd ← Rd v K                                           | Z,N,V                  | 1        |

|                | Rd, Rr             | Exclusive OR Registers                                   | Rd ← Rd ⊕ Rr                                          |                        | 1        |

| NEG NEG        | Rd                 | One's Complement                                         | Rd ← \$FF – Rd                                        | Z,C,N,V<br>Z,C,N,V,H   | 1        |

|                | Rd, K              | Two's Complement                                         | Rd ← \$00 – Rd                                        |                        | 1        |

| SBR            |                    | Set Bit(s) in Register                                   | Rd ← Rd v K                                           | Z,N,V                  | 1        |

| CBR            | Rd, K              | Clear Bit(s) in Register                                 | Rd ← Rd • (\$FF – K)                                  | Z,N,V                  | 1 1      |

| INC            | Rd                 | Increment                                                | Rd ← Rd + 1                                           | Z,N,V                  | 1        |

| DEC            | Rd                 | Decrement Tank for Zona an Minus                         | Rd ← Rd − 1                                           | Z,N,V                  | 1        |

| TST            | Rd                 | Test for Zero or Minus                                   | Rd ← Rd • Rd                                          | Z,N,V                  | 1        |

| CLR            | Rd                 | Clear Register                                           | Rd ← Rd ⊕ Rd                                          | Z,N,V                  | 1        |

| SER            | Rd                 | Set Register                                             | Rd ← \$FF                                             | None                   | 1        |

| BRANCH INSTRUC |                    | I s                                                      | T no. no                                              | 1.,                    | 1 .      |

| RJMP           | k                  | Relative Jump                                            | PC ← PC + k + 1                                       | None                   | 2        |

| IJMP           | <u> </u>           | Indirect Jump to (Z)                                     | PC ← Z                                                | None                   | 2        |

| RCALL          | k                  | Relative Subroutine Call                                 | PC ← PC + k + 1                                       | None                   | 3        |

| ICALL          |                    | Indirect Call to (Z)                                     | PC ← Z                                                | None                   | 3        |

| RET            |                    | Subroutine Return                                        | PC ← STACK                                            | None                   | 4        |

| RETI           | D. D.              | Interrupt Return                                         | PC ← STACK                                            | l l                    | 4        |

| CPSE           | Rd, Rr             | Compare, Skip if Equal                                   | if (Rd = Rr) PC ← PC + 2 or 3                         | None                   | 1/2/3    |

| CP             | Rd, Rr             | Compare                                                  | Rd – Rr                                               | Z,N,V,C,H              | 1        |

| CPC            | Rd, Rr             | Compare with Carry                                       | Rd – Rr – C                                           | Z,N,V,C,H              | 1        |

| CPI            | Rd, K              | Compare Register with Immediate                          | Rd – K                                                | Z,N,V,C,H              | 1        |

| SBRC           | Rr, b              | Skip if Bit in Register Cleared                          | if $(Rr(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$   | None                   | 1/2/3    |

| SBRS           | Rr, b              | Skip if Bit in Register is Set                           | if $(Rr(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$   | None                   | 1/2/3    |

| SBIC           | P, b               | Skip if Bit in I/O Register Cleared                      | if $(P(b) = 0)$ PC $\leftarrow$ PC + 2 or 3           | None                   | 1/2/3    |

| SBIS           | P, b               | Skip if Bit in I/O Register is Set                       | if $(R(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$    | None                   | 1/2/3    |

| BRBS           | s, k               | Branch if Status Flag Set                                | if (SREG(s) = 1) then PC ← PC + k + 1                 | None                   | 1/2      |

| BRBC           | s, k               | Branch if Status Flag Cleared                            | if (SREG(s) = 0) then PC ← PC + k + 1                 | None                   | 1/2      |

| BREQ           | k                  | Branch if Equal                                          | if (Z = 1) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRNE           | k                  | Branch if Not Equal                                      | if (Z = 0) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRCS           | k                  | Branch if Carry Set                                      | if (C = 1) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRCC           | k                  | Branch if Carry Cleared                                  | if (C = 0) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRSH           | k                  | Branch if Same or Higher                                 | if (C = 0) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRLO           | <u>k</u>           | Branch if Lower                                          | if (C = 1) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRMI           | k                  | Branch if Minus                                          | if (N = 1) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRPL           | k                  | Branch if Plus                                           | if $(N = 0)$ then $PC \leftarrow PC + k + 1$          | None                   | 1/2      |

| BRGE           | k                  | Branch if I ass Than Zara Signed                         | if $(N \oplus V = 0)$ then $PC \leftarrow PC + k + 1$ | None                   | 1/2      |

| BRLT           | k                  | Branch if Less Than Zero, Signed                         | if $(N \oplus V = 1)$ then $PC \leftarrow PC + k + 1$ | None                   | 1/2      |

| BRHS           | k                  | Branch if Half-carry Flag Set                            | if (H = 1) then PC $\leftarrow$ PC + k + 1            | None                   | 1/2      |

| BRHC           | k                  | Branch if Half-carry Flag Cleared                        | if (H = 0) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRTS           | k                  | Branch if T-flag Set                                     | if (T = 1) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRTC           | k                  | Branch if T-flag Cleared                                 | if (T = 0) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRVS           | k                  | Branch if Overflow Flag is Set                           | if (V = 1) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRVC           | k                  | Branch if Overflow Flag is Cleared                       | if (V = 0) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRIE           | k                  | Branch if Interrupt Enabled                              | if (I = 1) then PC ← PC + k + 1                       | None                   | 1/2      |

| BRID           | k                  | Branch if Interrupt Disabled                             | if (I = 0) then PC $\leftarrow$ PC + k + 1            | None                   | 1/2      |

## **Instruction Set Summary (Continued)**

| Mnemonic                                                                |               | I                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                         |                                       |                                           |

|-------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------|

| DATA TRANSFED                                                           | Operands      | Description                                                                                                                                                                                                                                                                                                                                  | Operation                                                                                                                                                                                                                                                                               | Flags                                 | # Clocks                                  |

| PATA INANGEEN                                                           | INSTRUCTIONS  | 1                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                       | 1                                     | 1                                         |

| MOV                                                                     | Rd, Rr        | Move between Registers                                                                                                                                                                                                                                                                                                                       | Rd ← Rr                                                                                                                                                                                                                                                                                 | None                                  | 1                                         |

| LDI                                                                     | Rd, K         | Load Immediate                                                                                                                                                                                                                                                                                                                               | $Rd \leftarrow K$                                                                                                                                                                                                                                                                       | None                                  | 1                                         |

| LD                                                                      | Rd, X         | Load Indirect                                                                                                                                                                                                                                                                                                                                | $Rd \leftarrow (X)$                                                                                                                                                                                                                                                                     | None                                  | 2                                         |

| LD                                                                      | Rd, X+        | Load Indirect and Post-inc.                                                                                                                                                                                                                                                                                                                  | $Rd \leftarrow (X), X \leftarrow X + 1$                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| LD                                                                      | Rd, -X        | Load Indirect and Pre-dec.                                                                                                                                                                                                                                                                                                                   | $X \leftarrow X - 1$ , Rd $\leftarrow (X)$                                                                                                                                                                                                                                              | None                                  | 2                                         |

| LD                                                                      | Rd, Y         | Load Indirect                                                                                                                                                                                                                                                                                                                                | $Rd \leftarrow (Y)$                                                                                                                                                                                                                                                                     | None                                  | 2                                         |

| LD                                                                      | Rd, Y+        | Load Indirect and Post-inc.                                                                                                                                                                                                                                                                                                                  | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| LD                                                                      | Rd, -Y        | Load Indirect and Pre-dec.                                                                                                                                                                                                                                                                                                                   | $Y \leftarrow Y - 1$ , $Rd \leftarrow (Y)$                                                                                                                                                                                                                                              | None                                  | 2                                         |

| LDD                                                                     | Rd,Y+q        | Load Indirect with Displacement                                                                                                                                                                                                                                                                                                              | $Rd \leftarrow (Y + q)$                                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| LD                                                                      | Rd, Z         | Load Indirect                                                                                                                                                                                                                                                                                                                                | $Rd \leftarrow (Z)$                                                                                                                                                                                                                                                                     | None                                  | 2                                         |

| LD                                                                      | Rd, Z+        | Load Indirect and Post-inc.                                                                                                                                                                                                                                                                                                                  | $Rd \leftarrow (Z), Z \leftarrow Z + 1$                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| LD                                                                      | Rd, -Z        | Load Indirect and Pre-dec.                                                                                                                                                                                                                                                                                                                   | $Z \leftarrow Z - 1$ , $Rd \leftarrow (Z)$                                                                                                                                                                                                                                              | None                                  | 2                                         |

| LDD                                                                     | Rd, Z+q       | Load Indirect with Displacement                                                                                                                                                                                                                                                                                                              | $Rd \leftarrow (Z + q)$                                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| LDS                                                                     | Rd, k         | Load Direct from SRAM                                                                                                                                                                                                                                                                                                                        | $Rd \leftarrow (k)$                                                                                                                                                                                                                                                                     | None                                  | 2                                         |

| ST                                                                      | X, Rr         | Store Indirect                                                                                                                                                                                                                                                                                                                               | (X) ← Rr                                                                                                                                                                                                                                                                                | None                                  | 2                                         |

| ST                                                                      | X+, Rr        | Store Indirect and Post-inc.                                                                                                                                                                                                                                                                                                                 | $(X) \leftarrow Rr, X \leftarrow X + 1$                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| ST                                                                      | -X, Rr        | Store Indirect and Pre-dec.                                                                                                                                                                                                                                                                                                                  | $X \leftarrow X - 1$ , $(X) \leftarrow Rr$                                                                                                                                                                                                                                              | None                                  | 2                                         |

| ST                                                                      | Y, Rr         | Store Indirect                                                                                                                                                                                                                                                                                                                               | $(Y) \leftarrow Rr$                                                                                                                                                                                                                                                                     | None                                  | 2                                         |

| ST                                                                      | Y+, Rr        | Store Indirect and Post-inc.                                                                                                                                                                                                                                                                                                                 | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| ST                                                                      | -Y, Rr        | Store Indirect and Pre-dec.                                                                                                                                                                                                                                                                                                                  | $Y \leftarrow Y - 1$ , $(Y) \leftarrow Rr$                                                                                                                                                                                                                                              | None                                  | 2                                         |

| STD                                                                     | Y+q, Rr       | Store Indirect with Displacement                                                                                                                                                                                                                                                                                                             | $(Y + q) \leftarrow Rr$                                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| ST                                                                      | Z, Rr         | Store Indirect                                                                                                                                                                                                                                                                                                                               | (Z) ← Rr                                                                                                                                                                                                                                                                                | None                                  | 2                                         |

| ST                                                                      | Z+, Rr        | Store Indirect and Post-inc.                                                                                                                                                                                                                                                                                                                 | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$                                                                                                                                                                                                                                                 | None                                  | 2                                         |

| ST                                                                      | -Z, Rr        | Store Indirect and Pre-dec.                                                                                                                                                                                                                                                                                                                  | $Z \leftarrow Z - 1$ , $(Z) \leftarrow Rr$                                                                                                                                                                                                                                              | None                                  | 2                                         |

| STD                                                                     | Z+q, Rr       | Store Indirect with Displacement                                                                                                                                                                                                                                                                                                             | (Z + q) ← Rr                                                                                                                                                                                                                                                                            | None                                  | 2                                         |

| STS                                                                     | k, Rr         | Store Direct to SRAM                                                                                                                                                                                                                                                                                                                         | (k) ← Rr                                                                                                                                                                                                                                                                                | None                                  | 2                                         |

| LPM                                                                     |               | Load Program Memory                                                                                                                                                                                                                                                                                                                          | R0 ← (Z)                                                                                                                                                                                                                                                                                | None                                  | 3                                         |

| IN                                                                      | Rd, P         | In Port                                                                                                                                                                                                                                                                                                                                      | Rd ← P                                                                                                                                                                                                                                                                                  | None                                  | 1                                         |

| OUT                                                                     | P, Rr         | Out Port                                                                                                                                                                                                                                                                                                                                     | P ← Rr                                                                                                                                                                                                                                                                                  | None                                  | 1                                         |

| PUSH                                                                    | Rr            | Push Register on Stack                                                                                                                                                                                                                                                                                                                       | STACK ← Rr                                                                                                                                                                                                                                                                              | None                                  | 2                                         |

| POP                                                                     | Rd            | Pop Register from Stack                                                                                                                                                                                                                                                                                                                      | Rd ← STACK                                                                                                                                                                                                                                                                              | None                                  | 2                                         |

| BIT AND BIT-TEST                                                        | TINSTRUCTIONS |                                                                                                                                                                                                                                                                                                                                              | ·                                                                                                                                                                                                                                                                                       |                                       |                                           |

| SBI                                                                     | P, b          | Set Bit in I/O Register                                                                                                                                                                                                                                                                                                                      | I/O(P,b) ← 1                                                                                                                                                                                                                                                                            | None                                  | 2                                         |

| CBI                                                                     | P, b          | Clear Bit in I/O Register                                                                                                                                                                                                                                                                                                                    | I/O(P,b) ← 0                                                                                                                                                                                                                                                                            | None                                  | 2                                         |

| LSL                                                                     | Rd            | Logical Shift Left                                                                                                                                                                                                                                                                                                                           | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                                                                                                                                                                                                                                          | Z,C,N,V                               | 1                                         |

| LSR                                                                     | Rd            | Logical Shift Right                                                                                                                                                                                                                                                                                                                          | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                                                                                                                                                                                                                                          | Z,C,N,V                               | 1                                         |

| ROL                                                                     | Rd            | Rotate Left through Carry                                                                                                                                                                                                                                                                                                                    | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$                                                                                                                                                                                                                      | Z,C,N,V                               | 1                                         |

| ROR                                                                     | Rd            | Rotate Right through Carry                                                                                                                                                                                                                                                                                                                   | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$                                                                                                                                                                                                                      | Z,C,N,V                               | 1                                         |

| ASR                                                                     | Rd            | Arithmetic Shift Right                                                                                                                                                                                                                                                                                                                       | $Rd(n) \leftarrow Rd(n+1), n = 06$                                                                                                                                                                                                                                                      | Z,C,N,V                               | 1                                         |

| SWAP                                                                    | Rd            | Swap Nibbles                                                                                                                                                                                                                                                                                                                                 | $Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30)$                                                                                                                                                                                                                                    | None                                  | 1                                         |

| BSET                                                                    | s             | Flag Set                                                                                                                                                                                                                                                                                                                                     | SREG(s) $\leftarrow$ 1                                                                                                                                                                                                                                                                  | SREG(s)                               | 1                                         |

| BCLR                                                                    | s             | Flag Clear                                                                                                                                                                                                                                                                                                                                   | SREG(s) ← 0                                                                                                                                                                                                                                                                             | SREG(s)                               | 1                                         |

| BST                                                                     | Rr, b         | Bit Store from Register to T                                                                                                                                                                                                                                                                                                                 | $T \leftarrow Rr(b)$                                                                                                                                                                                                                                                                    | T                                     | 1                                         |

| BLD                                                                     |               | -                                                                                                                                                                                                                                                                                                                                            | $Rd(b) \leftarrow T$                                                                                                                                                                                                                                                                    | None                                  | 1                                         |

|                                                                         | I Rd h        |                                                                                                                                                                                                                                                                                                                                              | (5) \                                                                                                                                                                                                                                                                                   | 110110                                |                                           |

|                                                                         | Rd, b         | Bit Load from T to Register Set Carry                                                                                                                                                                                                                                                                                                        | C ← 1                                                                                                                                                                                                                                                                                   | С                                     |                                           |

| SEC                                                                     | Hd, b         | Set Carry                                                                                                                                                                                                                                                                                                                                    | C ← 1                                                                                                                                                                                                                                                                                   | С                                     | 1                                         |

| SEC<br>CLC                                                              | Rd, b         | Set Carry Clear Carry                                                                                                                                                                                                                                                                                                                        | C ← 0                                                                                                                                                                                                                                                                                   | С                                     | 1 1                                       |

| SEC<br>CLC<br>SEN                                                       | Hd, b         | Set Carry Clear Carry Set Negative Flag                                                                                                                                                                                                                                                                                                      | C ← 0<br>N ← 1                                                                                                                                                                                                                                                                          | C<br>N                                | 1 1 1                                     |

| SEC<br>CLC<br>SEN<br>CLN                                                | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag                                                                                                                                                                                                                                                                                  | $ \begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \end{array} $                                                                                                                                                                                                     | C<br>N<br>N                           | 1<br>1<br>1<br>1                          |

| SEC CLC SEN CLN SEZ                                                     | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag                                                                                                                                                                                                                                                                    | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \end{array}$                                                                                                                                                                                     | C<br>N<br>N<br>Z                      | 1<br>1<br>1<br>1                          |

| SEC CLC SEN CLN SEZ CLZ                                                 | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag                                                                                                                                                                                                                                                    | $C \leftarrow 0$<br>$N \leftarrow 1$<br>$N \leftarrow 0$<br>$Z \leftarrow 1$<br>$Z \leftarrow 0$                                                                                                                                                                                        | C N N Z Z Z                           | 1<br>1<br>1<br>1<br>1<br>1                |

| SEC CLC SEN CLN SEZ CLZ SEI                                             | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable                                                                                                                                                                                                                            | $C \leftarrow 0$<br>$N \leftarrow 1$<br>$N \leftarrow 0$<br>$Z \leftarrow 1$<br>$Z \leftarrow 0$<br>$I \leftarrow 1$                                                                                                                                                                    | C<br>N<br>N<br>Z<br>Z                 | 1<br>1<br>1<br>1<br>1<br>1<br>1           |

| SEC CLC SEN CLN SEZ CLZ SEI CLI                                         | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable                                                                                                                                                                                                   | $C \leftarrow 0$ $N \leftarrow 1$ $N \leftarrow 0$ $Z \leftarrow 1$ $Z \leftarrow 0$ $I \leftarrow 1$ $I \leftarrow 0$                                                                                                                                                                  | C N N Z Z I I I                       | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES                                     | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag                                                                                                                                                                              | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \end{array}$                                                                                                             | C N N S Z Z I I S S                   | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS                                 | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag                                                                                                                                                       | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \end{array}$                                                                                           | C N N N Z Z Z I I I S S S             | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SES                             | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Two's Complement Overflow                                                                                                                         | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \end{array}$                                                                         | C N N N Z Z Z I I I S S S V           | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SEV CLV                         | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Two's Complement Overflow Clear Two's Complement Overflow                                                                                         | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \end{array}$                                                       | C N N N Z Z Z I I I S S S V V V       | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SEV CLV SET                     | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Two's Complement Overflow Clear Two's Complement Overflow Set T in SREG                                                                           | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ T \leftarrow 1 \end{array}$                                     | C N N N Z Z Z I I I S S S V V V T T   | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SES CLS SEV CLV SET CLT         | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Clear Tin SREG Clear T in SREG                                                                                                                        | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ T \leftarrow 1 \\ T \leftarrow 0 \\ \end{array}$                | C N N N Z Z Z I I I S S S V V V T T T | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SES CLS SEV CLV SET CLT SEH     | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Two's Complement Overflow Clear Two's Complement Overflow Set T in SREG Clear T in SREG Set Half-carry Flag in SREG                               | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ T \leftarrow 1 \\ T \leftarrow 0 \\ H \leftarrow 1 \end{array}$ | C N N Z Z Z I I I S S S V V V T T T H | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SES CLS SEV CLV SET CLT SEH CLH | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Two's Complement Overflow Clear Two's Complement Overflow Set T in SREG Clear T in SREG Set Half-carry Flag in SREG Clear Half-carry Flag in SREG | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ T \leftarrow 1 \\ T \leftarrow 0 \\ \end{array}$                | C N N S S S V V V T T T H H H         | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

| SEC CLC SEN CLN SEZ CLZ SEI CLI SES CLS SES CLS SEV CLV SET CLT SEH     | Hd, b         | Set Carry Clear Carry Set Negative Flag Clear Negative Flag Set Zero Flag Clear Zero Flag Global Interrupt Enable Global Interrupt Disable Set Signed Test Flag Clear Signed Test Flag Set Two's Complement Overflow Clear Two's Complement Overflow Set T in SREG Clear T in SREG Set Half-carry Flag in SREG                               | $\begin{array}{c} C \leftarrow 0 \\ N \leftarrow 1 \\ N \leftarrow 0 \\ Z \leftarrow 1 \\ Z \leftarrow 0 \\ I \leftarrow 1 \\ I \leftarrow 0 \\ S \leftarrow 1 \\ S \leftarrow 0 \\ V \leftarrow 1 \\ V \leftarrow 0 \\ T \leftarrow 1 \\ T \leftarrow 0 \\ H \leftarrow 1 \end{array}$ | C N N Z Z Z I I I S S S V V V T T T H | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1     |

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

Europe

Atmel SarL

Route des Arsenaux 41