Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 1MHz                                                                     |

| Connectivity               | SPI                                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 2KB (1K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 8-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90ls2343-1si |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Description

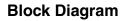

The AT90S/LS2323 and AT90S/LS2343 are low-power, CMOS, 8-bit microcontrollers based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S2323/2343 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general-purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

Figure 1. The AT90S/LS2343 Block Diagram

chip, the Atmel AT90S2323/2343 is a powerful microcontroller that provides a highly flexible and cost-effective solution to many embedded control applications.

The AT90S2323/2343 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators and evaluation kits.

# Comparison between AT90S/LS2323 and AT90S/LS2343

The AT90S/LS2323 is intended for use with external quartz crystal or ceramic resonator as the clock source. The start-up time is fuse-selectable as either 1 ms (suitable for ceramic resonator) or 16 ms (suitable for crystal). The device has three I/O pins.

The AT90S/LS2343 is intended for use with either an external clock source or the internal RC oscillator as clock source. The device has five I/O pins.

Table 1 summarizes the differences in features of the two devices.

| Table 1. | Feature Difference | Summary |

|----------|--------------------|---------|

|----------|--------------------|---------|

| Part                         | AT90S/LS2323 | AT90S/LS2343        |  |

|------------------------------|--------------|---------------------|--|

| On-chip Oscillator Amplifier | yes          | no                  |  |

| Internal RC Clock            | no           | yes                 |  |

| PB3 available as I/O pin     | never        | internal clock mode |  |

| PB4 available as I/O pin     | never        | always              |  |

| Start-up time                | 1 ms/16 ms   | 16 µs fixed         |  |

# Pin Descriptions AT90S/LS2323

| A1500/202020    |                                                                                                                                                                                                                                                       |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC             | Supply voltage pin.                                                                                                                                                                                                                                   |

| GND             | Ground pin.                                                                                                                                                                                                                                           |

| Port B (PB2PB0) | Port B is a 3-bit bi-directional I/O port with internal pull-up resistors. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low, will source current if the pull-up resistors are activated.               |

|                 | Port B also serves the functions of various special features.                                                                                                                                                                                         |

|                 | Port pins can provide internal pull-up resistors (selected for each bit). The Port B pins are tri-stated when a reset condition becomes active.                                                                                                       |

| RESET           | Reset input. An external reset is generated by a low level on the $\overrightarrow{\text{RESET}}$ pin. Reset pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. |

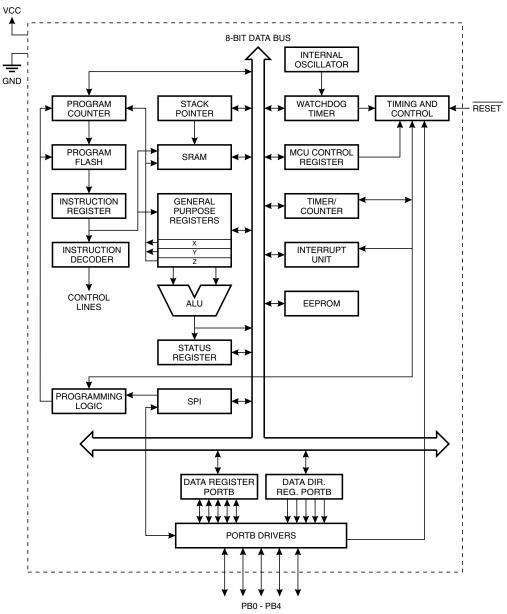

| XTAL1           | Input to the inverting oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                        |

| XTAL2           | Output from the inverting oscillator amplifier.                                                                                                                                                                                                       |

# Pin Descriptions AT90S/LS2343

| VCC                | Supply voltage pin.                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                | Ground pin.                                                                                                                                                                                                                                                                                                                                                            |

| Port B (PB4PB0)    | Port B is a 5-bit bi-directional I/O port with internal pull-up resistors. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low, will source current if the pull-up resistors are activated.                                                                                                                                |

|                    | Port B also serves the functions of various special features.                                                                                                                                                                                                                                                                                                          |

|                    | Port pins can provide internal pull-up resistors (selected for each bit). The Port B pins are tri-stated when a reset condition becomes active.                                                                                                                                                                                                                        |

| RESET              | Reset input. An external reset is generated by a low level on the $\overline{\text{RESET}}$ pin. Reset pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.                                                                                                                        |

| CLOCK              | Clock signal input in external clock mode.                                                                                                                                                                                                                                                                                                                             |

| Clock Options      |                                                                                                                                                                                                                                                                                                                                                                        |

| Crystal Oscillator | The AT90S/LS2323 contains an inverting amplifier that can be configured for use as an On-chip oscillator, as shown in Figure 3. XTAL1 and XTAL2 are input and output respectively. Either a quartz crystal or a ceramic resonator may be used. It is recommended that the AT90S/LS2343 be used if an external clock source is used, since this gives an extra I/O pin. |

Figure 3. Oscillator Connection

#### **External Clock**

The AT90S/LS2343 can be clocked by an external clock signal, as shown in Figure 4, or by the On-chip RC oscillator. This RC oscillator runs at a nominal frequency of 1 MHz ( $V_{CC} = 5V$ ). A fuse bit (RCEN) in the Flash memory selects the On-chip RC oscillator as the clock source when programmed ("0"). The AT90S/LS2343 is shipped with this bit programmed. The AT90S/LS2343 is recommended if an external clock source is used, because this gives an extra I/O pin.

The AT90S/LS2323 can be clocked by an external clock as well, as shown in Figure 4. No fuse bit selects the clock source for AT90S/LS2323.

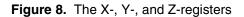

# X-register, Y-register and Z-register

The registers R26..R31 have some added functions to their general-purpose usage. These registers are the address pointers for indirect addressing of the Data Space. The three indirect address registers X, Y, and Z, are defined in Figure 8.

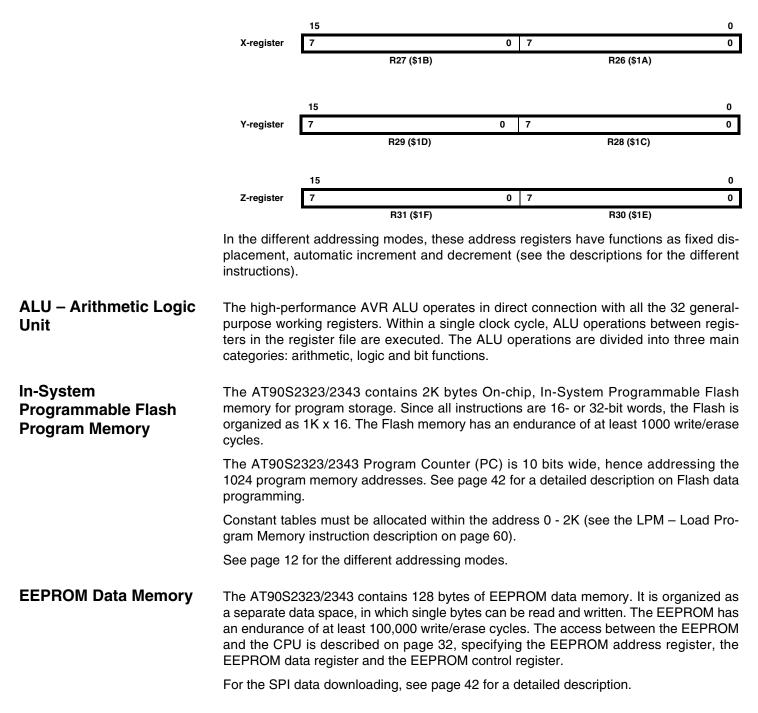

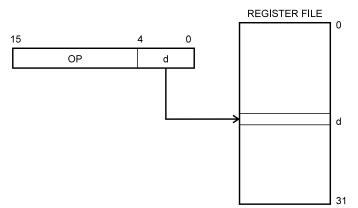

Program and Data Addressing Modes The AT90S2323/2343 AVR RISC microcontroller supports powerful and efficient addressing modes for access to the program memory (Flash) and data memory. This section describes the different addressing modes supported by the AVR architecture. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits.

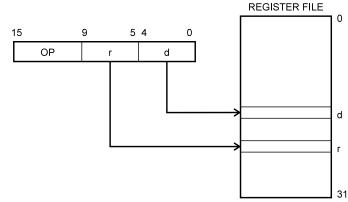

Figure 10. Direct Single Register Addressing

Register Direct, Single Register Rd

**Register Direct, Two Registers** Figure 11. Direct Register Addressing, Two Registers Rd and Rr

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

#### I/O Direct

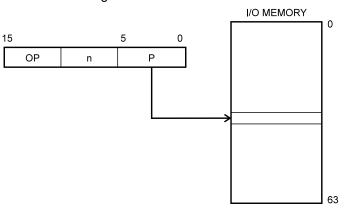

Figure 12. I/O Direct Addressing

Operand address is contained in six bits of the instruction word. n is the destination or source register address.

**Data Direct**

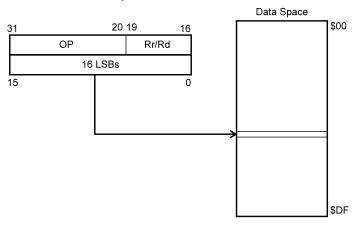

Figure 13. Direct Data Addressing

A 16-bit data address is contained in the 16 LSBs of a 2-word instruction. Rd/Rr specify the destination or source register.

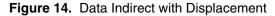

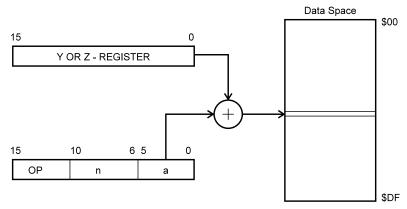

Operand address is the result of the Y- or Z-register contents added to the address contained in six bits of the instruction word.

Data Indirect with Displacement

and OUT, the I/O addresses \$00 - \$3F must be used. When addressing I/O registers as SRAM, \$20 must be added to these addresses. All I/O register addresses throughout this document are shown with the SRAM address in parentheses.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical "1" to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a "1" back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

The I/O and peripherals control registers are explained in the following sections.

Status Register – SREG The AVR Status Register (SREG) at I/O space location \$3F (\$5F) is defined as:

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F)   | I   | Т   | Н   | S   | v   | N   | Z   | С   | SREG |

| Read/Write    | R/W | -    |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### • Bit 7 – I: Global Interrupt Enable

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the global interrupt enable register is cleared (zero), none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred and is set by the RETI instruction to enable subsequent interrupts.

#### • Bit 6 – T: Bit Copy Storage

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source and destination for the operated bit. A bit from a register in the register file can be copied into T by the BST instruction and a bit in T can be copied into a bit in a register in the register file by the BLD instruction.

#### • Bit 5 – H: Half-carry Flag

The half-carry flag H indicates a half-carry in some arithmetic operations. See the Instruction Set description for detailed information.

• Bit 4 – S: Sign Bit, S = N ⊕ V

The S-bit is always an exclusive or between the negative flag N and the two's complement overflow flag V. See the Instruction Set description for detailed information.

#### • Bit 3 – V: Two's Complement Overflow Flag

The two's complement overflow flag V supports two's complement arithmetics. See the Instruction Set description for detailed information.

#### • Bit 2 – N: Negative Flag

The negative flag N indicates a negative result from an arithmetical or logical operation. See the Instruction Set description for detailed information.

#### • Bit 1 – Z: Zero Flag

The zero flag Z indicates a zero result from an arithmetical or logical operation. See the Instruction Set description for detailed information.

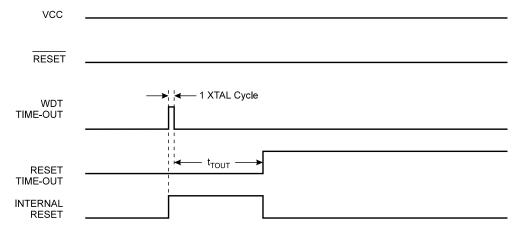

#### Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of 1 CPU clock cycle duration. On the falling edge of this pulse, the delay timer starts counting the Time-out period  $t_{TOUT}$ . Refer to page 30 for details on operation of the Watchdog.

Figure 28. Watchdog Reset during Operation

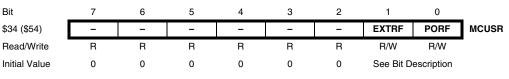

#### MCU Status Register – MCUSR

The MCU Status Register provides information on which reset source caused an MCU reset.

• Bits 7..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read as zero.

#### • Bit 1 – EXTRF: External Reset Flag

After a Power-on Reset, this bit is undefined (X). It will be set by an External Reset. A Watchdog Reset will leave this bit unchanged.

Bit 0 – PORF: Power-on Reset Flag

This bit is set by a Power-on Reset. A Watchdog Reset or an External Reset will leave this bit unchanged.

To summarize, Table 7 shows the value of these two bits after the three modes of reset.

#### Table 7. PORF and EXTRF Values after Reset

| Reset Source   | PORF      | EXTRF     |

|----------------|-----------|-----------|

| Power-on Reset | 1         | Undefined |

| External Reset | Unchanged | 1         |

| Watchdog Reset | Unchanged | Unchanged |

To make use of these bits to identify a reset condition, the user software should clear both the PORF and EXTRF bits as early as possible in the program. Checking the PORF and EXTRF values is done before the bits are cleared. If the bit is cleared before an External or Watchdog Reset occurs, the source of reset can be found by using the following truth table, Table 8.

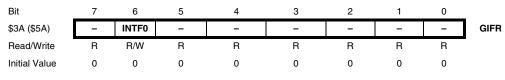

#### General Interrupt Flag Register – GIFR

#### • Bit 7 – Res: Reserved Bit

This bit is a reserved bit in the AT90S2323/2343 and always reads as zero.

#### • Bit 6 – INTF0: External Interrupt Flag0

When an edge on the INTO pin triggers an interrupt request, the corresponding interrupt flag, INTFO becomes set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INTO in GIMSK, is set (one), the MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag is cleared by writing a logical "1" to it. This flag is always cleared when INTO is configured as level interrupt.

#### • Bits 5..0 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read as zero.

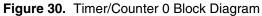

### Timer/Counter Interrupt Mask

Register – TIMSK

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0 | _     |

|---------------|---|---|---|---|---|---|-------|---|-------|

| \$39 (\$59)   | - | - | - | - | - | - | TOIE0 | - | TIMSK |

| Read/Write    | R | R | R | R | R | R | R/W   | R | -     |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0 |       |

#### • Bits 7..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read zero.

#### • Bit 1 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt (at vector \$002) is executed if an overflow in Timer/Counter0 occurs, i.e., when the Overflow Flag (Timer/Counter0) is set (one) in the Timer/Counter Interrupt Flag Register (TIFR).

#### • Bit 0 - Res: Reserved Bit

This bit is a reserved bit in the AT90S2323/2343 and always reads as zero.

#### Timer/Counter Interrupt FLAG Register – TIFR

#### • Bits 7..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read zero.

#### • Bit 1 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logical "1" to the flag. When the SREG I-bit and TOIE0 (Timer/Counter0 Overflow Interrupt Enable) and TOV0 are set (one), the Timer/Counter0 Overflow Interrupt is executed.

#### • Bit 0 – Res: Reserved Bit

This bit is a reserved bit in the AT90S2323/2343 and always reads zero.

**External Interrupt** The external interrupt is triggered by the INTO pin. Observe that, if enabled, the interrupt will trigger even if the INTO pin is configured as an output. This feature provides a way of generating a software interrupt. The external interrupt can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register (MCUCR). When the external interrupt is enabled and is configured as level-triggered, the interrupt will trigger as long as the pin is held low.

The external interrupt is set up as described in the specification for the MCU Control Register (MCUCR).

Interrupt Response Time The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. Four clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During these four clock cycles, the Program Counter (2 bytes) is popped back from the stack, the Stack Pointer is incremented by 2 and the I-flag in SREG is set. The vector is a relative jump to the interrupt routine and this jump takes two clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes four clock cycles. During these four clock cycles, the Program Counter (2 bytes) is popped back from the stack and the Stack Pointer is incremented by 2. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

MCU Control Register – MCUCR The MCU Control Register contains control bits for general MCU functions.

| Bit           | 7 | 6 | 5   | 4   | 3 | 2 | 1     | 0     | _     |

|---------------|---|---|-----|-----|---|---|-------|-------|-------|

| \$35 (\$55)   | - | - | SE  | SM  | - | - | ISC01 | ISC00 | MCUCR |

| Read/Write    | R | R | R/W | R/W | R | R | R/W   | R/W   |       |

| Initial Value | 0 | 0 | 0   | 0   | 0 | 0 | 0     | 0     |       |

#### • Bits 7, 6 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read as zero.

#### • Bit 5 – SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the Sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the Sleep mode, unless it is the programmer's purpose, it is recommended to set the Sleep Enable (SE) bit just before the execution of the SLEEP instruction.

#### • Bit 4 – SM: Sleep Mode

This bit selects between the two available sleep modes. When SM is cleared (zero), Idle mode is selected as Sleep mode. When SM is set (one), Power-down mode is selected as sleep mode. For details, refer to the section "Sleep Modes".

• Bits 3, 2 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read as zero.

#### • Bits 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT0 pin that

• Bits 7..3 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read zero.

#### • Bits 2, 1, 0 – CS02, CS01, CS00: Clock Select0, Bits 2, 1 and 0

The Clock Select0 bits 2, 1 and 0 define the prescaling source of Timer/Counter0.

Table 10. Clock 0 Prescale Select

| CS02 | CS01 | CS00 | Description                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Stop, the Timer/Counter0 is stopped. |

| 0    | 0    | 1    | СК                                   |

| 0    | 1    | 0    | CK/8                                 |

| 0    | 1    | 1    | CK/64                                |

| 1    | 0    | 0    | CK/256                               |

| 1    | 0    | 1    | CK/1024                              |

| 1    | 1    | 0    | External Pin T0, falling edge        |

| 1    | 1    | 1    | External Pin T0, rising edge         |

Timer/Counter0 Control Register – TCCR0

| Table 16. | High-voltage | Serial Programming | Instruction Set |

|-----------|--------------|--------------------|-----------------|

|-----------|--------------|--------------------|-----------------|

|                                        | Instruction Format |                                                                      |                                                                      |                                                             |                                                    |                                                                                                                                               |  |

|----------------------------------------|--------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Instruction                            |                    | Instr.1                                                              | Instr.2                                                              | Instr.3                                                     | Instr.4                                            | Operation Remarks                                                                                                                             |  |

| Chip Erase                             | PB0<br>PB1<br>PB2  | 0_1000_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0110_1100_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx     | Wait $t_{WLWH_CE}$ after Instr.3 for the Chip Erase cycle to finish.                                                                          |  |

| Write Flash<br>High and Low<br>Address | PB0<br>PB1<br>PB2  | 0_0001_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx                       | 0_0000_00 <b>aa</b> _00<br>0_0001_1100_00<br>x_xxxx_xxxx_xx          | 0_ <b>bbbb_bbbb</b> _00<br>0_0000_1100_00<br>x_xxxx_xxxx_xx |                                                    | Repeat Instr.2 for a new 256-byte page. Repeat Instr.3 for each new address.                                                                  |  |

| Write Flash<br>Low Byte                | PB0<br>PB1<br>PB2  | 0_1111_1111_00<br>0_0010_1100_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0110_1100_00<br>0_0000_0000_00          |                                                    | Wait after Instr.3 until PB2<br>goes high. Repeat Instr.1,<br>Instr. 2 and Instr.3 for each<br>new address.                                   |  |

| Write Flash<br>High Byte               | PB0<br>PB1<br>PB2  | 0_1111_1111_00<br>0_0010_1100_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0111_0100_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0111_1100_00<br>0_0000_0000_00          |                                                    | Wait after Instr.3 until PB2<br>goes high. Repeat Instr.1,<br>Instr. 2 and Instr.3 for each<br>new address.                                   |  |

| Read Flash<br>High and Low<br>Address  | PB0<br>PB1<br>PB2  | 0_0000_0010_00<br>0_0100_1100_00<br>x_xxxx_xxx                       | 0_0000_00 <b>aa</b> _00<br>0_0001_1100_00<br>x_xxxx_xxxx_xx          | 0_ <b>bbbb_bbbb</b> _00<br>0_0000_1100_00<br>x_xxxx_xxxx_xx |                                                    | Repeat Instr.2 and Instr.3 for each new address.                                                                                              |  |

| Read Flash<br>Low Byte                 | PB0<br>PB1<br>PB2  | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0110_1100_00<br><b>o_0000_000</b> x_xx           |                                                             |                                                    | Repeat Instr.1 and Instr.2 for each new address.                                                                                              |  |

| Read Flash<br>High Byte                | PB0<br>PB1P<br>B2  | 0_0000_0000_00<br>0_0111_1000_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0111_1100_00<br><b>0_0000_000</b>                |                                                             |                                                    | Repeat Instr.1 and Instr.2 for each new address.                                                                                              |  |

| Write<br>EEPROM<br>Low Address         | PB0<br>PB1<br>PB2  | 0_0001_0001_00<br>0_0100_1100_00<br>x_xxxx_xxx                       | 0_0 <b>bbb_bbbb</b> _00<br>0_0000_1100_00<br>x_xxxx_xxxx_xx          |                                                             |                                                    | Repeat Instr.2 for each new address.                                                                                                          |  |

| Write<br>EEPROM<br>Byte                | PB0<br>PB1<br>PB2  | 0_ <b>iiii</b> _ <b>iiii</b> _00<br>0_0010_1100_00<br>x_xxxx_xxxx_xx | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0110_1100_00<br>0_0000_0000_00          |                                                    | Wait after Instr.3 until PB2<br>goes high                                                                                                     |  |

| Read<br>EEPROM<br>Low Address          | PB0<br>PB1<br>PB2  | 0_0000_0011_00<br>0_0100_1100_00<br>x_xxxx_xxx                       | 0_0 <b>bbb_bbbb</b> _00<br>0_0000_1100_00<br>x_xxxx_xxxx_xx          |                                                             |                                                    | Repeat Instr.2 for each new address.                                                                                                          |  |

| Read<br>EEPROM<br>Byte                 | PB0<br>PB1<br>PB2  | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx                       | 0_0000_0000_00<br>0_0110_1100_00<br><b>0_0000_000</b>                |                                                             |                                                    | Repeat Instr.2 for each new address                                                                                                           |  |

| Write Fuse<br>Bits (AT90S/<br>LS2323)  | PB0<br>PB1<br>PB2  | 0_0100_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx                       | 0_11 <b>S</b> 1_111 <b>F</b> _00<br>0_0010_1100_00<br>x_xxxx_xxxx_xx | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br>x_xxxx_xxx     | Wait t <sub>WLWH_PFB</sub> after Instr.3 for<br>the Write Fuse bits cycle to<br>finish. Set <b>S,F</b> = "0" to<br>program, "1" to unprogram. |  |

| Write Fuse<br>Bits (AT90S/<br>LS2343)  | PB0<br>PB1<br>PB2  | 0_0100_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx                       | 0_11 <b>S</b> 1_111 <b>R</b> _00<br>0_0010_1100_00<br>x_xxxx_xxxx_xx | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br>x_xxxx_xxx     | Wait t <sub>WLWH_PFB</sub> after Instr.3 for<br>the Write Fuse bits cycle to<br>finish. Set <b>S,R</b> = "0" to<br>program, "1" to unprogram. |  |

| Write Lock<br>Bits                     | PB0<br>PB1<br>PB2  | 0_0010_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx                       | 0_1111_1 <b>21</b> 1_00<br>0_0010_1100_00<br>x_xxxx_xxxx_xx          | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br>0_0000_0000_00 | Wait after Instr.4 until PB2<br>goes high. Write <b>2</b> , <b>1</b> = "0" to<br>program the Lock bit.                                        |  |

### High-voltage Serial Programming Characteristics

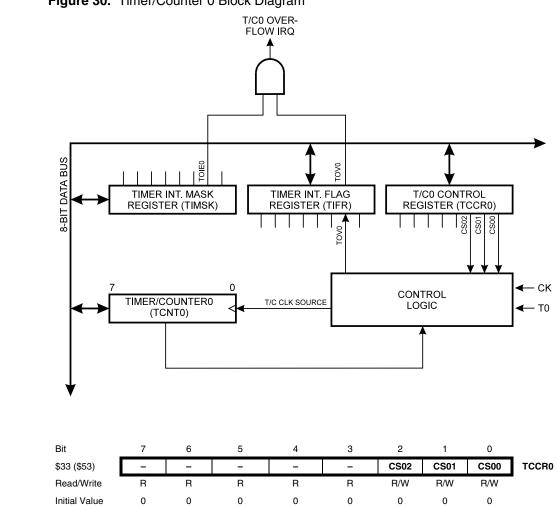

Figure 34. High-voltage Serial Programming Timing

**Table 17.** High-voltage Serial Programming Characteristics,  $T_A = 25^{\circ}C \pm 10^{\circ}$ ,  $V_{CC} = 5.0V \pm 10^{\circ}$  (unless otherwise noted)

| Symbol                | Parameter                                               | Min   | Тур  | Max  | Units |

|-----------------------|---------------------------------------------------------|-------|------|------|-------|

| t <sub>SHSL</sub>     | SCI (XTAL1/PB3) Pulse Width High                        | 100.0 |      |      | ns    |

| t <sub>SLSH</sub>     | SCI (XTAL1/PB3) Pulse Width Low                         | 100.0 |      |      | ns    |

| t <sub>IVSH</sub>     | SDI (PB0), SII (PB1) Valid to SCI (XTAL1/PB3)<br>High   | 50.0  |      |      | ns    |

| t <sub>shix</sub>     | SDI (PB0), SII (PB1) Hold after SCI (XTAL1/PB3)<br>High | 50.0  |      |      | ns    |

| t <sub>SHOV</sub>     | SCI (XTAL1/PB3) High to SDO (PB2) Valid                 | 10.0  | 16.0 | 32.0 | ns    |

| t <sub>WLWH_CE</sub>  | Wait after Instr.3 for Chip Erase                       | 5.0   | 10.0 | 15.0 | ms    |

| t <sub>WLWH_PFB</sub> | Wait after Instr.3 for Write Fuse Bits                  | 1.0   | 1.5  | 1.8  | ms    |

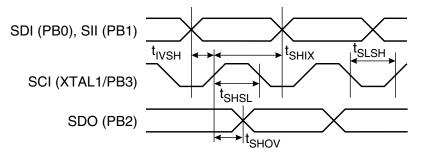

#### Low-voltage Serial Downloading

Both the program and data memory arrays can be programmed using the serial SPI bus while RESET is pulled to GND. The serial interface consists of pins SCK, MOSI (input) and MISO (output) (see Figure 35). After RESET is set low, the Programming Enable instruction needs to be executed first before program/erase instructions can be executed.

Figure 35. Low-voltage Serial Programming and Verify

### **Electrical Characteristics**

### **Absolute Maximum Ratings\***

| Operating Temperature55°C to +125°C                                                                     |

|---------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                                       |

| Voltage on Any Pin except $\overrightarrow{\text{RESET}}$ with respect to Ground1.0V to $V_{CC}$ + 0.5V |

| Voltage on RESET with Respect to Ground1.0V to +13.0V                                                   |

| Maximum Operating Voltage 6.6V                                                                          |

| DC Current per I/O Pin 40.0 mA                                                                          |

| DC Current $V_{CC}$ and GND Pins                                                                        |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

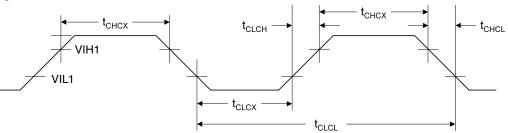

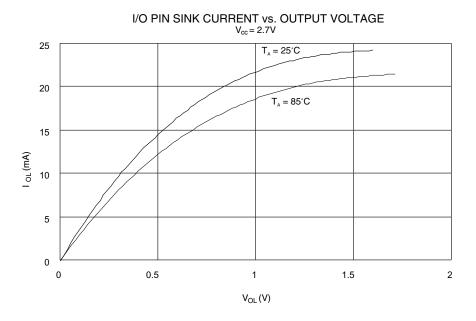

#### **DC Characteristics**

| $T_A = -40^{\circ}C$ to 85°C, $V_{CC} = 2.7V$ to 6.0V (unless otherwise no |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|

| Symbol           | Parameter                         | Condition                                                                        | Min                                 | Тур  | Max                                | Units  |

|------------------|-----------------------------------|----------------------------------------------------------------------------------|-------------------------------------|------|------------------------------------|--------|

| V <sub>IL</sub>  | Input Low Voltage                 | (Except XTAL)                                                                    | -0.5                                |      | 0.3 V <sub>CC</sub> <sup>(1)</sup> | V      |

| V <sub>IL1</sub> | Input Low Voltage                 | XTAL                                                                             | -0.5                                |      | 0.1 <sup>(1)</sup>                 | V      |

| V <sub>IH</sub>  | Input High Voltage                | (Except XTAL, RESET)                                                             | 0.6 V <sub>CC</sub> <sup>(2)</sup>  |      | V <sub>CC</sub> + 0.5              | V      |

| V <sub>IH1</sub> | Input High Voltage                | XTAL                                                                             | 0.7 V <sub>CC</sub> <sup>(2)</sup>  |      | V <sub>CC</sub> + 0.5              | V      |

| V <sub>IH2</sub> | Input High Voltage                | RESET                                                                            | 0.85 V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5              | V      |

| V <sub>OL</sub>  | Output Low Voltage Ports B        | $I_{OL}$ = 20 mA, $V_{CC}$ = 5V<br>$I_{OL}$ = 10 mA, $V_{CC}$ = 3V               |                                     |      | 0.5<br>0.4                         | V<br>V |

| V <sub>он</sub>  | Output High Voltage Ports B       | $I_{OH} = -3 \text{ mA}, V_{CC} = 5V$<br>$I_{OH} = -1.5 \text{ mA}, V_{CC} = 3V$ | 4.2<br>2.4                          |      |                                    | V<br>V |

| I                | Input Leakage<br>Current I/O Pin  | V <sub>CC</sub> = 6V, Pin Low<br>(absolute value)                                |                                     |      | 8.0                                | μA     |

| I <sub>IH</sub>  | Input Leakage<br>Current I/O Pin  | V <sub>CC</sub> = 6V, Pin High<br>(absolute value)                               |                                     |      | 8.0                                | μA     |

| RRST             | Reset Pull-up                     |                                                                                  | 100.0                               |      | 500.0                              | kΩ     |

| R <sub>I/O</sub> | I/O Pin Pull-up                   |                                                                                  | 30.0                                |      | 150.0                              | kΩ     |

|                  | Power Supply Current<br>AT90S2343 | Active 4 MHz, V <sub>CC</sub> = 3V                                               |                                     |      | 3.0                                | mA     |

|                  |                                   | Idle 4 MHz, V <sub>CC</sub> = 3V                                                 |                                     |      | 1.1                                | mA     |

|                  |                                   | Power-down 4 MHz <sup>(3)</sup> ,<br>V <sub>CC</sub> = 3V WDT Enabled            |                                     |      | 25.0                               | μA     |

|                  |                                   | Power-down 4 MHz <sup>(3)</sup> ,<br>V <sub>CC</sub> = 3V WDT Disabled           |                                     |      | 20.0                               | μA     |

| I <sub>cc</sub>  | Power Supply Current<br>AT90S2323 | Active 4 MHz, V <sub>CC</sub> = 3V                                               |                                     |      | 4.0                                | mA     |

|                  |                                   | ldle 4 MHz, V <sub>CC</sub> = 3V                                                 |                                     | 1.0  | 1.2                                | mA     |

|                  |                                   | Power-down <sup>(3)</sup> ,<br>V <sub>CC</sub> = 3V WDT Enabled                  |                                     | 9.0  | 15.0                               | μA     |

|                  |                                   | Power-down <sup>(3)</sup> ,<br>$V_{CC}$ = 3V WDT Disabled                        |                                     | <1.0 | 2.0                                | μA     |

1. "Max" means the highest value where the pin is guaranteed to be read as low.

2. "Min" means the lowest value where the pin is guaranteed to be read as high.

3. Minimum  $V_{CC}$  for Power-down is 2V.

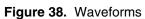

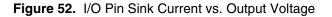

### **External Clock Drive Waveforms**

### **External Clock Drive**

| $T_A =$ | -40°C to | 85°C |

|---------|----------|------|

|---------|----------|------|

|                     |                      | V <sub>CC</sub> : 2.7V to 4.0V |     | V <sub>cc</sub> : 4.0V to 6.0V |      |       |

|---------------------|----------------------|--------------------------------|-----|--------------------------------|------|-------|

| Symbol              | Parameter            | Min                            | Max | Min                            | Max  | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                              | 4.0 | 0                              | 10.0 | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 250.0                          |     | 100.0                          |      | ns    |

| t <sub>CHCX</sub>   | High Time            | 100.0                          |     | 40.0                           |      | ns    |

| t <sub>CLCX</sub>   | Low Time             | 100.0                          |     | 40.0                           |      | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                                | 1.6 |                                | 0.5  | μs    |

| t <sub>CHCL</sub>   | Fall Time            |                                | 1.6 |                                | 0.5  | μs    |

## Instruction Set Summary

| Mnemonic       | Operands         | Description                                                      | Operation                                                                                    | Flags     | # Clocks |

|----------------|------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------|----------|

| ARITHMETIC AND | LOGIC INSTRUCTIO | ONS                                                              |                                                                                              |           |          |

| ADD            | Rd, Rr           | Add Two Registers                                                | $Rd \leftarrow Rd + Rr$                                                                      | Z,C,N,V,H | 1        |

| ADC            | Rd, Rr           | Add with Carry Two Registers                                     | $Rd \leftarrow Rd + Rr + C$                                                                  | Z,C,N,V,H | 1        |

| ADIW           | Rdl, K           | Add Immediate to Word                                            | Rdh:Rdl ← Rdh:Rdl + K                                                                        | Z,C,N,V,S | 2        |

| SUB            | Rd, Rr           | Subtract Two Registers                                           | Rd ← Rd – Rr                                                                                 | Z,C,N,V,H | 1        |

| SUBI           | Rd, K            | Subtract Constant from Register                                  | $Rd \leftarrow Rd - K$                                                                       | Z,C,N,V,H | 1        |

| SBIW           | Rdl, K           | Subtract Immediate from Word                                     | $Rdh:RdI \leftarrow Rdh:RdI - K$                                                             | Z,C,N,V,S | 2        |

| SBC            | Rd, Rr           | Subtract with Carry Two Registers                                | $Rd \leftarrow Rd - Rr - C$                                                                  | Z,C,N,V,H | 1        |

| SBCI           | Rd, K            | Subtract with Carry Constant from Reg.                           | $Rd \leftarrow Rd - K - C$                                                                   | Z,C,N,V,H | 1        |

| AND            | Rd, Rr           | Logical AND Registers                                            | $Rd \leftarrow Rd \bullet Rr$                                                                | Z,N,V     | 1        |

| ANDI           | Rd, K            | Logical AND Register and Constant                                | $Rd \gets Rd \bullet K$                                                                      | Z,N,V     | 1        |

| OR             | Rd, Rr           | Logical OR Registers                                             | $Rd \leftarrow Rd \lor Rr$                                                                   | Z,N,V     | 1        |

| ORI            | Rd, K            | Logical OR Register and Constant                                 | $Rd \leftarrow Rd \lor K$                                                                    | Z,N,V     | 1        |

| EOR            | Rd, Rr           | Exclusive OR Registers                                           | $Rd \gets Rd \oplus Rr$                                                                      | Z,N,V     | 1        |

| COM            | Rd               | One's Complement                                                 | $Rd \leftarrow \$FF - Rd$                                                                    | Z,C,N,V   | 1        |

| NEG            | Rd               | Two's Complement                                                 | $Rd \leftarrow \$00 - Rd$                                                                    | Z,C,N,V,H | 1        |

| SBR            | Rd, K            | Set Bit(s) in Register                                           | $Rd \gets Rd \lor K$                                                                         | Z,N,V     | 1        |

| CBR            | Rd, K            | Clear Bit(s) in Register                                         | $Rd \leftarrow Rd \bullet (\$FF - K)$                                                        | Z,N,V     | 1        |

| INC            | Rd               | Increment                                                        | $Rd \leftarrow Rd + 1$                                                                       | Z,N,V     | 1        |

| DEC            | Rd               | Decrement                                                        | $Rd \leftarrow Rd - 1$                                                                       | Z,N,V     | 1        |

| TST            | Rd               | Test for Zero or Minus                                           | $Rd \leftarrow Rd \bullet Rd$                                                                | Z,N,V     | 1        |

| CLR            | Rd               | Clear Register                                                   | $Rd \leftarrow Rd \oplus Rd$                                                                 | Z,N,V     | 1        |

| SER            | Rd               | Set Register                                                     | $Rd \leftarrow FF$                                                                           | None      | 1        |

| BRANCH INSTRU  | CTIONS           |                                                                  |                                                                                              |           |          |

| RJMP           | k                | Relative Jump                                                    | $PC \leftarrow PC + k + 1$                                                                   | None      | 2        |

| IJMP           |                  | Indirect Jump to (Z)                                             | $PC \leftarrow Z$                                                                            | None      | 2        |

| RCALL          | k                | Relative Subroutine Call                                         | $PC \leftarrow PC + k + 1$                                                                   | None      | 3        |

| ICALL          |                  | Indirect Call to (Z)                                             | $PC \leftarrow Z$                                                                            | None      | 3        |

| RET            |                  | Subroutine Return                                                | $PC \leftarrow STACK$                                                                        | None      | 4        |

| RETI           |                  | Interrupt Return                                                 | $PC \leftarrow STACK$                                                                        | 1         | 4        |

| CPSE           | Rd, Rr           | Compare, Skip if Equal                                           | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                                     | None      | 1/2/3    |

| CP             | Rd, Rr           | Compare                                                          | Rd – Rr                                                                                      | Z,N,V,C,H | 1        |

| CPC            | Rd, Rr           | Compare with Carry                                               | Rd – Rr – C                                                                                  | Z,N,V,C,H | 1        |

| CPI            | Rd, K            | Compare Register with Immediate                                  | Rd – K                                                                                       | Z,N,V,C,H | 1        |

| SBRC           | Rr, b            | Skip if Bit in Register Cleared                                  | if $(Rr(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$                                          | None      | 1/2/3    |

| SBRS           | Rr, b            | Skip if Bit in Register is Set                                   | if $(Rr(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$                                          | None      | 1/2/3    |

| SBIC           | P, b             | Skip if Bit in I/O Register Cleared                              | if $(P(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$                                           | None      | 1/2/3    |

| SBIS           | P, b             | Skip if Bit in I/O Register is Set                               | if $(R(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$                                           | None      | 1/2/3    |

| BRBS           | s, k             | Branch if Status Flag Set                                        | if (SREG(s) = 1) then PC $\leftarrow$ PC + k + 1                                             | None      | 1/2      |

| BRBC           | s, k             | Branch if Status Flag Cleared                                    | if (SREG(s) = 0) then PC $\leftarrow$ PC + k + 1                                             | None      | 1/2      |

| BREQ           | k                | Branch if Equal                                                  | if (Z = 1) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRNE           | k                | Branch if Not Equal                                              | if (Z = 0) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRCS           | k                | Branch if Carry Set                                              | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRCC           | k                | Branch if Carry Cleared                                          | if (C = 0) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRSH           | k                | Branch if Same or Higher                                         | if (C = 0) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRLO           | k                | Branch if Lower                                                  | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRMI           | k                | Branch if Minus                                                  | if (N = 1) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRPL           | k                | Branch if Plus                                                   | if (N = 0) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRGE           | k                | Branch if Greater or Equal, Signed                               | if $(N \oplus V = 0)$ then PC $\leftarrow$ PC + k + 1                                        | None      | 1/2      |

| BRLT           | k                | Branch if Less Than Zero, Signed                                 | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1                                        | None      | 1/2      |

| BRHS           | k                | Branch if Half-carry Flag Set                                    | if (H = 1) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRHC           | k                | Branch if Half-carry Flag Cleared                                | if (H = 0) then $PC \leftarrow PC + k + 1$                                                   | None      | 1/2      |

| BRTS           | k                | Branch if T-flag Set                                             | if (T = 1) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRTC           | k                | Branch if T-flag Cleared                                         | if $(T = 0)$ then PC $\leftarrow$ PC + k + 1                                                 | None      | 1/2      |

| BRVS           | k                | Branch if Overflow Flag is Set                                   | if (V = 1) then PC $\leftarrow$ PC + k + 1                                                   | None      | 1/2      |

| BRVC           | k                | Branch if Overflow Flag is Cleared                               |                                                                                              |           | 1/2      |

|                |                  | Branch if Overnow Flag is Cleared<br>Branch if Interrupt Enabled | if $(V = 0)$ then PC $\leftarrow$ PC + k + 1<br>if $(l = 1)$ then PC $\leftarrow$ PC + k + 1 | None      |          |

| BRIE           | k<br>k           | Branch if Interrupt Enabled<br>Branch if Interrupt Disabled      | if (I = 1) then PC $\leftarrow$ PC + k + 1<br>if (I = 0) then PC $\leftarrow$ PC + k + 1     | None      | 1/2      |

### Instruction Set Summary (Continued)

| Mnemonic         | Operands       | Description                      | Operation                                                            | Flags   | # Clocks |

|------------------|----------------|----------------------------------|----------------------------------------------------------------------|---------|----------|

| DATA TRANSFER    | INSTRUCTIONS   |                                  |                                                                      |         | •        |

| MOV              | Rd, Rr         | Move between Registers           | Rd ← Rr                                                              | None    | 1        |

| LDI              | Rd, K          | Load Immediate                   | $Rd \leftarrow K$                                                    | None    | 1        |

| LD               | Rd, X          | Load Indirect                    | $Rd \leftarrow (X)$                                                  | None    | 2        |

| LD               | Rd, X+         | Load Indirect and Post-inc.      | $Rd \leftarrow (X), X \leftarrow X + 1$                              | None    | 2        |

| LD               | Rd, -X         | Load Indirect and Pre-dec.       | $X \leftarrow X - 1$ , Rd $\leftarrow$ (X)                           | None    | 2        |

| LD               | Rd, Y          | Load Indirect                    | $Rd \leftarrow (Y)$                                                  | None    | 2        |

| LD               | Rd, Y+         | Load Indirect and Post-inc.      | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                              | None    | 2        |

| LD               | Rd, -Y         | Load Indirect and Pre-dec.       | $Y \leftarrow Y - 1$ , Rd $\leftarrow$ (Y)                           | None    | 2        |

| LDD              | Rd,Y+q         | Load Indirect with Displacement  | $Rd \leftarrow (Y + q)$                                              | None    | 2        |

| LD               | Rd, Z          | Load Indirect                    | $Rd \leftarrow (Z)$                                                  | None    | 2        |

| LD               | Rd, Z+         | Load Indirect and Post-inc.      | $Rd \leftarrow (Z), Z \leftarrow Z + 1$                              | None    | 2        |

| LD               | Rd, -Z         | Load Indirect and Pre-dec.       | $Z \leftarrow Z - 1$ , $Rd \leftarrow (Z)$                           | None    | 2        |

| LDD              | Rd, Z+q        | Load Indirect with Displacement  | $Rd \leftarrow (Z + q)$                                              | None    | 2        |

| LDS              | Rd, k          | Load Direct from SRAM            | $Rd \leftarrow (k)$                                                  | None    | 2        |

| ST               | X, Rr          | Store Indirect                   | (X) ← Rr                                                             | None    | 2        |

| ST               | X+, Rr         | Store Indirect and Post-inc.     | $(X) \leftarrow \operatorname{Rr}, X \leftarrow X + 1$               | None    | 2        |

| ST               | -X, Rr         | Store Indirect and Pre-dec.      | $X \leftarrow X - 1, (X) \leftarrow Rr$                              | None    | 2        |

| ST               | Y, Rr          | Store Indirect                   | $(Y) \leftarrow Rr$                                                  | None    | 2        |

| ST               | Y+, Rr         | Store Indirect and Post-inc.     | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                              | None    | 2        |

| ST               | -Y, Rr         | Store Indirect and Pre-dec.      | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                              | None    | 2        |

| STD              | Y+q, Rr        | Store Indirect and Fie-dec.      | $(Y + q) \leftarrow Rr$                                              | None    | 2        |

| ST               | Z, Rr          | Store Indirect                   | $(T + q) \leftarrow Rr$                                              | None    | 2        |

| ST               | Z+, Rr         | Store Indirect and Post-inc.     | $(Z) \leftarrow \operatorname{Rr}, Z \leftarrow Z + 1$               | None    | 2        |

| ST               | -Z, Rr         | Store Indirect and Pre-dec.      | $Z \leftarrow Z - 1, (Z) \leftarrow Rr$                              | None    | 2        |

| STD              | Z+q, Rr        | Store Indirect with Displacement |                                                                      | None    | 2        |

| STS              | k, Rr          | Store Direct to SRAM             | $(Z + q) \leftarrow \operatorname{Rr}$                               |         | 2        |

| LPM              | к, пі          | Load Program Memory              | $(k) \leftarrow Rr$                                                  | None    | 3        |

|                  |                |                                  | $R0 \leftarrow (Z)$                                                  | None    |          |

| IN               | Rd, P<br>P, Rr | In Port Out Port                 | $Rd \leftarrow P$                                                    | None    | 1        |

| OUT              |                |                                  | $P \leftarrow Rr$                                                    | None    |          |

| PUSH             | Rr             | Push Register on Stack           |                                                                      | None    | 2        |

| POP              | Rd             | Pop Register from Stack          | $Rd \leftarrow STACK$                                                | None    | 2        |

| BIT AND BIT-TEST |                |                                  |                                                                      |         |          |

| SBI              | P, b           | Set Bit in I/O Register          | $I/O(P,b) \leftarrow 1$                                              | None    | 2        |

| CBI              | P, b           | Clear Bit in I/O Register        | $I/O(P,b) \leftarrow 0$                                              | None    | 2        |

| LSL              | Rd             | Logical Shift Left               | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                       | Z,C,N,V | 1        |

| LSR              | Rd             | Logical Shift Right              | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                       | Z,C,N,V | 1        |

| ROL              | Rd             | Rotate Left through Carry        | $Rd(0) \leftarrow C,  Rd(n+1) \leftarrow Rd(n),  C \leftarrow Rd(7)$ | Z,C,N,V | 1        |

| ROR              | Rd             | Rotate Right through Carry       | $Rd(7) \leftarrow C,  Rd(n) \leftarrow Rd(n+1),  C \leftarrow Rd(0)$ | Z,C,N,V | 1        |

| ASR              | Rd             | Arithmetic Shift Right           | $Rd(n) \leftarrow Rd(n+1), n = 06$                                   | Z,C,N,V | 1        |

| SWAP             | Rd             | Swap Nibbles                     | $Rd(30) \leftarrow Rd(74),  Rd(74) \leftarrow Rd(30)$                | None    | 1        |

| BSET             | s              | Flag Set                         | $SREG(s) \leftarrow 1$                                               | SREG(s) | 1        |

| BCLR             | s              | Flag Clear                       | $SREG(s) \leftarrow 0$                                               | SREG(s) | 1        |

| BST              | Rr, b          | Bit Store from Register to T     | $T \leftarrow Rr(b)$                                                 | Т       | 1        |

| BLD              | Rd, b          | Bit Load from T to Register      | $Rd(b) \leftarrow T$                                                 | None    | 1        |

| SEC              |                | Set Carry                        | C ← 1                                                                | С       | 1        |

| CLC              |                | Clear Carry                      | $C \leftarrow 0$                                                     | С       | 1        |

| SEN              |                | Set Negative Flag                | N ← 1                                                                | N       | 1        |

| CLN              |                | Clear Negative Flag              | N ← 0                                                                | N       | 1        |

| SEZ              |                | Set Zero Flag                    | Z ← 1                                                                | Z       | 1        |

| CLZ              |                | Clear Zero Flag                  | $Z \leftarrow 0$                                                     | Z       | 1        |

| SEI              |                | Global Interrupt Enable          | I ← 1                                                                | 1       | 1        |

| CLI              |                | Global Interrupt Disable         | I ← 0                                                                | 1       | 1        |

| SES              |                | Set Signed Test Flag             | S ← 1                                                                | S       | 1        |

| CLS              |                | Clear Signed Test Flag           | S ← 0                                                                | S       | 1        |

| SEV              |                | Set Two's Complement Overflow    | $V \leftarrow 1$                                                     | V       | 1        |

| CLV              |                | Clear Two's Complement Overflow  | $V \leftarrow 0$                                                     | V       | 1        |

| SET              |                | Set T in SREG                    | T ← 1                                                                | Т       | 1        |

| CLT              |                | Clear T in SREG                  | $T \leftarrow 0$                                                     | Т       | 1        |

| SEH              |                | Set Half-carry Flag in SREG      | H ← 1                                                                | Н       | 1        |

| CLH              |                | Clear Half-carry Flag in SREG    | H ← 0                                                                | Н       | 1        |

| NOP              |                | No Operation                     |                                                                      | None    | 1        |

|                  | 1              | Sleep                            | (see specific descr. for Sleep function)                             | None    | 1        |

| SLEEP            |                | Sleep                            |                                                                      |         |          |

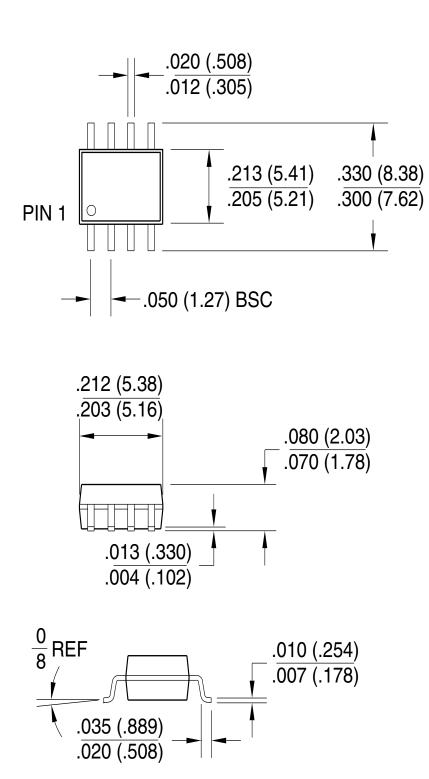

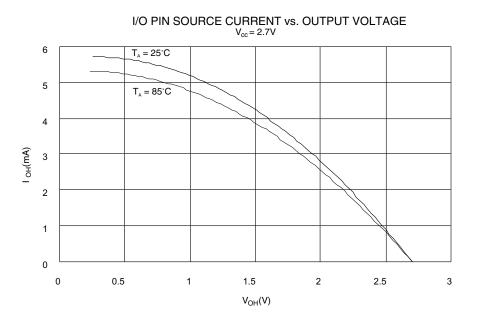

### **Packaging Information**

8P3

REV. A 04/11/2001

8S2