#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessorAVRCore Size8-BitSpeed10MHzConnectivitySPIPeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O5Program Memory Size2KB (1K x 16)Program Memory TypeFLASH |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Core Size8-BitSpeed10MHzConnectivitySPIPeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O5Program Memory Size2KB (1K x 16)                                                                |  |

| Speed10MHzConnectivitySPIPeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O5Program Memory Size2KB (1K x 16)                                                                              |  |

| ConnectivitySPIPeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O5Program Memory Size2KB (1K x 16)                                                                                        |  |

| PeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O5Program Memory Size2KB (1K x 16)                                                                                                       |  |

| Number of I/O5Program Memory Size2KB (1K x 16)                                                                                                                                                  |  |

| Program Memory Size 2KB (1K x 16)                                                                                                                                                               |  |

|                                                                                                                                                                                                 |  |

| Program Memory Type FLASH                                                                                                                                                                       |  |

|                                                                                                                                                                                                 |  |

| EEPROM Size 128 x 8                                                                                                                                                                             |  |

| RAM Size 128 x 8                                                                                                                                                                                |  |

| Voltage - Supply (Vcc/Vdd) 4V ~ 6V                                                                                                                                                              |  |

| Data Converters -                                                                                                                                                                               |  |

| Oscillator Type Internal                                                                                                                                                                        |  |

| Operating Temperature 0°C ~ 70°C                                                                                                                                                                |  |

| Mounting Type Through Hole                                                                                                                                                                      |  |

| Package / Case 8-DIP (0.300", 7.62mm)                                                                                                                                                           |  |

| Supplier Device Package 8-PDIP                                                                                                                                                                  |  |

| Purchase URL https://www.e-xfl.com/product-detail/microch                                                                                                                                       |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

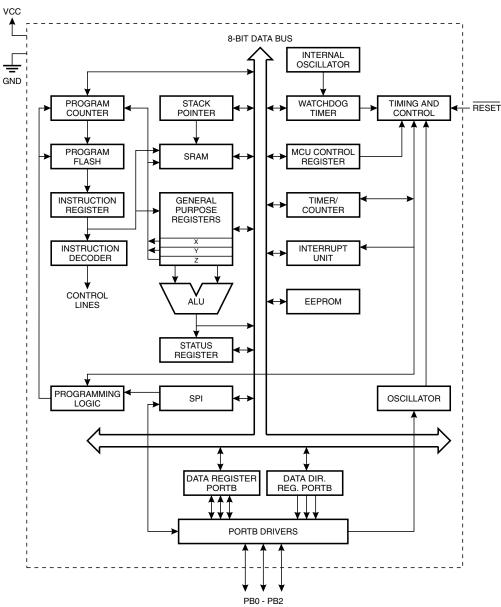

Figure 2. The AT90S/LS2323 Block Diagram

The AT90S2323/2343 provides the following features: 2K bytes of In-System Programmable Flash, 128 bytes EEPROM, 128 bytes SRAM, 3 (AT90S/LS2323)/5 (AT90S/LS2343) general-purpose I/O lines, 32 general-purpose working registers, an 8bit timer/counter, internal and external interrupts, programmable Watchdog Timer with internal oscillator, an SPI serial port for Flash Memory downloading and two softwareselectable power-saving modes. The Idle mode stops the CPU while allowing the SRAM, timer/counters, SPI port and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.

The device is manufactured using Atmel's high-density nonvolatile memory technology. The On-chip Flash allows the program memory to be reprogrammed in-system through an SPI serial interface. By combining an 8-bit RISC CPU with ISP Flash on a monolithic

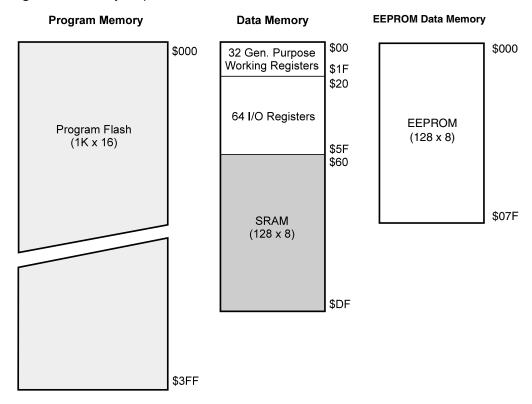

The AVR has Harvard architecture – with separate memories and buses for program and data. The program memory is accessed with a two-stage pipeline. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is in-system downloadable Flash memory.

With the relative jump and call instructions, the whole 1K address space is directly accessed. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the stack. The stack is effectively allocated in the general data SRAM and consequently, the stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the reset routine (before subroutines or interrupts are executed). The 8-bit stack pointer (SP) is read/write-accessible in the I/O space.

The 128 bytes data SRAM + register file and I/O registers can be easily accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

Figure 6. Memory Maps

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the program memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address, the higher the priority.

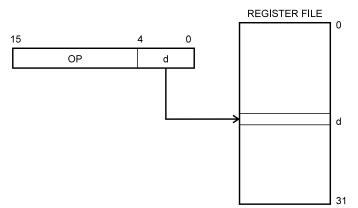

Program and Data Addressing Modes The AT90S2323/2343 AVR RISC microcontroller supports powerful and efficient addressing modes for access to the program memory (Flash) and data memory. This section describes the different addressing modes supported by the AVR architecture. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits.

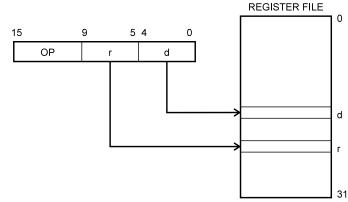

Figure 10. Direct Single Register Addressing

Register Direct, Single Register Rd

**Register Direct, Two Registers** Figure 11. Direct Register Addressing, Two Registers Rd and Rr

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

## AT90S/LS2323/2343

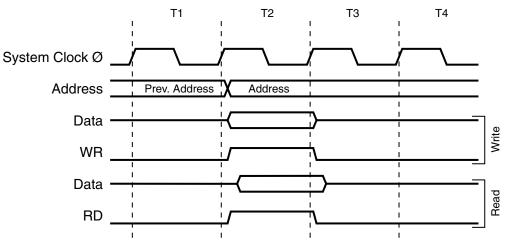

Figure 23. On-chip Data SRAM Access Cycles

#### I/O Memory

The I/O space definition of the AT90S2323/2343 is shown in Table 2.

| Address Hex | Name  | Function                              |

|-------------|-------|---------------------------------------|

| \$3F (\$5F) | SREG  | Status REGister                       |

| \$3D (\$5D) | SPL   | Stack Pointer Low                     |

| \$3B (\$5B) | GIMSK | General Interrupt MaSK register       |

| \$3A (\$5A) | GIFR  | General Interrupt Flag Register       |

| \$39 (\$59) | TIMSK | Timer/Counter Interrupt MaSK register |

| \$38 (\$58) | TIFR  | Timer/Counter Interrupt Flag register |

| \$35 (\$55) | MCUCR | MCU Control Register                  |

| \$34 (\$54) | MCUSR | MCU Status Register                   |

| \$33 (\$53) | TCCR0 | Timer/Counter0 Control Register       |

| \$32 (\$52) | TCNT0 | Timer/Counter0 (8-bit)                |

| \$21 (\$41) | WDTCR | Watchdog Timer Control Register       |

| \$1E (\$3E) | EEAR  | EEPROM Address Register               |

| \$1D (\$3D) | EEDR  | EEPROM Data Register                  |

| \$1C (\$3C) | EECR  | EEPROM Control Register               |

| \$18 (\$38) | PORTB | Data Register, Port B                 |

| \$17 (\$37) | DDRB  | Data Direction Register, Port B       |

| \$16 (\$36) | PINB  | Input Pins, Port B                    |

Table 2. AT90S2323/2343 I/O Space

Note: Reserved and unused locations are not shown in the table.

All AT90S2323/2343 I/Os and peripherals are placed in the I/O space. The I/O locations are accessed by the IN and OUT instructions transferring data between the 32 generalpurpose working registers and the I/O space. I/O registers within the address range \$00 - \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set section for more details. When using the I/O-specific commands IN

and OUT, the I/O addresses \$00 - \$3F must be used. When addressing I/O registers as SRAM, \$20 must be added to these addresses. All I/O register addresses throughout this document are shown with the SRAM address in parentheses.

For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical "1" to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a "1" back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

The I/O and peripherals control registers are explained in the following sections.

Status Register – SREG The AVR Status Register (SREG) at I/O space location \$3F (\$5F) is defined as:

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F)   | I   | Т   | Н   | S   | v   | Ν   | Z   | С   | SREG |

| Read/Write    | R/W | -    |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### • Bit 7 – I: Global Interrupt Enable

The global interrupt enable bit must be set (one) for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the global interrupt enable register is cleared (zero), none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred and is set by the RETI instruction to enable subsequent interrupts.

#### • Bit 6 – T: Bit Copy Storage

The bit copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source and destination for the operated bit. A bit from a register in the register file can be copied into T by the BST instruction and a bit in T can be copied into a bit in a register in the register file by the BLD instruction.

#### • Bit 5 – H: Half-carry Flag

The half-carry flag H indicates a half-carry in some arithmetic operations. See the Instruction Set description for detailed information.

• Bit 4 – S: Sign Bit, S = N ⊕ V

The S-bit is always an exclusive or between the negative flag N and the two's complement overflow flag V. See the Instruction Set description for detailed information.

#### • Bit 3 – V: Two's Complement Overflow Flag

The two's complement overflow flag V supports two's complement arithmetics. See the Instruction Set description for detailed information.

#### • Bit 2 – N: Negative Flag

The negative flag N indicates a negative result from an arithmetical or logical operation. See the Instruction Set description for detailed information.

#### • Bit 1 – Z: Zero Flag

The zero flag Z indicates a zero result from an arithmetical or logical operation. See the Instruction Set description for detailed information.

#### • Bit 0 – C: Carry Flag

The carry flag C indicates a carry in an arithmetical or logical operation. See the Instruction Set description for detailed information.

Note that the Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt routine. This must be handled by software.

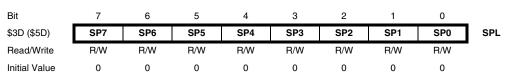

Stack Pointer – SPL An 8-bit register at I/O address \$3D (\$5D) forms the stack pointer of the AT90S2323/2343. Eight bits are used to address the 128 bytes of SRAM in locations \$60 - \$DF.

The Stack Pointer points to the data SRAM stack area where the Subroutine and Interrupt stacks are located. This stack space in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts are enabled. The Stack Pointer must be set to point above \$60. The Stack Pointer is decremented by 1 when data is pushed onto the Stack with the PUSH instruction and it is decremented by 2 when an address is pushed onto the stack with subroutine calls and interrupts. The Stack Pointer is incremented by 1 when data is popped from the stack with the POP instruction and it is incremented by 2 when an address is popped from the stack with return from subroutine RET or return from interrupt RETI.

Reset and InterruptThe AT90S2323/2343 provides two interrupt sources. These interrupts and the separate<br/>reset vector each have a separate program vector in the program memory space. Both<br/>interrupts are assigned individual enable bits that must be set (one) together with the<br/>I-bit in the Status Register in order to enable the interrupt.

The lowest addresses in the program memory space are automatically defined as the Reset and Interrupt vectors. The complete list of vectors is shown in Table 3. The list also determines the priority levels of the interrupts. The lower the address, the higher the priority level. RESET has the highest priority, and next is INT0 (the External Interrupt Request 0), etc.

| Table 3. | Reset and | Interrupt | Vectors |

|----------|-----------|-----------|---------|

|----------|-----------|-----------|---------|

| Vector No. | Program Address | Source       | Interrupt Definition                            |

|------------|-----------------|--------------|-------------------------------------------------|

| 1          | \$000           | RESET        | Hardware Pin, Power-on Reset and Watchdog Reset |

| 2          | \$001           | INT0         | External Interrupt Request 0                    |

| 3          | \$002           | TIMER0, OVF0 | Timer/Counter0 Overflow                         |

# AT90S/LS2323/2343

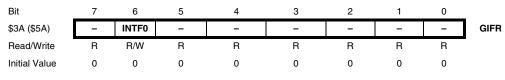

#### General Interrupt Flag Register – GIFR

#### • Bit 7 – Res: Reserved Bit

This bit is a reserved bit in the AT90S2323/2343 and always reads as zero.

#### • Bit 6 – INTF0: External Interrupt Flag0

When an edge on the INTO pin triggers an interrupt request, the corresponding interrupt flag, INTFO becomes set (one). If the I-bit in SREG and the corresponding interrupt enable bit, INTO in GIMSK, is set (one), the MCU will jump to the interrupt vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag is cleared by writing a logical "1" to it. This flag is always cleared when INTO is configured as level interrupt.

#### • Bits 5..0 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read as zero.

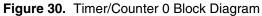

## Timer/Counter Interrupt Mask

Register – TIMSK

| Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0 | _     |

|---------------|---|---|---|---|---|---|-------|---|-------|

| \$39 (\$59)   | - | - | - | - | - | - | TOIE0 | - | TIMSK |

| Read/Write    | R | R | R | R | R | R | R/W   | R | -     |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0 |       |

#### • Bits 7..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read zero.

#### • Bit 1 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt (at vector \$002) is executed if an overflow in Timer/Counter0 occurs, i.e., when the Overflow Flag (Timer/Counter0) is set (one) in the Timer/Counter Interrupt Flag Register (TIFR).

#### • Bit 0 - Res: Reserved Bit

This bit is a reserved bit in the AT90S2323/2343 and always reads as zero.

#### Timer/Counter Interrupt FLAG Register – TIFR

#### • Bits 7..2 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read zero.

#### • Bit 1 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logical "1" to the flag. When the SREG I-bit and TOIE0 (Timer/Counter0 Overflow Interrupt Enable) and TOV0 are set (one), the Timer/Counter0 Overflow Interrupt is executed.

#### • Bit 0 – Res: Reserved Bit

This bit is a reserved bit in the AT90S2323/2343 and always reads zero.

**External Interrupt** The external interrupt is triggered by the INTO pin. Observe that, if enabled, the interrupt will trigger even if the INTO pin is configured as an output. This feature provides a way of generating a software interrupt. The external interrupt can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register (MCUCR). When the external interrupt is enabled and is configured as level-triggered, the interrupt will trigger as long as the pin is held low.

The external interrupt is set up as described in the specification for the MCU Control Register (MCUCR).

Interrupt Response Time The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. Four clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During these four clock cycles, the Program Counter (2 bytes) is popped back from the stack, the Stack Pointer is incremented by 2 and the I-flag in SREG is set. The vector is a relative jump to the interrupt routine and this jump takes two clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes four clock cycles. During these four clock cycles, the Program Counter (2 bytes) is popped back from the stack and the Stack Pointer is incremented by 2. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

MCU Control Register – MCUCR The MCU Control Register contains control bits for general MCU functions.

| Bit           | 7 | 6 | 5   | 4   | 3 | 2 | 1     | 0     | _     |

|---------------|---|---|-----|-----|---|---|-------|-------|-------|

| \$35 (\$55)   | - | - | SE  | SM  | - | - | ISC01 | ISC00 | MCUCR |

| Read/Write    | R | R | R/W | R/W | R | R | R/W   | R/W   |       |

| Initial Value | 0 | 0 | 0   | 0   | 0 | 0 | 0     | 0     |       |

#### • Bits 7, 6 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read as zero.

#### • Bit 5 – SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the Sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the Sleep mode, unless it is the programmer's purpose, it is recommended to set the Sleep Enable (SE) bit just before the execution of the SLEEP instruction.

#### • Bit 4 – SM: Sleep Mode

This bit selects between the two available sleep modes. When SM is cleared (zero), Idle mode is selected as Sleep mode. When SM is set (one), Power-down mode is selected as sleep mode. For details, refer to the section "Sleep Modes".

• Bits 3, 2 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read as zero.

#### • Bits 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-flag and the corresponding interrupt mask are set. The level and edges on the external INT0 pin that

activate the interrupt are defined in Table 9. The value on the INT01 pin is sampled before detecting edges. If edge or toggle interrupt is selected, pulses that last longer than one clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low-level interrupt is selected, the low level must be held until the completion of the currently executing instruction to generate an interrupt.

| ISC01 | ISC00 | Description                                              |

|-------|-------|----------------------------------------------------------|

| 0     | 0     | The low level of INT0 generates an interrupt request.    |

| 0     | 1     | Reserved                                                 |

| 1     | 0     | The falling edge of INT0 generates an interrupt request. |

| 1     | 1     | The rising edge of INT0 generates an interrupt request.  |

**Sleep Modes** To enter the sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruction must be executed. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU awakes, executes the interrupt routine and resumes execution from the instruction following SLEEP. The contents of the register file, SRAM and I/O memory are unaltered. If a reset occurs during Sleep mode, the MCU wakes up and executes from the Reset vector.

Idle Mode When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle mode, stopping the CPU but allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like Timer Overflow interrupt and Watchdog reset.

**Power-down Mode** When the SM bit is set (one), the SLEEP instruction forces the MCU into the Powerdown mode. In this mode, the external oscillator is stopped while the external interrupts and the Watchdog (if enabled) continue operating. Only an external reset, a Watchdog reset (if enabled), or an external level interrupt on INTO can wake up the MCU.

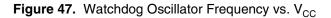

Note that if a level-triggered interrupt is used for wake-up from Power-down mode, the changed level must be held for some time to wake up the MCU. This makes the MCU less sensitive to noise. The changed level is sampled twice by the Watchdog oscillator clock and if the input has the required level during this time, the MCU will wake up. The period of the Watchdog oscillator is 1 µs (nominal) at 5.0V and 25°C. The frequency of the Watchdog oscillator is voltage-dependent as shown in section "Typical Characteristics" on page 49.

When waking up from Power-down mode, a delay from the wake-up condition occurs until the wake-up becomes effective. This allows the clock to restart and become stable after having been stopped. The wake-up period is equal to the clock reset period, as shown in Table 4 and Table 5 on page 21.

If the wake-up condition disappears before the MCU wakes up and starts to execute, e.g., a low-level on is not held long enough, the interrupt causing the wake-up will not be executed.

• Bits 7..3 - Res: Reserved Bits

These bits are reserved bits in the AT90S2323/2343 and always read zero.

#### • Bits 2, 1, 0 – CS02, CS01, CS00: Clock Select0, Bits 2, 1 and 0

The Clock Select0 bits 2, 1 and 0 define the prescaling source of Timer/Counter0.

Table 10. Clock 0 Prescale Select

| CS02 | CS01 | CS00 | Description                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Stop, the Timer/Counter0 is stopped. |

| 0    | 0    | 1    | СК                                   |

| 0    | 1    | 0    | CK/8                                 |

| 0    | 1    | 1    | CK/64                                |

| 1    | 0    | 0    | CK/256                               |

| 1    | 0    | 1    | CK/1024                              |

| 1    | 1    | 0    | External Pin T0, falling edge        |

| 1    | 1    | 1    | External Pin T0, rising edge         |

Timer/Counter0 Control Register – TCCR0

# Port B Input Pins Address – PINB

| Bit           | 7 | 6 | 5 | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|---|---|---|-------|-------|-------|-------|-------|------|

| \$16 (\$36)   | - | - | - | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write    | R | R | R | R     | R     | R     | R     | R     |      |

| Initial Value | 0 | 0 | 0 | N/A   | N/A   | N/A   | N/A   | N/A   |      |

The Port B Input Pins address (PINB) is not a register and this address enables access to the physical value on each Port B pin. When reading PORTB, the Port B Data Latch is read and when reading PINB, the logical values present on the pins are read.

# **Port B as General Digital** All pins in port B have equal functionality when used as digital I/O pins.

PBn, general I/O pin: The DDBn bit in the DDRB register selects the direction of this pin, if DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero), PBn is configured as an input pin. If PORTBn is set (one) when the pin is configured as an input pin, the MOS pull-up resistor is activated. To switch the pull-up resistor off, the PORTBn has to be cleared (zero) or the pin has to be configured as an output pin. The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.

| DDBn | PORTBn | I/O    | Pull-up | Comment                                    |  |  |  |  |  |  |

|------|--------|--------|---------|--------------------------------------------|--|--|--|--|--|--|

| 0    | 0      | Input  | No      | Tri-state (high-Z)                         |  |  |  |  |  |  |

| 0    | 1      | Input  | Yes     | PBn will source current if ext. pulled low |  |  |  |  |  |  |

| 1    | 0      | Output | No      | Push-pull Zero Output                      |  |  |  |  |  |  |

| 1    | 1      | Output | No      | Push-pull One Output                       |  |  |  |  |  |  |

Table 13. DDBn Effects on Port B Pins

Alternate Functions of Port B

**B** The alternate pin functions of Port B are as follows:

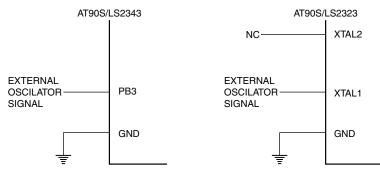

#### • CLOCK – Port B, Bit 3

Clock input: AT90S/LS2343 only. When the RCEN fuse is programmed and the device runs from the internal RC oscillator, this pin is a general I/O pin. When the RCEN fuse is unprogrammed, an external clock source must be connected to CLOCK.

#### • SCK/T0 – Port B, Bit 2

In Serial Programming mode, this bit serves as the serial clock input, SCK.

During normal operation, this pin can serve as the external counter clock input. See the timer/counter description for further details. If external timer/counter clocking is selected, activity on this pin will clock the counter even if it is configured as an output.

#### • MISO/INT0 - Port B, Bit 1

In Serial Programming mode, this bit serves as the serial data output, MISO.

During normal operation, this pin can serve as the external interrupt0 input. See the interrupt description for details on how to enable this interrupt. Note that activity on this pin will trigger the interrupt even if the pin is configured as an output.

#### • MOSI – Port B, Bit 0

In Serial Programming mode, this pin serves as the serial data input, MOSI.

# AT90S/LS2323/2343

|                                              | Instruction Format                  |                    |                   |                  |                                                                                                           |  |

|----------------------------------------------|-------------------------------------|--------------------|-------------------|------------------|-----------------------------------------------------------------------------------------------------------|--|

| Instruction                                  | ruction Byte 1 Byte 2 Byte 3 Byte 4 |                    | Byte 4            | Operation        |                                                                                                           |  |

| Programming<br>Enable                        | 1010 1100                           | 0101 0011          | XXXX XXXX         | XXXX XXXX        | Enable Serial programming while RESET is low.                                                             |  |

| Chip Erase                                   | 1010 1100                           | 100x xxxx          | XXXX XXXX         | XXXX XXXX        | Chip erase both Flash and<br>EEPROM memory arrays.                                                        |  |

| Read Program<br>Memory                       | 0010 <b>H</b> 000                   | 0000 00 <b>aa</b>  | bbbb bbbb         | 0000 0000        | Read <b>H</b> (high or low) data <b>o</b> from<br>program memory at word address<br><b>a</b> : <b>b</b> . |  |

| Write Program<br>Memory                      | 0100 <b>H</b> 000                   | 0000 00 <b>aa</b>  | bbbb bbbb         | <b>iiii iiii</b> | Write <b>H</b> (high or low) data <b>i</b> to program memory at word address <b>a</b> : <b>b</b> .        |  |

| Read<br>EEPROM Memory                        | 1010 0000                           | 0000 0000          | xbbb bbbb         | 0000 0000        | Read data <b>o</b> from EEPROM memory at address <b>b</b> .                                               |  |

| Write<br>EEPROM Memory                       | 1100 0000                           | 0000 0000          | xbbb bbbb         | 1111 1111        | Write data <b>i</b> to EEPROM memory at address <b>b</b> .                                                |  |

| Read Lock and<br>Fuse Bits<br>(AT90S/LS2323) | 0101 1000                           | XXXX XXXX          | XXXX XXXX         | 12Sx xxxF        | Read Lock and Fuse bits.<br>"0" = programmed,<br>"1" = unprogrammed                                       |  |

| Read Lock and<br>Fuse Bits<br>(AT90S/LS2343) | 0101 1000                           | XXXX XXXX          | XXXX XXXX         | 12Sx xxxR        | Read Lock and Fuse bits.<br>"0" = programmed,<br>"1" = unprogrammed                                       |  |

| Write Lock Bits                              | 1010 1100                           | 1111 1 <b>21</b> 1 | XXXX XXXX         | XXXX XXXX        | Write Lock bits. Set bits <b>1</b> , <b>2</b> = "0" to program Lock bits.                                 |  |

| Write FSTRT Bit<br>(AT90S/LS2323)            | 1010 1100                           | 1011 111 <b>F</b>  | XXXX XXXX         | XXXX XXXX        | Write FSTRT fuse. Set bit <b>F</b> = "0" to program, "1" to unprogram. <sup>(2)</sup>                     |  |

| Write RCEN Bit<br>(AT90S/LS2343)             | 1010 1100                           | 1011 111 <b>R</b>  | XXXX XXXX         | xxxx xxxx        | Write RCEN Fuse. Set bit <b>R</b> = '0' to program, '1' to unprogram. <sup>(2)</sup>                      |  |

| Read Signature<br>Bytes                      | 0011 0000                           | XXXX XXXX          | xxxx xx <b>bb</b> | 0000 0000        | Read signature byte <b>o</b> from address <b>b</b> . <sup>(3)</sup>                                       |  |

| Table 19. | Low-voltage Seria | I Programming Instruc | tion Set AT90S2323/2343 |

|-----------|-------------------|-----------------------|-------------------------|

|           |                   |                       |                         |

Notes: 1. **a** = address high bits

**b** = address low bits

$\mathbf{H} = 0 - \text{Low byte}, 1 - \text{High byte}$

$\mathbf{o} = data \ out$

$\mathbf{i} = data in$

- x = don't care

- **1** = lock bit 1

- **2** = lock bit 2

- **F** = FSTRT Fuse **R** = RCEN Fuse

- $\mathbf{S} = \text{SPIEN Fuse}$

2. When the state of the RCEN/FSTRT bit is changed, the device must be power cycled for the changes to have any effect.

3. The signature bytes are not readable in Lock mode 3, i.e., both Lock bits programmed.

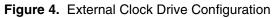

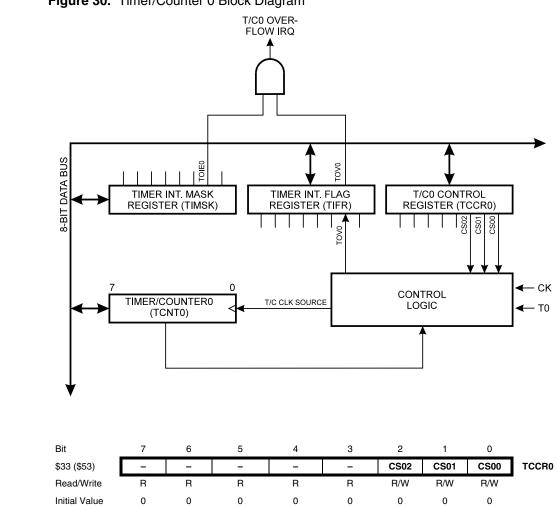

### **External Clock Drive Waveforms**

### **External Clock Drive**

| $T_A =$ | -40°C to | 85°C |

|---------|----------|------|

|---------|----------|------|

|                     |                      | V <sub>cc</sub> : 2.7V to 4.0V |     | V <sub>cc</sub> : 4.0V to 6.0V |      |       |

|---------------------|----------------------|--------------------------------|-----|--------------------------------|------|-------|

| Symbol              | Parameter            | Min                            | Max | Min                            | Max  | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                              | 4.0 | 0                              | 10.0 | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 250.0                          |     | 100.0                          |      | ns    |

| t <sub>CHCX</sub>   | High Time            | 100.0                          |     | 40.0                           |      | ns    |

| t <sub>CLCX</sub>   | Low Time             | 100.0                          |     | 40.0                           |      | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                                | 1.6 |                                | 0.5  | μs    |

| t <sub>CHCL</sub>   | Fall Time            |                                | 1.6 |                                | 0.5  | μs    |

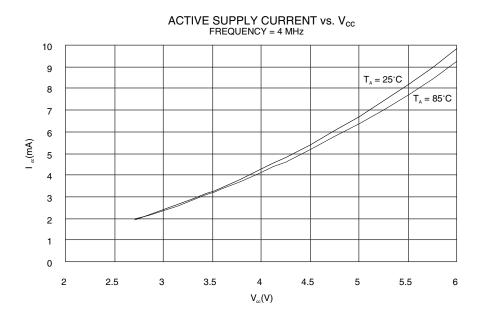

Figure 40. Active Supply Current vs. V<sub>CC</sub>

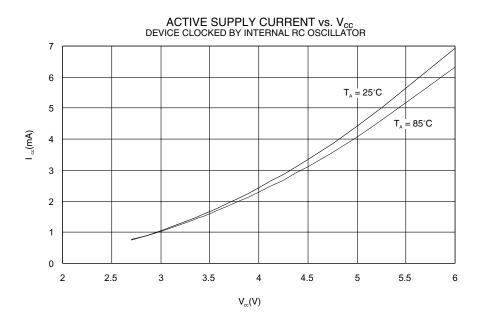

Figure 41. Active Supply Current vs. V<sub>CC</sub>

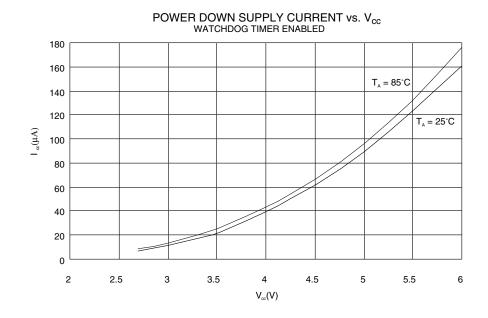

Figure 46. Power-down Supply Current vs. V<sub>CC</sub>

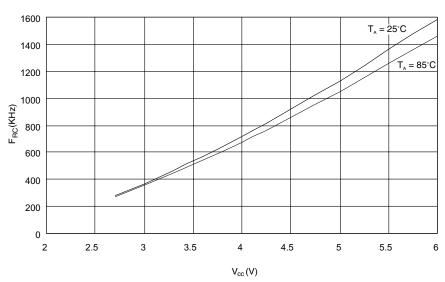

WATCHDOG OSCILLATOR FREQUENCY vs.  $V_{cc}$

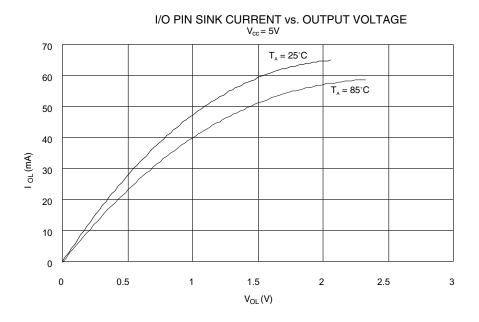

Figure 50. I/O Pin Sink Current vs. Output Voltage

## **Ordering Information**

| Power Supply | Speed (MHz) | Ordering Code  | Package | Operation Range |

|--------------|-------------|----------------|---------|-----------------|

| 2.7 - 6.0V   | 4           | AT90LS2323-4PC | 8P3     | Commercial      |

|              |             | AT90LS2323-4SC | 8S2     | (0°C to 70°C)   |

|              |             | AT90LS2323-4PI | 8P3     | Industrial      |

|              |             | AT90LS2323-4SI | 8S2     | (-40°C to 85°C) |

| 4.0 - 6.0V   | 10          | AT90S2323-10PC | 8P3     | Commercial      |

|              |             | AT90S2323-10SC | 8S2     | (0°C to 70°C)   |

|              |             | AT90S2323-10PI | 8P3     | Industrial      |

|              |             | AT90S2323-10SI | 8S2     | (-40°C to 85°C) |

| 2.7 - 6.0V   | 1           | AT90LS2343-1PC | 8P3     | Commercial      |

|              |             | AT90LS2343-1SC | 8S2     | (0°C to 70°C)   |

|              |             | AT90LS2343-1PI | 8P3     | Industrial      |

|              |             | AT90LS2343-1SI | 8S2     | (-40°C to 85°C) |

| 2.7 - 6.0V   | 4           | AT90LS2343-4PC | 8P3     | Commercial      |

|              |             | AT90LS2343-4SC | 8S2     | (0°C to 70°C)   |

|              |             | AT90LS2343-4PI | 8P3     | Industrial      |

|              |             | AT90LS2343-4SI | 8S2     | (-40°C to 85°C) |

| 4.0 - 6.0V   | 10          | AT90S2343-10PC | 8P3     | Commercial      |

|              |             | AT90S2343-10SC | 8S2     | (0°C to 70°C)   |

|              |             | AT90S2343-10PI | 8P3     | Industrial      |

|              |             | AT90S2343-10SI | 8S2     | (-40°C to 85°C) |

Notes: 1. The speed grade refers to maximum clock rate when using an external crystal or external clock drive. The internal RC oscillator has the same nominal clock frequency for all speed grades.

2. In AT90LS2343-1xx, the internal RC oscillator is selected as default MCU clock source (RCEN fuse is programmed) when the device is shipped from Atmel. In AT90LS2343-4xx and AT90S2343-10xx, the default MCU clock source is the clock input pin (RCEN fuse is unprogrammed). The fuse settings can be changed by high voltage serial programming.

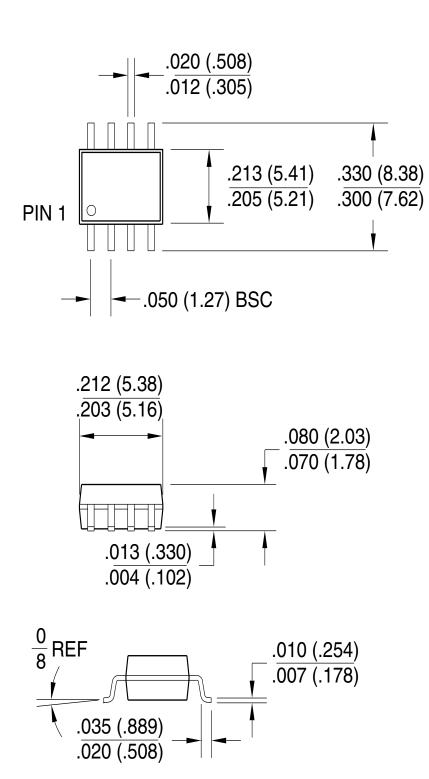

|     | Package Type                                                             |

|-----|--------------------------------------------------------------------------|

| 8P3 | 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                  |

| 8S2 | 8-lead, 0.200" Wide, Plastic Gull Wing Small Outline Package (EIAJ SOIC) |

8S2

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Product Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

#### Atmel Heilbronn

Theresienstrasse 2 POB 3535 D-74025 Heilbronn, Germany TEL (49) 71 31 67 25 94 FAX (49) 71 31 67 24 23

#### Atmel Nantes

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 0 2 40 18 18 18 FAX (33) 0 2 40 18 19 60

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

#### Atmel Smart Card ICs

Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-357-000 FAX (44) 1355-242-743

> *e-mail* literature@atmel.com

> Web Site http://www.atmel.com

BBS 1-(408) 436-4309

#### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® and AVR® are the registered trademarks of Atmel.

Other terms and product names may be the trademarks of others.