Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | e200z0h                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | DMA, POR, PWM, WDT                                                    |

| Number of I/O              | 121                                                                   |

| Program Memory Size        | 768KB (768K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 64K x 8                                                               |

| RAM Size                   | 64K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                             |

| Data Converters            | A/D 15x10b, 5x12b                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LQFP                                                              |

| Supplier Device Package    | 144-LQFP (20x20)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/ppc5605bclq48 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Block diagram

Table 2 summarizes the functions of the blocks present on the MPC5607B.

| Block                                                         | Function                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                             | Converts analog voltages to digital values                                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                                      | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                                 |

| Clock generation module<br>(MC_CGM)                           | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                                     |

| Clock monitor unit (CMU)                                      | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                                    |

| Cross triggering unit (CTU)                                   | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                               |

| Crossbar switch (XBAR)                                        | Supports simultaneous connections between two master ports and three slave ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus width.                                                                                                                                                            |

| Deserial serial peripheral interface (DSPI)                   | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                            |

| Enhanced Direct Memory Access<br>(eDMA)                       | Performs complex data transfers with minimal intervention from a host processor via " <i>n</i> " programmable channels                                                                                                                                                                                                     |

| Enhanced modular input output system (eMIOS)                  | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                                   |

| Error Correction Status Module<br>(ECSM)                      | Provides a myriad of miscellaneous control functions for the device including<br>program-visible information about configuration and revision levels, a reset status<br>register, wakeup control for exiting sleep modes, and optional features such as<br>information on memory errors reported by error-correcting codes |

| Flash memory                                                  | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                                    |

| FlexCAN (controller area network)                             | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                          |

| Frequency-modulated<br>phase-locked loop (FMPLL)              | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                          |

| Inter-integrated circuit (I <sup>2</sup> C <sup>™</sup> ) bus | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                           |

| Internal multiplexer (IMUX) SIU subblock                      | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                                        |

| Interrupt controller (INTC)                                   | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                                        |

| JTAG controller (JTAGC)                                       | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                           |

| LINFlex controller                                            | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                         |

| Memory protection unit (MPU)                                  | Provides hardware access control for all memory references generated in a device                                                                                                                                                                                                                                           |

| Mode entry module (MC_ME)                                     | Provides a mechanism for controlling the device operational mode and<br>modetransition sequences in all functional states; also manages the power<br>control unit, reset generation module and clock generation module, and holds the<br>configuration, control and status registers accessible for applications           |

#### Package pinouts and signal descriptions

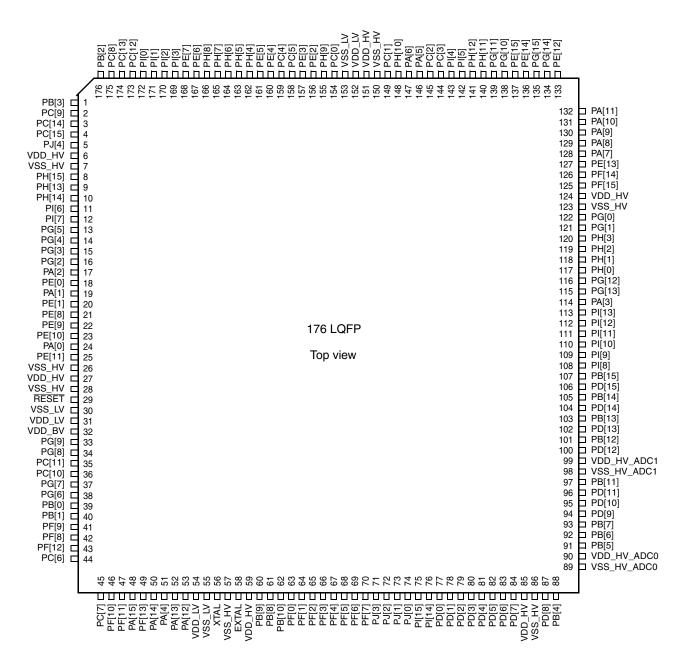

Figure 2 shows the MPC5607B in the 176 LQFP package.

Figure 2. 176 LQFP pin configuration

| Port pin  | Function                                                             | Pin number |          |          |            |  |  |

|-----------|----------------------------------------------------------------------|------------|----------|----------|------------|--|--|

| i ort pin |                                                                      | 100 LQFP   | 144 LQFP | 176 LQFP | 208 MAPBGA |  |  |

|           | Reference voltage and analog supply for the A/D converter 1 (12-bit) | 60         | 82       | 99       | K13        |  |  |

Table 3. Voltage supply pin descriptions (continued)

A decoupling capacitor must be placed between each of the three VDD\_LV/VSS\_LV supply pairs to ensure stable voltage (see the recommended operating conditions in the device data sheet).

# 3.5 Pad types

In the device the following types of pads are available for system pins and functional port pins:

$S = Slow^1$

$M = Medium^{1 2}$

$F = Fast^{1 2}$

- $I = Input only with analog feature^{1}$

- J = Input/Output ('S' pad) with analog feature

X = Oscillator

# 3.6 System pins

The system pins are listed in Table 4.

|          |                                                                                                                                                                                       | direction | type   | RESET                                                              | Pin number  |             |             |                             |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|--------------------------------------------------------------------|-------------|-------------|-------------|-----------------------------|--|--|

| Port pin | Function                                                                                                                                                                              |           | Pad ty | configuration                                                      | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP | 208 MAP<br>BGA <sup>1</sup> |  |  |

| RESET    | Bidirectional reset with Schmitt-Trigger characteristics and noise filter.                                                                                                            | I/O       | М      | Input weak<br>pull-up after<br>RGM PHASE2<br>and 40 FIRC<br>cycles | 17          | 21          | 29          | J1                          |  |  |

| EXTAL    | Analog output of the oscillator<br>amplifier circuit, when the oscillator is<br>not in bypass mode.<br>Analog input for the clock generator<br>when the oscillator is in bypass mode. | I/O       | Х      | Tristate                                                           | 36          | 50          | 58          | N8                          |  |  |

| XTAL     | Analog input of the oscillator amplifier circuit. Needs to be grounded if oscillator bypass mode is used.                                                                             | Ι         | Х      | Tristate                                                           | 34          | 48          | 56          | P8                          |  |  |

Table 4. System pin descriptions

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

<sup>1.</sup> See the I/O pad electrical characteristics in the chip data sheet for details.

<sup>2.</sup> All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium. The only exception is PC[1] which is in medium configuration by default (see the PCR.SRC description in the chip reference manual, Pad Configuration Registers (PCR0–PCR148)).

|          |         | tion <sup>1</sup>                                      |                                                                    |                                                                     | 2                                            |          | n <sup>3</sup>                      |             | Pin nu      | umber       |                                |

|----------|---------|--------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------|----------|-------------------------------------|-------------|-------------|-------------|--------------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>                        | Function                                                           | Peripheral                                                          | I/O direction <sup>2</sup>                   | Pad type | RESET<br>configuration <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP | 208<br>MAP<br>BGA <sup>4</sup> |

| PA[7]    | PCR[7]  | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[7]<br>E0UC[7]<br>LIN3TX<br>—<br>EIRQ[2]<br>ADC1_S[1]          | SIUL<br>eMIOS_0<br>LINFlex_3<br><br>SIUL<br>ADC_1                   | I/O<br>I/O<br>O<br>I<br>I<br>I               | J        | Tristate                            | 71          | 104         | 128         | D16                            |

| PA[8]    | PCR[8]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>N/A <sup>7</sup><br>— | GPIO[8]<br>EOUC[8]<br>EOUC[14]<br>—<br>EIRQ[3]<br>ABS[0]<br>LIN3RX | SIUL<br>eMIOS_0<br>eMIOS_0<br>—<br>SIUL<br>BAM<br>LINFlex_3         | /0<br> /0<br> /0<br> -<br> -<br> -           | S        | Input,<br>weak<br>pull-up           | 72          | 105         | 129         | C16                            |

| PA[9]    | PCR[9]  | AF0<br>AF1<br>AF2<br>AF3<br>N/A <sup>7</sup>           | GPIO[9]<br>E0UC[9]<br>—<br>CS2_1<br>FAB                            | SIUL<br>eMIOS_0<br><br>DSPI_1<br>BAM                                | I/O<br>I/O<br>—<br>0<br>I                    | S        | Pull-<br>down                       | 73          | 106         | 130         | C15                            |

| PA[10]   | PCR[10] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[10]<br>E0UC[10]<br>SDA<br>LIN2TX<br>ADC1_S[2]                 | SIUL<br>eMIOS_0<br>I <sup>2</sup> C_0<br>LINFlex_2<br>ADC_1         | I/O<br>I/O<br>I/O<br>I                       | J        | Tristate                            | 74          | 107         | 131         | B16                            |

| PA[11]   | PCR[11] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>—                | GPIO[11]<br>E0UC[11]<br>SCL<br>EIRQ[16]<br>LIN2RX<br>ADC1_S[3]     | SIUL<br>eMIOS_0<br>I <sup>2</sup> C_0<br>SIUL<br>LINFlex_2<br>ADC_1 | I/O<br>I/O<br>I/O<br>I/O<br>I<br>I<br>I<br>I | J        | Tristate                            | 75          | 108         | 132         | B15                            |

| PA[12]   | PCR[12] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[12]<br>—<br>E0UC[28]<br>CS3_1<br>EIRQ[17]<br>SIN_0            | SIUL<br>—<br>eMIOS_0<br>DSPI_1<br>SIUL<br>DSPI_0                    | ½     ½ 0  −  −                              | S        | Tristate                            | 31          | 45          | 53          | T7                             |

| PA[13]   | PCR[13] | AF0<br>AF1<br>AF2<br>AF3                               | GPIO[13]<br>SOUT_0<br>E0UC[29]<br>—                                | SIUL<br>DSPI_0<br>eMIOS_0<br>—                                      | I/O<br>O<br>I/O<br>—                         | М        | Tristate                            | 30          | 44          | 52          | R7                             |

| Table 5. Functional port pi    | n descriptions (continued) |

|--------------------------------|----------------------------|

| iable et l'alletterlai pert pi |                            |

|          |         | ion <sup>1</sup>                   |                                                | 2                                |                            |          | n <sup>3</sup>                      |             | Pin n       | umber       |                                |

|----------|---------|------------------------------------|------------------------------------------------|----------------------------------|----------------------------|----------|-------------------------------------|-------------|-------------|-------------|--------------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>    | Function                                       | Peripheral                       | I/O direction <sup>2</sup> | Pad type | RESET<br>configuration <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP | 208<br>MAP<br>BGA <sup>4</sup> |

| PD[2]    | PCR[50] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[50]<br>—<br>—<br>ADC0_P[6]<br>ADC1_P[6]   | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | -                          | Ι        | Tristate                            | 43          | 65          | 79          | R12                            |

| PD[3]    | PCR[51] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[51]<br>—<br>—<br>ADC0_P[7]<br>ADC1_P[7]   | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> -<br> <br>            | I        | Tristate                            | 44          | 66          | 80          | P13                            |

| PD[4]    | PCR[52] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[52]<br>—<br>—<br>ADC0_P[8]<br>ADC1_P[8]   | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> <br> <br>             | Ι        | Tristate                            | 45          | 67          | 81          | R13                            |

| PD[5]    | PCR[53] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[53]<br>—<br>—<br>ADC0_P[9]<br>ADC1_P[9]   | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> <br> <br>             | Ι        | Tristate                            | 46          | 68          | 82          | T13                            |

| PD[6]    | PCR[54] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[54]<br>—<br>—<br>ADC0_P[10]<br>ADC1_P[10] | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> <br> <br>             | Ι        | Tristate                            | 47          | 69          | 83          | T14                            |

| PD[7]    | PCR[55] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[55]<br>—<br>—<br>ADC0_P[11]<br>ADC1_P[11] | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | -                          | Ι        | Tristate                            | 48          | 70          | 84          | R14                            |

| PD[8]    | PCR[56] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[56]<br>—<br>—<br>ADC0_P[12]<br>ADC1_P[12] | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> -<br> <br>            | Ι        | Tristate                            | 49          | 71          | 87          | T15                            |

#### Table 8. PAD3V5V field description<sup>1</sup>

| Value <sup>2</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

<sup>1</sup> See the device reference manual for more information on the NVUSRO register.

<sup>2</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

# 4.2.2 NVUSRO[OSCILLATOR\_MARGIN] field description

The fast external crystal oscillator consumption is dependent on the OSCILLATOR\_MARGIN bit value. Table 9 shows how NVUSRO[OSCILLATOR\_MARGIN] controls the device configuration.

#### Table 9. OSCILLATOR\_MARGIN field description<sup>1</sup>

| Value <sup>2</sup> | Description                                 |

|--------------------|---------------------------------------------|

| 0                  | Low consumption configuration (4 MHz/8 MHz) |

| 1                  | High margin configuration (4 MHz/16 MHz)    |

<sup>1</sup> See the device reference manual for more information on the NVUSRO register.

<sup>2</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

# 4.2.3 NVUSRO[WATCHDOG\_EN] field description

The watchdog enable/disable configuration after reset is dependent on the WATCHDOG\_EN bit value. Table 10 shows how NVUSRO[WATCHDOG\_EN] controls the device configuration.

#### Table 10. WATCHDOG\_EN field description

| Value <sup>1</sup> | Description         |

|--------------------|---------------------|

| 0                  | Disable after reset |

| 1                  | Enable after reset  |

<sup>1</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

# 4.3 Absolute maximum ratings

#### Table 11. Absolute maximum ratings

| Symbo              | 1                                    | Parameter                                                                                     | Conditions                  | Va                    | lue                   | Unit |

|--------------------|--------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------|-----------------------|-----------------------|------|

| Symbo              | 'I                                   | i arameter                                                                                    | Conditions                  | Min                   | Мах                   | onne |

| V <sub>SS</sub>    | SR                                   | Digital ground on VSS_HV pins                                                                 | —                           | 0                     | 0                     | V    |

| V <sub>DD</sub>    |                                      | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                              | —                           | -0.3                  | 6.0                   | V    |

| V <sub>SS_LV</sub> |                                      | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | —                           | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| V <sub>DD_BV</sub> |                                      | Voltage on VDD_BV (regulator supply) pin with                                                 | —                           | -0.3                  | 6.0                   | V    |

|                    | respect to ground (V <sub>SS</sub> ) |                                                                                               | Relative to V <sub>DD</sub> | -0.3                  | V <sub>DD</sub> + 0.3 |      |

# 4.5 Thermal characteristics

## 4.5.1 External ballast resistor recommendations

External ballast resistor on  $V_{DD_BV}$  pin helps in reducing the overall power dissipation inside the device. This resistor is required only when maximum power consumption exceeds the limit imposed by package thermal characteristics.

As stated in Table 14 LQFP thermal characteristics, considering a thermal resistance of 144 LQFP as 48.3 °C/W, at ambient temperature  $T_A = 125$  °C, the junction temperature  $T_j$  will cross 150 °C if the total power dissipation is greater than (150 - 125)/48.3 = 517 mW. Therefore, the total device current  $I_{DDMAX}$  at 125 °C/5.5 V must not exceed 94.1 mA (i.e., PD/VDD). Assuming an average  $I_{DD}(V_{DD_{HV}})$  of 15–20 mA consumption typically during device RUN mode, the LV domain consumption  $I_{DD}(V_{DD_{BV}})$  is thus limited to  $I_{DDMAX} - I_{DD}(V_{DD_{HV}})$ , i.e., 80 mA.

Therefore, respecting the maximum power allowed as explained in Section 4.5.2, "Package thermal characteristics, it is recommended to use this resistor only in the 125 °C/5.5 V operating corner as per the following guidelines:

- If  $I_{DD}(V_{DD BV}) < 80$  mA, then no resistor is required.

- If 80 mA  $< I_{DD}(V_{DD BV}) < 90$  mA, then 4  $\Omega$  resistor can be used.

- If  $I_{DD}(V_{DD BV}) > 90$  mA, then 8  $\Omega$  resistor can be used.

Using resistance in the range of 4–8  $\Omega$ , the gain will be around 10–20% of total consumption on V<sub>DD\_BV</sub>. For example, if 8  $\Omega$  resistor is used, then power consumption when I<sub>DD</sub>(V<sub>DD\_BV</sub>) is 110 mA is equivalent to power consumption when I<sub>DD</sub>(V<sub>DD\_BV</sub>) is 90 mA (approximately) when resistor not used.

In order to ensure correct power up, the minimum  $V_{DD_BV}$  to be guaranteed is 30 ms/V. If the supply ramp is slower than this value, then LVDHV3B monitoring ballast supply  $V_{DD_BV}$  pin gets triggered leading to device reset. Until the supply reaches certain threshold, this low voltage detector (LVD) generates destructive reset event in the system. This threshold depends on the maximum  $I_{DD}(V_{DD_BV})$  possible across the external resistor.

# 4.5.2 Package thermal characteristics

#### Table 14. LQFP thermal characteristics<sup>1</sup>

| Symb            |    | С | Parameter                                           | Conditions <sup>2</sup> | Pin count |     | •   | Unit |      |

|-----------------|----|---|-----------------------------------------------------|-------------------------|-----------|-----|-----|------|------|

| Synn            |    | C | Falanciel                                           | Conditions              |           | Min | Тур | Max  | Onit |

| $R_{\theta JA}$ | СС | D | Thermal resistance,                                 | Single-layer board — 1s | 100       |     |     | 64   | °C/W |

|                 |    |   | junction-to-ambient natural convection <sup>3</sup> |                         | 144       |     |     | 64   |      |

|                 |    |   |                                                     |                         | 176       |     |     | 64   |      |

|                 |    |   |                                                     | Four-layer board — 2s2p | 100       |     |     | 49.7 |      |

|                 |    |   |                                                     |                         | 144       |     |     | 48.3 |      |

|                 |    |   |                                                     |                         | 176       |     |     | 47.3 |      |

| $R_{\theta JB}$ | СС |   | Thermal resistance,                                 | Single-layer board — 1s | 100       | _   | _   | 36   | °C/W |

|                 |    |   | junction-to-board <sup>4</sup>                      |                         | 144       |     |     | 38   |      |

|                 |    |   |                                                     |                         | 176       |     |     | 38   |      |

|                 |    |   |                                                     | Four-layer board — 2s2p | 100       | _   | _   | 33.6 |      |

|                 |    |   |                                                     |                         | 144       | _   | _   | 33.4 |      |

|                 |    |   |                                                     |                         | 176       |     |     | 33.4 |      |

| Syml            | hol | с | Parameter                               |           | Conditions <sup>1</sup>                                                                                                   |                       | Value |                    | Unit |

|-----------------|-----|---|-----------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|--------------------|------|

| Synn            | 001 | C | Farameter                               |           | Conditions                                                                                                                | Min                   | Тур   | Max                | Unit |

| V <sub>OH</sub> | CC  | Ρ | Output high level<br>SLOW configuration | Push Pull | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>PAD3V5V = 0<br>(recommended)                           | 0.8V <sub>DD</sub>    |       |                    | V    |

|                 |     | С |                                         |           | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>$PAD3V5V = 1^2$                                        | 0.8V <sub>DD</sub>    | _     | _                  |      |

|                 |     | С |                                         |           | $I_{OH} = -1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1<br>(recommended)                           | V <sub>DD</sub> – 0.8 |       |                    |      |

| V <sub>OL</sub> | CC  | Ρ | Output low level<br>SLOW configuration  | Push Pull | $\begin{split} I_{OL} &= 2 \text{ mA}, \\ V_{DD} &= 5.0 \text{ V} \pm 10\%, \\ PAD3V5V &= 0 \\ (recommended) \end{split}$ | —                     |       | 0.1V <sub>DD</sub> | V    |

|                 |     | С |                                         |           | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>$PAD3V5V = 1^2$                                         | —                     | _     | 0.1V <sub>DD</sub> |      |

|                 |     | С |                                         |           | $I_{OL} = 1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1<br>(recommended)                            | —                     | _     | 0.5                |      |

Table 17. SLOW configuration output buffer electrical characteristics

$^{1}$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified

<sup>2</sup> The configuration PAD3V5 = 1 when  $V_{DD}$  = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

| Table 18. MEDIUM configuration output I | buffer electrical characteristics |

|-----------------------------------------|-----------------------------------|

|-----------------------------------------|-----------------------------------|

| Svm             | Symbol ( | C | Parameter                                 |                                                                                                 | V                                                                                                    | Unit                  |     |     |   |

|-----------------|----------|---|-------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|---|

| - Cym           |          | • | i di dillotoi                             |                                                                                                 | Conditions <sup>1</sup>                                                                              | Min                   | Тур | Мах | 0 |

| V <sub>OH</sub> | СС       |   | Output high level<br>MEDIUM configuration | Push Pull $I_{OH} = -3.8 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ |                                                                                                      | 0.8V <sub>DD</sub>    | —   | _   | V |

|                 |          | Ρ |                                           |                                                                                                 | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | 0.8V <sub>DD</sub>    | _   | _   |   |

|                 |          | С |                                           |                                                                                                 | $I_{OH} = -1 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^2$                | 0.8V <sub>DD</sub>    | —   |     |   |

|                 |          | С |                                           |                                                                                                 | $I_{OH} = -1$ mA,<br>$V_{DD} = 3.3$ V ± 10%, PAD3V5V = 1<br>(recommended)                            | V <sub>DD</sub> – 0.8 | —   | _   |   |

|                 |          | С |                                           |                                                                                                 | I <sub>OH</sub> = −100 μA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                             | 0.8V <sub>DD</sub>    | —   |     |   |

| Package                    |                                                 | Supply segment   |                    |                    |                    |                  |      |               |  |  |  |  |

|----------------------------|-------------------------------------------------|------------------|--------------------|--------------------|--------------------|------------------|------|---------------|--|--|--|--|

| Гаскауе                    | 1                                               | 2                | 3                  | 4                  | 5                  | 6                | 7    | 8             |  |  |  |  |

| 208<br>MAPBGA <sup>1</sup> | Equivalent to 176 LQFP segment pad distribution |                  |                    |                    |                    |                  | МСКО | MDOn<br>/MSEO |  |  |  |  |

| 176 LQFP                   | pin7 –<br>pin27                                 | pin28 –<br>pin57 | pin59 –<br>pin85   | pin86 –<br>pin123  | pin124 –<br>pin150 | pin151 –<br>pin6 | —    | —             |  |  |  |  |

| 144 LQFP                   | pin20 –<br>pin49                                | pin51 –<br>pin99 | pin100 –<br>pin122 | pin 123 –<br>pin19 | _                  | _                | —    | —             |  |  |  |  |

| 100 LQFP                   | pin16 –<br>pin35                                | pin37 –<br>pin69 | pin70 –<br>pin83   | pin84 –<br>pin15   | —                  | _                | —    | —             |  |  |  |  |

#### Table 21. I/O supply segments

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

#### Table 22. I/O consumption

| Cymbo                            |    | с | Parameter                                       | Condi                           | itions <sup>1</sup>                           |     | Value | )    | Unit |

|----------------------------------|----|---|-------------------------------------------------|---------------------------------|-----------------------------------------------|-----|-------|------|------|

| Symbo                            |    | C | Parameter                                       | Condi                           | luons <sup>.</sup>                            | Min | Тур   | Max  | Unit |

| I <sub>SWTSLW</sub> <sup>2</sup> | СС | D | Dynamic I/O current for<br>SLOW configuration   | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | -   | —     | 20   | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | —   | —     | 16   |      |

| I <sub>SWTMED</sub> <sup>2</sup> | СС | D | Dynamic I/O current for<br>MEDIUM configuration | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | —   | —     | 29   | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | —   | —     | 17   |      |

| I <sub>SWTFST</sub> <sup>2</sup> | СС | D | Dynamic I/O current for<br>FAST configuration   | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | —   | —     | 110  | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | —   |       | 50   |      |

| I <sub>RMSSLW</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 5.0 V \pm 10\%$ ,                   | —   | —     | 2.3  | mA   |

|                                  |    |   | current for SLOW<br>configuration               | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 0                                   | —   | —     | 3.2  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 2 MHz  | -                                             | —   | —     | 6.6  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 3.3 V \pm 10\%$ ,                   | —   | —     | 1.6  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 1                                   | —   | —     | 2.3  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 2 MHz  | -                                             | _   | —     | 4.7  |      |

| I <sub>RMSMED</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 5.0 V \pm 10\%$ ,                   | —   | —     | 6.6  | mA   |

|                                  |    |   | current for MEDIUM<br>configuration             | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 0                                   | _   | —     | 13.4 |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 13 MHz | -                                             | —   | —     | 18.3 |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   | —   | —     | 5    |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 1                                   | _   | —     | 8.5  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 13 MHz |                                               | —   | —     | 11   |      |

# 4.8 Power management electrical characteristics

# 4.8.1 Voltage regulator electrical characteristics

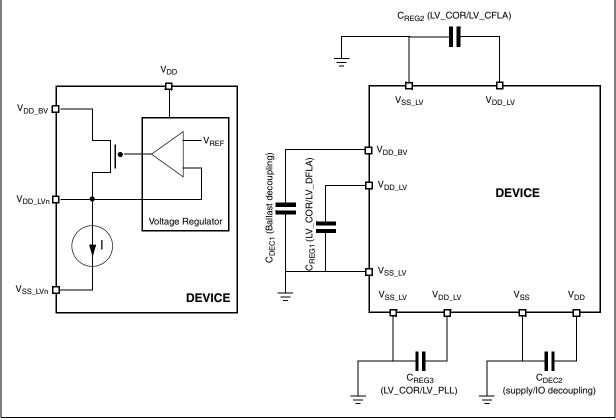

The device implements an internal voltage regulator to generate the low voltage core supply  $V_{DD\_LV}$  from the high voltage ballast supply  $V_{DD\_BV}$ . The regulator itself is supplied by the common I/O supply  $V_{DD}$ . The following supplies are involved:

- HV: High voltage external power supply for voltage regulator module. This must be provided externally through V<sub>DD</sub> power pin.

- BV: High voltage external power supply for internal ballast module. This must be provided externally through  $V_{DD_BV}$  power pin. Voltage values should be aligned with  $V_{DD}$ .

- LV: Low voltage internal power supply for core, FMPLL and Flash digital logic. This is generated by the internal voltage regulator but provided outside to connect stability capacitor. It is further split into four main domains to ensure noise isolation between critical LV modules within the device:

- LV\_COR: Low voltage supply for the core. It is also used to provide supply for FMPLL through double bonding.

- LV\_CFLA: Low voltage supply for code flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_DFLA: Low voltage supply for data flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_PLL: Low voltage supply for FMPLL. It is shorted to LV\_COR through double bonding.

Figure 9. Voltage regulator capacitance connection

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

| Symbol                | Ratings Conditions                                    |                                                      | Class | Max value <sup>3</sup> | Unit |

|-----------------------|-------------------------------------------------------|------------------------------------------------------|-------|------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human Body Model) | $T_A = 25 \ ^{\circ}C$<br>conforming to AEC-Q100-002 | H1C   | 2000                   | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage<br>(Machine Model)    | $T_A = 25 \ ^{\circ}C$<br>conforming to AEC-Q100-003 | M2    | 200                    |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage                       | $T_A = 25 \degree C$                                 | C3A   | 500                    |      |

|                       | (Charged Device Model)                                | conforming to AEC-Q100-011                           |       | 750 (corners)          |      |

#### Table 34. ESD absolute maximum ratings<sup>1,2</sup>

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

<sup>3</sup> Data based on characterization results, not tested in production

### 4.11.3.2 Static latch-up (LU)

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with the EIA/JESD 78 IC latch-up standard.

#### Table 35. Latch-up results

| Symbol | Parameter             | Conditions                                       | Class      |  |

|--------|-----------------------|--------------------------------------------------|------------|--|

| LU     | Static latch-up class | $T_A = 125 \ ^{\circ}C$<br>conforming to JESD 78 | II level A |  |

# 4.12 Fast external crystal oscillator (4 to 16 MHz) electrical characteristics

The device provides an oscillator/resonator driver. Figure 11 describes a simple model of the internal oscillator driver and provides an example of a connection for an oscillator or a resonator.

Table 36 provides the parameter description of 4 MHz to 16 MHz crystals used for the design simulations.

relying the constitution notice where shall be considered. A growing the three constitutions of C

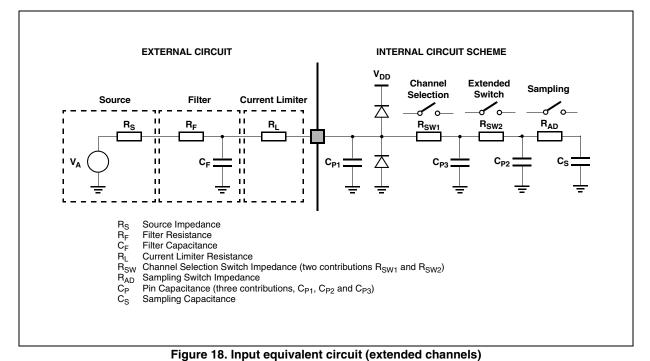

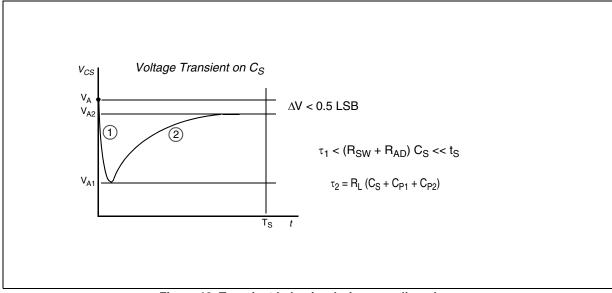

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in Figure 17): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

Figure 19. Transient behavior during sampling phase

In particular two different transient periods can be distinguished:

1. A first and quick charge transfer from the internal capacitance  $C_{P1}$  and  $C_{P2}$  to the sampling capacitance  $C_S$  occurs ( $C_S$  is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which  $C_{P2}$  is reported in parallel to  $C_{P1}$  (call  $C_P = C_{P1} + C_{P2}$ ), the two capacitances  $C_P$  and  $C_S$  are in series, and the time constant is

Eqn. 5

Fan 6

$$\tau_1 = (\mathbf{R}_{SW} + \mathbf{R}_{AD}) \bullet \frac{\mathbf{C}_P \bullet \mathbf{C}_S}{\mathbf{C}_P + \mathbf{C}_S}$$

Equation 5 can again be simplified considering only  $C_S$  as an additional worst condition. In reality, the transient is faster, but the A/D converter circuitry has been designed to be robust also in the very worst case: the sampling time  $t_S$  is always much longer than the internal time constant:

$$\tau_1 < (R_{SW} + R_{AD}) \bullet C_S \ll t_s$$

The charge of  $C_{P1}$  and  $C_{P2}$  is redistributed also on  $C_S$ , determining a new value of the voltage  $V_{A1}$  on the capacitance according to Equation 7:

$$V_{A1} \bullet (C_S + C_{P1} + C_{P2}) = V_A \bullet (C_{P1} + C_{P2})$$

Eqn. 7

2. A second charge transfer involves also  $C_F$  (that is typically bigger than the on-chip capacitance) through the resistance  $R_L$ : again considering the worst case in which  $C_{P2}$  and  $C_S$  were in parallel to  $C_{P1}$  (since the time constant in reality would be faster), the time constant is:

$$\tau_2 < R_L \bullet (C_S + C_{P1} + C_{P2})$$

Eqn. 8

In this case, the time constant depends on the external circuit: in particular imposing that the transient is completed well before the end of sampling time  $t_s$ , a constraints on  $R_I$  sizing is obtained:

$$10 \bullet \tau_2 = 10 \bullet R_L \bullet (C_S + C_{P1} + C_{P2}) < t_s$$

Of course,  $R_L$  shall be sized also according to the current limitation constraints, in combination with  $R_S$  (source impedance) and  $R_F$  (filter resistance). Being  $C_F$  definitively bigger than  $C_{P1}$ ,  $C_{P2}$  and  $C_S$ , then the final voltage  $V_{A2}$  (at the end of the charge transfer transient) will be much higher than  $V_{A1}$ . Equation 10 must be respected (charge balance assuming now  $C_S$  already charged at  $V_{A1}$ ):

Eqn. 10

Egn. 9

$$V_{A2} \bullet (C_S + C_{P1} + C_{P2} + C_F) = V_A \bullet C_F + V_{A1} \bullet (C_{P1} + C_{P2} + C_S)$$

The two transients above are not influenced by the voltage source that, due to the presence of the  $R_FC_F$  filter, is not able to provide the extra charge to compensate the voltage drop on  $C_S$  with respect to the ideal source  $V_A$ ; the time constant  $R_FC_F$  of the filter is very high with respect to the sampling time ( $t_s$ ). The filter is typically designed to act as antialiasing.

<sup>1</sup> Operating conditions:  $T_A = 25 \text{ °C}$ ,  $f_{periph} = 8 \text{ MHz}$  to 64 MHz

<sup>2</sup> f<sub>periph</sub> is an absolute value.

<sup>3</sup> During the conversion, the total current consumption is given from the sum of the static and dynamic consumption, i.e., (41 + 46) \* f<sub>periph</sub>.

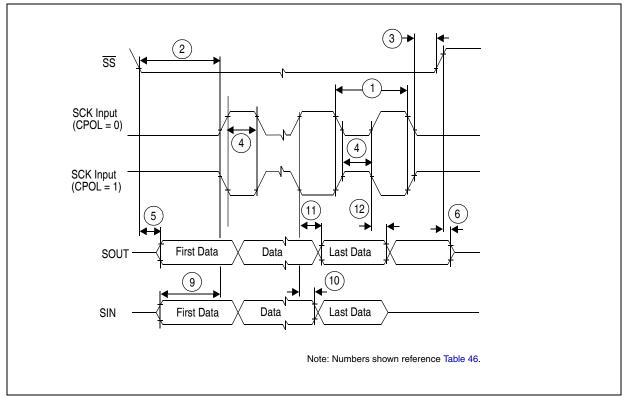

#### 4.18.2 **DSPI** characteristics

| No. | Symbo                            |    | с | Parameter                                                                                                  |                           | DSPI0/D                 | SPI1/DS             | PI5/DSPI6                | C                       | SPI2/DS             | SPI4                      | Unit |

|-----|----------------------------------|----|---|------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------|---------------------|--------------------------|-------------------------|---------------------|---------------------------|------|

| NO. | Symbo                            | 51 |   |                                                                                                            |                           |                         | Max                 | Min Typ                  |                         | Max                 | Onne                      |      |

| 1   | t <sub>SCK</sub>                 | SR | D | SCK cycle time                                                                                             | Master mode<br>(MTFE = 0) | 125                     | —                   | _                        | 333                     | —                   |                           | ns   |

|     |                                  |    | D |                                                                                                            | Slave mode<br>(MTFE = 0)  | 125                     | _                   | _                        | 333                     |                     | _                         |      |

|     |                                  |    | D |                                                                                                            | Master mode<br>(MTFE = 1) | 83                      | _                   | _                        | 125                     | _                   | _                         |      |

|     |                                  |    | D |                                                                                                            | Slave mode<br>(MTFE = 1)  | 83                      | —                   | _                        | 125                     | —                   | _                         |      |

| —   | f <sub>DSPI</sub>                | SR | D | DSPI digital controller frequ                                                                              | lency                     | —                       | _                   | f <sub>CPU</sub>         | _                       | _                   | f <sub>CPU</sub>          | MHz  |

| —   | ∆t <sub>CSC</sub>                | CC | D | Internal delay between pad<br>associated to SCK and pad<br>associated to CSn in<br>master mode for CSn1->0 |                           | —                       | _                   | 130 <sup>2</sup>         | _                       | _                   | 15 <sup>3</sup>           | ns   |

| _   | ∆t <sub>ASC</sub>                | СС | D | Internal delay between pad<br>associated to SCK and pad<br>associated to CSn in<br>master mode for CSn1->1 | Master mode               | _                       | _                   | 130 <sup>3</sup>         |                         | _                   | 130 <sup>3</sup>          | ns   |

| 2   | t <sub>CSCext</sub> <sup>4</sup> | SR | D | CS to SCK delay                                                                                            | Slave mode                | 32                      | —                   | —                        | 32                      | —                   | _                         | ns   |

| 3   | t <sub>ASCext</sub> 5            | SR | D | After SCK delay                                                                                            | Slave mode                | 1/f <sub>DSPI</sub> + 5 | —                   | —                        | 1/f <sub>DSPI</sub> + 5 | —                   | _                         | ns   |

| 4   | t <sub>SDC</sub>                 | СС | D | SCK duty cycle                                                                                             | Master mode               | _                       | t <sub>SCK</sub> /2 | —                        | _                       | t <sub>SCK</sub> /2 | _                         | ns   |

|     |                                  | SR | D |                                                                                                            | Slave mode                | t <sub>SCK</sub> /2     | —                   | —                        | t <sub>SCK</sub> /2     | —                   | _                         |      |

| 5   | t <sub>A</sub>                   | SR | D | Slave access time                                                                                          | Slave mode                | —                       | —                   | 1/f <sub>DSPI</sub> + 70 | _                       | —                   | 1/f <sub>DSPI</sub> + 130 | ns   |

| 6   | t <sub>DI</sub>                  | SR | D | Slave SOUT disable time                                                                                    | Slave mode                | 7                       |                     | —                        | 7                       |                     | —                         | ns   |

#### Table 47. DSPI characteristics<sup>1</sup>

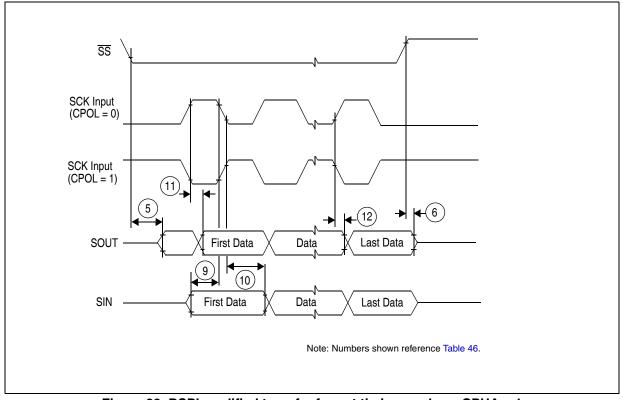

Figure 28. DSPI modified transfer format timing — slave, CPHA = 0

Figure 29. DSPI modified transfer format timing — slave, CPHA = 1

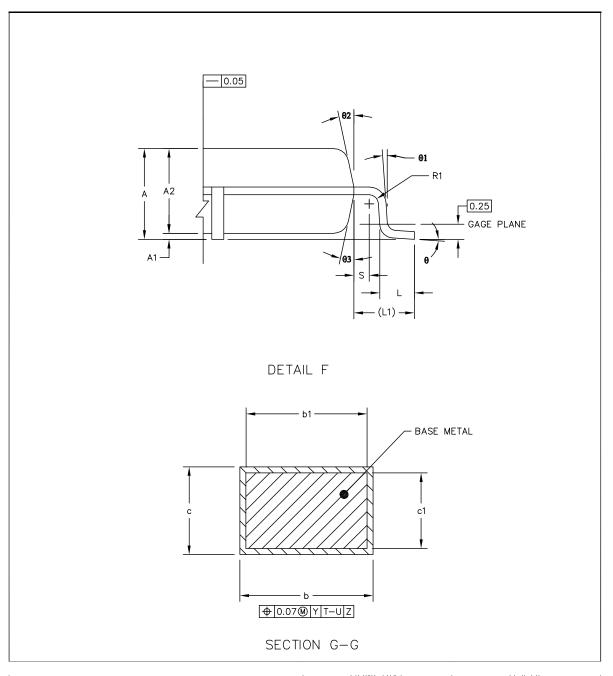

Figure 34. 176 LQFP package mechanical drawing (Part 2 of 3)

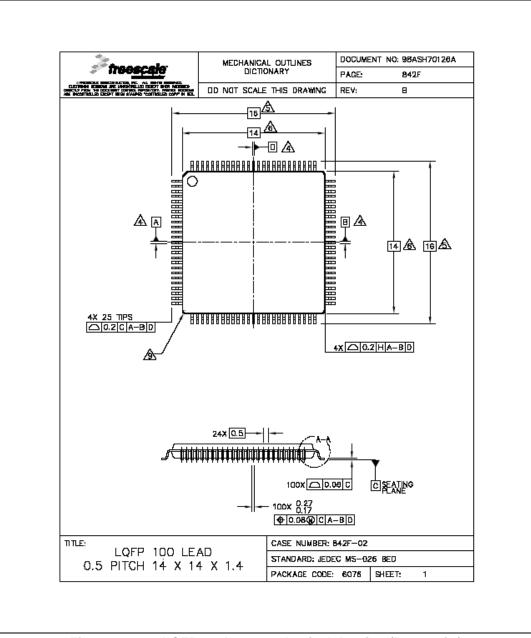

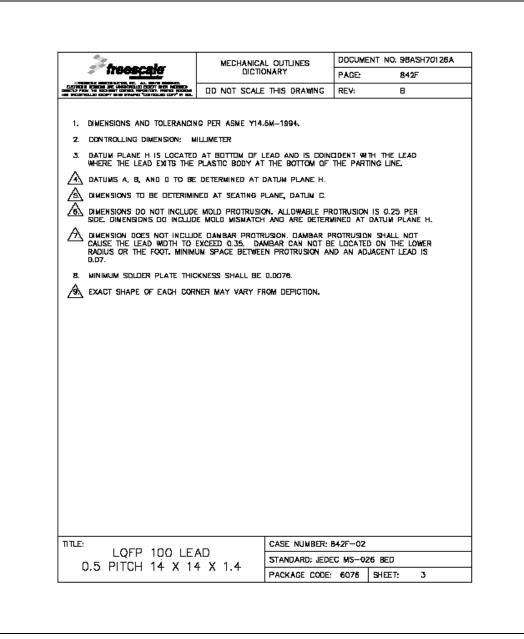

## 5.1.3 100 LQFP

Figure 38. 100 LQFP package mechanical drawing (Part 1 of 3)

Figure 40. 100 LQFP package mechanical drawing (Part 3 of 3)

Package characteristics

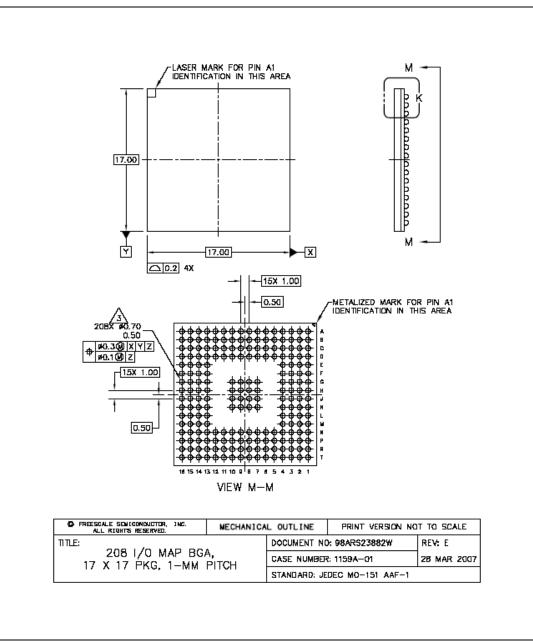

## 5.1.4 208 MAPBGA

Figure 41. 208 MAPBGA package mechanical drawing (Part 1 of 2)

#### **Revision history**

| Revision     | Date                   | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>(cont.) | 24 Aug 2010<br>(cont.) | Table 40:• Added $f_{VCO}$ row• Added $\Delta t_{ST,JIT}$ rowTable 41• I_{FIRCPWD}: removed row for $T_A = 55 \ ^{\circ}C$ • Updated $T_{FIRCSU}$ rowTable 44: Added two rows: I_{ADC0pwd} and I_{ADC0run}Table 45• Added two rows: I_{ADC1pwd} and I_{ADC1run}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |                        | <ul> <li>Updated values of f<sub>ADC_1</sub> and t<sub>ADC1_PU</sub></li> <li>Updated t<sub>ADC1_C</sub> row</li> <li>Updated Table 46</li> <li>Updated Table 47</li> <li>Updated Figure 43</li> <li>Section 6, "Ordering information: deleted "Orderable part number summary" table</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5            | 27 Aug 2010            | Removed "Preliminary—Subject to Change Without Notice" marking. This data sheet contains specifications based on characterization data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6            | 08 Jul 2011            | <ul> <li>Editorial and formatting changes throughout</li> <li>Replaced instances of "e20020" with "e20020h"Device family comparision table:</li> <li>changed LINFlex count for 144-pin LQFP—was '6'; is '8'</li> <li>changed LINFlex count for 176-pin LQFP—was '8'; is '10'</li> <li>replaced 105 °C with 125 °C in footnote 2</li> <li>MPC5607B block diagram: added GPIO and VREG to legend</li> <li>MPC5607B series block summary: added acronym "JTAGC"; in WKPU function changed "up to 18 external sources" to "up to 27 external sources"</li> <li>144 LQFP pin configuration: for pins 37–72, restored the pin labels that existed prior to 27 July 2010</li> <li>176 LQFP pin configuration: corrected name of pin 4: was EPC[15]; is PC[15]</li> <li>Added following sections:</li> <li>Pad configuration during reset phases</li> <li>Pad configuration during standby mode exit</li> <li>Voltage supply pins</li> <li>Pad types</li> <li>System pins</li> <li>Functional port pins</li> <li>Nexus 2+ pins</li> <li>Section "NVUSRO register": edited content to separate configuration into electrical parameters and digital functionality; updated footnote describing default value of '1' in field descriptions NVUSRO[PAD3V5V] and NVUSRO[OSCILLATOR_MARGIN]</li> <li>Added section "NVUSRO[WATCHDOG_EN] field description"</li> <li>Tables "Absolute maximum ratings" and "Recommended operating conditions (3.3 V)": replaced "VSS_HV_ADC0, VSS_HV_ADC1" with "VDD_HV_ADC0, VDD_HV_ADC1" in V<sub>DD_ADC</sub> parameter description</li> </ul> |

#### Table 51. Revision history (continued)