Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | e200z0h                                                     |

| Core Size                  | 32-Bit Single-Core                                          |

| Speed                      | 64MHz                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                  |

| Peripherals                | DMA, POR, PWM, WDT                                          |

| Number of I/O              | 149                                                         |

| Program Memory Size        | 1.5MB (1.5M x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 64K x 8                                                     |

| RAM Size                   | 96K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                   |

| Data Converters            | A/D 29x10b, 5x12b                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 176-LQFP                                                    |

| Supplier Device Package    | 176-LQFP (24x24)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5607bf1mlu6 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

# 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device.

# 1.2 Description

This family of 32-bit system-on-chip (SoC) microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding family of automotive-focused products designed to address the next wave of body electronics applications within the vehicle.

The advanced and cost-efficient e200z0h host processor core of this automotive controller family complies with the Power Architecture technology and only implements the VLE (variable-length encoding) APU (Auxiliary Processor Unit), providing improved code density. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

| Feature                                          |                  | MPC5605B |       | MPC           | 5606B  | MPC5607B |  |  |  |

|--------------------------------------------------|------------------|----------|-------|---------------|--------|----------|--|--|--|

| CPU                                              |                  |          |       | e200z0h       |        |          |  |  |  |

| Execution speed <sup>2</sup>                     |                  |          | ļ     | Up to 64 MH   | z      |          |  |  |  |

| Code flash memory                                | 768 KB           |          |       | 11            | ИB     | 1.5 MB   |  |  |  |

| Data flash memory                                |                  |          | 6     | 64 (4 × 16) K | В      |          |  |  |  |

| SRAM                                             |                  | 64 KB    |       | 80            | KB     | 96 KB    |  |  |  |

| MPU                                              |                  |          |       | 8-entry       |        |          |  |  |  |

| eDMA                                             |                  |          |       | 16 ch         |        |          |  |  |  |

| 10-bit ADC                                       |                  |          |       | Yes           |        |          |  |  |  |

| dedicated <sup>3</sup>                           | 7 ch             | 15 ch    | 29 ch | 15 ch         |        | 29 ch    |  |  |  |

| shared with 12-bit ADC                           |                  |          |       | 19 ch         |        |          |  |  |  |

| 12-bit ADC                                       |                  |          |       | Yes           |        |          |  |  |  |

| dedicated <sup>4</sup>                           |                  |          |       | 5 ch          |        |          |  |  |  |

| shared with 10-bit ADC                           |                  |          |       | 19 ch         |        |          |  |  |  |

| Total timer I/O <sup>5</sup> eMIOS               | 37 ch,<br>16-bit |          |       | 64 ch,        | 16-bit |          |  |  |  |

| Counter / OPWM / ICOC <sup>6</sup>               |                  |          |       | 10 ch         |        |          |  |  |  |

| O(I)PWM / OPWFMB /<br>OPWMCB / ICOC <sup>7</sup> |                  |          |       | 7 ch          |        |          |  |  |  |

| O(I)PWM / ICOC <sup>8</sup>                      | 7 ch             |          |       | 14            | ch     |          |  |  |  |

| OPWM / ICOC <sup>9</sup>                         | 13 ch            | 13 ch    |       |               | ch     |          |  |  |  |

| SCI (LINFlex)                                    | 4                | 8        | 10    | 8             |        | 10       |  |  |  |

| SPI (DSPI)                                       | 3                | 5        | 6     | 5             |        | 6        |  |  |  |

Table 1. MPC5607B family comparison<sup>1</sup>

# 3.3 Pad configuration during standby mode exit

Pad configuration (input buffer enable, pull enable) for low-power wakeup pads is controlled by both the SIUL and WKPU modules. During standby exit, all low power pads PA[0,1,2,4,15],  $PB[1,3,8,9,10]^1$ , PC[7,9,11], PD[0,1], PE[0,9,11],  $PF[9,11,13]^2$ ,  $PG[3,5,7,9]^2$ ,  $PI[1,3]^3$  are configured according to their respective configuration done in the WKPU module. All other pads will have the same configuration as expected after a reset.

The TDO pad has been moved into the STANDBY domain in order to allow low-power debug handshaking in STANDBY mode. However, no pull-resistor is active on the TDO pad while in STANDBY mode. At this time the pad is configured as an input. When no debugger is connected the TDO pad is floating causing additional current consumption.

To avoid the extra consumption TDO must be connected. An external pull-up resistor in the range of 47–100 kOhms should be added between the TDO pin and VDD. Only if the TDO pin is used as an application pin and a pull-up cannot be used should a pull-down resistor with the same value be used instead between the TDO pin and GND.

# 3.4 Voltage supply pins

Voltage supply pins are used to provide power to the device. Three dedicated VDD\_LV/VSS\_LV supply pairs are used for 1.2 V regulator stabilization.

| Port pin    | Function                                                                                                                                       | Pin number            |                        |                                |                                                                                   |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|--------------------------------|-----------------------------------------------------------------------------------|--|--|--|

| Fortpin     | T unction                                                                                                                                      | 100 LQFP              | 144 LQFP               | 176 LQFP                       | 208 MAPBGA                                                                        |  |  |  |

| VDD_HV      | Digital supply voltage                                                                                                                         | 15, 37, 70, 84        | 19, 51, 100,<br>123    | 6, 27, 59, 85,<br>124, 151     | C2, D9, E16,<br>G13, H3, N4,<br>N9, R5                                            |  |  |  |

| VSS_HV      | Digital ground                                                                                                                                 | 14, 16, 35, 69,<br>83 | 18, 20, 49, 99,<br>122 | 7, 26, 28, 57,<br>86, 123, 150 | G7, G8, G9,<br>G10, H7, H8,<br>H9, H10, J7,<br>J8, J9, J10,<br>K7, K8, K9,<br>K10 |  |  |  |

| VDD_LV      | 1.2 V decoupling pins. Decoupling capacitor must be connected between these pins and the nearest $V_{SS_{LV}}$ pin. <sup>1</sup>               | 19, 32, 85            | 23, 46, 124            | 31, 54, 152                    | D8, K4, P7                                                                        |  |  |  |

| VSS_LV      | 1.2 V decoupling pins. Decoupling<br>capacitor must be connected<br>between these pins and the nearest<br>V <sub>DD_LV</sub> pin. <sup>1</sup> | 18, 33, 86            | 22, 47, 125            | 30, 55, 153                    | C8, J2, N7                                                                        |  |  |  |

| VDD_BV      | Internal regulator supply voltage                                                                                                              | 20                    | 24                     | 32                             | K3                                                                                |  |  |  |

| VSS_HV_ADC0 | Reference ground and analog ground for the A/D converter 0 (10-bit)                                                                            | 51                    | 73                     | 89                             | R15                                                                               |  |  |  |

| VDD_HV_ADC0 | Reference voltage and analog supply for the A/D converter 0 (10-bit)                                                                           | 52                    | 74                     | 90                             | P14                                                                               |  |  |  |

| VSS_HV_ADC1 | Reference ground and analog ground for the A/D converter 1 (12-bit)                                                                            | 59                    | 81                     | 98                             | N12                                                                               |  |  |  |

## Table 3. Voltage supply pin descriptions

1. PB[8, 9] ports have wakeup functionality in all modes except STANDBY.

2. PF[9,11,13], PG[3,5,7,9], PI[1,3] are not available in the 100-pin LQFP.

3. PI[1,3] are not available in the 144-pin LQFP.

|                     |         | tion <sup>1</sup>               |                                                    |                                             | 1 <sup>2</sup>             |                 | n³                                  |             | Pin nu      | umber       |                                |

|---------------------|---------|---------------------------------|----------------------------------------------------|---------------------------------------------|----------------------------|-----------------|-------------------------------------|-------------|-------------|-------------|--------------------------------|

| Port pin            | PCR     | Alternate function <sup>1</sup> | Function                                           | Peripheral                                  | I/O direction <sup>2</sup> | Pad type        | RESET<br>configuration <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP | 208<br>MAP<br>BGA <sup>4</sup> |

| PB[11]              | PCR[27] | AF0<br>AF1<br>AF2               | GPIO[27]<br>E0UC[3]<br>—                           | SIUL<br>eMIOS_0                             | I/O<br>I/O                 | J               | Tristate                            | —           | —           | 97          | N13                            |

|                     |         | AF3<br>—                        | CS0_0<br>ADC0_S[3]                                 | DSPI_0<br>ADC_0                             | I/O<br>I                   |                 |                                     |             |             |             |                                |

| PB[12]              | PCR[28] | AF0<br>AF1<br>AF2               | GPIO[28]<br>E0UC[4]<br>—                           | SIUL<br>eMIOS_0                             | I/O<br>I/O                 | J               | Tristate                            | 61          | 83          | 101         | M16                            |

|                     |         | AF3<br>—                        | CS1_0<br>ADC0_X[0]                                 | DSPI_0<br>ADC_0                             | 0<br>1                     |                 |                                     |             |             |             |                                |

| PB[13]              | PCR[29] | AF0<br>AF1<br>AF2               | GPIO[29]<br>E0UC[5]<br>—                           | SIUL<br>eMIOS_0                             | I/O<br>I/O                 | J               | Tristate                            | 63          | 85          | 103         | M13                            |

|                     |         | AF3<br>—                        | CS2_0<br>ADC0_X[1]                                 | DSPI_0<br>ADC_0                             | 0<br>1                     |                 |                                     |             |             |             |                                |

| PB[14]              | PCR[30] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[30]<br>E0UC[6]<br>—<br>CS3_0<br>ADC0_X[2]     | SIUL<br>eMIOS_0<br>—<br>DSPI_0<br>ADC_0     | I/O<br>I/O<br>- O<br>-     | J               | Tristate                            | 65          | 87          | 105         | L16                            |

| PB[15]              | PCR[31] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[31]<br>E0UC[7]<br><br>CS4_0<br>ADC0_X[3]      | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC_0      | I/O<br>I/O<br>—<br>0<br>I  | J               | Tristate                            | 67          | 89          | 107         | L13                            |

|                     |         | <u> </u>                        |                                                    | Por                                         | t C                        | <u> </u>        |                                     |             |             |             |                                |

| PC[0] <sup>10</sup> | PCR[32] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[32]<br>—<br>TDI<br>—                          | SIUL<br>—<br>JTAGC<br>—                     | I/O<br><br>                | М               | Input,<br>weak<br>pull-up           | 87          | 126         | 154         | A8                             |

| PC[1] <sup>10</sup> | PCR[33] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[33]<br><br>TDO<br>                            | SIUL<br>—<br>JTAGC<br>—                     | I/O<br>—<br>0<br>—         | F <sup>11</sup> | Tristate                            | 82          | 121         | 149         | C9                             |

| PC[2]               | PCR[34] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[34]<br>SCK_1<br>CAN4TX<br>DEBUG[0]<br>EIRQ[5] | SIUL<br>DSPI_1<br>FlexCAN_4<br>SSCM<br>SIUL | I/O<br>I/O<br>O<br>O<br>I  | Μ               | Tristate                            | 78          | 117         | 145         | A11                            |

| Table 5. Functional port pir | n descriptions (continued) |

|------------------------------|----------------------------|

|------------------------------|----------------------------|

|          |         | ion <sup>1</sup>                        |                                                                       |                                                      | 2                                                                                                  |          | <sup>3</sup>                        |             | Pin nu      | umber       |                                |

|----------|---------|-----------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------|-------------------------------------|-------------|-------------|-------------|--------------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>         | Function                                                              | Peripheral                                           | I/O direction <sup>2</sup>                                                                         | Pad type | RESET<br>configuration <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP | 208<br>MAP<br>BGA <sup>4</sup> |

| PC[11]   | PCR[43] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—      | GPIO[43]<br>—<br>MA[2]<br>WKPU[5] <sup>5</sup><br>CAN1RX<br>CAN4RX    | SIUL<br>—<br>ADC_0<br>WKPU<br>FlexCAN_1<br>FlexCAN_4 | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>— | S        | Tristate                            | 21          | 27          | 35          | M4                             |

| PC[12]   | PCR[44] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[44]<br>E0UC[12]<br>—<br>EIRQ[19]<br>SIN_2                        | SIUL<br>eMIOS_0<br>—<br>SIUL<br>DSPI_2               | 10<br>10<br>10<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                                  | Μ        | Tristate                            | 97          | 141         | 173         | B4                             |

| PC[13]   | PCR[45] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[45]<br>E0UC[13]<br>SOUT_2<br>—                                   | SIUL<br>eMIOS_0<br>DSPI_2<br>—                       | 1/0 /0                                                                                             | S        | Tristate                            | 98          | 142         | 174         | A2                             |

| PC[14]   | PCR[46] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[46]<br>E0UC[14]<br>SCK_2<br>—<br>EIRQ[8]                         | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>SIUL               | I/O<br>I/O<br>I/O<br>I                                                                             | S        | Tristate                            | 3           | 3           | 3           | C1                             |

| PC[15]   | PCR[47] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[47]<br>E0UC[15]<br>CS0_2<br>—<br>EIRQ[20]                        | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>SIUL               | I/O<br>I/O<br>I/O<br>I                                                                             | М        | Tristate                            | 4           | 4           | 4           | D3                             |

|          |         |                                         |                                                                       | Por                                                  | t D                                                                                                |          |                                     |             |             |             |                                |

| PD[0]    | PCR[48] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[48]<br>—<br>—<br>WKPU[27] <sup>5</sup><br>ADC0_P[4]<br>ADC1_P[4] | SIUL<br>—<br>—<br>WKPU<br>ADC_0<br>ADC_1             | <br> -<br> <br> <br>                                                                               | Ι        | Tristate                            | 41          | 63          | 77          | P12                            |

| PD[1]    | PCR[49] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[49]<br>—<br>—<br>WKPU[28] <sup>5</sup><br>ADC0_P[5]<br>ADC1_P[5] | SIUL<br>—<br>—<br>WKPU<br>ADC_0<br>ADC_1             | <br> <br> <br>                                                                                     | Ι        | Tristate                            | 42          | 64          | 78          | T12                            |

Table 5. Functional port pin descriptions (continued)

|          |         | ion <sup>1</sup>                |                                                |                                  | 2                          |          | n <sup>3</sup>                      |             | Pin n       | umber       |                                |

|----------|---------|---------------------------------|------------------------------------------------|----------------------------------|----------------------------|----------|-------------------------------------|-------------|-------------|-------------|--------------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup> | Function                                       | Peripheral                       | I/O direction <sup>2</sup> | Pad type | RESET<br>configuration <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP | 208<br>MAP<br>BGA <sup>4</sup> |

| PD[2]    | PCR[50] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[50]<br>—<br>—<br>ADC0_P[6]<br>ADC1_P[6]   | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | -                          | Ι        | Tristate                            | 43          | 65          | 79          | R12                            |

| PD[3]    | PCR[51] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[51]<br>—<br>—<br>ADC0_P[7]<br>ADC1_P[7]   | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> -<br> <br>            | I        | Tristate                            | 44          | 66          | 80          | P13                            |

| PD[4]    | PCR[52] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[52]<br>—<br>—<br>ADC0_P[8]<br>ADC1_P[8]   | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> <br> <br>             | Ι        | Tristate                            | 45          | 67          | 81          | R13                            |

| PD[5]    | PCR[53] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[53]<br>—<br>—<br>ADC0_P[9]<br>ADC1_P[9]   | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> <br> <br>             | Ι        | Tristate                            | 46          | 68          | 82          | T13                            |

| PD[6]    | PCR[54] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[54]<br>—<br>—<br>ADC0_P[10]<br>ADC1_P[10] | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> <br> <br>             | Ι        | Tristate                            | 47          | 69          | 83          | T14                            |

| PD[7]    | PCR[55] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[55]<br>—<br>—<br>ADC0_P[11]<br>ADC1_P[11] | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | -                          | Ι        | Tristate                            | 48          | 70          | 84          | R14                            |

| PD[8]    | PCR[56] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[56]<br>—<br>—<br>ADC0_P[12]<br>ADC1_P[12] | SIUL<br>—<br>—<br>ADC_0<br>ADC_1 | <br> -<br> <br>            | Ι        | Tristate                            | 49          | 71          | 87          | T15                            |

- <sup>1</sup> Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIUL module. PCR.PA = 00 → AF0; PCR.PA = 01 → AF1; PCR.PA = 10 → AF2; PCR.PA = 11 → AF2. This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "—".

- <sup>2</sup> Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

- <sup>3</sup> The RESET configuration applies during and after reset.

- <sup>4</sup> 208 MAPBGA available only as development package for Nexus2+

- <sup>5</sup> All WKPU pins also support external interrupt capability. See the WKPU chapter for further details.

- <sup>6</sup> NMI has higher priority than alternate function. When NMI is selected, the PCR.AF field is ignored.

- <sup>7</sup> "Not applicable" because these functions are available only while the device is booting. Refer to the BAM information for details.

- <sup>8</sup> Value of PCR.IBE bit must be 0

- <sup>9</sup> This wakeup input cannot be used to exit STANDBY mode.

- <sup>10</sup> Out of reset all the functional pins except PC[0:1] and PH[9:10] are available to the user as GPIO. PC[0:1] are available as JTAG pins (TDI and TDO respectively). PH[9:10] are available as JTAG pins (TCK and TMS respectively).

- It is up to the user to configure these pins as GPIO when needed.

- <sup>11</sup> PC[1] is a fast/medium pad but is in medium configuration by default. This pad is in Alternate Function 2 mode after reset which has TDO functionality. The reset value of PCR.OBE is '1', but this setting has no impact as long as this pad stays in AF2 mode. After configuring this pad as GPIO (PCR.PA = 0), output buffer is enabled as reset value of PCR.OBE = 1.

- <sup>12</sup> Not available in 100 LQFP package

## 3.8 Nexus 2+ pins

In the 208 MAPBGA package, eight additional debug pins are available (see Table 6).

|          |                       | I/O       |          | Function    | Pin number  |             |                             |  |

|----------|-----------------------|-----------|----------|-------------|-------------|-------------|-----------------------------|--|

| Port pin | Function              | direction | Pad type | after reset | 100<br>LQFP | 144<br>LQFP | 208 MAP<br>BGA <sup>1</sup> |  |

| МСКО     | Message clock out     | 0         | F        | —           | —           | _           | T4                          |  |

| MDO0     | Message data out 0    | 0         | М        | —           |             |             | H15                         |  |

| MDO1     | Message data out 1    | 0         | М        | _           |             | _           | H16                         |  |

| MDO2     | Message data out 2    | 0         | М        | —           |             | _           | H14                         |  |

| MDO3     | Message data out 3    | 0         | М        | —           |             |             | H13                         |  |

| EVTI     | Event in              | I         | М        | Pull-up     |             | _           | K1                          |  |

| EVTO     | Event out             | 0         | М        | —           |             | _           | L4                          |  |

| MSEO     | Message start/end out | 0         | М        | —           | —           | _           | G16                         |  |

Table 6. Nexus 2+ pin descriptions

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

| Symbol                      |    | Parameter                                                                                               | Conditions                             | Va                    | lue                   | Unit |

|-----------------------------|----|---------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------|-----------------------|------|

| Symbol                      |    | Farameter                                                                                               | Conditions                             | Min                   | Max                   | Unit |

| V <sub>SS_ADC</sub>         | SR | Voltage on VSS_HV_ADC0,<br>VSS_HV_ADC1 (ADC reference) pin with<br>respect to ground (V <sub>SS</sub> ) |                                        | V <sub>SS</sub> - 0.1 | V <sub>SS</sub> + 0.1 | V    |

| $V_{DD\_ADC}^4$             | SR | Voltage on VDD_HV_ADC0,                                                                                 | —                                      | 3.0 <sup>5</sup>      | 3.6                   | V    |

|                             |    | VDD_HV_ADC1 (ADC reference) with respect to ground (V <sub>SS</sub> )                                   | Relative to V <sub>DD</sub>            | V <sub>DD</sub> - 0.1 | V <sub>DD</sub> + 0.1 |      |

| V <sub>IN</sub>             | SR |                                                                                                         | —                                      | $V_{SS} - 0.1$        | —                     | V    |

|                             |    | ground (V <sub>SS</sub> )                                                                               | Relative to V <sub>DD</sub>            | —                     | V <sub>DD</sub> + 0.1 |      |

| I <sub>INJPAD</sub>         | SR | Injected input current on any pin during<br>overload condition                                          | _                                      | -5                    | 5                     | mA   |

| I <sub>INJSUM</sub>         | SR | Absolute sum of all injected input currents during overload condition                                   | _                                      | -50                   | 50                    | -    |

| TV <sub>DD</sub>            | SR | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                                           | —                                      | —                     | 0.25                  | V/µs |

| T <sub>A C-Grade Part</sub> | SR | Ambient temperature under bias                                                                          | f <sub>CPU</sub> < 64 MHz <sup>7</sup> | -40                   | 85                    | °C   |

| T <sub>J C-Grade</sub> Part | SR | Junction temperature under bias                                                                         | —                                      | -40                   | 110                   |      |

| T <sub>A V-Grade Part</sub> | SR | Ambient temperature under bias                                                                          | f <sub>CPU</sub> < 64 MHz <sup>7</sup> | -40                   | 105                   |      |

| T <sub>J V-Grade</sub> Part | SR | Junction temperature under bias                                                                         | —                                      | -40                   | 130                   | 1    |

| TA M-Grade Part             | SR | Ambient temperature under bias                                                                          | f <sub>CPU</sub> < 64 MHz <sup>7</sup> | -40                   | 125                   | 1    |

| T <sub>J M-Grade Part</sub> | SR | Junction temperature under bias                                                                         | —                                      | -40                   | 150                   | 1    |

Table 12. Recommended operating conditions (3.3 V) (continued)

<sup>1</sup> 100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair.

$^2~$  330 nF capacitance needs to be provided between each V\_{DD~LV}/V\_{SS~LV} supply pair.

<sup>3</sup> 470 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics). Supply ramp slope on VDD\_BV should always be faster or equal to slope of VDD\_HV. Otherwise, device may enter regulator bypass mode if slope on VDD\_BV is slower.

$^4\,$  100 nF capacitance needs to be provided between V\_DD\_ADC/V\_SS\_ADC pair.

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

<sup>6</sup> Guaranteed by device validation

<sup>7</sup> This frequency includes the 4% frequency modulation guardband.

| Table 13 | . Recommended | operating | conditions | (5.0 V | /) |

|----------|---------------|-----------|------------|--------|----|

|----------|---------------|-----------|------------|--------|----|

| Symbol                          |    | Parameter                                                                                        | Conditions                | Va                    | Unit                  |      |

|---------------------------------|----|--------------------------------------------------------------------------------------------------|---------------------------|-----------------------|-----------------------|------|

| Symbol                          |    | i arameter                                                                                       | Conditions                | Min                   | Max                   | onit |

| V <sub>SS</sub>                 | SR | Digital ground on VSS_HV pins                                                                    | —                         | 0                     | 0                     | V    |

| V <sub>DD</sub> <sup>1</sup>    | SR | Voltage on VDD_HV pins with respect to ground                                                    | —                         | 4.5                   | 5.5                   | V    |

|                                 |    | (V <sub>SS</sub> )                                                                               | Voltage drop <sup>2</sup> | 3.0                   | 5.5                   |      |

| V <sub>SS_LV</sub> <sup>3</sup> |    | Voltage on VSS_LV (low voltage digital supply)<br>pins with respect to ground (V <sub>SS</sub> ) | —                         | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

# 4.5 Thermal characteristics

## 4.5.1 External ballast resistor recommendations

External ballast resistor on  $V_{DD_BV}$  pin helps in reducing the overall power dissipation inside the device. This resistor is required only when maximum power consumption exceeds the limit imposed by package thermal characteristics.

As stated in Table 14 LQFP thermal characteristics, considering a thermal resistance of 144 LQFP as 48.3 °C/W, at ambient temperature  $T_A = 125$  °C, the junction temperature  $T_j$  will cross 150 °C if the total power dissipation is greater than (150 - 125)/48.3 = 517 mW. Therefore, the total device current  $I_{DDMAX}$  at 125 °C/5.5 V must not exceed 94.1 mA (i.e., PD/VDD). Assuming an average  $I_{DD}(V_{DD_{HV}})$  of 15–20 mA consumption typically during device RUN mode, the LV domain consumption  $I_{DD}(V_{DD_{BV}})$  is thus limited to  $I_{DDMAX} - I_{DD}(V_{DD_{HV}})$ , i.e., 80 mA.

Therefore, respecting the maximum power allowed as explained in Section 4.5.2, "Package thermal characteristics, it is recommended to use this resistor only in the 125 °C/5.5 V operating corner as per the following guidelines:

- If  $I_{DD}(V_{DD BV}) < 80$  mA, then no resistor is required.

- If 80 mA  $< I_{DD}(V_{DD BV}) < 90$  mA, then 4  $\Omega$  resistor can be used.

- If  $I_{DD}(V_{DD BV}) > 90$  mA, then 8  $\Omega$  resistor can be used.

Using resistance in the range of 4–8  $\Omega$ , the gain will be around 10–20% of total consumption on V<sub>DD\_BV</sub>. For example, if 8  $\Omega$  resistor is used, then power consumption when I<sub>DD</sub>(V<sub>DD\_BV</sub>) is 110 mA is equivalent to power consumption when I<sub>DD</sub>(V<sub>DD\_BV</sub>) is 90 mA (approximately) when resistor not used.

In order to ensure correct power up, the minimum  $V_{DD_BV}$  to be guaranteed is 30 ms/V. If the supply ramp is slower than this value, then LVDHV3B monitoring ballast supply  $V_{DD_BV}$  pin gets triggered leading to device reset. Until the supply reaches certain threshold, this low voltage detector (LVD) generates destructive reset event in the system. This threshold depends on the maximum  $I_{DD}(V_{DD_BV})$  possible across the external resistor.

## 4.5.2 Package thermal characteristics

## Table 14. LQFP thermal characteristics<sup>1</sup>

| Symb            |    | С | Parameter                                           | Conditions <sup>2</sup> | Pin count |     | Value | •    | Unit |

|-----------------|----|---|-----------------------------------------------------|-------------------------|-----------|-----|-------|------|------|

| Synn            |    | C | Falanciel                                           | Conditions              |           | Min | Тур   | Max  | Onit |

| $R_{\theta JA}$ | СС | D | Thermal resistance,                                 | Single-layer board — 1s | 100       |     |       | 64   | °C/W |

|                 |    |   | junction-to-ambient natural convection <sup>3</sup> |                         | 144       |     |       | 64   |      |

|                 |    |   |                                                     |                         | 176       |     |       | 64   |      |

|                 |    |   |                                                     | Four-layer board — 2s2p | 100       |     |       | 49.7 |      |

|                 |    |   |                                                     |                         | 144       |     |       | 48.3 |      |

|                 |    |   |                                                     |                         | 176       |     |       | 47.3 |      |

| $R_{\theta JB}$ | СС |   | Thermal resistance,                                 | Single-layer board — 1s | 100       | _   | _     | 36   | °C/W |

|                 |    |   | junction-to-board <sup>4</sup>                      |                         | 144       |     |       | 38   |      |

|                 |    |   |                                                     |                         | 176       |     |       | 38   |      |

|                 |    |   |                                                     | Four-layer board — 2s2p | 100       | _   | _     | 33.6 |      |

|                 |    |   |                                                     |                         | 144       | _   | _     | 33.4 |      |

|                 |    |   |                                                     |                         | 176       |     |       | 33.4 |      |

| Syml            | hol | с                                              | Parameter                              |                                                                                                 | Conditions <sup>1</sup>                                                                                                    |                                          | Value |                    | Unit |

|-----------------|-----|------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|--------------------|------|

| Synn            | 001 | C                                              | Farameter                              |                                                                                                 | Conditions                                                                                                                 | Min                                      | Тур   | Max                | Unit |

| V <sub>OH</sub> | CC  | CC P Output high level Push SLOW configuration |                                        | Push Pull                                                                                       | $\begin{split} I_{OH} &= -2 \text{ mA}, \\ V_{DD} &= 5.0 \text{ V} \pm 10\%, \\ PAD3V5V &= 0 \\ (recommended) \end{split}$ | 0.8V <sub>DD</sub>                       |       |                    | V    |

|                 |     | С                                              |                                        |                                                                                                 | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>$PAD3V5V = 1^2$                                         | 0.8V <sub>DD</sub>                       | _     | _                  |      |

|                 | C   |                                                |                                        | $I_{OH} = -1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1<br>(recommended) | V <sub>DD</sub> – 0.8                                                                                                      |                                          |       |                    |      |

| V <sub>OL</sub> | CC  | Ρ                                              | Output low level<br>SLOW configuration | Push Pull                                                                                       | $\begin{split} I_{OL} &= 2 \text{ mA}, \\ V_{DD} &= 5.0 \text{ V} \pm 10\%, \\ PAD3V5V &= 0 \\ (recommended) \end{split}$  | 2 mA, — — — (<br>5.0 V ± 10%,<br>/5V = 0 |       | 0.1V <sub>DD</sub> | V    |

|                 |     | С                                              |                                        |                                                                                                 | $I_{OL} = 2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%,$<br>$PAD3V5V = 1^2$                                          | —                                        | _     | 0.1V <sub>DD</sub> |      |

|                 |     | С                                              |                                        |                                                                                                 | $I_{OL} = 1 \text{ mA},$<br>$V_{DD} = 3.3 \text{ V} \pm 10\%,$<br>PAD3V5V = 1<br>(recommended)                             | —                                        | _     | 0.5                |      |

Table 17. SLOW configuration output buffer electrical characteristics

$^{1}$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified

<sup>2</sup> The configuration PAD3V5 = 1 when  $V_{DD}$  = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

| Table 18. MEDIUM configuration output I | buffer electrical characteristics |

|-----------------------------------------|-----------------------------------|

|-----------------------------------------|-----------------------------------|

| Sym             | bol | C | Parameter                                 |            | Conditions <sup>1</sup>                                                                              | V                     |     | Unit |   |

|-----------------|-----|---|-------------------------------------------|------------|------------------------------------------------------------------------------------------------------|-----------------------|-----|------|---|

| - Oym           |     |   |                                           | Conditions | Min                                                                                                  | Тур                   | Max | Unit |   |

| V <sub>OH</sub> | СС  |   | Output high level<br>MEDIUM configuration | Push Pull  | I <sub>OH</sub> = -3.8 mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                             | 0.8V <sub>DD</sub>    | —   |      | V |

|                 |     | Ρ |                                           |            | $I_{OH} = -2 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$<br>(recommended) | 0.8V <sub>DD</sub>    | _   | _    |   |

|                 |     | С |                                           |            | $I_{OH} = -1 \text{ mA},$<br>$V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^2$                | 0.8V <sub>DD</sub>    | —   | _    |   |

|                 |     | С |                                           |            | $I_{OH} = -1$ mA,<br>$V_{DD} = 3.3$ V ± 10%, PAD3V5V = 1<br>(recommended)                            | V <sub>DD</sub> – 0.8 | —   | _    |   |

|                 |     | С |                                           |            | I <sub>OH</sub> = −100 μA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                             | 0.8V <sub>DD</sub>    | —   |      |   |

<sup>2</sup> The configuration PAD3V5 = 1 when  $V_{DD}$  = 5 V is only a transient configuration during power-up. All pads but RESET and Nexus output (MDOx, EVTO, MCKO) are configured in input or in high impedance state.

## 4.6.4 Output pin transition times

| Symb            |     | с | Parameter                                                                                                              | (c)                     | nditions <sup>1</sup>                                              |     | Value | •   | Unit |

|-----------------|-----|---|------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------|-----|-------|-----|------|

| Synn            | 101 | C | Falameter                                                                                                              |                         | nations                                                            | Min | Тур   | Max | Onit |

| T <sub>tr</sub> | СС  | D | Output transition time output pin <sup>2</sup>                                                                         | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 V \pm 10\%$ ,                                        |     |       | 50  | ns   |

|                 |     | Т | SLOW configuration                                                                                                     | C <sub>L</sub> = 50 pF  | PAD3V5V = 0                                                        | _   | _     | 100 |      |

|                 |     | D |                                                                                                                        | C <sub>L</sub> = 100 pF |                                                                    | _   | —     | 125 |      |

|                 |     | D |                                                                                                                        | C <sub>L</sub> = 25 pF  | $V_{DD} = 3.3 V \pm 10\%$ ,                                        | _   | —     | 50  |      |

|                 |     | Т |                                                                                                                        | C <sub>L</sub> = 50 pF  | PAD3V5V = 1                                                        | _   | _     | 100 |      |

|                 |     | D |                                                                                                                        | C <sub>L</sub> = 100 pF |                                                                    | _   | _     | 125 |      |

| T <sub>tr</sub> | СС  | D | $\begin{array}{c} \text{MEDIUM configuration} \\ \text{C}_{L} = 50 \text{ pF} \\ \text{SIUL.PCRx.SRC} = 1 \end{array}$ | _                       | —                                                                  | 10  | ns    |     |      |

|                 |     | Т |                                                                                                                        |                         | _                                                                  | _   | 20    |     |      |

|                 |     | D |                                                                                                                        | C <sub>L</sub> = 100 pF |                                                                    | _   | _     | 40  |      |

|                 |     | D |                                                                                                                        | C <sub>L</sub> = 25 pF  | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1<br>SIUL.PCRx.SRC = 1 | _   | _     | 12  |      |

|                 |     | Т |                                                                                                                        | C <sub>L</sub> = 50 pF  |                                                                    |     |       | 25  |      |

|                 |     | D |                                                                                                                        | C <sub>L</sub> = 100 pF |                                                                    |     |       | 40  |      |

| T <sub>tr</sub> | СС  | D | Output transition time output pin <sup>2</sup>                                                                         | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 V \pm 10\%$ ,                                        | _   | _     | 4   | ns   |

|                 |     |   | FAST configuration                                                                                                     | C <sub>L</sub> = 50 pF  | PAD3V5V = 0                                                        |     |       | 6   |      |

|                 |     |   |                                                                                                                        | C <sub>L</sub> = 100 pF | ]                                                                  | —   | —     | 12  |      |

|                 |     |   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                  | _                       | —                                                                  | 4   |       |     |      |

|                 |     |   |                                                                                                                        | —                       | —                                                                  | 7   |       |     |      |

|                 |     |   |                                                                                                                        | C <sub>L</sub> = 100 pF |                                                                    | _   | _     | 12  |      |

Table 20. Output pin transition times

$\overline{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

$^2~$  CL includes device and package capacitances (C\_{PKG} < 5 pF).

## 4.6.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in Table 21.

Table 22 provides I/O consumption figures.

In order to ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{AVGSEG}$  maximum value.

| •           |             |             |        |                      | 176 L   | QFP          |         |            | 144/10  | 0 LQFP       |         |

|-------------|-------------|-------------|--------|----------------------|---------|--------------|---------|------------|---------|--------------|---------|

| Sup         | ply segr    | nent        | Pad    | Weight 5 V           |         | Weight 3.3 V |         | Weight 5 V |         | Weight 3.3 V |         |

| 176<br>LQFP | 144<br>LQFP | 100<br>LQFP |        | SRC <sup>2</sup> = 0 | SRC = 1 | SRC = 0      | SRC = 1 | SRC = 0    | SRC = 1 | SRC = 0      | SRC = 1 |

| 1           |             | _           | PH[15] | 2%                   | 3%      | 3%           | 3%      | _          | _       |              | —       |

|             |             | _           | PH[13] | 3%                   | 4%      | 3%           | 4%      | —          | _       |              | _       |

|             |             | _           | PH[14] | 3%                   | 4%      | 4%           | 4%      | —          | —       | —            | —       |

|             |             | _           | PI[6]  | 4%                   | —       | 4%           | —       | —          | —       | —            | —       |

|             | —           | _           | PI[7]  | 4%                   | —       | 4%           |         | —          | —       | —            | —       |

|             | 4           | _           | PG[5]  | 4%                   | —       | 5%           |         | 10%        | —       | 12%          | —       |

|             |             | _           | PG[4]  | 4%                   | 6%      | 5%           | 5%      | 9%         | 13%     | 11%          | 12%     |

|             |             | _           | PG[3]  | 4%                   | —       | 5%           | —       | 9%         | —       | 11%          | —       |

|             |             | _           | PG[2]  | 4%                   | 6%      | 5%           | 5%      | 9%         | 12%     | 10%          | 11%     |

|             |             | 4           | PA[2]  | 4%                   | —       | 5%           | —       | 8%         | —       | 10%          | —       |

|             |             |             | PE[0]  | 4%                   | —       | 5%           | —       | 8%         | —       | 9%           | —       |

|             |             |             | PA[1]  | 4%                   | —       | 5%           | —       | 8%         | —       | 9%           | —       |

|             |             |             | PE[1]  | 4%                   | 6%      | 5%           | 6%      | 7%         | 10%     | 9%           | 9%      |

|             |             |             | PE[8]  | 4%                   | 6%      | 5%           | 6%      | 7%         | 10%     | 8%           | 9%      |

|             |             |             | PE[9]  | 4%                   | —       | 5%           | —       | 6%         | —       | 8%           | —       |

|             |             |             | PE[10] | 4%                   | —       | 5%           | —       | 6%         | —       | 7%           | —       |

|             |             |             | PA[0]  | 4%                   | 6%      | 5%           | 5%      | 6%         | 8%      | 7%           | 7%      |

|             |             |             | PE[11] | 4%                   | —       | 5%           | —       | 5%         | —       | 6%           | —       |

Table 23. I/O weight<sup>1</sup> (continued)

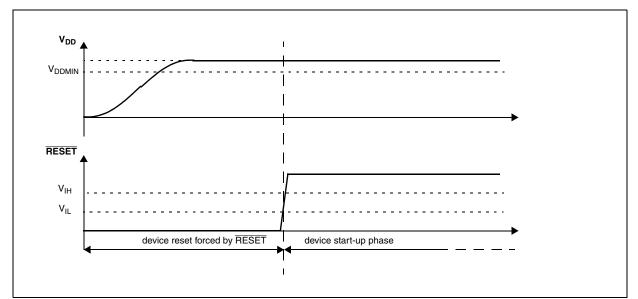

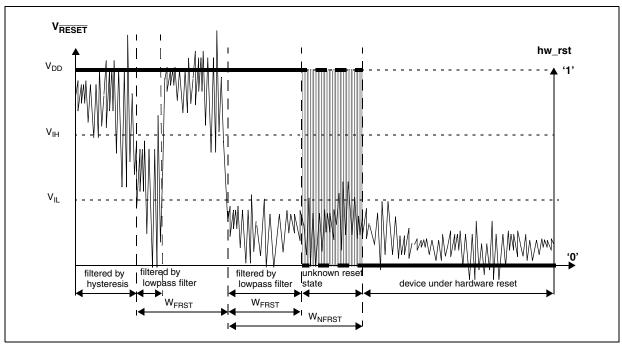

## 4.7 **RESET** electrical characteristics

The device implements a dedicated bidirectional  $\overline{\text{RESET}}$  pin.

Figure 7. Start-up reset requirements

Figure 8. Noise filtering on reset signal

| Symbol                | Ratings                                               | Conditions                                         | Class | Max value <sup>3</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------|-------|------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human Body Model) | $T_A = 25 \degree C$<br>conforming to AEC-Q100-002 | H1C   | 2000                   | V    |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage<br>(Machine Model)    | $T_A = 25 \degree C$<br>conforming to AEC-Q100-003 | M2    | 200                    |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage                       | $T_A = 25 \degree C$                               | C3A   | 500                    |      |

|                       | (Charged Device Model)                                | conforming to AEC-Q100-011                         |       | 750 (corners)          |      |

## Table 34. ESD absolute maximum ratings<sup>1,2</sup>

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

<sup>3</sup> Data based on characterization results, not tested in production

## 4.11.3.2 Static latch-up (LU)

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with the EIA/JESD 78 IC latch-up standard.

#### Table 35. Latch-up results

| Symbol | Parameter             | Conditions                                       | Class      |

|--------|-----------------------|--------------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = 125 \ ^{\circ}C$<br>conforming to JESD 78 | II level A |

# 4.12 Fast external crystal oscillator (4 to 16 MHz) electrical characteristics

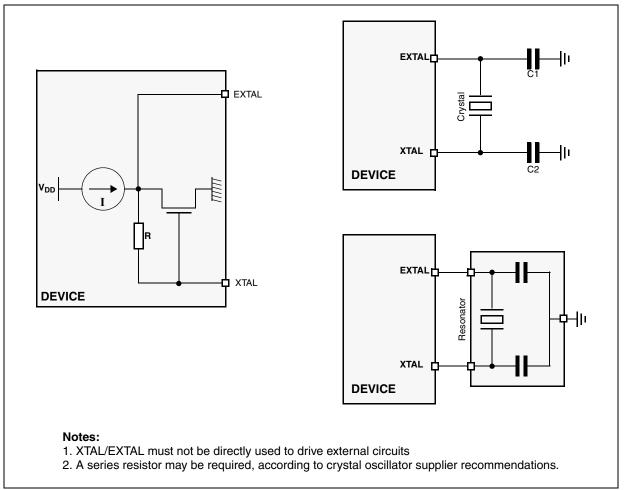

The device provides an oscillator/resonator driver. Figure 11 describes a simple model of the internal oscillator driver and provides an example of a connection for an oscillator or a resonator.

Table 36 provides the parameter description of 4 MHz to 16 MHz crystals used for the design simulations.

## Figure 11. Crystal oscillator and resonator connection scheme

Shunt Crystal Load on capacitance Crystal Crystal Nominal equivalent NDK crystal motional motional xtalin/xtalout between frequency series reference capacitance inductance C1 = C2 xtalout (MHz) resistance (C<sub>m</sub>) fF (L<sub>m</sub>) mH  $(pF)^1$ and xtalin **ESR**  $\Omega$ C0<sup>2</sup> (pF) 4 NX8045GB 300 2.68 591.0 21 2.93 8 NX5032GA 300 2.46 160.7 17 3.01 10 150 2.93 86.6 15 2.91 12 120 3.11 56.5 15 2.93 16 120 3.90 25.3 10 3.00

Table 36. Crystal description

The values specified for C1 and C2 are the same as used in simulations. It should be ensured that the testing includes all the parasitics (from the board, probe, crystal, etc.) as the AC / transient behavior depends upon them.

<sup>2</sup> The value of C0 specified here includes 2 pF additional capacitance for parasitics (to be seen with bond-pads, package, etc.).

| Symbol                |    | с | Parameter                                                                                                                                                 | C.                      | onditions <sup>1</sup> |    | Value |     | Unit |

|-----------------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|----|-------|-----|------|

| Symbol                |    | C | Faiametei                                                                                                                                                 |                         | Conditions             |    |       | Max | onn  |

| I <sub>FIRCSTOP</sub> | CC | Т | Fast internal RC oscillator high                                                                                                                          | T <sub>A</sub> = 25 °C  | sysclk = off           |    | 500   |     | μA   |

|                       |    |   | frequency and system clock<br>current in stop mode                                                                                                        |                         | sysclk = 2 MHz         |    | 600   |     |      |

|                       |    |   | ,                                                                                                                                                         |                         | sysclk = 4 MHz         |    | 700   |     |      |

|                       |    |   |                                                                                                                                                           |                         | sysclk = 8 MHz         |    | 900   |     |      |

|                       |    |   |                                                                                                                                                           |                         | sysclk = 16 MHz        |    | 1250  |     |      |

| t <sub>FIRCSU</sub>   | СС | С | Fast internal RC oscillator start-up time                                                                                                                 | V <sub>DD</sub> = 5.0 V | ± 10%                  |    | 1.1   | 2.0 | μs   |

| AFIRCPRE              | СС | С | Fast internal RC oscillator<br>precision after software<br>trimming of f <sub>FIRC</sub>                                                                  | T <sub>A</sub> = 25 °C  |                        | -1 | —     | 1   | %    |

| $\Delta_{FIRCTRIM}$   | СС | С | Fast internal RC oscillator trimming step                                                                                                                 | T <sub>A</sub> = 25 °C  |                        |    | 1.6   |     | %    |

|                       | СС | С | Fast internal RC oscillator<br>variation over temperature and<br>supply with respect to $f_{FIRC}$ at<br>$T_A = 25$ °C in high-frequency<br>configuration |                         | _                      | -5 |       | 5   | %    |

Table 41. Fast internal RC oscillator (16 MHz) electrical characteristics (continued)

$^{1}$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified

<sup>2</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

# 4.16 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz low power internal RC oscillator. This can be used as the reference clock for the RTC module.

Table 42. Slow internal RC oscillator (128 kHz) electrical characteristics

| Symbol                          | Symbol |   | Parameter                                                                          | Conditions <sup>1</sup>                           |     |     |     | Unit |

|---------------------------------|--------|---|------------------------------------------------------------------------------------|---------------------------------------------------|-----|-----|-----|------|

| Cymbol                          |        | С | i didineter                                                                        | Conditions                                        | Min | Тур | Max | onn  |

| f <sub>SIRC</sub>               | СС     | Ρ | Slow internal RC oscillator low                                                    | T <sub>A</sub> = 25 °C, trimmed                   |     | 128 | _   | kHz  |

|                                 | SR     | _ | frequency                                                                          | _                                                 | 100 | _   | 150 |      |

| I <sub>SIRC</sub> <sup>2,</sup> | СС     | - | Slow internal RC oscillator low<br>frequency current                               | T <sub>A</sub> = 25 °C, trimmed                   |     | _   | 5   | μA   |

| t <sub>SIRCSU</sub>             | СС     |   | Slow internal RC oscillator start-up time                                          | $T_A = 25 \ ^{\circ}C, V_{DD} = 5.0 \ V \pm 10\%$ |     | 8   | 12  | μs   |

| $\Delta_{SIRCPRE}$              | СС     |   | Slow internal RC oscillator precision after software trimming of f <sub>SIRC</sub> | T <sub>A</sub> = 25 °C                            | -2  |     | 2   | %    |

|                                 | СС     | С | Slow internal RC oscillator trimming step                                          | —                                                 | _   | 2.7 | _   |      |

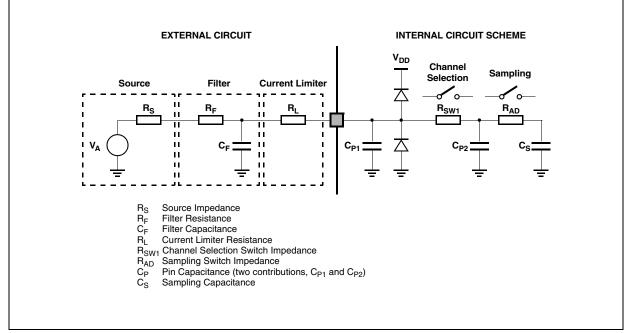

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance:  $C_S$  being substantially a switched capacitance, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (fc*C_S)$ , where fc represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S$ ) and the sum of  $R_S + R_F + R_L + R_{SW} + R_{AD}$ , the external circuit must be designed to respect the Equation 4:

Eqn. 4

$$V_A \bullet \frac{R_S + R_F + R_L + R_{SW} + R_{AD}}{R_{EQ}} < \frac{1}{2} LSB$$

Equation 4 generates a constraint for external network design, in particular on resistive path. Internal switch resistances ( $R_{SW}$  and  $R_{AD}$ ) can be neglected with respect to external resistances.

Figure 17. Input equivalent circuit (precise channels)

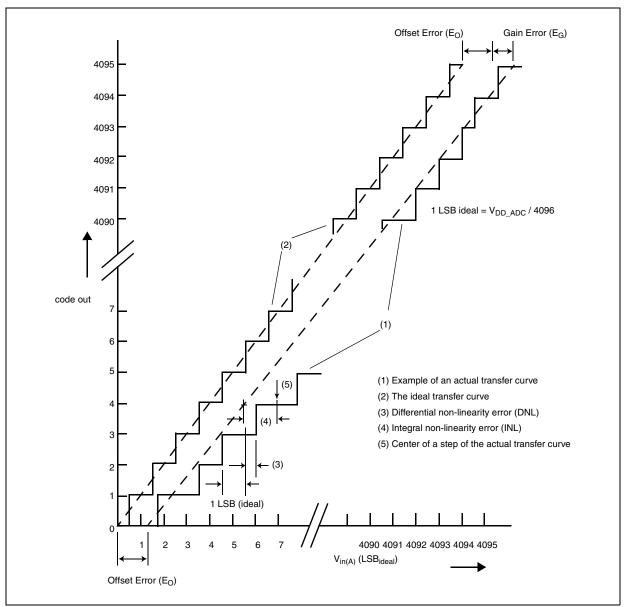

Figure 21. ADC\_1 characteristic and error definitions

| Table 45. ADC | 1 conversion | characteristics | (12-bit ADC 1) |

|---------------|--------------|-----------------|----------------|

|               |              |                 |                |

| Symbol               | 1  | с | Parameter                                                                                                 | Conditions <sup>1</sup> |                       | Unit |                       |     |

|----------------------|----|---|-----------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|------|-----------------------|-----|

| Cymbol               |    | Ŭ | i didineter                                                                                               |                         |                       | Тур  | Max                   | onn |

| V <sub>SS_ADC1</sub> | SR |   | Voltage on VSS_HV_ADC1<br>(ADC_1 reference) pin with<br>respect to ground (V <sub>SS</sub> ) <sup>2</sup> | _                       | -0.1                  |      | 0.1                   | V   |

| V <sub>DD_ADC1</sub> | SR |   | Voltage on VDD_HV_ADC1 pin<br>(ADC_1 reference) with<br>respect to ground (V <sub>SS</sub> )              | _                       | V <sub>DD</sub> – 0.1 |      | V <sub>DD</sub> + 0.1 | V   |

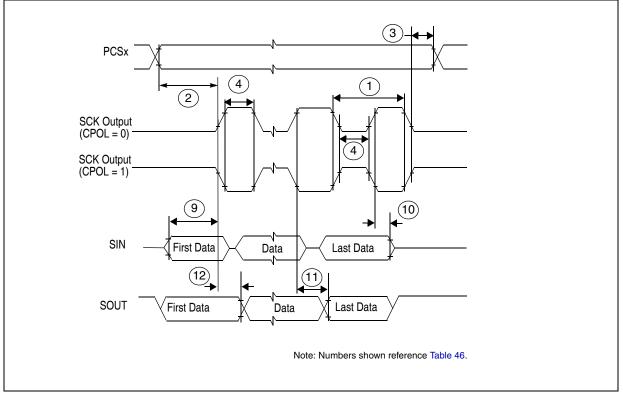

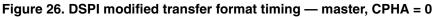

Figure 27. DSPI modified transfer format timing — master, CPHA = 1

MPC5607B Microcontroller Data Sheet, Rev. 6

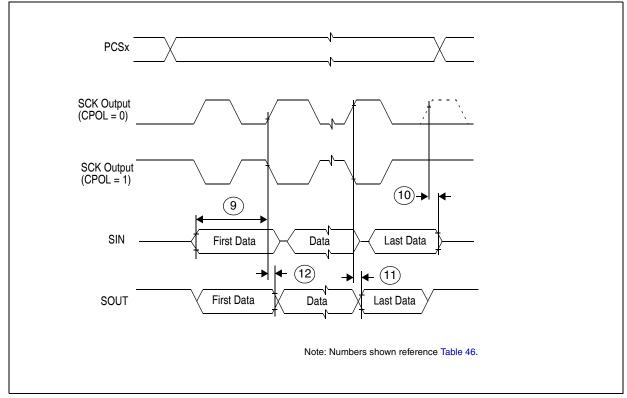

Figure 34. 176 LQFP package mechanical drawing (Part 2 of 3)

| Revision | Date        | Substantive changes                                                                                                                                                     |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | 24 Aug 2010 | Editorial changes and improvements.                                                                                                                                     |

|          | -           | Updated "Features" section                                                                                                                                              |

|          |             | Table 1: updated footnote concerning 208 MAPBGA                                                                                                                         |

|          |             | In the block diagram:                                                                                                                                                   |

|          |             | Added "5ch 12-bit ADC" block.                                                                                                                                           |

|          |             | Updated Legend.                                                                                                                                                         |

|          |             | <ul> <li>Added "Interrupt request with wakeup functionality" as an input to the WKPU block.</li> </ul>                                                                  |

|          |             | Figure 2: removed alternate functions                                                                                                                                   |

|          |             | Figure 3: removed alternate functions                                                                                                                                   |

|          |             | Figure 4: removed alternate functions                                                                                                                                   |

|          |             | Table 2: added contents concerning the following blocks: CMU, eDMA, ECSM, MC_ME                                                                                         |

|          |             | MC_PCU, NMI, SSCM, SWT and WKPU                                                                                                                                         |

|          |             | Added Section 3.2, Pin muxing                                                                                                                                           |

|          |             | Section 4, "Electrical characteristics: removed "Caution" note                                                                                                          |

|          |             | Section 4.2, "NVUSRO register: removed "NVUSRO[WATCHDOG_EN] field description                                                                                           |

|          |             | section<br>Table 11: V <sub>IN</sub> : removed min value in "relative to V <sub>DD</sub> " row                                                                          |

|          |             | Table 12                                                                                                                                                                |

|          |             | <ul> <li>TA C-Grade Part, TJ C-Grade Part, TA V-Grade Part, TJ V-Grade Part, TA M-Grade Part, TJ M-Grade Part<br/>added new rows</li> </ul>                             |

|          |             | <ul> <li>TV<sub>DD</sub>: contents merged into one row</li> </ul>                                                                                                       |

|          |             | <ul> <li>V<sub>DD BV</sub>: changed min value in "relative to V<sub>DD</sub>" row</li> </ul>                                                                            |

|          |             | Section 4.5, "Thermal characteristics                                                                                                                                   |

|          |             | • Section 4.5.1, "External ballast resistor recommendations: added new paragraph                                                                                        |

|          |             | about power supply                                                                                                                                                      |

|          |             | <ul> <li>Table 14: added R<sub>AJB</sub> and R<sub>AJC</sub> rows</li> </ul>                                                                                            |

|          |             | <ul> <li>Removed "208 MAPBGA thermal characteristics" table</li> </ul>                                                                                                  |

|          |             | Table 15: rewrote parameter description of W <sub>FI</sub> and W <sub>NFI</sub>                                                                                         |

|          |             | Section 4.6.5, "I/O pad current specification                                                                                                                           |

|          |             | <ul> <li>Removed I<sub>DYNSEG</sub> information</li> </ul>                                                                                                              |

|          |             | <ul> <li>Updated "I/O supply segments" table</li> </ul>                                                                                                                 |

|          |             | Table 22: removed I <sub>DYNSEG</sub> row                                                                                                                               |

|          |             | Added Table 23                                                                                                                                                          |

|          |             | Table 25                                                                                                                                                                |

|          |             | Updated all values                                                                                                                                                      |

|          |             | Removed I <sub>VREGREF</sub> and I <sub>VREDLVD12</sub> rows                                                                                                            |

|          |             | Added the footnote "The duration of the in-rush current depends on the capacitance     placed on LV pipe, BV decape must be sized accordingly. Befor to IMPEC value for |

|          |             | placed on LV pins. BV decaps must be sized accordingly. Refer to IMREG value for                                                                                        |

|          |             | minimum amount of current to be provided in cc." to the I <sub>DD_BV</sub> specification.<br>Table 26                                                                   |

|          |             | Updated V <sub>PORH</sub> min/max value                                                                                                                                 |

|          |             | Updated V <sub>LVDLVCORL</sub> min value                                                                                                                                |

|          |             | Updated Table 27                                                                                                                                                        |

|          |             | Table 28                                                                                                                                                                |

|          |             | T <sub>dwprogram</sub> : added initial max value                                                                                                                        |

|          |             | <ul> <li>Inserted T<sub>eslat</sub> row</li> </ul>                                                                                                                      |