Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                           |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 120MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, LINbus, SPI, UART, USB                |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                          |

| Number of I/O              | 55                                                                                 |

| Program Memory Size        | 1MB (1M x 8)                                                                       |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 160K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                      |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                              |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-100-11                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4500f100f1024abxqma1 |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### About this Document

# About this Document

This Data Sheet is addressed to embedded hardware and software developers. It provides the reader with detailed descriptions about the ordering designations, available features, electrical and physical characteristics of the XMC4500 series devices.

The document describes the characteristics of a superset of the XMC4500 series devices. For simplicity, the various device types are referred to by the collective term XMC4500 throughout this manual.

#### XMC4000 Family User Documentation

The set of user documentation includes:

- Reference Manual

- decribes the functionality of the superset of devices.

- Data Sheets

- list the complete ordering designations, available features and electrical characteristics of derivative devices.

- Errata Sheets

- list deviations from the specifications given in the related Reference Manual or Data Sheets. Errata Sheets are provided for the superset of devices.

# Attention: Please consult all parts of the documentation set to attain consolidated knowledge about your device.

Application related guidance is provided by Users Guides and Application Notes.

Please refer to http://www.infineon.com/xmc4000 to get access to the latest versions of those documents.

#### **General Device Information**

# 2 General Device Information

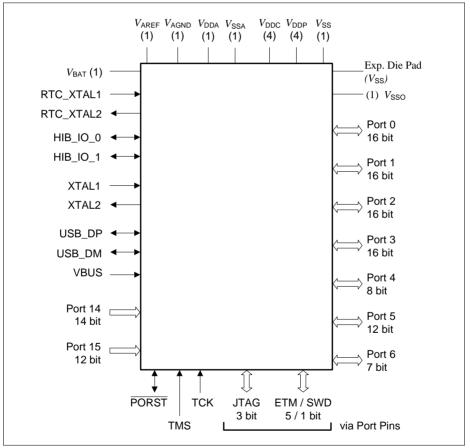

This section summarizes the logic symbols and package pin configurations with a detailed list of the functional I/O mapping.

# 2.1 Logic Symbols

Figure 2 XMC4500 Logic Symbol PG-LQFP-144

#### **General Device Information**

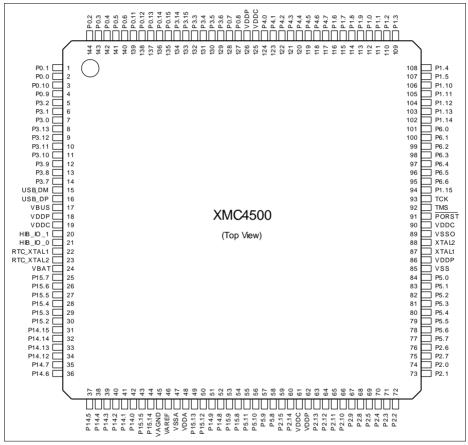

# 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the four sides of the different packages.

. .

#### **General Device Information**

| Table 9Package Pin Mapping (cont'd) |          |           |          |          |                                                              |  |  |  |  |

|-------------------------------------|----------|-----------|----------|----------|--------------------------------------------------------------|--|--|--|--|

| Function                            | LQFP-144 | LFBGA-144 | LQFP-100 | Pad Type | Notes                                                        |  |  |  |  |

| RTC_XTAL1                           | 22       | F2        | 15       | clock_IN |                                                              |  |  |  |  |

| RTC_XTAL2                           | 23       | F1        | 16       | clock_O  |                                                              |  |  |  |  |

| VBAT                                | 24       | G1        | 17       | Power    | When VDDP is supplied<br>VBAT has to be supplied<br>as well. |  |  |  |  |

| VBUS                                | 17       | E2        | 10       | special  |                                                              |  |  |  |  |

| VAREF                               | 46       | M3        | 33       | AN_Ref   |                                                              |  |  |  |  |

| VAGND                               | 45       | M2        | 32       | AN_Ref   |                                                              |  |  |  |  |

| VDDA                                | 48       | L1        | 35       | AN_Power |                                                              |  |  |  |  |

| VSSA                                | 47       | M1        | 34       | AN_Power |                                                              |  |  |  |  |

| VDDC                                | 19       | -         | 12       | Power    |                                                              |  |  |  |  |

| VDDC                                | 61       | -         | 42       | Power    |                                                              |  |  |  |  |

| VDDC                                | 90       | -         | 64       | Power    |                                                              |  |  |  |  |

| VDDC                                | 125      | -         | 86       | Power    |                                                              |  |  |  |  |

| VDDC                                | -        | A2        | -        | Power    |                                                              |  |  |  |  |

| VDDC                                | -        | B12       | -        | Power    |                                                              |  |  |  |  |

| VDDC                                | -        | M11       | -        | Power    |                                                              |  |  |  |  |

| VDDP                                | 18       | -         | 11       | Power    |                                                              |  |  |  |  |

| VDDP                                | 62       | -         | 43       | Power    |                                                              |  |  |  |  |

| VDDP                                | 86       | -         | 60       | Power    |                                                              |  |  |  |  |

| VDDP                                | 126      | -         | 87       | Power    |                                                              |  |  |  |  |

| VDDP                                | -        | A11       | -        | Power    |                                                              |  |  |  |  |

| VDDP                                | -        | B1        | -        | Power    |                                                              |  |  |  |  |

| VDDP                                | -        | L12       | -        | Power    |                                                              |  |  |  |  |

| VSS                                 | 85       | -         | 59       | Power    |                                                              |  |  |  |  |

| VSS                                 | -        | A1        | -        | Power    |                                                              |  |  |  |  |

| VSS                                 | -        | A12       | -        | Power    |                                                              |  |  |  |  |

| VSS                                 | -        | M12       | -        | Power    |                                                              |  |  |  |  |

# 2.3 Power Connection Scheme

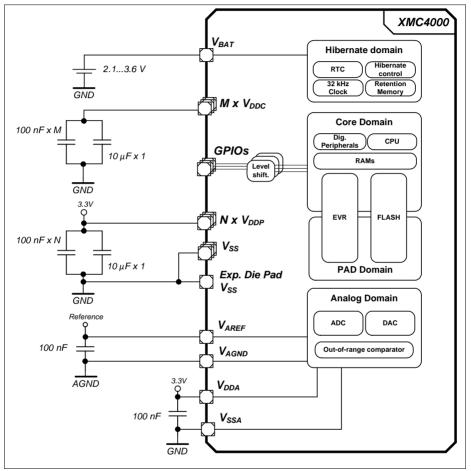

Figure 9. shows a reference power connection scheme for the XMC4500.

#### Figure 9 Power Connection Scheme

Every power supply pin needs to be connected. Different pins of the same supply need also to be externally connected. As example, all  $V_{\rm DDP}$  pins must be connected externally to one  $V_{\rm DDP}$  net. In this reference scheme one 100 nF capacitor is connected at each supply pin against  $V_{\rm SS}$ . An additional 10 µF capacitor is connected to the  $V_{\rm DDP}$  nets and an additional 10 µF capacitor to the  $V_{\rm DDP}$  nets.

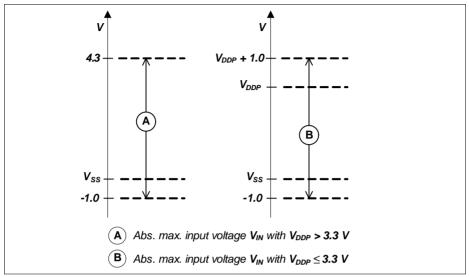

Figure 10 Absolute Maximum Input Voltage Ranges

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 13 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload conditions, then the parameters of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

38

#### Table 21 Standard Pads Class\_A1+

| Parameter                | Symbol               | Va                     | lues | Unit | Note /                                                                  |

|--------------------------|----------------------|------------------------|------|------|-------------------------------------------------------------------------|

|                          |                      | Min.                   | Max. |      | Test Condition                                                          |

| Output high voltage,     | V <sub>OHA1+</sub>   | V <sub>DDP</sub> - 0.4 | -    | V    | $I_{OH} \ge$ -400 $\mu$ A                                               |

| POD <sup>1)</sup> = weak | CC                   | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -500 μA                                        |

| Output high voltage,     | _                    | V <sub>DDP</sub> - 0.4 | -    | V    | <i>I</i> <sub>OH</sub> ≥ -1.4 mA                                        |

| $POD^{1)} = medium$      |                      | 2.4                    | -    | V    | <i>I</i> <sub>OH</sub> ≥ -2 mA                                          |

| Output high voltage,     |                      | V <sub>DDP</sub> - 0.4 | -    | V    | $I_{\rm OH} \ge$ -1.4 mA                                                |

| $POD^{1)} = strong$      |                      | 2.4                    | _    | V    | $I_{\rm OH} \ge$ -2 mA                                                  |

| Output low voltage       | $V_{\rm OLA1+}$ CC   | -                      | 0.4  | V    | $I_{OL} \le 500 \ \mu A;$<br>POD <sup>1)</sup> = weak                   |

|                          |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = medium                |

|                          |                      | -                      | 0.4  | V    | $I_{OL} \le 2 \text{ mA};$<br>POD <sup>1)</sup> = strong                |

| Fall time                | t <sub>FA1+</sub> CC | -                      | 150  | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak                    |

|                          |                      | -                      | 50   | ns   | $C_{\rm L}$ = 50 pF;<br>POD <sup>1)</sup> = medium                      |

|                          |                      | -                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |

|                          |                      | _                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft; |

| Rise time                | t <sub>RA1+</sub> CC | -                      | 150  | ns   | $C_{L} = 20 \text{ pF};$<br>POD <sup>1)</sup> = weak                    |

|                          |                      | -                      | 50   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = medium                  |

|                          |                      | -                      | 28   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = slow  |

|                          |                      | -                      | 16   | ns   | $C_{L} = 50 \text{ pF};$<br>POD <sup>1)</sup> = strong;<br>edge = soft  |

1) POD = Pin Out Driver

| Conditions apply)                                   |                     |       |        |       |      |                                  |  |  |  |  |

|-----------------------------------------------------|---------------------|-------|--------|-------|------|----------------------------------|--|--|--|--|

| Parameter                                           | Symbol              |       | Values | 5     | Unit | Note /                           |  |  |  |  |

|                                                     |                     | Min.  | Тур.   | Max.  |      | Test Condition                   |  |  |  |  |

| Input low voltage                                   | $V_{\rm IL}$ SR     | -     | -      | 0.8   | V    |                                  |  |  |  |  |

| Input high voltage<br>(driven)                      | V <sub>IH</sub> SR  | 2.0   | -      | -     | V    |                                  |  |  |  |  |

| Input high voltage<br>(floating) <sup>1)</sup>      | V <sub>IHZ</sub> SR | 2.7   | -      | 3.6   | V    |                                  |  |  |  |  |

| Differential input sensitivity                      | V <sub>DIS</sub> CC | 0.2   | -      | -     | V    |                                  |  |  |  |  |

| Differential common mode range                      | V <sub>CM</sub> CC  | 0.8   | -      | 2.5   | V    |                                  |  |  |  |  |

| Output low voltage                                  | V <sub>OL</sub> CC  | 0.0   | -      | 0.3   | V    | 1.5 kOhm pull-<br>up to 3.6 V    |  |  |  |  |

| Output high voltage                                 | V <sub>OH</sub> CC  | 2.8   | -      | 3.6   | V    | 15 kOhm pull-<br>down to 0 V     |  |  |  |  |

| DP pull-up resistor (idle bus)                      | R <sub>PUI</sub> CC | 900   | -      | 1 575 | Ohm  |                                  |  |  |  |  |

| DP pull-up resistor<br>(upstream port<br>receiving) | R <sub>PUA</sub> CC | 1 425 | -      | 3 090 | Ohm  |                                  |  |  |  |  |

| DP, DM pull-down resistor                           | R <sub>PD</sub> CC  | 14.25 | -      | 24.8  | kOhm |                                  |  |  |  |  |

| Input impedance DP,<br>DM                           | Z <sub>INP</sub> CC | 300   | -      | -     | kOhm | $0 \ V \leq V_{IN} \leq V_{DDP}$ |  |  |  |  |

| Driver output resistance<br>DP, DM                  | Z <sub>DRV</sub> CC | 28    | -      | 44    | Ohm  |                                  |  |  |  |  |

# Table 29 USB OTG Data Line (USB\_DP, USB\_DM) Parameters (Operating Conditions apply)

Measured at A-connector with 1.5 kOhm ± 5% to 3.3 V ± 0.3 V connected to USB\_DP or USB\_DM and at Bconnector with 15 kOhm ± 5% to ground connected to USB\_DP and USB\_DM.

# 3.2.9 Flash Memory Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                                                 | Symbol                                      |      | Value | S    | Unit  | Note /                                                                                       |

|---------------------------------------------------------------------------|---------------------------------------------|------|-------|------|-------|----------------------------------------------------------------------------------------------|

|                                                                           |                                             | Min. | Тур.  | Max. |       | Test Condition                                                                               |

| Erase Time per 256<br>Kbyte Sector                                        | $t_{\sf ERP}\sf CC$                         | _    | 5     | 5.5  | S     |                                                                                              |

| Erase Time per 64 Kbyte<br>Sector                                         | t <sub>ERP</sub> CC                         | _    | 1.2   | 1.4  | S     |                                                                                              |

| Erase Time per 16 Kbyte<br>Logical Sector                                 | $t_{\sf ERP}\sf CC$                         | -    | 0.3   | 0.4  | S     |                                                                                              |

| Program time per page <sup>1)</sup>                                       | t <sub>PRP</sub> CC                         | -    | 5.5   | 11   | ms    |                                                                                              |

| Erase suspend delay                                                       | t <sub>FL_ErSusp</sub>                      | -    | -     | 15   | ms    |                                                                                              |

| Wait time after margin change                                             | t <sub>FL_Margin</sub><br><sub>Del</sub> CC | 10   | -     | -    | μs    |                                                                                              |

| Wake-up time                                                              | t <sub>WU</sub> CC                          | -    | -     | 270  | μS    |                                                                                              |

| Read access time                                                          | t <sub>a</sub> CC                           | 22   | -     | -    | ns    | For operation<br>with 1 / $f_{CPU} < t_a$<br>wait states must<br>be configured <sup>2)</sup> |

| Data Retention Time,<br>Physical Sector <sup>3)4)</sup>                   | t <sub>RET</sub> CC                         | 20   | -     | -    | years | Max. 1000<br>erase/program<br>cycles                                                         |

| Data Retention Time,<br>Logical Sector <sup>3)4)</sup>                    | t <sub>RETL</sub> CC                        | 20   | -     | -    | years | Max. 100<br>erase/program<br>cycles                                                          |

| Data Retention Time,<br>User Configuration Block<br>(UCB) <sup>3)4)</sup> | t <sub>RTU</sub> CC                         | 20   | -     | -    | years | Max. 4<br>erase/program<br>cycles per UCB                                                    |

#### Table 33 Flash Memory Parameters

1) In case the Program Verify feature detects weak bits, these bits will be programmed once more. The reprogramming takes an additional time of 5.5 ms.

68

2) The following formula applies to the wait state configuration: FCON.WSPFLASH × (1 /  $f_{CPU}$ )  $\geq t_a$ .

3) Storage and inactive time included.

4) Values given are valid for an average weighted junction temperature of  $T_{\rm J}$  = 110°C.

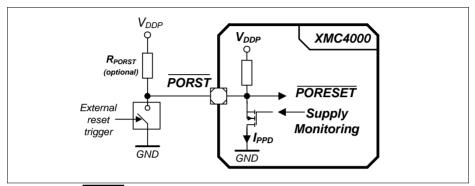

# 3.3.2 Power-Up and Supply Monitoring

PORST is always asserted when  $V_{\text{DDP}}$  and/or  $V_{\text{DDC}}$  violate the respective thresholds.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

# Figure 25 PORST Circuit

| Table 34 | Supply Monitoring Parameters |  |

|----------|------------------------------|--|

|----------|------------------------------|--|

| Parameter                                                       | Symbol                   |                    | Value | s                  | Unit | Note /<br>Test Condition                                                                                         |  |

|-----------------------------------------------------------------|--------------------------|--------------------|-------|--------------------|------|------------------------------------------------------------------------------------------------------------------|--|

|                                                                 |                          | Min.               | Тур.  | Max.               |      |                                                                                                                  |  |

| Digital supply voltage reset threshold                          | V <sub>POR</sub> CC      | 2.79 <sup>1)</sup> | -     | 3.05 <sup>2)</sup> | V    | 3)                                                                                                               |  |

| Core supply voltage reset threshold                             | V <sub>PV</sub> CC       | -                  | -     | 1.17               | V    |                                                                                                                  |  |

| $V_{\text{DDP}}$ voltage to ensure defined pad states           | V <sub>DDPPA</sub><br>CC | -                  | 1.0   | -                  | V    |                                                                                                                  |  |

| PORST rise time                                                 | t <sub>PR</sub> SR       | -                  | _     | 2                  | μS   | 4)                                                                                                               |  |

| Startup time from power-on reset with code execution from Flash | t <sub>SSW</sub> CC      | -                  | 2.5   | 3.5                | ms   | Time to the first<br>user code<br>instruction                                                                    |  |

| $V_{ m DDC}$ ramp up time                                       | t <sub>VCR</sub> CC      | _                  | 550   | _                  | μS   | Ramp up after<br>power-on or<br>after a reset<br>triggered by a<br>violation of<br>$V_{\rm POR}$ or $V_{\rm PV}$ |  |

1) Minimum threshold for reset assertion.

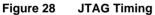

## Table 44 USIC SSC Slave Mode Timing

| 5                                                                                         |                        |      |      |        |      |      |                |  |  |  |

|-------------------------------------------------------------------------------------------|------------------------|------|------|--------|------|------|----------------|--|--|--|

| Parameter                                                                                 | Syn                    | nbol |      | Values | S    | Unit | Note /         |  |  |  |

|                                                                                           |                        |      | Min. | Тур.   | Max. |      | Test Condition |  |  |  |

| DX1 slave clock period                                                                    | t <sub>CLK</sub>       | SR   | 66.6 | -      | -    | ns   |                |  |  |  |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>               | t <sub>10</sub>        | SR   | 3    | -      | -    | ns   |                |  |  |  |

| Select input DX2 hold after<br>last clock input DX1 receive<br>edge <sup>1)</sup>         | <i>t</i> <sub>11</sub> | SR   | 4    | _      | _    | ns   |                |  |  |  |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | <i>t</i> <sub>12</sub> | SR   | 6    | _      | _    | ns   |                |  |  |  |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | t <sub>13</sub>        | SR   | 4    | -      | _    | ns   |                |  |  |  |

| Data output DOUT[3:0] valid time                                                          | t <sub>14</sub>        | СС   | 0    | -      | 24   | ns   |                |  |  |  |

This input timing is valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

Figure 33 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration, for which the slave select signal is low-active, and the serial clock signal is not shifted and not inverted.

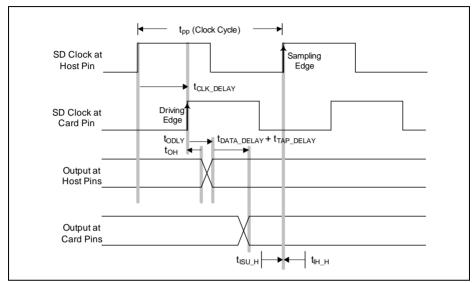

# Full-Speed Input Path (Read)

Figure 38 Full-Speed Input Path

# Full-Speed Read Meeting Setup (Maximum Delay)

The following equations show how to calculate the allowed combined propagation delay range of the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(5)

```

t_{\text{CLK\_DELAY}} + t_{\text{DATA\_DELAY}} + t_{\text{TAP\_DELAY}} + t_{\text{ODLY}} + t_{\text{ISU\_F}} < 0.5 \times t_{\text{pp}}

```

$t_{\text{CLK\_DELAY}} + t_{\text{DATA\_DELAY}} < 0.5 \times t_{pp} - t_{\text{ODLY}} - t_{\text{ISU\_F}} - t_{\text{TAP\_DELAY}}$

$t_{\mathrm{CLK\_DELAY}} + t_{\mathrm{DATA\_DELAY}} < 20 - 14 - 2 - t_{\mathrm{TAP\_DELAY}}$

$t_{\rm CLK\_DELAY} + t_{\rm DATA\_DELAY} < 4 - t_{\rm TAP\_DELAY}$

The data + clock delay can be up to 4 ns for a 40 ns clock cycle.

### Full-Speed Read Meeting Hold (Minimum Delay)

The following equations show how to calculate the allowed combined propagation delay range of the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(6)

$t_{CLK\_DELAY} + t_{OH} + t_{DATA\_DELAY} + t_{TAP\_DELAY} > t_{IH\_F}$

$t_{\mathrm{CLK\_DELAY}} + t_{\mathrm{DATA\_DELAY}} > t_{\mathrm{IH\_F}} - t_{\mathrm{OH}} - t_{\mathrm{TAP\_DELAY}}$

$t_{\text{CLK\_DELAY}} + t_{\text{DATA\_DELAY}} > 2 - t_{\text{TAP\_DELAY}}$

The data + clock delay must be greater than 2 ns if  $t_{TAP DELAY}$  is not used.

If the  $t_{TAP\_DELAY}$  is programmed to at least 2 ns, the data + clock delay must be greater than 0 ns (or less). This is always fulfilled.

#### AC Timing Specifications (High-Speed Mode)

| Parameter                                                | Symbol               |                 | Values | 5    | Unit | Note/ Test<br>Condition |

|----------------------------------------------------------|----------------------|-----------------|--------|------|------|-------------------------|

|                                                          |                      |                 | Min.   | Max. |      |                         |

| Clock frequency in high speed transfer mode $(1/t_{pp})$ | $f_{\rm pp}$         | СС              | 0      | 48   | MHz  |                         |

| Clock cycle in high speed transfer mode                  | t <sub>pp</sub>      | СС              | 20     | _    | ns   |                         |

| Clock low time                                           | t <sub>WL</sub>      | СС              | 7      | -    | ns   |                         |

| Clock high time                                          | t <sub>WH</sub>      | СС              | 7      | -    | ns   |                         |

| Clock rise time                                          | t <sub>TLH</sub>     | СС              | -      | 3    | ns   |                         |

| Clock fall time                                          | t <sub>THL</sub>     | CC              | -      | 3    | ns   |                         |

| Inputs setup to clock rising edge                        | t <sub>ISU_H</sub>   | SR              | 2      | _    | ns   |                         |

| Inputs hold after clock rising edge                      | t <sub>IH_H</sub>    | SR              | 2      | -    | ns   |                         |

| Outputs valid time in high speed mode                    | t <sub>ODLY_</sub> H | <sup>1</sup> CC | -      | 14   | ns   |                         |

| Outputs hold time in high speed mode                     | t <sub>OH_H</sub>    | СС              | 2      | -    | ns   |                         |

#### Table 51 SDMMC Timing for High-Speed Mode

| No clock delay:   |                                                                                                                                                     | (7) |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                   | $t_{ODLY\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL}$                                                                                 |     |

| With clock delay: |                                                                                                                                                     |     |

|                   | f . f . f . f . f                                                                                                                                   | (8) |

|                   | $t_{ODLY\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL} + t_{CLK\_DELAY}$                                                                |     |

|                   |                                                                                                                                                     | (9) |

|                   | $t_{DATA\_DELAY} + t_{TAP\_DELAY} - t_{CLK\_DELAY} < t_{WL} - t_{ISU} - t_{ODLY\_H}$                                                                |     |

|                   | $t_{\text{DATA}\_\text{DELAY}} - t_{\text{CLK}\_\text{DELAY}} < t_{\text{WL}} - t_{\text{ISU}} - t_{\text{ODLY}\_H} - t_{\text{TAP}\_\text{DELAY}}$ |     |

|                   | $t_{DATA\_DELAY} - t_{CLK\_DELAY} < 10 - 6 - 14 - t_{TAP\_DELAY}$                                                                                   |     |

|                   | $t_{\text{DATA\_DELAY}} - t_{\text{CLK\_DELAY}} < -10 - t_{\text{TAP\_DELAY}}$                                                                      |     |

The data delay is less than the clock delay by at least 10 ns in the ideal case where  $t_{WL}$ = 10 ns.

#### High-Speed Write Meeting Hold (Minimum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(10)

$t_{\mathrm{CLK\_DELAY}} < t_{\mathrm{WL}} + t_{\mathrm{OH\_H}} + t_{\mathrm{DATA\_DELAY}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{IH}}$

$t_{\mathrm{CLK\_DELAY}} - t_{\mathrm{DATA\_DELAY}} < t_{\mathrm{WL}} + t_{\mathrm{OH\_H}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{IH}}$

$t_{\mathrm{CLK\_DELAY}} - t_{\mathrm{DATA\_DELAY}} < 10 + 2 + t_{\mathrm{TAP\_DELAY}} - 2$

$t_{\rm CLK\_DELAY} - t_{\rm DATA\_DELAY} < 10 + t_{\rm TAP\_DELAY}$

The clock can be delayed versus data up to 13.2 ns (external delay line) in ideal case of  $t_{WL}$ = 10 ns, with maximum  $t_{TAP DELAY}$  = 3.2 ns programmed.

## Write Timing

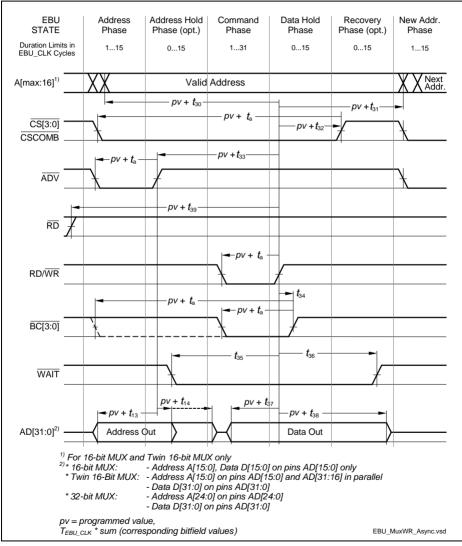

# Table 55 Asynchronous Write Timing, Multiplexed and Demultiplexed

| Parameter            | Symbol                      | Limit Values |                 | Unit |      |    |

|----------------------|-----------------------------|--------------|-----------------|------|------|----|

|                      |                             |              |                 | Min. | Max. |    |

| A(24:0) output delay | to RD/WR rising             | CC           | t <sub>30</sub> | -2.5 | 2.5  | ns |

| A(24:0) output delay | edge, deviation from        | CC           | t <sub>31</sub> | -2.5 | 2.5  |    |

| CS rising edge       | the ideal programmed value. | CC           | t <sub>32</sub> | -2   | 2    |    |

| ADV rising edge      |                             | CC           | t <sub>33</sub> | -2   | 4.5  |    |

| BC rising edge       |                             | CC           | t <sub>34</sub> | -2.5 | 2    |    |

| WAIT input setup     |                             | SR           | t <sub>35</sub> | 12   | -    |    |

| WAIT input hold      |                             | SR           | t <sub>36</sub> | 0    | -    |    |

| Data output delay    |                             | CC           | t <sub>37</sub> | -5.5 | 2    |    |

| Data output delay    |                             | CC           | t <sub>38</sub> | -5.5 | 2    |    |

| RD / WR output delay |                             | CC           | t <sub>39</sub> | -2.5 | 1.5  |    |

## Multiplexed Write Timing

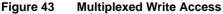

# 3.3.10.2 EBU Burst Mode Access Timing

- Note: These parameters are not subject to production test, but verified by design and/or characterization.

- Note: Operating Conditions apply, with Class A2 pins and  $C_1 = 16 \text{ pF}$ .

| Parameter                                                                 | Symbol                  |    |      | Values | 5    | Unit | Note /         |

|---------------------------------------------------------------------------|-------------------------|----|------|--------|------|------|----------------|

|                                                                           |                         |    | Min. | Тур.   | Max. |      | Test Condition |

| Output delay from BFCLKO rising edge                                      | t <sub>10</sub>         | CC | -2   | -      | 2    | ns   | -              |

| RD and RD/WR<br>active/inactive after<br>BFCLKO active edge <sup>1)</sup> | t <sub>12</sub>         | CC | -2   | -      | 2    | ns   | -              |

| CSx output delay from<br>BFCLKO active edge <sup>1)</sup>                 | <i>t</i> <sub>21</sub>  | CC | -2.5 | -      | 1.5  | ns   | -              |

| ADV active/inactive after<br>BFCLKO active edge <sup>2)</sup>             | t <sub>22</sub>         | CC | -2   | -      | 2    | ns   | -              |

| BAA active/inactive after<br>BFCLKO active edge <sup>2)</sup>             | <i>t</i> <sub>22a</sub> | CC | -2.5 | -      | 1.5  | ns   | -              |

| Data setup to BFCLKI rising edge <sup>3)</sup>                            | <i>t</i> <sub>23</sub>  | SR | 3    | -      | -    | ns   | -              |

| Data hold from BFCLKI rising edge <sup>3)</sup>                           | <i>t</i> <sub>24</sub>  | SR | 0    | -      | -    | ns   | -              |

| WAIT setup (low or high) to BFCLKI rising edge <sup>3)</sup>              | t <sub>25</sub>         | SR | 3    | -      | -    | ns   | -              |

| WAIT hold (low or high) from BFCLKI rising edge <sup>3)</sup>             | t <sub>26</sub>         | SR | 0    | -      | -    | ns   | -              |

#### Table 56 EBU Burst Mode Read / Write Access Timing Parameters

1) An active edge can be a rising or falling edge, depending on the settings of bits BFCON.EBSE / ECSE and the clock divider ratio.

Negative minimum values for these parameters mean that the last data read during a burst may be corrupted. However, with clock feedback enabled, this value is an oversampling not required for the internal bus transaction, and will be discarded.

2) This parameter is valid for BUSCONx.EBSE = 1 and BUSAPx.EXTCLK = 00<sub>B</sub>.

For BUSCONx.EBSE = 1 and other values of BUSAPx.EXTCLK, ADV and BAA will be delayed by 1/2 of the internal bus clock period  $T_{CPU}$  = 1 /  $f_{CPU}$ .

For BUSCONx. EBSE = 0 and BUSAPx.EXTCLK =  $11_B$ , add 2 internal bus clock periods.

For BUSCONx. EBSE = 0 and other values of BUSAPx.EXTCLK, add 1 internal bus clock period.

# XMC4500 XMC4000 Family

#### **Electrical Parameters**

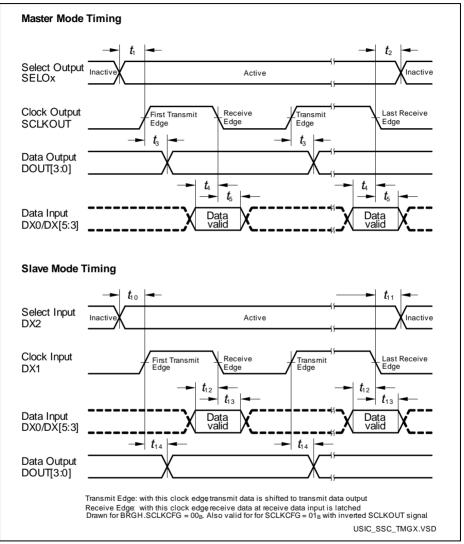

Figure 49 EBU SDRAM Write Access Timing