Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | ARM® Cortex®-M4                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | DMA, I <sup>2</sup> S, LED, POR, PWM, WDT                                         |

| Number of I/O              | 91                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 3.63V                                                                     |

| Data Converters            | A/D 32x12b; D/A 2x12b                                                             |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 144-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-144-18                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc4504f144k512acxqma1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

• Flexible CRC Engine (FCE) for multiple bit error detection

#### **On-Chip Memories**

- 16 KB on-chip boot ROM

- 64 KB on-chip high-speed program memory

- 64 KB on-chip high speed data memory

- 32 KB on-chip high-speed communication

- 1024 KB on-chip Flash Memory with 4 KB instruction cache

### **Communication Peripherals**

- Ethernet MAC module capable of 10/100 Mbit/s transfer rates

- Universal Serial Bus, USB 2.0 host, Full-Speed OTG, with integrated PHY

- Controller Area Network interface (MultiCAN), Full-CAN/Basic-CAN with 3 nodes, 64 message objects (MO), data rate up to 1MBit/s

- Six Universal Serial Interface Channels (USIC), providing 6 serial channels, usable as UART, double-SPI, quad-SPI, IIC, IIS and LIN interfaces

- LED and Touch-Sense Controller (LEDTS) for Human-Machine interface

- SD and Multi-Media Card interface (SDMMC) for data storage memory cards

- External Bus Interface Unit (EBU) enabling communication with external memories and off-chip peripherals

## **Analog Frontend Peripherals**

- Four Analog-Digital Converters (VADC) of 12-bit resolution, 8 channels each, with input out-of-range comparators

- Delta Sigma Demodulator with four channels, digital input stage for A/D signal conversion

- Digital-Analogue Converter (DAC) with two channels of 12-bit resolution

#### **Industrial Control Peripherals**

- Two Capture/Compare Units 8 (CCU8) for motor control and power conversion

- Four Capture/Compare Units 4 (CCU4) for use as general purpose timers

- Two Position Interfaces (POSIF) for servo motor positioning

- Window Watchdog Timer (WDT) for safety sensitive applications

- Die Temperature Sensor (DTS)

- Real Time Clock module with alarm support

- System Control Unit (SCU) for system configuration and control

#### **General Device Information**

| Table 9  | Package F | Package Pin Mapping (cont'd) |          |          |                                                                             |  |  |  |  |  |  |

|----------|-----------|------------------------------|----------|----------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| Function | LQFP-144  | LFBGA-144                    | LQFP-100 | Pad Type | Notes                                                                       |  |  |  |  |  |  |

| P0.11    | 139       | E5                           | 95       | A1+      |                                                                             |  |  |  |  |  |  |

| P0.12    | 138       | D5                           | 94       | A1+      |                                                                             |  |  |  |  |  |  |

| P0.13    | 137       | C5                           | -        | A1+      |                                                                             |  |  |  |  |  |  |

| P0.14    | 136       | E6                           | -        | A1+      |                                                                             |  |  |  |  |  |  |

| P0.15    | 135       | C6                           | -        | A1+      |                                                                             |  |  |  |  |  |  |

| P1.0     | 112       | D9                           | 79       | A1+      |                                                                             |  |  |  |  |  |  |

| P1.1     | 111       | E9                           | 78       | A1+      |                                                                             |  |  |  |  |  |  |

| P1.2     | 110       | C11                          | 77       | A2       |                                                                             |  |  |  |  |  |  |

| P1.3     | 109       | C12                          | 76       | A2       |                                                                             |  |  |  |  |  |  |

| P1.4     | 108       | C10                          | 75       | A1+      |                                                                             |  |  |  |  |  |  |

| P1.5     | 107       | D10                          | 74       | A1+      |                                                                             |  |  |  |  |  |  |

| P1.6     | 116       | B9                           | 83       | A2       |                                                                             |  |  |  |  |  |  |

| P1.7     | 115       | B10                          | 82       | A2       |                                                                             |  |  |  |  |  |  |

| P1.8     | 114       | A10                          | 81       | A2       |                                                                             |  |  |  |  |  |  |

| P1.9     | 113       | B11                          | 80       | A2       |                                                                             |  |  |  |  |  |  |

| P1.10    | 106       | D12                          | 73       | A1+      |                                                                             |  |  |  |  |  |  |

| P1.11    | 105       | D11                          | 72       | A1+      |                                                                             |  |  |  |  |  |  |

| P1.12    | 104       | E11                          | 71       | A2       |                                                                             |  |  |  |  |  |  |

| P1.13    | 103       | E12                          | 70       | A2       |                                                                             |  |  |  |  |  |  |

| P1.14    | 102       | E10                          | 69       | A2       |                                                                             |  |  |  |  |  |  |

| P1.15    | 94        | G12                          | 68       | A2       |                                                                             |  |  |  |  |  |  |

| P2.0     | 74        | J11                          | 52       | A2       |                                                                             |  |  |  |  |  |  |

| P2.1     | 73        | K12                          | 51       | A2       | After a system reset, via<br>HWSEL this pin selects<br>the DB.TDO function. |  |  |  |  |  |  |

| P2.2     | 72        | K11                          | 50       | A2       |                                                                             |  |  |  |  |  |  |

| P2.3     | 71        | L11                          | 49       | A2       |                                                                             |  |  |  |  |  |  |

| P2.4     | 70        | L10                          | 48       | A2       |                                                                             |  |  |  |  |  |  |

| P2.5     | 69        | M10                          | 47       | A2       |                                                                             |  |  |  |  |  |  |

| P2.6     | 76        | J9                           | 54       | A1+      |                                                                             |  |  |  |  |  |  |

| P2.7     | 75        | K9                           | 53       | A1+      |                                                                             |  |  |  |  |  |  |

| P2.8     | 68        | L9                           | 46       | A2       |                                                                             |  |  |  |  |  |  |

| P2.9     | 67        | M9                           | 45       | A2       |                                                                             |  |  |  |  |  |  |

#### Data Sheet

#### **General Device Information**

| Table 9  | Package F | Package Pin Mapping (cont'd) |          |          |       |  |  |  |  |  |  |

|----------|-----------|------------------------------|----------|----------|-------|--|--|--|--|--|--|

| Function | LQFP-144  | LFBGA-144                    | LQFP-100 | Pad Type | Notes |  |  |  |  |  |  |

| P2.10    | 66        | L8                           | 44       | A2       |       |  |  |  |  |  |  |

| P2.11    | 65        | M8                           | -        | A2       |       |  |  |  |  |  |  |

| P2.12    | 64        | L7                           | -        | A2       |       |  |  |  |  |  |  |

| P2.13    | 63        | M7                           | -        | A2       |       |  |  |  |  |  |  |

| P2.14    | 60        | K7                           | 41       | A2       |       |  |  |  |  |  |  |

| P2.15    | 59        | J6                           | 40       | A2       |       |  |  |  |  |  |  |

| P3.0     | 7         | C1                           | 7        | A2       |       |  |  |  |  |  |  |

| P3.1     | 6         | B2                           | 6        | A2       |       |  |  |  |  |  |  |

| P3.2     | 5         | B3                           | 5        | A2       |       |  |  |  |  |  |  |

| P3.3     | 132       | F7                           | 93       | A1+      |       |  |  |  |  |  |  |

| P3.4     | 131       | E7                           | 92       | A1+      |       |  |  |  |  |  |  |

| P3.5     | 130       | B6                           | 91       | A2       |       |  |  |  |  |  |  |

| P3.6     | 129       | A7                           | 90       | A2       |       |  |  |  |  |  |  |

| P3.7     | 14        | E4                           | -        | A1+      |       |  |  |  |  |  |  |

| P3.8     | 13        | E3                           | -        | A1+      |       |  |  |  |  |  |  |

| P3.9     | 12        | F5                           | -        | A1+      |       |  |  |  |  |  |  |

| P3.10    | 11        | F6                           | -        | A1+      |       |  |  |  |  |  |  |

| P3.11    | 10        | D3                           | -        | A1+      |       |  |  |  |  |  |  |

| P3.12    | 9         | D2                           | -        | A2       |       |  |  |  |  |  |  |

| P3.13    | 8         | C2                           | -        | A2       |       |  |  |  |  |  |  |

| P3.14    | 134       | D6                           | -        | A1+      |       |  |  |  |  |  |  |

| P3.15    | 133       | D7                           | -        | A1+      |       |  |  |  |  |  |  |

| P4.0     | 124       | B8                           | 85       | A2       |       |  |  |  |  |  |  |

| P4.1     | 123       | A9                           | 84       | A2       |       |  |  |  |  |  |  |

| P4.2     | 122       | E8                           | -        | A1+      |       |  |  |  |  |  |  |

| P4.3     | 121       | F8                           | -        | A1+      |       |  |  |  |  |  |  |

| P4.4     | 120       | C7                           | -        | A1+      |       |  |  |  |  |  |  |

| P4.5     | 119       | D8                           | -        | A1+      |       |  |  |  |  |  |  |

| P4.6     | 118       | C8                           | -        | A1+      |       |  |  |  |  |  |  |

| P4.7     | 117       | C9                           | -        | A1+      |       |  |  |  |  |  |  |

| P5.0     | 84        | H9                           | 58       | A1+      |       |  |  |  |  |  |  |

| P5.1     | 83        | H8                           | 57       | A1+      |       |  |  |  |  |  |  |

| P5.2     | 82        | H7                           | 56       | A1+      |       |  |  |  |  |  |  |

#### **General Device Information**

| Function | LQFP-144 | LFBGA-144 | LQFP-100 | Pad Type | Notes                                                                                                                                                                                                                                                                                                                                       |

|----------|----------|-----------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSSO     | 89       | J12       | 63       | Power    |                                                                                                                                                                                                                                                                                                                                             |

| VSS      | Exp. Pad | -         | Exp. Pad | Power    | <b>Exposed Die Pad</b><br>The exposed die pad is<br>connected internally to<br>VSS. For proper<br>operation, it is mandatory<br>to connect the exposed<br>pad directly to the<br>common ground on the<br>board.<br>For thermal aspects,<br>please refer to the Data<br>Sheet. Board layout<br>examples are given in an<br>application note. |

## Table 9 Package Pin Mapping (cont'd)

#### Table 11 Port I/O Functions (cont'd)

| Function | Outputs         |                  |                 |                  |                           |              | Inputs             |             |                    |                 |              |                 |                |                |                |                  |

|----------|-----------------|------------------|-----------------|------------------|---------------------------|--------------|--------------------|-------------|--------------------|-----------------|--------------|-----------------|----------------|----------------|----------------|------------------|

|          | ALT1            | ALT2             | ALT3            | ALT4             | HWO0                      | HWO1         | HWIO               | HWI1        | Input              | Input           | Input        | Input           | Input          | Input          | Input          | Input            |

| 21.5     | CAN.<br>N1_TXD  | U0C0.<br>DOUTO   | CCU80.<br>OUT23 | CCU81.<br>OUT10  | U0C0.<br>DOUTO            |              | U0C0.<br>HWIN0     |             | UOCO.<br>DXOA      | CAN.<br>NO_RXDA | ERU0.<br>2A0 | ERU1.<br>0A0    | CCU41.<br>IN1C | DSD.<br>DIN2B  |                |                  |

| 1.6      |                 | U0C0.<br>SCLKOUT |                 |                  | SDMMC.<br>DATA1_OUT       | EBU.<br>AD10 | SDMMC.<br>DATA1_IN | EBU.<br>D10 | DSD.<br>DIN2A      |                 |              |                 |                |                |                |                  |

| 1.7      |                 | UOCO.<br>DOUTO   | DSD.<br>MCLK2   |                  | SDMMC.<br>DATA2_OUT       | EBU.<br>AD11 | SDMMC.<br>DATA2_IN | EBU.<br>D11 |                    | DSD.<br>MCLK2A  |              |                 |                |                |                |                  |

| 1.8      |                 | U0C0.<br>SELO1   | DSD.<br>MCLK1   |                  | SDMMC.<br>DATA4_OUT       | EBU.<br>AD12 | SDMMC.<br>DATA4_IN | EBU.<br>D12 | CAN.<br>N2_RXDA    | DSD.<br>MCLK1A  |              |                 |                |                |                |                  |

| 1.9      |                 | CAN.<br>N2_TXD   |                 |                  | SDMMC.<br>DATA5_OUT       | EBU.<br>AD13 | SDMMC.<br>DATA5_IN | EBU.<br>D13 |                    | DSD.<br>MCLK0A  |              |                 |                |                |                |                  |

| 91.10    | ETH0.<br>MDC    | U0C0.<br>SCLKOUT | CCU81.<br>OUT21 |                  |                           |              | SDMMC.<br>SDCD     |             |                    |                 |              |                 | CCU41.<br>IN2C |                |                |                  |

| 4.11     |                 | U0C0.<br>SELO0   | CCU81.<br>OUT11 |                  | ETH0.<br>MDO              |              | ETH0.<br>MDIC      |             |                    |                 |              |                 | CCU41.<br>IN3C |                |                |                  |

| 21.12    | ETH0.<br>TX_EN  | CAN.<br>N1_TXD   | CCU81.<br>OUT01 |                  | SDMMC.<br>DATA6_OUT       | EBU.<br>AD16 | SDMMC.<br>DATA6_IN | EBU.<br>D16 |                    |                 |              |                 |                |                |                |                  |

| 21.13    | ETH0.<br>TXD0   | U0C1.<br>SELO3   | CCU81.<br>OUT20 |                  | SDMMC.<br>DATA7_OUT       | EBU.<br>AD17 | SDMMC.<br>DATA7_IN | EBU.<br>D17 | CAN.<br>N1_RXDC    |                 |              |                 |                |                |                |                  |

| 21.14    | ETH0.<br>TXD1   | U0C1.<br>SELO2   | CCU81.<br>OUT10 |                  |                           | EBU.<br>AD18 |                    | EBU.<br>D18 |                    |                 |              |                 |                |                |                |                  |

| 21.15    | SCU.<br>EXTCLK  | DSD.<br>MCLK2    | CCU81.<br>OUT00 |                  |                           | EBU.<br>AD19 |                    | EBU.<br>D19 |                    | DSD.<br>MCLK2B  |              | ERU1.<br>1A0    |                |                |                |                  |

| 2.0      |                 | CCU81.<br>OUT21  | DSD.<br>CGPWMN  | LEDTS0.<br>COL1  | ETH0.<br>MDO              | EBU.<br>AD20 | ETH0.<br>MDIB      | EBU.<br>D20 |                    |                 | ERU0.<br>0B3 |                 | CCU40.<br>IN1C |                |                |                  |

| 2.1      |                 | CCU81.<br>OUT11  | DSD.<br>CGPWMP  | LEDTS0.<br>COL0  | DB.TDO/<br>TRACESWO       | EBU.<br>AD21 |                    | EBU.<br>D21 | ETH0.<br>CLK_RMIIA |                 |              | ERU1.<br>0B0    | CCU40.<br>IN0C |                |                | ETH0.<br>CLKRXA  |

| 2.2      | VADC.<br>EMUX00 | CCU81.<br>OUT01  | CCU41.<br>OUT3  | LEDTS0.<br>LINE0 | LEDTS0.<br>EXTENDED0      | EBU.<br>AD22 | LEDTS0.<br>TSIN0A  | EBU.<br>D22 | ETH0.<br>RXD0A     | U0C1.<br>DX0A   | ERU0.<br>1B2 |                 | CCU41.<br>IN3A |                |                |                  |

| 2.3      | VADC.<br>EMUX01 | U0C1.<br>SELO0   | CCU41.<br>OUT2  | LEDTS0.<br>LINE1 | LEDTS0.<br>EXTENDED1      | EBU.<br>AD23 | LEDTS0.<br>TSIN1A  | EBU.<br>D23 | ETH0.<br>RXD1A     | U0C1.<br>DX2A   | ERU0.<br>1A2 | POSIF1.<br>IN2A | CCU41.<br>IN2A |                |                |                  |

| 2.4      | VADC.<br>EMUX02 | U0C1.<br>SCLKOUT | CCU41.<br>OUT1  | LEDTS0.<br>LINE2 | LEDTS0.<br>EXTENDED2      | EBU.<br>AD24 | LEDTS0.<br>TSIN2A  | EBU.<br>D24 | ETH0.<br>RXERA     | U0C1.<br>DX1A   | ERU0.<br>0B2 | POSIF1.<br>IN1A | CCU41.<br>IN1A |                |                |                  |

| 2.5      | ETH0.<br>TX_EN  | U0C1.<br>DOUT0   | CCU41.<br>OUT0  | LEDTS0.<br>LINE3 | LEDTS0.<br>EXTENDED3      | EBU.<br>AD25 | LEDTS0.<br>TSIN3A  | EBU.<br>D25 | ETH0.<br>RXDVA     | U0C1.<br>DX0B   | ERU0.<br>0A2 | POSIF1.<br>IN0A | CCU41.<br>INDA |                |                | ETH0.<br>CRS_DVA |

| 2.6      | U2C0.<br>SELO4  |                  | CCU80.<br>OUT13 | LEDTS0.<br>COL3  | U2C0.<br>DOUT3            |              | U2C0.<br>HWIN3     |             | DSD.<br>DIN1B      | CAN.<br>N1_RXDA | ERU0.<br>1B3 |                 | CCU40.<br>IN3C |                |                |                  |

| 2.7      | ETH0.<br>MDC    | CAN.<br>N1_TXD   | CCU80.<br>OUT03 | LEDTS0.<br>COL2  |                           |              |                    |             | DSD.<br>DIN0B      |                 |              | ERU1.<br>1B0    | CCU40.<br>IN2C |                |                |                  |

| 2.8      | ETH0.<br>TXD0   |                  | CCU80.<br>OUT32 | LEDTS0.<br>LINE4 | LEDTS0.<br>EXTENDED4      | EBU.<br>AD26 | LEDTS0.<br>TSIN4A  | EBU.<br>D26 | DAC.<br>TRIGGER5   |                 |              |                 | CCU40.<br>IN0B | CCU40.<br>IN1B | CCU40.<br>IN2B | CCU40.<br>IN3B   |

| 2.9      | ETH0.<br>TXD1   |                  | CCU80.<br>OUT22 | LEDTS0.<br>LINE5 | LEDTS0.<br>EXTENDED5      | EBU.<br>AD27 | LEDTS0.<br>TSIN5A  | EBU.<br>D27 | DAC.<br>TRIGGER4   |                 |              |                 | CCU41.<br>IN0B | CCU41.<br>IN1B | CCU41.<br>IN2B | CCU41.<br>IN3B   |

| 2.10     | VADC.<br>EMUX10 |                  |                 |                  | DB.<br>ETM_TRACEDA<br>TA3 | EBU.<br>AD28 |                    | EBU.<br>D28 |                    |                 |              |                 |                |                |                |                  |

| 2.11     | ETH0.<br>TXER   |                  | CCU80.<br>OUT22 |                  | DB.<br>ETM_TRACEDA<br>TA2 | EBU.<br>AD29 |                    | EBU.<br>D29 |                    |                 |              |                 |                |                |                |                  |

Infineon

Data Sheet

XMC4500 XMC4000 Family

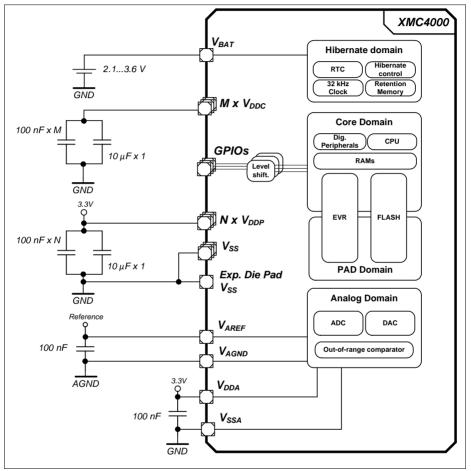

## 2.3 Power Connection Scheme

Figure 9. shows a reference power connection scheme for the XMC4500.

#### Figure 9 Power Connection Scheme

Every power supply pin needs to be connected. Different pins of the same supply need also to be externally connected. As example, all  $V_{\rm DDP}$  pins must be connected externally to one  $V_{\rm DDP}$  net. In this reference scheme one 100 nF capacitor is connected at each supply pin against  $V_{\rm SS}$ . An additional 10 µF capacitor is connected to the  $V_{\rm DDP}$  nets and an additional 10 µF capacitor to the  $V_{\rm DDP}$  nets.

# 3 Electrical Parameters

## 3.1 General Parameters

## 3.1.1 Parameter Interpretation

The parameters listed in this section partly represent the characteristics of the XMC4500 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are marked with a two-letter abbreviation in column "Symbol":

• CC

Such parameters indicate Controller Characteristics, which are a distinctive feature of the XMC4500 and must be regarded for system design.

• SR

Such parameters indicate **S**ystem **R**equirements, which must be provided by the application system in which the XMC4500 is designed in.

## 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                                                                              | Symb                 | loo |      | Va   | lues                                  | Unit | Note /                |

|------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|------|---------------------------------------|------|-----------------------|

|                                                                                                                        |                      |     | Min. | Тур. | Max.                                  |      | Test Con<br>dition    |

| Storage temperature                                                                                                    | $T_{\rm ST}$         | SR  | -65  | -    | 150                                   | °C   | -                     |

| Junction temperature                                                                                                   | $T_{J}$              | SR  | -40  | -    | 150                                   | °C   | -                     |

| Voltage at 3.3 V power supply pins with respect to $V_{\rm SS}$                                                        | $V_{DDP}$            | SR  | -    | -    | 4.3                                   | V    | -                     |

| Voltage on any Class A and dedicated input pin with respect to $V_{\rm SS}$                                            | V <sub>IN</sub>      | SR  | -1.0 | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Voltage on any analog input pin with respect to $V_{\text{AGND}}$                                                      | $V_{AIN}$ $V_{AREF}$ | SR  | -1.0 | -    | V <sub>DDP</sub> + 1.0<br>or max. 4.3 | V    | whichever<br>is lower |

| Input current on any pin<br>during overload condition                                                                  | I <sub>IN</sub>      | SR  | -10  | -    | +10                                   | mA   |                       |

| Absolute maximum sum of all<br>input circuit currents for one<br>port group during overload<br>condition <sup>1)</sup> | $\Sigma I_{\rm IN}$  | SR  | -25  | -    | +25                                   | mA   |                       |

| Absolute maximum sum of all input circuit currents during overload condition                                           | $\Sigma I_{\rm IN}$  | SR  | -100 | -    | +100                                  | mA   |                       |

#### Table 12 Absolute Maximum Rating Parameters

1) The port groups are defined in **Table 16**.

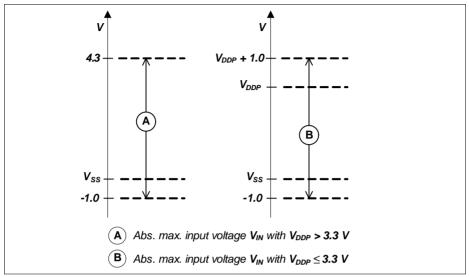

**Figure 10** explains the input voltage ranges of  $V_{\rm IN}$  and  $V_{\rm AIN}$  and its dependency to the supply level of  $V_{\rm DDP}$ . The input voltage must not exceed 4.3 V, and it must not be more than 1.0 V above  $V_{\rm DDP}$ . For the range up to  $V_{\rm DDP}$  + 1.0 V also see the definition of the overload conditions in Section 3.1.3.

Figure 10 Absolute Maximum Input Voltage Ranges

# 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 13 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$  or  $V_{\text{DDA}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload conditions, then the parameters of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

38

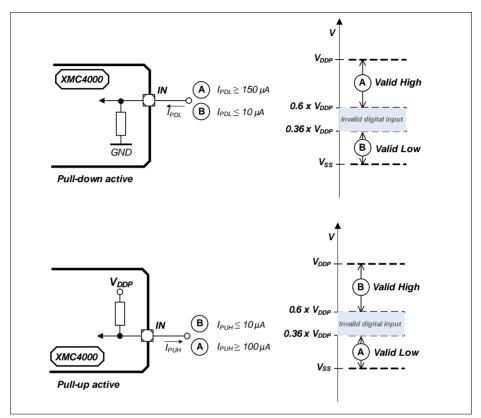

#### Figure 13 Pull Device Input Characteristics

Figure 13 visualizes the input characteristics with an active internal pull device:

- in the cases "A" the internal pull device is overridden by a strong external driver;

- in the cases "B" the internal pull device defines the input logical state against a weak external load.

| Parameter                                                                 | Symbol                                                 |      | Value | S     | Unit | Note /                                                                                    |  |

|---------------------------------------------------------------------------|--------------------------------------------------------|------|-------|-------|------|-------------------------------------------------------------------------------------------|--|

|                                                                           |                                                        | Min. | Тур.  | Max.  |      | Test Condition                                                                            |  |

| Total Unadjusted Error                                                    | TUE CC                                                 | -4   | -     | 4     | LSB  | 12-bit resolution;                                                                        |  |

| Differential Non-Linearity<br>Error <sup>8)</sup>                         | EA <sub>DNL</sub><br>CC                                | -3   | -     | 3     | LSB  | $V_{\text{DDA}} = 3.3 \text{ V};$ $V_{\text{AREF}} = V_{\text{DDA}}^{7)}$                 |  |

| Gain Error <sup>8)</sup>                                                  | EA <sub>GAIN</sub><br>CC                               | -4   | -     | 4     | LSB  |                                                                                           |  |

| Integral Non-Linearity <sup>8)</sup>                                      | EA <sub>INL</sub> CC                                   | -3   | -     | 3     | LSB  |                                                                                           |  |

| Offset Error <sup>8)</sup>                                                | EA <sub>OFF</sub><br>CC                                | -4   | -     | 4     | LSB  |                                                                                           |  |

| Worst case ADC $V_{\text{DDA}}$ power supply current per active converter | I <sub>DDAA</sub><br>CC                                | -    | 1.5   | 2     | mA   | during conversion<br>$V_{\text{DDP}} = 3.6 \text{ V},$<br>$T_{\text{J}} = 150 \text{ °C}$ |  |

| Charge consumption on $V_{\text{AREF}}$ per conversion <sup>5)</sup>      | $\begin{array}{c} Q_{\rm CONV} \\ { m CC} \end{array}$ | -    | 30    | -     | рС   | $0 V \le V_{AREF} \le V_{DDA}^{9)}$                                                       |  |

| ON resistance of the analog input path                                    | R <sub>AIN</sub> CC                                    | -    | 700   | 1 700 | Ohm  |                                                                                           |  |

| ON resistance for the ADC test (pull down for AIN7)                       | R <sub>AIN7T</sub><br>CC                               | 180  | 550   | 900   | Ohm  |                                                                                           |  |

| Resistance of the reference voltage input path                            | R <sub>AREF</sub><br>CC                                | -    | 700   | 1 700 | Ohm  |                                                                                           |  |

#### Table 23 VADC Parameters (Operating Conditions apply)

1) A running conversion may become imprecise in case the normal conditions are violated (voltage overshoot).

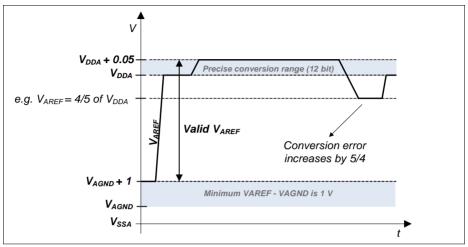

If the analog reference voltage is below V<sub>DDA</sub>, then the ADC converter errors increase. If the reference voltage is reduced by the factor k (k<1), TUE, DNL, INL, Gain, and Offset errors increase also by the factor 1/k.</li>

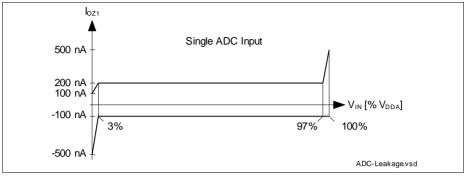

- 3) The leakage current definition is a continuous function, as shown in figure ADCx Analog Inputs Leakage. The numerical values defined determine the characteristic points of the given continuous linear approximation they do not define step function (see Figure 16).

- 4) The sampling capacity of the conversion C-network is pre-charged to V<sub>AREF</sub>/2 before the sampling moment. Because of the parasitic elements, the voltage measured at AINx can deviate from V<sub>AREF</sub>/2.

- 5) Applies to AINx, when used as alternate reference input.

- 6) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead, smaller capacitances are successively switched to the reference voltage.

- For 10-bit conversions, the errors are reduced to 1/4; for 8-bit conversions, the errors are reduced to 1/16. Never less than ±1 LSB.

- 8) The sum of DNL/INL/GAIN/OFF errors does not exceed the related total unadjusted error TUE.

- 9) The resulting current for a conversion can be calculated with  $I_{AREF} = Q_{CONV} / t_c$ . The fastest 12-bit post-calibrated conversion of  $t_c = 550$  ns results in a typical average current of  $I_{AREF} = 54.5 \ \mu$ A.

## Figure 14 VADC Reference Voltage Range

The power-up calibration of the VADC requires a maximum number of 4  $352 f_{ADCI}$  cycles.

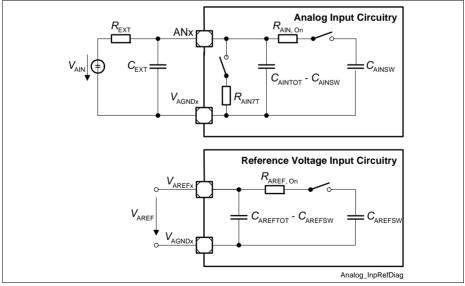

Figure 15 VADC Input Circuits

## Figure 16 VADC Analog Input Leakage Current

#### **Conversion Time**

| Table 24 | Conversion Time | (Operating Conditions appl  | V)         |

|----------|-----------------|-----------------------------|------------|

|          |                 | Coporating contaitions appl | <b>y</b> / |

| Parameter Symbol   |                | nbol | Values                                                      | Unit | Note                                                                                             |

|--------------------|----------------|------|-------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------|

| Conversion<br>time | t <sub>C</sub> | CC   | $2 \times T_{ADC}$ +<br>(2 + N + STC + PC +DM) × $T_{ADCI}$ |      | N = 8, 10, 12 for<br>N-bit conversion<br>$T_{ADC} = 1 / f_{PERIPH}$<br>$T_{ADCI} = 1 / f_{ADCI}$ |

- STC defines additional clock cycles to extend the sample time

- · PC adds two cycles if post-calibration is enabled

- DM adds one cycle for an extended conversion time of the MSB

## **Conversion Time Examples**

System assumptions:

$f_{ADC}$  = 120 MHz i.e.  $t_{ADC}$  = 8.33 ns, DIVA = 3,  $f_{ADCI}$  = 30 MHz i.e.  $t_{ADCI}$  = 33.3 ns

According to the given formulas the following minimum conversion times can be achieved (STC = 0, DM = 0):

12-bit post-calibrated conversion (PC = 2):

$t_{\text{CN12C}} = (2 + 12 + 2) \times t_{\text{ADCI}} + 2 \times t_{\text{ADC}} = 16 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 550 \text{ ns}$

12-bit uncalibrated conversion:

$t_{CN12} = (2 + 12) \times t_{ADCI} + 2 \times t_{ADC} = 14 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 483 \text{ ns}$

10-bit uncalibrated conversion:

$t_{CN10} = (2 + 10) \times t_{ADCI} + 2 \times t_{ADC} = 12 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 417 \text{ ns}$

8-bit uncalibrated:

$t_{CN8} = (2 + 8) \times t_{ADCI} + 2 \times t_{ADC} = 10 \times 33.3 \text{ ns} + 2 \times 8.33 \text{ ns} = 350 \text{ ns}$

## 3.2.8 Power Supply Current

The total power supply current defined below consists of a leakage and a switching component.

Application relevant values are typically lower than those given in the following tables, and depend on the customer's system operating conditions (e.g. thermal connection or used application configurations).

If not stated otherwise, the operating conditions for the parameters in the following table are:

$V_{\rm DDP}$  = 3.3 V,  $T_{\rm A}$  = 25 °C

| Parameter                                       | Symb           | Symbol |      | Values | S    | Unit | Note /          |

|-------------------------------------------------|----------------|--------|------|--------|------|------|-----------------|

|                                                 |                |        | Min. | Тур.   | Max. |      | Test Condition  |

| Active supply current <sup>1)10)</sup>          | $I_{\rm DDPA}$ | CC     | -    | 122    | -    | mA   | 120 / 120 / 120 |

| Peripherals enabled                             |                |        | -    | 110    | -    |      | 120 / 60 / 60   |

| Frequency: $f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz  |                |        | -    | 85     | -    |      | 60 / 60 / 120   |

| JCPU, JPERIPH, JCCU                             |                |        | -    | 65     | -    |      | 24 / 24 / 24    |

|                                                 |                |        | -    | 52     | -    |      | 1/1/1           |

| Active supply current                           | $I_{\rm DDPA}$ | СС     | -    | 98     | -    | mA   | 120 / 120 / 120 |

| Code execution from RAM<br>Flash in Sleep mode  |                |        | -    | 80     | -    |      | 120 / 60 / 60   |

| Active supply current <sup>2)</sup>             | $I_{\rm DDPA}$ | CC     | -    | 115    | -    | mA   | 120 / 120 / 120 |

| Peripherals disabled                            |                |        | -    | 105    | -    |      | 120 / 60 / 60   |

| Frequency: $f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz  |                |        | -    | 80     | -    |      | 60 / 60 / 120   |

| JCPU, JPERIPH, JCCU                             |                |        | -    | 63     | -    |      | 24 / 24 / 24    |

|                                                 |                |        | -    | 50     | -    |      | 1/1/1           |

| Sleep supply current <sup>3)</sup>              | $I_{\rm DDPS}$ | CC     | -    | 115    | -    | mA   | 120 / 120 / 120 |

| Peripherals enabled                             |                |        | -    | 105    | -    |      | 120 / 60 / 60   |

| Frequency: $f_{CPU}/f_{PERIPH}/f_{CCU}$ in MHz  |                |        | -    | 83     | -    |      | 60 / 60 / 120   |

| JCPU / JPERIPH / JCCU                           |                |        | -    | 60     | -    | -    | 24 / 24 / 24    |

|                                                 |                |        | -    | 48     | -    |      | 1/1/1           |

| $f_{\rm CPU}/f_{\rm PERIPH}/f_{\rm CCU}$ in kHz | 1              |        | -    | 46     | -    | 1    | 100 / 100 / 100 |

## Table 32 Power Supply Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

## 3.3 AC Parameters

## 3.3.1 Testing Waveforms

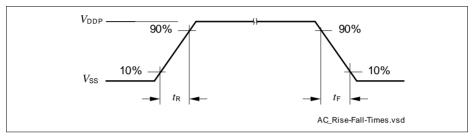

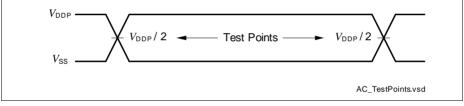

Figure 23 Testing Waveform, Output Delay

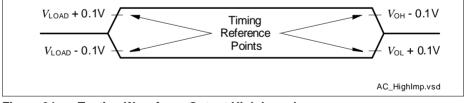

Figure 24 Testing Waveform, Output High Impedance

## 3.3.9 Peripheral Timing

## 3.3.9.1 Delta-Sigma Demodulator Digital Interface Timing

The following parameters are applicable for the digital interface of the Delta-Sigma Demodulator (DSD).

The data timing is relative to the active clock edge. Depending on the operation mode of the connected modulator that can be the rising and falling clock edge.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                      | Syr                   | nbol |                            | Values | 5    | Unit | t Note /                                |  |

|------------------------------------------------|-----------------------|------|----------------------------|--------|------|------|-----------------------------------------|--|

|                                                |                       |      | Min.                       | Тур.   | Max. |      | Test Condition                          |  |

| MCLK period in master mode                     | <i>t</i> <sub>1</sub> | CC   | 33.3                       | -      | -    | ns   | $t_1 \ge 4 \ge t_{\text{PERIPH}}^{(1)}$ |  |

| MCLK high time in master mode                  | <i>t</i> <sub>2</sub> | CC   | 9                          | -      | -    | ns   | $t_2 > t_{\text{PERIPH}}^{1)}$          |  |

| MCLK low time in master mode                   | <i>t</i> <sub>3</sub> | CC   | 9                          | -      | -    | ns   | $t_3 > t_{\text{PERIPH}}^{1)}$          |  |

| MCLK period in slave mode                      | <i>t</i> <sub>1</sub> | SR   | 33.3                       | -      | -    | ns   | $t_1 \ge 4 \ge t_{\text{PERIPH}}^{(1)}$ |  |

| MCLK high time in slave mode                   | <i>t</i> <sub>2</sub> | SR   | t <sub>PERIPH</sub>        | -      | -    | ns   | 1)                                      |  |

| MCLK low time in slave mode                    | <i>t</i> <sub>3</sub> | SR   | t <sub>PERIPH</sub>        | -      | -    | ns   | 1)                                      |  |

| DIN input setup time to the active clock edge  | <i>t</i> <sub>4</sub> | SR   | $t_{\text{PERIPH}}$ + 4    | -      | -    | ns   | 1)                                      |  |

| DIN input hold time from the active clock edge | <i>t</i> <sub>5</sub> | SR   | t <sub>PERIPH</sub><br>+ 3 | -      | -    | ns   | 1)                                      |  |

|                                                |                       |      |                            |        |      |      |                                         |  |

### Table 42 DSD Interface Timing Parameters

1)  $t_{\text{PERIPH}} = 1 / f_{\text{PERIPH}}$

```

With clock delay:

t_{ODLY_F} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL} + t_{CLK\_DELAY}

t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{WL} < t_{PP} + t_{CLK\_DELAY} - t_{ISU} - t_{ODLY\_F}

t_{DATA\_DELAY} + t_{TAP\_DELAY} + 20 < 40 + t_{CLK\_DELAY} - 5 - 10

```

$t_{DATA\_DELAY} < 5 + t_{CLK\_DELAY} - t_{TAP\_DELAY}$

The data can be delayed versus clock up to 5 ns in ideal case of  $t_{WL}$  = 20 ns.

### Full-Speed Write Meeting Hold (Minimum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(4)

(2)

(3)

$t_{\text{CLK\_DELAY}} < t_{\text{WL}} + t_{\text{OH\_F}} + t_{\text{DATA\_DELAY}} + t_{\text{TAP\_DELAY}} - t_{\text{IH}}$

$t_{\rm CLK\_DELAY} < 20 + t_{\rm DATA\_DELAY} + t_{\rm TAP\_DELAY} - 5$

$t_{DATA\_DELAY} < 15 + t_{CLK\_DELAY} + t_{TAP\_DELAY}$

The clock can be delayed versus data up to 18.2 ns (external delay line) in ideal case of  $t_{WL}$  = 20 ns, with maximum  $t_{TAP DELAY}$  = 3.2 ns programmed.

| No clock delay:   |                                                                                                                                                     | (7) |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                   | $t_{ODLY\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL}$                                                                                 |     |

| With clock delay: |                                                                                                                                                     |     |

|                   | f . f . f . f . f                                                                                                                                   | (8) |

|                   | $t_{ODLY\_H} + t_{DATA\_DELAY} + t_{TAP\_DELAY} + t_{ISU} < t_{WL} + t_{CLK\_DELAY}$                                                                |     |

|                   |                                                                                                                                                     | (9) |

|                   | $t_{DATA\_DELAY} + t_{TAP\_DELAY} - t_{CLK\_DELAY} < t_{WL} - t_{ISU} - t_{ODLY\_H}$                                                                |     |

|                   | $t_{\text{DATA}\_\text{DELAY}} - t_{\text{CLK}\_\text{DELAY}} < t_{\text{WL}} - t_{\text{ISU}} - t_{\text{ODLY}\_H} - t_{\text{TAP}\_\text{DELAY}}$ |     |

|                   | $t_{DATA\_DELAY} - t_{CLK\_DELAY} < 10 - 6 - 14 - t_{TAP\_DELAY}$                                                                                   |     |

|                   | $t_{\text{DATA\_DELAY}} - t_{\text{CLK\_DELAY}} < -10 - t_{\text{TAP\_DELAY}}$                                                                      |     |

The data delay is less than the clock delay by at least 10 ns in the ideal case where  $t_{WL}$ = 10 ns.

## High-Speed Write Meeting Hold (Minimum Delay)

The following equations show how to calculate the allowed skew range between the SD\_CLK and SD\_DAT/CMD signals on the PCB.

(10)

$t_{\mathrm{CLK\_DELAY}} < t_{\mathrm{WL}} + t_{\mathrm{OH\_H}} + t_{\mathrm{DATA\_DELAY}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{IH}}$

$t_{\mathrm{CLK\_DELAY}} - t_{\mathrm{DATA\_DELAY}} < t_{\mathrm{WL}} + t_{\mathrm{OH\_H}} + t_{\mathrm{TAP\_DELAY}} - t_{\mathrm{IH}}$

$t_{\mathrm{CLK\_DELAY}} - t_{\mathrm{DATA\_DELAY}} < 10 + 2 + t_{\mathrm{TAP\_DELAY}} - 2$

$t_{\rm CLK\_DELAY} - t_{\rm DATA\_DELAY} < 10 + t_{\rm TAP\_DELAY}$

The clock can be delayed versus data up to 13.2 ns (external delay line) in ideal case of  $t_{WL}$ = 10 ns, with maximum  $t_{TAP DELAY}$  = 3.2 ns programmed.

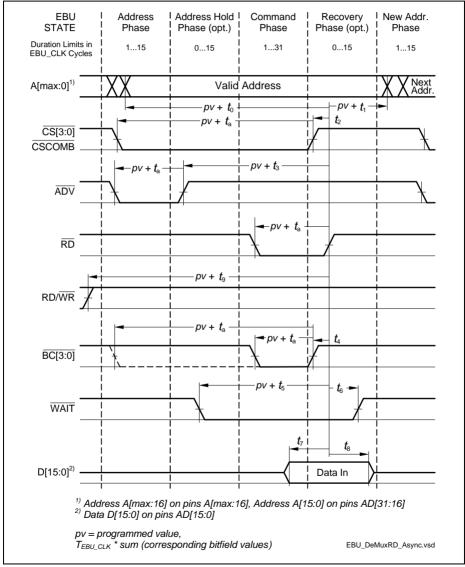

## Demultiplexed Read Timing

Figure 42 Demultiplexed Read Access

## Package and Reliability

power dissipation must be limited so that the average junction temperature does not exceed 150 °C.

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta,IA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}}-V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OL}} \times I_{\text{OL}})$

The dynamic external power consumption caused by the output drivers ( $P_{\text{IODYN}}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers