Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 48 MIPS                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 4.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                     |

| Data Converters            | A/D 21x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 32-QFN (5x5)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f389-b-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1.1. Product Selection Guide

| Ordering Part Number                              | MIPS (Peak) | Flash Memory (Bytes) | RAM  | <b>Calibrated Internal Oscillator</b> | Low Frequency Oscillator | Supply Voltage Regulator | SMBus/I2C | Enhanced SPI | UARTs | Timers (16-bit) | Programmable Counter Array | Digital Port I/O | External Memory Interface (EMIF) | 10-bit 500ksps ADC | Temperature Sensor | Voltage Reference | Analog Comparators | Package      |

|---------------------------------------------------|-------------|----------------------|------|---------------------------------------|--------------------------|--------------------------|-----------|--------------|-------|-----------------|----------------------------|------------------|----------------------------------|--------------------|--------------------|-------------------|--------------------|--------------|

| C8051F388-B-GQ                                    | 48          | 64k                  | 4352 | ~                                     | $\checkmark$             | $\checkmark$             | 2         | $\checkmark$ | 2     | 6               | $\checkmark$               | 40               | $\checkmark$                     | $\checkmark$       | $\checkmark$       | $\checkmark$      | 2                  | TQFP48       |

| C8051F389-B-GQ                                    | 48          | 64k                  | 4352 | $\checkmark$                          | $\checkmark$             | $\checkmark$             | 2         | $\checkmark$ | 2     | 6               | $\checkmark$               | 25               |                                  | $\checkmark$       | $\checkmark$       | $\checkmark$      | 2                  | LQFP32       |

| C8051F389-B-GM                                    | 48          | 64k                  | 4352 | $\checkmark$                          | $\checkmark$             | $\checkmark$             | 2         | $\checkmark$ | 2     | 6               | $\checkmark$               | 25               |                                  | $\checkmark$       | $\checkmark$       | $\checkmark$      | 2                  | QFN32        |

| C8051F38A-B-GQ                                    | 48          | 32k                  | 2304 | $\checkmark$                          | $\checkmark$             | $\checkmark$             | 2         | $\checkmark$ | 2     | 6               | $\checkmark$               | 40               | $\checkmark$                     | $\checkmark$       | $\checkmark$       | $\checkmark$      | 2                  | TQFP48       |

| C8051F38B-B-GQ                                    | 48          | 32k                  | 2304 | $\checkmark$                          | $\checkmark$             | $\checkmark$             | 2         | $\checkmark$ | 2     | 6               | $\checkmark$               | 25               |                                  | $\checkmark$       | $\checkmark$       | $\checkmark$      | 2                  | LQFP32       |

| C8051F38B-B-GM                                    | 48          | 32k                  | 2304 | ~                                     | $\checkmark$             | $\checkmark$             | 2         | $\checkmark$ | 2     | 6               | <                          | 25               |                                  | <                  | $\checkmark$       | $\checkmark$      | 2                  | QFN32        |

| Note: Starting with silico<br>use this format: "( |             |                      |      | ering                                 | ) par                    | t nu                     | mbe       | rs h         | avel  | beer            | n upo                      | dated            | to in                            | clud               | le th              | e sili            | con                | revision and |

### Table 5.10. ADC0 Electrical Characteristics

$V_{DD}$  = 3.0 V, VREF = 2.40 V (REFSL=0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                                  | Test Condition               | Min       | Тур       | Max             | Unit             |

|------------------------------------------------------------|------------------------------|-----------|-----------|-----------------|------------------|

| DC Accuracy                                                |                              |           |           |                 |                  |

| Resolution                                                 |                              |           | 10        |                 | bits             |

| Integral Nonlinearity                                      |                              | _         | ±0.5      | ±1              | LSB              |

| Differential Nonlinearity                                  | Guaranteed Monotonic         | —         | ±0.5      | ±1              | LSB              |

| Offset Error                                               |                              | -2        | 0         | 2               | LSB              |

| Full Scale Error                                           |                              | -5        | -2        | 0               | LSB              |

| Offset Temperature Coefficient                             |                              | —         | 0.005     | —               | LSB/°C           |

| Dynamic performance (10 kHz s                              | ine-wave single-ended input, | 1 dB belo | w Full Sc | ale, 500        | ksps)            |

| Signal-to-Noise Plus Distortion                            |                              | 55        | 58        | —               | dB               |

| Total Harmonic Distortion                                  | Up to the 5th harmonic       | —         | -73       | —               | dB               |

| Spurious-Free Dynamic Range                                |                              | —         | 78        | —               | dB               |

| Conversion Rate                                            |                              |           |           |                 |                  |

| SAR Conversion Clock                                       |                              | _         | _         | 8.33            | MHz              |

| Conversion Time in SAR Clocks                              | 10-bit Mode<br>8-bit Mode    | 13<br>11  | _         | _               | clocks<br>clocks |

| Track/Hold Acquisition Time                                |                              | 300       | _         | —               | ns               |

| Throughput Rate                                            |                              | —         |           | 500             | ksps             |

| Analog Inputs                                              |                              |           |           |                 |                  |

| ADC Input Voltage Range                                    | Single Ended (AIN+ – GND)    | 0         | _         | VREF            | V                |

|                                                            | Differential (AIN+ – AIN–)   | -VREF     | _         | VREF            | V                |

| Absolute Pin Voltage with respect to GND                   | Single Ended or Differential | 0         | —         | V <sub>DD</sub> | V                |

| Sampling Capacitance                                       |                              | —         | 30        | —               | pF               |

| Input Multiplexer Impedance                                |                              | —         | 5         | —               | kΩ               |

| Power Specifications                                       |                              |           |           |                 |                  |

| Power Supply Current<br>(V <sub>DD</sub> supplied to ADC0) | Operating Mode, 500 ksps     | —         | 750       | 1000            | μA               |

| Power Supply Rejection                                     |                              | _         | 1         | —               | mV/V             |

| Note: Represents one standard devia                        | ation from the mean.         |           |           |                 |                  |

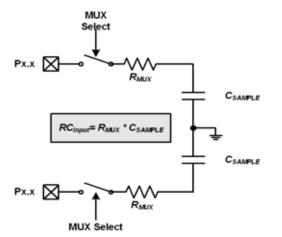

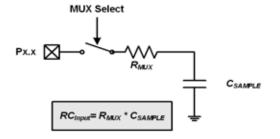

#### 6.3.3. Settling Time Requirements

A minimum tracking time is required before each conversion to ensure that an accurate conversion is performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 6.5 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 6.1. See Table 5.10 for ADC0 minimum settling time requirements as well as the mux impedance and sampling capacitor values.

### Equation 6.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance. *n* is the ADC resolution in bits (10).

## **Differential Mode**

## Single-Ended Mode

### Figure 6.5. ADC0 Equivalent Input Circuits

Rev. 1.1

## SFR Definition 6.7. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit   | 7              | 6            | 5                                         | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|----------------|--------------|-------------------------------------------|---|---|---|---|---|--|--|--|

| Nam   | e              | ADC0LTH[7:0] |                                           |   |   |   |   |   |  |  |  |

| Туре  | R/W            |              |                                           |   |   |   |   |   |  |  |  |

| Rese  | et O           | 0            | 0 0 0 0 0 0 0                             |   |   |   |   |   |  |  |  |

| SFR A | Address = 0xC6 | ; SFR Page   | e = All Pages                             |   |   |   |   |   |  |  |  |

| Bit   | Name           |              | Function                                  |   |   |   |   |   |  |  |  |

| 7:0   | ADC0LTH[7:0    | ] ADC0 Le    | ADC0 Less-Than Data Word High-Order Bits. |   |   |   |   |   |  |  |  |

## SFR Definition 6.8. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit   | 7              | 7 6 5 4 3 2 1 0                                   |               |   |  |  |  |  |  |  |  |

|-------|----------------|---------------------------------------------------|---------------|---|--|--|--|--|--|--|--|

| Nam   | e              | ADC0LTL[7:0]                                      |               |   |  |  |  |  |  |  |  |

| Туре  | R/W            |                                                   |               |   |  |  |  |  |  |  |  |

| Rese  | et 0           | 0 0 0 0 0 0                                       |               |   |  |  |  |  |  |  |  |

| SFR A | Address = 0xC5 | ; SFR Page                                        | e = All Pages | 5 |  |  |  |  |  |  |  |

| Bit   | Name           |                                                   | Function      |   |  |  |  |  |  |  |  |

| 7:0   | ADC0LTL[7:0    | O]       ADC0 Less-Than Data Word Low-Order Bits. |               |   |  |  |  |  |  |  |  |

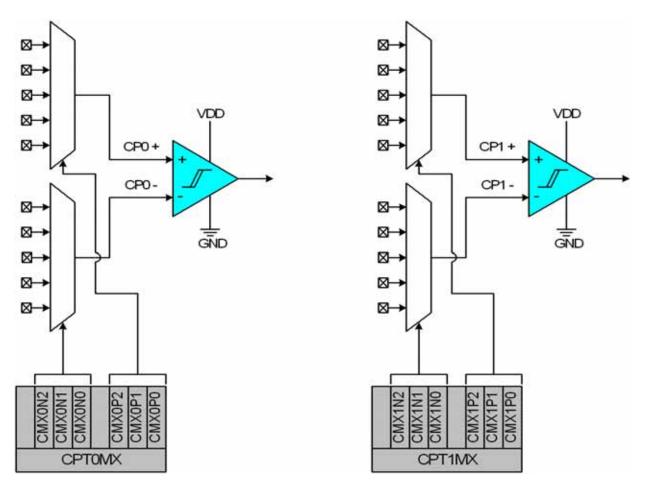

#### 8.1. Comparator Multiplexers

C8051F388/9/A/B devices include an analog input multiplexer to connect Port I/O pins to the comparator inputs. The Comparator inputs are selected in the CPTnMX registers (SFR Definition 8.5 and SFR Definition 8.6). The CMXnP2–CMXnP0 bits select the Comparator positive input; the CMXnN2–CMXnN0 bits select the Comparator negative input.

**Important Note About Comparator Inputs:** The Port pins selected as comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see Section "20.3. General Purpose Port I/O" on page 155).

Figure 8.4. Comparator Input Multiplexer Block Diagram

## SFR Definition 14.2. EMI0CF: External Memory Interface Configuration

| Bit   | 7 | 6        | 5 | 4    | 3        | 2 | 1         | 0 |

|-------|---|----------|---|------|----------|---|-----------|---|

| Name  |   | Reserved |   | EMD2 | EMD[1:0] |   | EALE[1:0] |   |

| Туре  | R | R/W      | R | R/W  | R/W      |   | R/W       |   |

| Reset | 0 | 0        | 0 | 0    | 0        | 0 | 1         | 1 |

#### SFR Address = 0x85; SFR Page = All Pages

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Unused    | Read = 0b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6   | Reserved  | Read = 0b; Must Write 0b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | Unused    | Read = 0b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4   | EMD2      | EMIF Multiplex Mode Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |           | <ul><li>0: EMIF operates in multiplexed address/data mode.</li><li>1: EMIF operates in non-multiplexed mode (separate address and data pins).</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3:2 | EMD[1:0]  | EMIF Operating Mode Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |           | These bits control the operating mode of the External Memory Interface.<br>00: Internal Only: MOVX accesses on-chip XRAM only. All effective addresses<br>alias to on-chip memory space.<br>01: Split Mode without Bank Select: Accesses below the on-chip XRAM boundary<br>are directed on-chip. Accesses above the on-chip XRAM boundary are directed<br>off-chip. 8-bit off-chip MOVX operations use the current contents of the Address<br>High port latches to resolve upper address byte. Note that in order to access<br>off-chip space, EMI0CN must be set to a page that is not contained in the on-chip<br>address space.<br>10: Split Mode with Bank Select: Accesses below the on-chip XRAM boundary are<br>directed on-chip. Accesses above the on-chip XRAM boundary are directed<br>off-chip. 8-bit off-chip MOVX operations use the contents of EMI0CN to determine<br>the high-byte of the address.<br>11: External Only: MOVX accesses off-chip XRAM only. On-chip XRAM is not visi-<br>ble to the CPU. |

| 1:0 | EALE[1:0] | <ul> <li>ALE Pulse-Width Select Bits (only has effect when EMD2 = 0).</li> <li>00: ALE high and ALE low pulse width = 1 SYSCLK cycle.</li> <li>01: ALE high and ALE low pulse width = 2 SYSCLK cycles.</li> <li>10: ALE high and ALE low pulse width = 3 SYSCLK cycles.</li> <li>11: ALE high and ALE low pulse width = 4 SYSCLK cycles.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

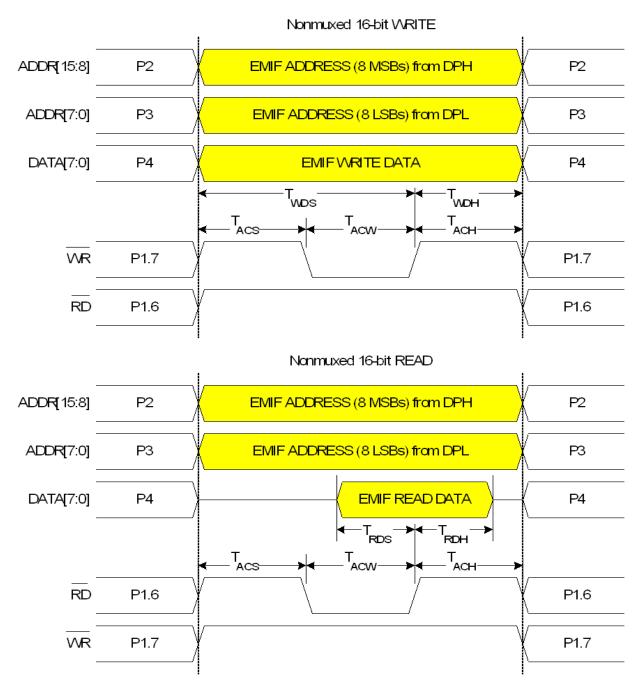

### 14.6.1. Non-multiplexed Mode

14.6.1.1. 16-bit MOVX: EMI0CF[4:2] = 101, 110, or 111

Figure 14.4. Non-Multiplexed 16-bit MOVX Timing

#### 14.6.1.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 110

Muxed 8-bit WRITE with Bank Select

Figure 14.6. Non-Multiplexed 8-bit MOVX with Bank Select Timing

### Table 15.2. Special Function Registers

| SFRs are liste | ed in alpha | betical order | r. All undefined SFR locations are reserved |

|----------------|-------------|---------------|---------------------------------------------|

|                |             |               |                                             |

| Register           | Address              | Page      | Description                             | Page |

|--------------------|----------------------|-----------|-----------------------------------------|------|

| ACC                | 0xE0                 | All Pages | Accumulator                             | 82   |

| ADC0CF             | 0xBC                 | All Pages | ADC0 Configuration                      | 49   |

| ADC0CN             | 0xE8                 | All Pages | ADC0 Control                            | 51   |

| ADC0GTH            | 0xC4                 | All Pages | ADC0 Greater-Than Compare High          | 52   |

| ADC0GTL            | 0xC3                 | All Pages | ADC0 Greater-Than Compare Low           | 52   |

| ADC0H              | 0xBE                 | All Pages | ADC0 High                               | 50   |

| ADC0L              | ADC0L 0xBD All Pages |           | ADC0 Low                                | 50   |

| ADCOLTH 0xC6 All F |                      | All Pages | ADC0 Less-Than Compare Word High        | 53   |

| ADC0LTL            | 0xC5                 | All Pages | ADC0 Less-Than Compare Word Low         | 53   |

| AMX0N              | 0xBA                 | All Pages | AMUX0 Negative Channel Select           | 57   |

| AMX0P              | 0xBB                 | All Pages | AMUX0 Positive Channel Select           | 56   |

| В                  | 0xF0                 | All Pages | B Register                              | 82   |

| CKCON              | 0x8E                 | All Pages | Clock Control                           | 225  |

| CKCON1             | 0xE4                 | F         | Clock Control 1                         | 226  |

| CLKMUL             | 0xB9                 | 0         | Clock Multiplier                        | 141  |

| CLKSEL             | 0xA9                 | All Pages | Clock Select                            | 138  |

| CPT0CN             | 0x9B                 | All Pages | Comparator0 Control                     | 63   |

| CPT0MD             | 0x9D                 | All Pages | Comparator0 Mode Selection              | 64   |

| CPT0MX             | 0x9F                 | All Pages | Comparator0 MUX Selection               | 68   |

| CPT1CN             | 0x9A                 | All Pages | Comparator1 Control                     | 65   |

| CPT1MD             | 0x9C                 | All Pages | Comparator1 Mode Selection              | 66   |

| CPT1MX             | 0x9E                 | All Pages | Comparator1 MUX Selection               | 69   |

| DPH                | 0x83                 | All Pages | Data Pointer High                       | 81   |

| DPL                | 0x82                 | All Pages | Data Pointer Low                        | 81   |

| EIE1               | 0xE6                 | All Pages | Extended Interrupt Enable 1             | 117  |

| EIE2               | 0xE7                 | All Pages | Extended Interrupt Enable 2             | 119  |

| EIP1               | 0xF6                 | All Pages | Extended Interrupt Priority 1           | 118  |

| EIP2               | 0xF7                 | All Pages | Extended Interrupt Priority 2           | 120  |

| EMIOCF             | 0x85                 | All Pages | External Memory Interface Configuration | 91   |

| EMIOCN             | 0xAA                 | All Pages | External Memory Interface Control       | 90   |

| EMIOTC             | 0x84                 | All Pages | External Memory Interface Timing        | 97   |

| FLKEY              | 0xB7                 | All Pages | Flash Lock and Key                      | 134  |

| FLSCL              | 0xB6                 | All Pages | Flash Scale                             | 135  |

#### **19.3. Clock Multiplier**

The C8051F388/9/A/B device includes a 48 MHz high-frequency oscillator instead of a 12 MHz oscillator and a 4x Clock Multiplier. For compatibility with C8051F34x and C8051F32x devices however, the CLK-MUL register (SFR Definition 19.4) behaves as if the Clock Multiplier is present and working.

### SFR Definition 19.4. CLKMUL: Clock Multiplier Control

| Bit   | 7     | 6       | 5      | 4 | 3 | 2 | 1           | 0 |  |

|-------|-------|---------|--------|---|---|---|-------------|---|--|

| Name  | MULEN | MULINIT | MULRDY |   |   |   | MULSEL[1:0] |   |  |

| Туре  | R     | R       | R      | R | R | R | R           |   |  |

| Reset | 1     | 1       | 1      | 0 | 0 | 0 | 0           | 0 |  |

SFR Address = 0xB9; SFR Page = 0

| Bit | Name        | Description                                                       |

|-----|-------------|-------------------------------------------------------------------|

| 7   | MULEN       | Clock Multiplier Enable Bit.<br>This bit always reads 1.          |

| 6   | MULINIT     | Clock Multiplier Initialize Bit.<br>This bit always reads 1.      |

| 5   | MULRDY      | Clock Multiplier Ready Bit.<br>This bit always reads 1.           |

| 4:2 | Unused      | Read = 000b; Write = don't care                                   |

| 1:0 | MULSEL[1:0] | Clock Multiplier Input Select Bits.<br>These bits always read 00. |

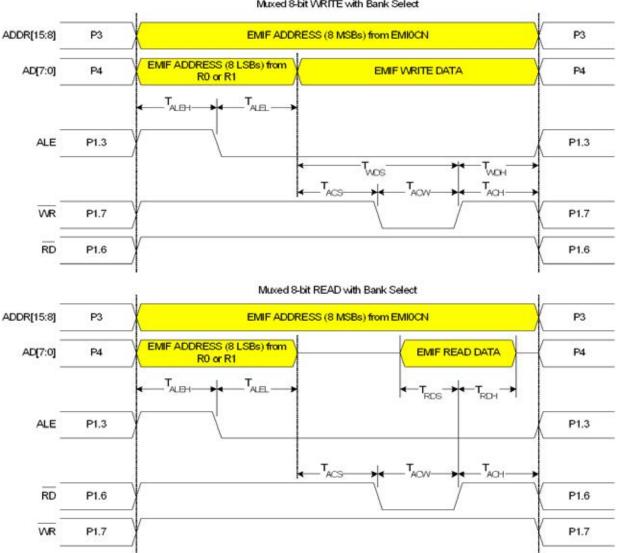

Figure 19.2. External Crystal Example

**Important Note on External Crystals:** Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device. The traces should be as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

When using an external crystal, the external oscillator drive circuit must be configured by software for *Crystal Oscillator Mode* or *Crystal Oscillator Mode with divide by 2 stage*. The divide by 2 stage ensures that the clock derived from the external oscillator has a duty cycle of 50%. The External Oscillator Frequency Control value (XFCN) must also be specified based on the crystal frequency (see SFR Definition 19.6).

When the crystal oscillator is first enabled, the external oscillator valid detector allows software to determine when the external system clock is valid and running. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure for starting the crystal is:

- 1. Configure XTAL1 and XTAL2 for analog I/O.

- 2. Disable the XTAL1 and XTAL2 digital output drivers by writing 1s to the appropriate bits in the Port Latch register.

- 3. Configure and enable the external oscillator.

- 4. Wait at least 1 ms.

- 5. Poll for XTLVLD  $\geq$  1.

- 6. Switch the system clock to the external oscillator.

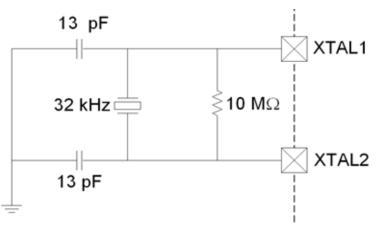

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 21.3 illustrates a typical SMBus transaction.

Figure 21.3. SMBus Transaction

#### 21.3.1. Transmitter Vs. Receiver

On the SMBus communications interface, a device is the "transmitter" when it is sending an address or data byte to another device on the bus. A device is a "receiver" when an address or data byte is being sent to it from another device on the bus. The transmitter controls the SDA line during the address or data byte. After each byte of address or data information is sent by the transmitter, the receiver sends an ACK or NACK bit during the ACK phase of the transfer, during which time the receiver controls the SDA line.

#### 21.3.2. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see Section "21.3.5. SCL High (SMBus Free) Timeout" on page 169). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

#### 21.3.3. Clock Low Extension

SMBus provides a clock synchronization mechanism, similar to I2C, which allows devices with different speed capabilities to coexist on the bus. A clock-low extension is used during a transfer in order to allow slower slave devices to communicate with faster masters. The slave may temporarily hold the SCL line LOW to extend the clock low period, effectively decreasing the serial clock frequency.

#### 21.3.4. SCL Low Timeout

If the SCL line is held low by a slave device on the bus, no further communication is possible. Furthermore, the master cannot force the SCL line high to correct the error condition. To solve this problem, the SMBus protocol specifies that devices participating in a transfer must detect any clock cycle held low longer than 25 ms as a "timeout" condition. Devices that have detected the timeout condition must reset the communication no later than 10 ms after detecting the timeout condition.

For the SMBus0 interface, Timer 3 is used to implement SCL low timeouts. Timer 4 is used on the SMBus1 interface for SCL low timeouts. The SCL low timeout feature is enabled by setting the SMBnTOE bit in SMBnCF. The associated timer is forced to reload when SCL is high, and allowed to count when SCL is

### 22.2. Operational Modes

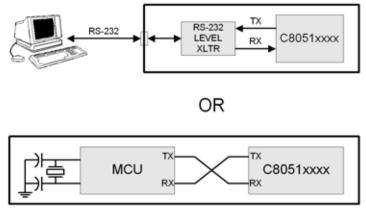

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown in Figure 22.3.

Figure 22.3. UART Interconnect Diagram

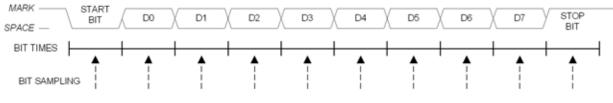

#### 22.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 22.4. 8-Bit UART Timing Diagram

## SFR Definition 22.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|------------|-----|---|---|---|---|---|---|--|--|--|

| Name  | SBUF0[7:0] |     |   |   |   |   |   |   |  |  |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |  |  |

| Reset | 0          | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

SFR Address = 0x99; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                    |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBUF0[7:0] | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                                                                                                                                                                      |

|     |            | This SFR accesses two registers; a transmit shift register and a receive latch register.<br>When data is written to SBUF0, it goes to the transmit shift register and is held for<br>serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of<br>SBUF0 returns the contents of the receive latch. |

## Table 22.1. Timer Settings for Standard Baud Rates Using Internal Oscillator

|            | Target<br>Baud | Actual<br>Baud | Baud<br>Rate | Oscillator<br>Divide | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale | T1M | Timer 1<br>Reload |

|------------|----------------|----------------|--------------|----------------------|-----------------------|-------------------------|-----|-------------------|

|            | Rate (bps)     | Rate (bps)     | Error        | Factor               | course                | select*                 |     | Value (hex)       |

|            | 230400         | 230769         | 0.16%        | 52                   | SYSCLK                | XX                      | 1   | 0xE6              |

| MHz        | 115200         | 115385         | 0.16%        | 104                  | SYSCLK                | XX                      | 1   | 0xCC              |

| 2          | 57600          | 57692          | 0.16%        | 208                  | SYSCLK                | XX                      | 1   | 0x98              |

| 1          | 28800          | 28846          | 0.16%        | 416                  | SYSCLK                | XX                      | 1   | 0x30              |

|            | 14400          | 14423          | 0.16%        | 832                  | SYSCLK/4              | 01                      | 0   | 0x98              |

| SCLK       | 9600           | 9615           | 0.16%        | 1248                 | SYSCLK/4              | 01                      | 0   | 0x64              |

| SΥS        | 2400           | 2404           | 0.16%        | 4992                 | SYSCLK / 12           | 00                      | 0   | 0x30              |

| S          | 1200           | 1202           | 0.16%        | 9984                 | SYSCLK / 48           | 10                      | 0   | 0x98              |

| Ν          | 230400         | 230769         | 0.16%        | 104                  | SYSCLK                | XX                      | 1   | 0xCC              |

| MHz        | 115200         | 115385         | 0.16%        | 208                  | SYSCLK                | XX                      | 1   | 0x98              |

| 24 N       | 57600          | 57692          | 0.16%        | 416                  | SYSCLK                | XX                      | 1   | 0x30              |

| 2          | 28800          | 28846          | 0.16%        | 832                  | SYSCLK/4              | 01                      | 0   | 0x98              |

|            | 14400          | 14423          | 0.16%        | 1664                 | SYSCLK/4              | 01                      | 0   | 0x30              |

| SCLK       | 9600           | 9615           | 0.16%        | 2496                 | SYSCLK / 12           | 00                      | 0   | 0x98              |

| SΥS        | 2400           | 2404           | 0.16%        | 9984                 | SYSCLK / 48           | 10                      | 0   | 0x98              |

| S          | 1200           | 1202           | 0.16%        | 19968                | SYSCLK / 48           | 10                      | 0   | 0x30              |

| Ŗ          | 230400         | 230769         | 0.16%        | 208                  | SYSCLK                | XX                      | 1   | 0x98              |

| MHz        | 115200         | 115385         | 0.16%        | 416                  | SYSCLK                | XX                      | 1   | 0x30              |

| 48         | 57600          | 57692          | 0.16%        | 832                  | SYSCLK/4              | 01                      | 0   | 0x98              |

|            | 28800          | 28846          | 0.16%        | 1664                 | SYSCLK/4              | 01                      | 0   | 0x30              |

| ا <u>۲</u> | 14400          | 14388          | 0.08%        | 3336                 | SYSCLK / 12           | 00                      | 0   | 0x75              |

| SCLK       | 9600           | 9615           | 0.16%        | 4992                 | SYSCLK / 12           | 00                      | 0   | 0x30              |

| SΥ         | 2400           | 2404           | 0.16%        | 19968                | SYSCLK / 48           | 10                      | 0   | 0x30              |

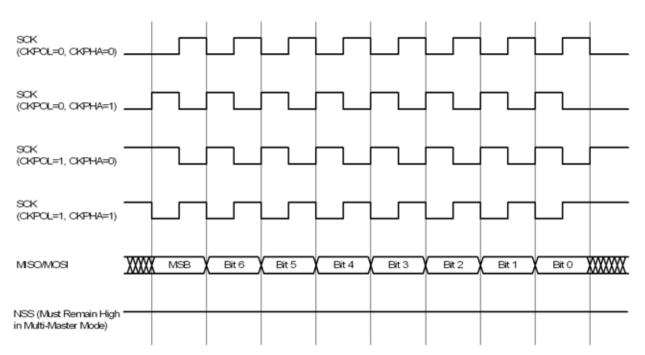

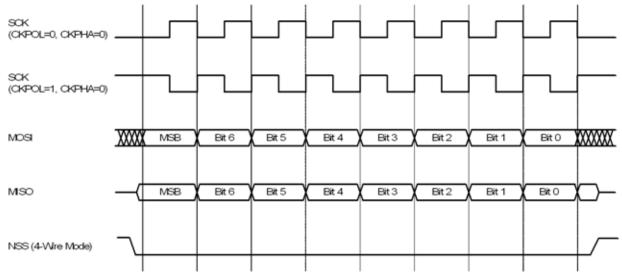

## SFR Definition 24.1. SPI0CFG: SPI0 Configuration

| Bit   | 7      | 6     | 5     | 4     | 3      | 2     | 1    | 0     |

|-------|--------|-------|-------|-------|--------|-------|------|-------|

| Name  | SPIBSY | MSTEN | СКРНА | CKPOL | SLVSEL | NSSIN | SRMT | RXBMT |

| Туре  | R      | R/W   | R/W   | R/W   | R      | R     | R    | R     |

| Reset | 0      | 0     | 0     | 0     | 0      | 1     | 1    | 1     |

#### SFR Address = 0xA1; SFR Page = All Pages

| Bit   | Name            | Function                                                                                                                                                                                 |

|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | SPIBSY          | SPI Busy.                                                                                                                                                                                |

|       |                 | This bit is set to logic 1 when a SPI transfer is in progress (master or slave mode).                                                                                                    |

| 6     | MSTEN           | Master Mode Enable.                                                                                                                                                                      |

|       |                 | 0: Disable master mode. Operate in slave mode.                                                                                                                                           |

|       |                 | 1: Enable master mode. Operate as a master.                                                                                                                                              |

| 5     | CKPHA           | SPI0 Clock Phase.                                                                                                                                                                        |

|       |                 | 0: Data centered on first edge of SCK period.*                                                                                                                                           |

|       |                 | 1: Data centered on second edge of SCK period.*                                                                                                                                          |

| 4     | CKPOL           | SPI0 Clock Polarity.                                                                                                                                                                     |

|       |                 | 0: SCK line low in idle state.                                                                                                                                                           |

|       |                 | 1: SCK line high in idle state.                                                                                                                                                          |

| 3     | SLVSEL          | Slave Selected Flag.                                                                                                                                                                     |

|       |                 | This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected                                                                                                   |

|       |                 | slave. It is cleared to logic 0 when NSS is high (slave not selected). This bit does not indicate the instantaneous value at the NSS pin, but rather a de-glitched ver-                  |

|       |                 | sion of the pin input.                                                                                                                                                                   |

| 2     | NSSIN           | NSS Instantaneous Pin Input.                                                                                                                                                             |

|       |                 | This bit mimics the instantaneous value that is present on the NSS port pin at the                                                                                                       |

|       |                 | time that the register is read. This input is not de-glitched.                                                                                                                           |

| 1     | SRMT            | Shift Register Empty (valid in slave mode only).                                                                                                                                         |

|       |                 | This bit will be set to logic 1 when all data has been transferred in/out of the shift                                                                                                   |

|       |                 | register, and there is no new information available to read from the transmit buffer<br>or write to the receive buffer. It returns to logic 0 when a data byte is transferred to         |

|       |                 | the shift register from the transmit buffer or by a transition on SCK. SRMT = 1 when                                                                                                     |

|       |                 | in Master Mode.                                                                                                                                                                          |

| 0     | RXBMT           | Receive Buffer Empty (valid in slave mode only).                                                                                                                                         |

|       |                 | This bit will be set to logic 1 when the receive buffer has been read and contains no                                                                                                    |

|       |                 | new information. If there is new information available in the receive buffer that has not been read, this bit will return to logic 0. RXBMT = 1 when in Master Mode.                     |

|       | la classa and l |                                                                                                                                                                                          |

| Note: |                 | data on MOSI is sampled in the center of each data bit. In master mode, data on MISO is<br>/SCLK before the end of each data bit, to provide maximum settling time for the slave device. |

|       | •               | for timing parameters.                                                                                                                                                                   |

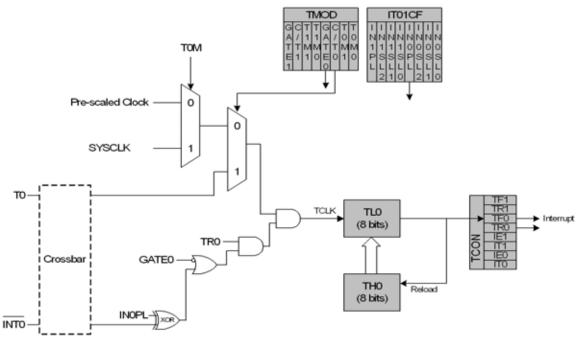

Figure 25.2. T0 Mode 2 Block Diagram

#### 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates or overflow conditions for other peripherals. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

### SFR Definition 25.5. TL0: Timer 0 Low Byte

| Bit   | 7                                        | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------------------------------------|----------|---|---|---|---|---|---|--|--|

| Nam   | 9                                        | TL0[7:0] |   |   |   |   |   |   |  |  |

| Туре  | •                                        | R/W      |   |   |   |   |   |   |  |  |

| Rese  | <b>t</b> 0                               | 0        | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A | SFR Address = 0x8A; SFR Page = All Pages |          |   |   |   |   |   |   |  |  |

| Bit   | Name                                     |          |   |   |   |   |   |   |  |  |

| SERF | 4001622 = 0.001 | A, SER Faye = All Fayes |

|------|-----------------|-------------------------|

| Dit  | Nomo            |                         |

| Bit | Name     | Function                                                |

|-----|----------|---------------------------------------------------------|

| 7:0 | TL0[7:0] | Timer 0 Low Byte.                                       |

|     |          | The TL0 register is the low byte of the 16-bit Timer 0. |

## SFR Definition 25.6. TL1: Timer 1 Low Byte

| Bit   | Bit 7 6 5 4 3 2 |                                                         |             |     |          |   |   | 0 |  |

|-------|-----------------|---------------------------------------------------------|-------------|-----|----------|---|---|---|--|

| Nam   | e               |                                                         |             | TL1 | [7:0]    |   |   |   |  |

| Туре  | 9               |                                                         |             | R/  | W        |   |   |   |  |

| Rese  | et 0            | 0                                                       | 0           | 0   | 0        | 0 | 0 | 0 |  |

| SFR A | ddress = 0x8    | B; SFR Page                                             | = All Pages |     |          |   |   |   |  |

| Bit   | Name            |                                                         |             |     | Function |   |   |   |  |

| 7:0   | TL1[7:0]        | 1[7:0] Timer 1 Low Byte.                                |             |     |          |   |   |   |  |

|       |                 | The TL1 register is the low byte of the 16-bit Timer 1. |             |     |          |   |   |   |  |

## SFR Definition 25.20. TMR4RLL: Timer 4 Reload Register Low Byte

| Bit    | 7            | 6            | 5   | 4 | 3        | 2 | 1 | 0 |  |  |  |

|--------|--------------|--------------|-----|---|----------|---|---|---|--|--|--|

| Name   |              | TMR4RLL[7:0] |     |   |          |   |   |   |  |  |  |

| Туре   |              | R/W          |     |   |          |   |   |   |  |  |  |

| Reset  | 0            | 0            | 0   | 0 | 0        | 0 | 0 | 0 |  |  |  |

| SFR Ad | dress = 0x92 | 2; SFR Page  | = F |   |          |   |   |   |  |  |  |

| D:4    | Nama         |              |     |   | E.mation |   |   |   |  |  |  |

| Bit | Name         | Function                                                    |

|-----|--------------|-------------------------------------------------------------|

| 7:0 | TMR4RLL[7:0] | Timer 4 Reload Register Low Byte.                           |

|     |              | TMR4RLL holds the low byte of the reload value for Timer 4. |

### SFR Definition 25.21. TMR4RLH: Timer 4 Reload Register High Byte

| Bit   | 7              | 6                                                            | 5   | 4 | 3        | 2 | 1 | 0 |  |  |  |

|-------|----------------|--------------------------------------------------------------|-----|---|----------|---|---|---|--|--|--|

| Nam   | e              | TMR4RLH[7:0]                                                 |     |   |          |   |   |   |  |  |  |

| Туре  | 9              |                                                              |     | R | W        |   |   |   |  |  |  |

| Rese  | et 0           | 0                                                            | 0   | 0 | 0        | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0x93 | ; SFR Page                                                   | = F |   |          |   |   |   |  |  |  |

| Bit   | Name           |                                                              |     |   | Function |   |   |   |  |  |  |

| 7:0   | TMR4RLH[7:0    | _H[7:0] Timer 4 Reload Register High Byte.                   |     |   |          |   |   |   |  |  |  |

|       |                | TMR4RLH holds the high byte of the reload value for Timer 4. |     |   |          |   |   |   |  |  |  |

## SFR Definition 25.22. TMR4L: Timer 4 Low Byte

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|------------|---|---|---|---|---|---|--|--|--|

| Name  |   | TMR4L[7:0] |   |   |   |   |   |   |  |  |  |

| Туре  |   | R/W        |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

#### SFR Address = 0x94; SFR Page = F

| Bit | Name | Function                                                                                                                                      |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 |      | Timer 4 Low Byte.                                                                                                                             |

|     |      | In 16-bit mode, the TMR4L register contains the low byte of the 16-bit Timer 4. In 8-bit mode, TMR4L contains the 8-bit low byte timer value. |

## SFR Definition 25.24. TMR5CN: Timer 5 Control

| Bit   | 7    | 6    | 5      | 4 | 3       | 2   | 1 | 0      |

|-------|------|------|--------|---|---------|-----|---|--------|

| Name  | TF5H | TF5L | TF5LEN |   | T5SPLIT | TR5 |   | T5XCLK |

| Туре  | R/W  | R/W  | R/W    | R | R/W     | R/W | R | R/W    |

| Reset | 0    | 0    | 0      | 0 | 0       | 0   | 0 | 0      |

#### SFR Address = 0xC8; SFR Page = F; Bit-Addressable

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | TF5H    | <b>Timer 5 High Byte Overflow Flag.</b><br>Set by hardware when the Timer 5 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 5 overflows from 0xFFFF to 0x0000. When the Timer 5 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 5 interrupt service routine. This bit is not automatically cleared by hardware.                |  |  |  |

| 6   | TF5L    | <b>Timer 5 Low Byte Overflow Flag.</b><br>Set by hardware when the Timer 5 low byte overflows from 0xFF to 0x00. TF5L will be set when the low byte overflows regardless of the Timer 5 mode. This bit is not automatically cleared by hardware.                                                                                                                                              |  |  |  |

| 5   | TF5LEN  | Timer 5 Low Byte Interrupt Enable.When set to 1, this bit enables Timer 5 Low Byte interrupts. If Timer 5 interrupts are<br>also enabled, an interrupt will be generated when the low byte of Timer 5 overflows.                                                                                                                                                                              |  |  |  |

| 4   | Unused  | Read = 0b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 3   | T5SPLIT | Timer 5 Split Mode Enable.When this bit is set, Timer 5 operates as two 8-bit timers with auto-reload.0: Timer 5 operates in 16-bit auto-reload mode.1: Timer 5 operates as two 8-bit auto-reload timers.                                                                                                                                                                                     |  |  |  |

| 2   | TR5     | <b>Timer 5 Run Control.</b><br>Timer 5 is enabled by setting this bit to 1. In 8-bit mode, this bit enables/disables<br>TMR5H only; TMR5L is always enabled in split mode.                                                                                                                                                                                                                    |  |  |  |

| 1   | Unused  | Read = 0b; Write = don't care.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 0   | T5XCLK  | Timer 5 External Clock Select.This bit selects the external clock source for Timer 5. However, the Timer 5 ClockSelect bits (T5MH and T5ML in register CKCON1) may still be used to selectbetween the external clock and the system clock for either timer.0: Timer 5 clock is the system clock divided by 12.1: Timer 5 clock is the external clock divided by 8 (synchronized with SYSCLK). |  |  |  |