Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 48 MIPS                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 4.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                     |

| Data Converters            | A/D 21x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-LQFP                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f389-b-gq |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

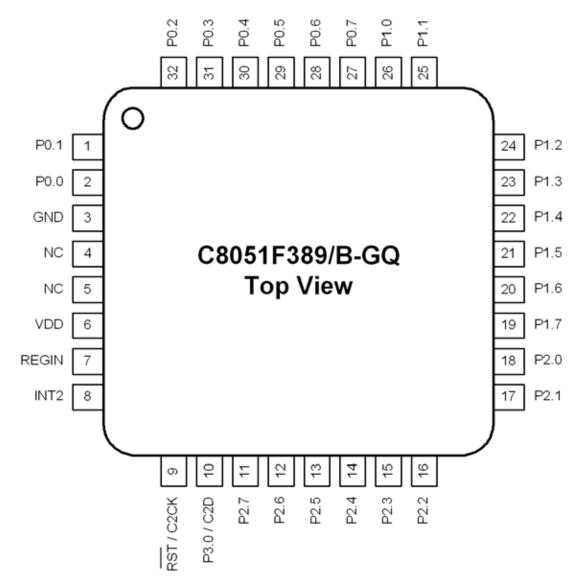

Figure 3.4. LQFP-32 (C8051F389/B) Pinout Diagram (Top View)

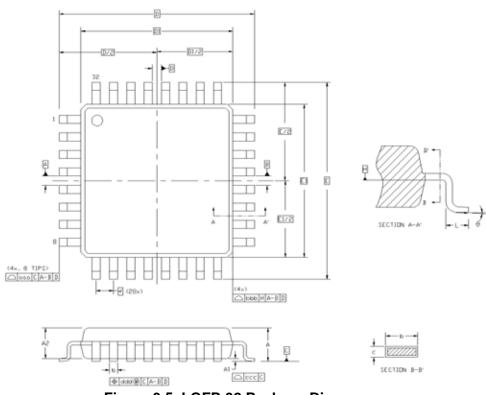

Figure 3.5. LQFP-32 Package Diagram

| Dimension | Min      | Nom      | Мах  | Dimension | Min  | Nom      | Мах  |

|-----------|----------|----------|------|-----------|------|----------|------|

| A         | _        | —        | 1.60 | E         |      | 9.00 BSC |      |

| A1        | 0.05     | —        | 0.15 | E1        |      | 7.00 BSC |      |

| A2        | 1.35     | 1.40     | 1.45 | L         | 0.45 | 0.60     | 0.75 |

| b         | 0.30     | 0.37     | 0.45 | aaa       |      | 0.20     |      |

| С         | 0.09     | —        | 0.20 | bbb       |      | 0.20     |      |

| D         | 9.00 BSC |          |      | CCC       |      | 0.10     |      |

| D1        | 7.00 BSC |          |      | ddd       |      | 0.20     |      |

| е         |          | 0.80 BSC |      | q         | 0°   | 3.5°     | 7°   |

#### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS-026, variation BBA.

- 4. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# SFR Definition 8.1. CPT0CN: Comparator0 Control

| Bit   | 7     | 6      | 5      | 4      | 3    | 2       | 1    | 0       |

|-------|-------|--------|--------|--------|------|---------|------|---------|

| Name  | CP0EN | CP0OUT | CP0RIF | CP0FIF | CP0H | /P[1:0] | CP0H | YN[1:0] |

| Туре  | R/W   | R      | R/W    | R/W    | R/W  |         | R/   | W       |

| Reset | 0     | 0      | 0      | 0      | 0    | 0       | 0    | 0       |

SFR Address = 0x9B; SFR Page = All Pages

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | CP0EN       | Comparator0 Enable Bit.                                                       |

|     |             | 0: Comparator0 Disabled.                                                      |

|     |             | 1: Comparator0 Enabled.                                                       |

| 6   | CP0OUT      | Comparator0 Output State Flag.                                                |

|     |             | 0: Voltage on CP0+ < CP0                                                      |

|     |             | 1: Voltage on CP0+ > CP0                                                      |

| 5   | CP0RIF      | Comparator0 Rising-Edge Flag. Must be cleared by software.                    |

|     |             | 0: No Comparator0 Rising Edge has occurred since this flag was last cleared.  |

|     |             | 1: Comparator0 Rising Edge has occurred.                                      |

| 4   | CP0FIF      | Comparator0 Falling-Edge Flag. Must be cleared by software.                   |

|     |             | 0: No Comparator0 Falling-Edge has occurred since this flag was last cleared. |

|     |             | 1: Comparator0 Falling-Edge has occurred.                                     |

| 3:2 | CP0HYP[1:0] | Comparator0 Positive Hysteresis Control Bits.                                 |

|     |             | 00: Positive Hysteresis Disabled.                                             |

|     |             | 01: Positive Hysteresis = 5 mV.                                               |

|     |             | 10: Positive Hysteresis = 10 mV.                                              |

|     |             | 11: Positive Hysteresis = 20 mV.                                              |

| 1:0 | CP0HYN[1:0] | Comparator0 Negative Hysteresis Control Bits.                                 |

|     |             | 00: Negative Hysteresis Disabled.                                             |

|     |             | 01: Negative Hysteresis = 5 mV.                                               |

|     |             | 10: Negative Hysteresis = 10 mV.                                              |

|     |             | 11: Negative Hysteresis = 20 mV.                                              |

# SFR Definition 8.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5             | 4      | 3 | 2 | 1    | 0      |

|-------|---|---|---------------|--------|---|---|------|--------|

| Name  |   |   | <b>CP0RIE</b> | CP0FIE |   |   | CP0M | D[1:0] |

| Туре  | R | R | R/W           | R/W    | R | R | R/W  |        |

| Reset | 0 | 0 | 0             | 0      | 0 | 0 | 1    | 0      |

#### SFR Address = 0x9D; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 5   | CPORIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                        |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                     |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

| Mnemonic                   | Description                                            | Bytes          | Clock<br>Cycles |  |

|----------------------------|--------------------------------------------------------|----------------|-----------------|--|

| ANL C, bit                 | AND direct bit to Carry                                | 2              | 2               |  |

| ANL C, /bit                | t AND complement of direct bit to Carry                |                |                 |  |

| ORL C, bit                 | OR direct bit to carry                                 | 2              | 2               |  |

| ORL C, /bit                | OR complement of direct bit to Carry                   | 2              | 2               |  |

| MOV C, bit                 | Move direct bit to Carry                               | 2              | 2               |  |

| MOV bit, C                 | Move Carry to direct bit                               | 2              | 2               |  |

| Program Flow               |                                                        | •              |                 |  |

| Timings are listed with th | e PFE on and FLRT = 0. Extra cycles are required for t | oranches if Fl | _RT = 1.        |  |

| JC rel                     | Jump if Carry is set                                   | 2              | 2/4             |  |

| JNC rel                    | Jump if Carry is not set                               | 2              | 2/4             |  |

| JB bit, rel                | Jump if direct bit is set                              | 3              | 3/5             |  |

| JNB bit, rel               | Jump if direct bit is not set                          | 3              | 3/5             |  |

| JBC bit, rel               | Jump if direct bit is set and clear bit                | 3              | 3/5             |  |

| ACALL addr11               | Absolute subroutine call                               | 2              | 4               |  |

| LCALL addr16               | Long subroutine call                                   | 3              | 5               |  |

| RET                        | Return from subroutine                                 | 1              | 6               |  |

| RETI                       | Return from interrupt                                  | 1              | 6               |  |

| AJMP addr11                | Absolute jump                                          | 2              | 4               |  |

| LJMP addr16                | Long jump                                              | 3              | 5               |  |

| SJMP rel                   | Short jump (relative address)                          | 2              | 4               |  |

| JMP @A+DPTR                | Jump indirect relative to DPTR                         | 1              | 4               |  |

| JZ rel                     | Jump if A equals zero                                  | 2              | 2/4             |  |

| JNZ rel                    | Jump if A does not equal zero                          | 2              | 2/4             |  |

| CJNE A, direct, rel        | Compare direct byte to A and jump if not equal         | 3              | 4/6             |  |

| CJNE A, #data, rel         | Compare immediate to A and jump if not equal           | 3              | 3/5             |  |

| CJNE Rn, #data, rel        | Compare immediate to Register and jump if not equal    | 3              | 3/5             |  |

| CJNE @Ri, #data, rel       | Compare immediate to indirect and jump if not equal    | 3              | 4/6             |  |

| DJNZ Rn, rel               | Decrement Register and jump if not zero                | 2              | 2/4             |  |

| DJNZ direct, rel           | Decrement direct byte and jump if not zero             | 3              | 3/5             |  |

| NOP                        | No operation                                           | 1              | 1               |  |

# Table 11.1. CIP-51 Instruction Set Summary (Continued)

## SFR Definition 11.3. SP: Stack Pointer

| Bit   | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------------|---|---|---|---|---|---|---|

| Name  | SP[7:0]         |   |   |   |   |   |   |   |

| Туре  | R/W             |   |   |   |   |   |   |   |

| Reset | 0 0 0 0 0 1 1 1 |   |   |   |   |   |   |   |

SFR Address = 0x81; SFR Page = All Pages

| Bit | Name    | Function                                                                                                                                                                       |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

## SFR Definition 11.4. ACC: Accumulator

| Bit   | 7   | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-----------------|---|---|---|---|---|---|

| Name  |     | ACC[7:0]        |   |   |   |   |   |   |

| Туре  | R/W |                 |   |   |   |   |   |   |

| Reset | 0   | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |

|       |     |                 |   |   |   | 0 | 0 | 0 |

SFR Address = 0xE0; SFR Page = All Pages; Bit-Addressable

| Bit | Name     | Function                                                    |

|-----|----------|-------------------------------------------------------------|

| 7:0 | ACC[7:0] | Accumulator.                                                |

|     |          | This register is the accumulator for arithmetic operations. |

## SFR Definition 11.5. B: B Register

| Bit   | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|---|---|---|---|---|---|---|

| Name  | B[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W    |   |   |   |   |   |   |   |

| Reset | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xF0; SFR Page = All Pages; Bit-Addressable

| Bit | Name   | Function                                                                        |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

| Address | Page   | 0(8)   | 1(9)          | 2(A)     | 3(B)     | 4(C)             | 5(D)     | 6(E)     | 7(F)    |

|---------|--------|--------|---------------|----------|----------|------------------|----------|----------|---------|

| F8      |        | SPI0CN | PCA0L         | PCA0H    | PCA0CPL0 | PCA0CPH0         | PCA0CPL4 | PCA0CPH4 | VDM0CN  |

| F0      |        | В      | P0MDIN        | P1MDIN   | P2MDIN   | P3MDIN           | P4MDIN   | EIP1     | EIP2    |

| E8      |        | ADC0CN | PCA0CPL1      | PCA0CPH1 | PCA0CPL2 | PCA0CPH2         | PCA0CPL3 | PCA0CPH3 | RSTSRC  |

| E0      | 0<br>F | ACC    | XBR0          | XBR1     | XBR2     | IT01CF<br>CKCON1 | SMOD1    | EIE1     | EIE2    |

| D8      |        | PCA0CN | PCA0MD        | PCA0CPM0 | PCA0CPM1 | PCA0CPM2         | PCA0CPM3 | PCA0CPM4 | P3SKIP  |

| D0      |        | PSW    | <b>REF0CN</b> | SCON1    | SBUF1    | P0SKIP           | P1SKIP   | P2SKIP   |         |

| 00      | 0      | TMR2CN | DECOLONI      | TMR2RLL  | TMR2RLH  | TMR2L            | TMR2H    | SMB0ADM  | SMB0ADR |

| C8      | F      | TMR5CN | REG01CN       | TMR5RLL  | TMR5RLH  | TMR5L            | TMR5H    | SMB1ADM  | SMB1ADR |

| 0       | 0      | SMB0CN | SMB0CF        | SMB0DAT  |          |                  |          |          | D4      |

| C0      | F      | SMB1CN | SMB1CF        | SMB1DAT  | ADC0GTL  | ADC0GTH          | ADC0LTL  | ADC0LTH  | P4      |

| B8      | 0      | IP     | CLKMUL        |          |          | ADC0CF           | ADC0L    |          |         |

| БО      | F      | IP     | SMBTC         | AMX0N    | AMX0P    |                  | ADCOL    | ADC0H    | SFRPAGE |

| B0      |        | P3     | OSCXCN        | OSCICN   | OSCICL   | SBRLL1           | SBRLH1   | FLSCL    | FLKEY   |

| A8      |        | IE     | CLKSEL        | EMIOCN   |          | SBCON1           |          | P4MDOUT  | PFE0CN  |

| A0      |        | P2     | SPI0CFG       | SPI0CKR  | SPI0DAT  | POMDOUT          | P1MDOUT  | P2MDOUT  | P3MDOUT |

| 98      |        | SCON0  | SBUF0         | CPT1CN   | CPT0CN   | CPT1MD           | CPT0MD   | CPT1MX   | CPT0MX  |

| 90      | 0      | P1     | TMR3CN        | TMR3RLL  | TMR3RLH  | TMR3L            | TMR3H    |          |         |

| 90      | F      | FI     | TMR4CN        | TMR4RLL  | TMR4RLH  | TMR4L            | TMR4H    |          |         |

| 88      |        | TCON   | TMOD          | TL0      | TL1      | TH0              | TH1      | CKCON    | PSCTL   |

| 80      |        | P0     | SP            | DPL      | DPH      | EMI0TC           | EMI0CF   | OSCLCN   | PCON    |

|         |        | 0(8)   | 1(9)          | 2(A)     | 3(B)     | 4(C)             | 5(D)     | 6(E)     | 7(F)    |

| Note    |        |        |               |          |          | •                | •        | -        |         |

## Table 15.1. Special Function Register (SFR) Memory Map

Notes:

1. SFR Addresses ending in 0x0 or 0x8 are bit-addressable locations and can be used with bitwise instructions.

2. Unless indicated otherwise, SFRs are available on both page 0 and page F.

# 16. Interrupts

The C8051F388/9/A/B include an extended interrupt system supporting multiple interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE, EIE1, or EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

**Note:** Any instruction that clears a bit to disable an interrupt should be immediately followed by an instruction that has two or more opcode bytes. Using EA (global interrupt enable) as an example:

```

// in 'C':

EA = 0; // clear EA bit.

EA = 0; // this is a dummy instruction with two-byte opcode.

; in assembly:

CLR EA ; clear EA bit.

CLR EA ; this is a dummy instruction with two-byte opcode.

```

For example, if an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears a bit to disable an interrupt source), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the enable bit will return a 0 inside the interrupt service routine. When the bit-clearing opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

### 16.1. MCU Interrupt Sources and Vectors

The C8051F388/9/A/B MCUs support several interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 16.1. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 16.1.1. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP, EIP1, or EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 16.1.

#### 16.1.2. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 6 system clock cycles: 1 clock cycle to detect the interrupt and 5 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 20 system clock cycles: 1 clock cycle to detect the interrupt, 6 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 5 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

Note that the CPU is stalled during Flash write operations. Interrupt service latency will be increased for interrupts occurring while the CPU is stalled. The latency for these situations will be determined by the standard interrupt service procedure (as described above) and the amount of time the CPU is stalled.

#### **16.2.** Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described in this section. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

## SFR Definition 17.2. RSTSRC: Reset Source

| Bit   | 7        | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|----------|--------|--------|--------|--------|--------|--------|--------|

| Name  | Reserved | FERROR | CORSEF | SWRSF  | WDTRSF | MCDRSF | PORSF  | PINRSF |

| Туре  | R/W      | R      | R/W    | R/W    | R      | R/W    | R/W    | R      |

| Reset | Varies   | Varies | Varies | Varies | Varies | Varies | Varies | Varies |

SFR Address = 0xEF; SFR Page = All Pages

| Name     | Description                                                                                    | Write                                                                                                                                                                                                                                                                                                             | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved |                                                                                                | Must Write 0b.                                                                                                                                                                                                                                                                                                    | Read = 0b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| FERROR   | Flash Error Reset Flag.                                                                        | N/A                                                                                                                                                                                                                                                                                                               | Set to 1 if Flash<br>read/write/erase error<br>caused the last reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CORSEF   | Comparator0 Reset Enable<br>and Flag.                                                          | Writing a 1 enables Com-<br>parator0 as a reset source<br>(active-low).                                                                                                                                                                                                                                           | Set to 1 if Comparator0 caused the last reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SWRSF    | Software Reset Force and Flag.                                                                 | Writing a 1 forces a sys-<br>tem reset.                                                                                                                                                                                                                                                                           | Set to 1 if last reset was<br>caused by a write to<br>SWRSF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WDTRSF   | Watchdog Timer Reset Flag.                                                                     | N/A                                                                                                                                                                                                                                                                                                               | Set to 1 if Watchdog Timer<br>overflow caused the last<br>reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MCDRSF   | Missing Clock Detector<br>Enable and Flag.                                                     | Writing a 1 enables the<br>Missing Clock Detector.<br>The MCD triggers a reset<br>if a missing clock condition<br>is detected.                                                                                                                                                                                    | Set to 1 if Missing Clock<br>Detector timeout caused<br>the last reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PORSF    | Power-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | Writing a 1 enables the<br>V <sub>DD</sub> monitor as a reset<br>source.<br>Writing 1 to this bit<br>before the V <sub>DD</sub> monitor<br>is enabled and stabilized<br>may cause a system<br>reset.                                                                                                              | Set to 1 anytime a power-<br>on or V <sub>DD</sub> monitor reset<br>occurs.<br>When set to 1 all other<br>RSTSRC flags are inde-<br>terminate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PINRSF   | HW Pin Reset Flag.                                                                             | N/A                                                                                                                                                                                                                                                                                                               | Set to 1 if RST pin caused the last reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| _        | Reserved<br>FERROR<br>CORSEF<br>SWRSF<br>WDTRSF<br>MCDRSF                                      | ReservedReservedFERRORFlash Error Reset Flag.CORSEFComparator0 Reset Enable<br>and Flag.SWRSFSoftware Reset Force and<br>Flag.WDTRSFWatchdog Timer Reset Flag.MCDRSFMissing Clock Detector<br>Enable and Flag.PORSFPower-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Enable. | ReservedMust Write Ob.FERRORFlash Error Reset Flag.N/ACORSEFComparator0 Reset Enable<br>and Flag.Writing a 1 enables Com-<br>parator0 as a reset source<br>(active-low).SWRSFSoftware Reset Force and<br>Flag.Writing a 1 forces a sys-<br>tem reset.WDTRSFWatchdog Timer Reset Flag.N/AMCDRSFMissing Clock Detector<br>Enable and Flag.N/AMCDRSFPower-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>is detected.Writing a 1 enables the<br>V <sub>DD</sub> monitor as a reset<br>source.PORSFPower-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>is detected.Writing a 1 enables the<br>V <sub>DD</sub> monitor as a reset<br>source.PORSFPower-On / V <sub>DD</sub> Monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>Reset Flag, and V <sub>DD</sub> monitor<br>is enabled and stabilized<br>may cause a system<br>reset. |

## SFR Definition 20.14. P2MDOUT: Port 2 Output Mode

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|--------------|---|---|---|---|---|---|

| Name  |   | P2MDOUT[7:0] |   |   |   |   |   |   |

| Туре  |   | R/W          |   |   |   |   |   |   |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xA6; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2MDOUT[7:0] | Output Configuration Bits for P2.7–P2.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P2MDIN is logic 0.<br>0: Corresponding P2.n Output is open-drain.<br>1: Corresponding P2.n Output is push-pull. |

## SFR Definition 20.15. P2SKIP: Port 2 Skip

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-------------|---|---|---|---|---|---|---|

| Name  | P2SKIP[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W         |   |   |   |   |   |   |   |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

SFR Address = 0xD6; SFR Page = All Pages

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P2SKIP[3:0] | Port 2 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 2 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P2.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P2.n pin is skipped by the Crossbar.</li> </ul> |

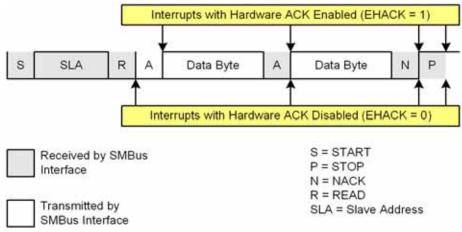

#### 21.5.4. Read Sequence (Slave)

During a read sequence, an SMBus master reads data from a slave device. The slave in this transfer will be a receiver during the address byte, and a transmitter during all data bytes. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. If hardware ACK generation is disabled, upon entering Slave Receiver Mode, an interrupt is generated and the ACKRQ bit is set. The software must respond to the received slave address with an ACK, or ignore the received slave address with a NACK. If hardware ACK generation is enabled, the hardware will apply the ACK for a slave address which matches the criteria set up by SMB0ADR and SMB0ADM. The interrupt will occur after the ACK cycle.

If the received slave address is ignored (by software or hardware), slave interrupts will be inhibited until the next START is detected. If the received slave address is acknowledged, zero or more data bytes are transmitted. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters slave transmitter mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (an error condition may be generated if SMB0DAT is written following a received NACK while in slave transmitter mode). The interface exits slave transmitter mode after receiving a STOP. The interface will switch to slave receiver mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 21.8 shows a typical slave read sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that all of the "data byte transferred" interrupts occur **after** the ACK cycle in this mode, regardless of whether hardware ACK generation is enabled.

## 21.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. The appropriate actions to take in response to an SMBus event depend on whether hardware slave address recognition and ACK generation is enabled or disabled. Table 21.5 describes the typical actions when hardware slave address recognition and ACK generation is disabled. Table 21.6 describes the typical actions when hardware slave address recognition and ACK generation is enabled. In the tables, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. The shown response options are only the typical responses; application-specific procedures are allowed as long as they conform to the SMBus specification. Highlighted responses are allowed by hardware but do not conform to the SMBus specification.

## SFR Definition 22.1. SCON0: Serial Port 0 Control

|       |              |                                                                                                                                                                                              | -           |               |          |      |     |     |

|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|----------|------|-----|-----|

| Bit   | 7            | 6                                                                                                                                                                                            | 5           | 4             | 3        | 2    | 1   | 0   |

| Nam   | e S0MOD      | E -                                                                                                                                                                                          | MCE0        | REN0          | TB80     | RB80 | TI0 | RI0 |

| Туре  | e R/W        | R                                                                                                                                                                                            | R/W         | R/W           | R/W      | R/W  | R/W | R/W |

| Rese  | et 0         | 1                                                                                                                                                                                            | 0           | 0             | 0        | 0    | 0   | 0   |

| SFR A | Address = 0> | (98; SFR Page                                                                                                                                                                                | = All Pages | ; Bit-Address | sable    |      |     |     |

| Bit   | Name         |                                                                                                                                                                                              |             |               | Function |      |     |     |

| 7     | SOMODE       | <ul> <li>Serial Port 0 Operation Mode.</li> <li>Selects the UART0 Operation Mode.</li> <li>0: 8-bit UART with Variable Baud Rate.</li> <li>1: 9-bit UART with Variable Baud Rate.</li> </ul> |             |               |          |      |     |     |

|   |        | 1: 9-bit UART with Variable Baud Rate.                                                                                                                                                                                                                                                                                                           |

|---|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | Unused | Read = 1b, Write = don't care.                                                                                                                                                                                                                                                                                                                   |

| 5 | MCE0   | Multiprocessor Communication Enable.                                                                                                                                                                                                                                                                                                             |

|   |        | The function of this bit is dependent on the Serial Port 0 Operation Mode:                                                                                                                                                                                                                                                                       |

|   |        | Mode 0: Checks for valid stop bit.                                                                                                                                                                                                                                                                                                               |

|   |        | 0: Logic level of stop bit is ignored.                                                                                                                                                                                                                                                                                                           |

|   |        | 1: RIO will only be activated if stop bit is logic level 1.                                                                                                                                                                                                                                                                                      |

|   |        | Mode 1: Multiprocessor Communications Enable.                                                                                                                                                                                                                                                                                                    |

|   |        | 0: Logic level of ninth bit is ignored.                                                                                                                                                                                                                                                                                                          |

|   | DENIO  | 1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1.                                                                                                                                                                                                                                                                  |

| 4 | REN0   | Receive Enable.                                                                                                                                                                                                                                                                                                                                  |

|   |        | 0: UART0 reception disabled.                                                                                                                                                                                                                                                                                                                     |

|   | TDaa   | 1: UART0 reception enabled.                                                                                                                                                                                                                                                                                                                      |

| 3 | TB80   | Ninth Transmission Bit.                                                                                                                                                                                                                                                                                                                          |

|   |        | The logic level of this bit will be sent as the ninth transmission bit in 9-bit UART Mode (Mode 1). Unused in 8-bit mode (Mode 0).                                                                                                                                                                                                               |

| 2 | RB80   | Ninth Receive Bit.                                                                                                                                                                                                                                                                                                                               |

|   |        | RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9th data bit in Mode 1.                                                                                                                                                                                                                                    |

| 1 | TI0    | Transmit Interrupt Flag.                                                                                                                                                                                                                                                                                                                         |

|   |        | Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bit<br>in 8-bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When<br>the UART0 interrupt is enabled, setting this bit causes the CPU to vector to the UART0<br>interrupt service routine. This bit must be cleared manually by software. |

| 0 | RI0    | Receive Interrupt Flag.                                                                                                                                                                                                                                                                                                                          |

|   |        | Set to 1 by hardware when a byte of data has been received by UART0 (set at the STOP bit sampling time). When the UART0 interrupt is enabled, setting this bit to 1 causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software.                                                              |

| Table 22.1. Timer Settings for Standard Baud Rates Using Internal Oscillator |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

|    | Target<br>Baud<br>Rate (bps)                                          | Actual<br>Baud<br>Rate (bps) | Baud<br>Rate<br>Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select* | T1M | Timer 1<br>Reload<br>Value (hex) |  |  |  |

|----|-----------------------------------------------------------------------|------------------------------|-----------------------|--------------------------------|-----------------------|------------------------------------|-----|----------------------------------|--|--|--|

| No | Note: SCA1-SCA0 and T1M define the Timer Clock Source. X = Don't care |                              |                       |                                |                       |                                    |     |                                  |  |  |  |

1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

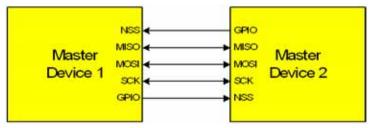

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 24.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 24.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 24.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

Figure 24.2. Multiple-Master Mode Connection Diagram

Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

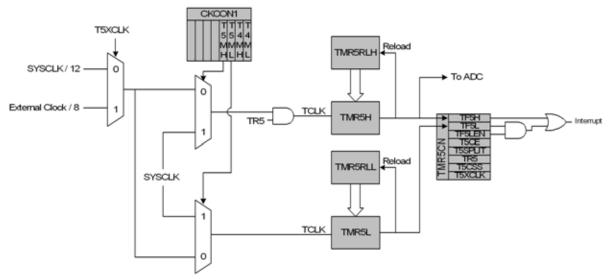

#### 25.5.2. 8-bit Timers with Auto-Reload

When T5SPLIT is 1 and T5CE = 0, Timer 5 operates as two 8-bit timers (TMR5H and TMR5L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.15. TMR5RLL holds the reload value for TMR5L; TMR5RLH holds the reload value for TMR5H. The TR5 bit in TMR5CN handles the run control for TMR5H. TMR5L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 5 Clock Select bits (T5MH and T5ML in CKCON1) select either SYSCLK or the clock defined by the Timer 5 External Clock Select bit (T5XCLK in TMR5CN), as follows:

| T5MH | T5XCLK | TMR5H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK/12          |

| 0    | 1      | External Clock/8   |

| 1    | Х      | SYSCLK             |

| T5ML | T5XCLK | TMR5L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK/12          |

| 0    | 1      | External Clock/8   |

| 1    | X      | SYSCLK             |

The TF5H bit is set when TMR5H overflows from 0xFF to 0x00; the TF5L bit is set when TMR5L overflows from 0xFF to 0x00. When Timer 5 interrupts are enabled, an interrupt is generated each time TMR5H overflows. If Timer 5 interrupts are enabled and TF5LEN (TMR5CN.5) is set, an interrupt is generated each time either TMR5L or TMR5H overflows. When TF5LEN is enabled, software must check the TF5H and TF5L flags to determine the source of the Timer 5 interrupt. The TF5H and TF5L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.15. Timer 5 8-Bit Mode Block Diagram

## SFR Definition 25.25. TMR5RLL: Timer 5 Reload Register Low Byte

| Bit     | 7                                | 6 | 5 | 4 | 3 | 2 | 1   | 0 |  |  |  |

|---------|----------------------------------|---|---|---|---|---|-----|---|--|--|--|

| Name    | TMR5RLL[7:0]                     |   |   |   |   |   |     |   |  |  |  |

| Туре    | R/W                              |   |   |   |   |   |     |   |  |  |  |

| Reset   | 0                                | 0 | 0 | 0 | 0 | 0 | 0 0 |   |  |  |  |

| SFR Add | SFR Address = 0xCA; SFR Page = F |   |   |   |   |   |     |   |  |  |  |

| Bit | Name         | Function                                                    |  |  |  |

|-----|--------------|-------------------------------------------------------------|--|--|--|

| 7:0 | TMR5RLL[7:0] | ner 5 Reload Register Low Byte.                             |  |  |  |

|     |              | TMR5RLL holds the low byte of the reload value for Timer 5. |  |  |  |

### SFR Definition 25.26. TMR5RLH: Timer 5 Reload Register High Byte

| Bit   | 7              | 6                                                                                                                     | 5     | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------|-------|---|---|---|---|---|--|--|--|

| Nam   | е              | TMR5RLH[7:0]                                                                                                          |       |   |   |   |   |   |  |  |  |

| Тур   | e              | R/W                                                                                                                   |       |   |   |   |   |   |  |  |  |

| Rese  | et 0           | 0                                                                                                                     | 0     | 0 | 0 | 0 | 0 | 0 |  |  |  |

| SFR A | Address = 0xCE | 3; SFR Page                                                                                                           | e = F |   |   |   |   |   |  |  |  |

| Bit   | Name           |                                                                                                                       |       |   |   |   |   |   |  |  |  |

| 7:0   | TMR5RLH[7:0    | MR5RLH[7:0] <b>Timer 5 Reload Register High Byte.</b><br>TMR5RLH holds the high byte of the reload value for Timer 5. |       |   |   |   |   |   |  |  |  |

## SFR Definition 25.27. TMR5L: Timer 5 Low Byte

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------------|---|---|---|---|---|---|---|--|--|

| Name  | TMR5L[7:0] |   |   |   |   |   |   |   |  |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

#### SFR Address = 0xCC; SFR Page = F

| Bit | Name       | Function                                                                                                                                      |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR5L[7:0] | Timer 5 Low Byte.                                                                                                                             |

|     |            | In 16-bit mode, the TMR5L register contains the low byte of the 16-bit Timer 5. In 8-bit mode, TMR5L contains the 8-bit low byte timer value. |

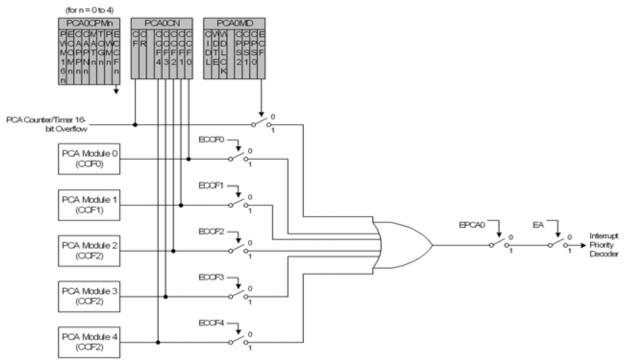

### 26.2. PCA0 Interrupt Sources

Figure 26.3 shows a diagram of the PCA interrupt tree. There are six independent event flags that can be used to generate a PCA0 interrupt. They are: the main PCA counter overflow flag (CF), which is set upon a 16-bit overflow of the PCA0 counter and the individual flags for each PCA channel (CCF0, CCF1, CCF2, CCF3, and CCF4), which are set according to the operation mode of that module. These event flags are always set when the trigger condition occurs. Each of these flags can be individually selected to generate a PCA0 interrupt, using the corresponding interrupt enable flag (ECF for CF, and ECCFn for each CCFn). PCA0 interrupts must be globally enabled before any individual interrupt sources are recognized by the processor. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1.

Figure 26.3. PCA Interrupt Block Diagram

### 26.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high-speed output, frequency output, 8-bit pulse width modulator, or 16-bit pulse width modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 26.2 summarizes the bit settings in the PCA0CPMn register used to select the PCA capture/compare module's operating mode. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

| Operational Mode                                                              |            |   |   |   | PCA0CPMn |   |   |   |   |  |  |

|-------------------------------------------------------------------------------|------------|---|---|---|----------|---|---|---|---|--|--|

|                                                                               | Bit Number | 7 | 6 | 5 | 4        | 3 | 2 | 1 | 0 |  |  |

| Capture triggered by positive edge on CEXn                                    |            | Х | Х | 1 | 0        | 0 | 0 | 0 | А |  |  |

| Capture triggered by negative edge on CEXn                                    |            | Х | Х | 0 | 1        | 0 | 0 | 0 | Α |  |  |

| Capture triggered by any transition on CEXn                                   |            | Х | Х | 1 | 1        | 0 | 0 | 0 | А |  |  |

| Software Timer                                                                |            | Х | В | 0 | 0        | 1 | 0 | 0 | A |  |  |

| High Speed Output                                                             |            | Х | В | 0 | 0        | 1 | 1 | 0 | Α |  |  |

| Frequency Output                                                              |            | Х | В | 0 | 0        | 0 | 1 | 1 | A |  |  |

| 8-Bit Pulse Width Modulator                                                   |            | 0 | В | 0 | 0        | С | 0 | 1 | Α |  |  |

| 16-Bit Pulse Width Modulator                                                  |            | 1 | В | 0 | 0        | С | 0 | 1 | Α |  |  |

| Notes:<br>1. X = Don't Care (no functional difference for individual module i | f 1 or 0)  |   |   |   |          |   |   |   |   |  |  |

#### Table 26.2. PCA0CPM Bit Settings for PCA Capture/Compare Modules

are (no functional difference for individual module if 1 or 0).

2. A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

3. B = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

4. C = When set, a match event will cause the CCFn flag for the associated channel to be set.

The 8-bit offset held in PCA0CPH4 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 26.4, where PCA0L is the value of the PCA0L register at the time of the update.

Offset =  $(256 \times PCA0CPL4) + (256 - PCA0L)$

#### Equation 26.4. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH4 and PCA0H. Software may force a WDT reset by writing a 1 to the CCF4 flag (PCA0CN.4) while the WDT is enabled.

#### 26.4.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- 1. Disable the WDT by writing a 0 to the WDTE bit.

- 2. Select the desired PCA clock source (with the CPS2–CPS0 bits).

- 3. Load PCA0CPL4 with the desired WDT update offset value.

- 4. Configure the PCA Idle mode (set CIDL if the WDT should be suspended while the CPU is in Idle mode).

- 5. Enable the WDT by setting the WDTE bit to 1.

- 6. Reset the WDT timer by writing to PCA0CPH4.

The PCA clock source and Idle mode select cannot be changed while the WDT is enabled. The watchdog timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL4 defaults to 0x00. Using Equation 26.4, this results in a WDT timeout interval of 256 PCA clock cycles, or 3072 system clock cycles. Table 26.3 lists some example timeout intervals for typical system clocks.