# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 48 MIPS                                                           |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 40                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                    |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                             |

| RAM Size                   | 2.25K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                      |

| Data Converters            | A/D 32x10b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 48-TQFP                                                           |

| Supplier Device Package    | 48-TQFP (7x7)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f38a-b-gqr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1. System Overview

C8051F388/9/A/B devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 48 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Supply Voltage Regulator

- True 10-bit 500 ksps differential / single-ended ADC with analog multiplexer

- On-chip Voltage Reference and Temperature Sensor

- On-chip Voltage Comparators (2)

- Precision internal calibrated 48 MHz internal oscillator

- Internal low-frequency oscillator for additional power savings

- Up to 64 kB of on-chip Flash memory

- Up to 4352 Bytes of on-chip RAM (256 + 4 kB)

- External Memory Interface (EMIF) available on 48-pin versions.

- 2 I<sup>2</sup>C/SMBus, 2 UARTs, and Enhanced SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer function

- On-chip Power-On Reset, V<sub>DD</sub> Monitor, and Missing Clock Detector

- Up to 40 Port I/O (5 V tolerant)

With on-chip Power-On Reset,  $V_{DD}$  monitor, Voltage Regulator, Watchdog Timer, and clock oscillator, C8051F388/9/A/B devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 2.7–5.25 V operation over the industrial temperature range (<u>-40</u> to +85 °C). For voltages above 3.6 V, the on-chip Voltage Regulator must be used. The Port I/O and RST pins are tolerant of input signals up to 5 V. C8051F388/9/A/B devices are available in 48-pin TQFP, 32-pin LQFP, or 32-pin QFN packages. See Table 1.1, "Product Selection Guide," on page 16 for feature and package choices.

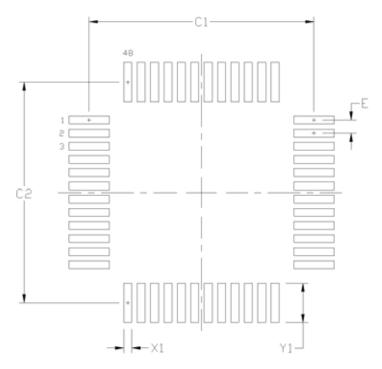

Figure 3.3. TQFP-48 Recommended PCB Land Pattern

| Table 3                                                                       | 3.3. TQFP-48                                                                                                                                                                               | PCB Land Pattern          | Dimensions                |  |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|--|--|--|--|

| Dimens                                                                        | ion                                                                                                                                                                                        | Min                       | Мах                       |  |  |  |  |

| C1                                                                            |                                                                                                                                                                                            | 8.30                      | 8.40                      |  |  |  |  |

| C2                                                                            |                                                                                                                                                                                            | 8.30                      | 8.40                      |  |  |  |  |

| E                                                                             |                                                                                                                                                                                            | 0.50                      | BSC                       |  |  |  |  |

| X1                                                                            |                                                                                                                                                                                            | 0.20                      | 0.30                      |  |  |  |  |

| Y1                                                                            |                                                                                                                                                                                            | 1.40                      | 1.50                      |  |  |  |  |

| Notes:                                                                        |                                                                                                                                                                                            |                           |                           |  |  |  |  |

| General:                                                                      |                                                                                                                                                                                            |                           |                           |  |  |  |  |

| 1. All dimensio                                                               | ons shown are in i                                                                                                                                                                         | millimeters (mm) unless   | otherwise noted.          |  |  |  |  |

| <ol><li>This Land P</li></ol>                                                 | attern Design is l                                                                                                                                                                         | based on the IPC-7351 g   | juidelines.               |  |  |  |  |

| Solder Mask Desig                                                             | gn:                                                                                                                                                                                        |                           |                           |  |  |  |  |

| 3. All metal page                                                             | ds are to be non-                                                                                                                                                                          | solder mask defined (NS   | MD). Clearance between    |  |  |  |  |

| the solder m                                                                  | hask and the meta                                                                                                                                                                          | al pad is to be 60 µm min | imum, all the way around  |  |  |  |  |

| the pad.                                                                      |                                                                                                                                                                                            |                           |                           |  |  |  |  |

| Stencil Design:                                                               | Stencil Design:                                                                                                                                                                            |                           |                           |  |  |  |  |

| 4. A stainless                                                                | steel, laser-cut ar                                                                                                                                                                        | nd electro-polished stend | il with trapezoidal walls |  |  |  |  |

| should be u                                                                   | should be used to assure good solder paste release.                                                                                                                                        |                           |                           |  |  |  |  |

| 5. The stencil t                                                              | 5. The stencil thickness should be 0.125 mm (5 mils).                                                                                                                                      |                           |                           |  |  |  |  |

| 6. The ratio of stencil aperture to land pad size should be 1:1 for all pads. |                                                                                                                                                                                            |                           |                           |  |  |  |  |

| Card Assembly:                                                                | ·                                                                                                                                                                                          | ·                         |                           |  |  |  |  |

| 7. A No-Clean,                                                                | 7. A No-Clean, Type-3 solder paste is recommended.                                                                                                                                         |                           |                           |  |  |  |  |

|                                                                               | <ol> <li>A No-Olean, Type-5 solider paster is recommended.</li> <li>The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.</li> </ol> |                           |                           |  |  |  |  |

Table 3.3. TQFP-48 PCB Land Pattern Dimensions

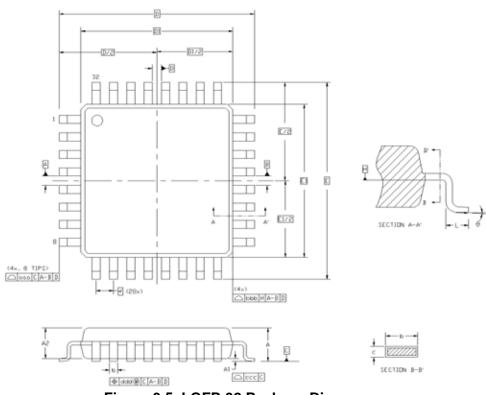

Figure 3.5. LQFP-32 Package Diagram

| Dimension | Min         | Nom            | Мах  |  | Dimension | Min  | Nom      | Мах  |

|-----------|-------------|----------------|------|--|-----------|------|----------|------|

| A         | _           | —              | 1.60 |  | E         |      | 9.00 BSC |      |

| A1        | 0.05        | —              | 0.15 |  | E1        |      | 7.00 BSC |      |

| A2        | 1.35        | 1.40           | 1.45 |  | L         | 0.45 | 0.60     | 0.75 |

| b         | 0.30        | 0.30 0.37 0.45 |      |  | aaa       | 0.20 |          |      |

| С         | 0.09 — 0.20 |                | 0.20 |  | bbb       | 0.20 |          |      |

| D         | 9.00 BSC    |                |      |  | CCC       |      | 0.10     |      |

| D1        | 7.00 BSC    |                |      |  | ddd       |      | 0.20     |      |

| е         |             | 0.80 BSC       |      |  | q         | 0°   | 3.5°     | 7°   |

#### Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS-026, variation BBA.

- 4. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

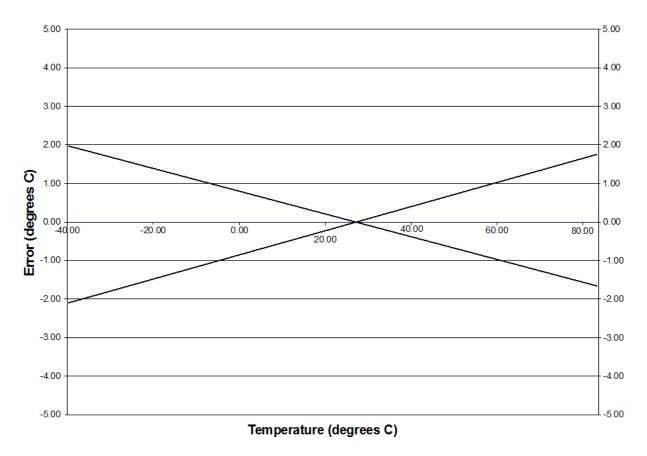

Figure 6.3. Temperature Sensor Error with 1-Point Calibration

### Table 11.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic             | Description                                | Bytes | Clock<br>Cycles |

|----------------------|--------------------------------------------|-------|-----------------|

| XRL direct, #data    | Exclusive-OR immediate to direct byte      | 3     | 3               |

| CLR A                | Clear A                                    | 1     | 1               |

| CPLA                 | Complement A                               | 1     | 1               |

| RLA                  | Rotate A left                              | 1     | 1               |

| RLC A                | Rotate A left through Carry                | 1     | 1               |

| RR A                 | Rotate A right                             | 1     | 1               |

| RRC A                | Rotate A right through Carry               | 1     | 1               |

| SWAP A               | Swap nibbles of A                          | 1     | 1               |

| Data Transfer        |                                            |       |                 |

| MOV A, Rn            | Move Register to A                         | 1     | 1               |

| MOV A, direct        | Move direct byte to A                      | 2     | 2               |

| MOV A, @Ri           | Move indirect RAM to A                     | 1     | 2               |

| MOV A, #data         | Move immediate to A                        | 2     | 2               |

| MOV Rn, A            | Move A to Register                         | 1     | 1               |

| MOV Rn, direct       | Move direct byte to Register               | 2     | 2               |

| MOV Rn, #data        | Move immediate to Register                 | 2     | 2               |

| MOV direct, A        | Move A to direct byte                      | 2     | 2               |

| MOV direct, Rn       | Move Register to direct byte               | 2     | 2               |

| MOV direct, direct   | Move direct byte to direct byte            | 3     | 3               |

| MOV direct, @Ri      | Move indirect RAM to direct byte           | 2     | 2               |

| MOV direct, #data    | Move immediate to direct byte              | 3     | 3               |

| MOV @Ri, A           | Move A to indirect RAM                     | 1     | 2               |

| MOV @Ri, direct      | Move direct byte to indirect RAM           | 2     | 2               |

| MOV @Ri, #data       | Move immediate to indirect RAM             | 2     | 2               |

| MOV DPTR, #data16    | Load DPTR with 16-bit constant             | 3     | 3               |

| MOVC A, @A+DPTR      | Move code byte relative DPTR to A          | 1     | 3               |

| MOVC A, @A+PC        | Move code byte relative PC to A            | 1     | 3               |

| MOVX A, @Ri          | Move external data (8-bit address) to A    | 1     | 3               |

| MOVX @Ri, A          | Move A to external data (8-bit address)    | 1     | 3               |

| MOVX A, @DPTR        | Move external data (16-bit address) to A   | 1     | 3               |

| MOVX @DPTR, A        | Move A to external data (16-bit address)   | 1     | 3               |

| PUSH direct          | Push direct byte onto stack                | 2     | 2               |

| POP direct           | Pop direct byte from stack                 | 2     | 2               |

| XCH A, Rn            | Exchange Register with A                   | 1     | 1               |

| XCH A, direct        | Exchange direct byte with A                | 2     | 2               |

| XCH A, @Ri           | Exchange indirect RAM with A               | 1     | 2               |

| XCHD A, @Ri          | Exchange low nibble of indirect RAM with A | 1     | 2               |

| Boolean Manipulation |                                            | I     | <u>I</u>        |

| CLR C                | Clear Carry                                | 1     | 1               |

| CLR bit              | Clear direct bit                           | 2     | 2               |

| SETB C               | Set Carry                                  | 1     | 1               |

| SETB bit             | Set direct bit                             | 2     | 2               |

| CPL C                | Complement Carry                           | 1     | 1               |

| CPL bit              | Complement direct bit                      | 2     | 2               |

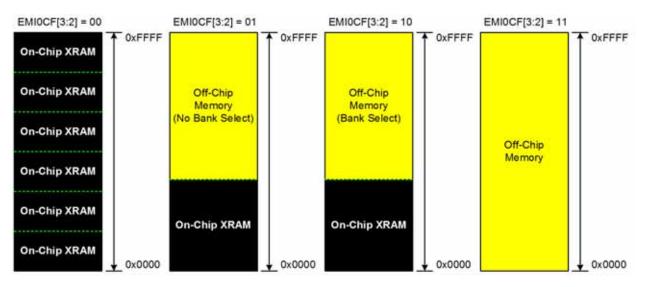

#### 14.5. Memory Mode Selection

The external data memory space can be configured in one of four modes, shown in Figure 14.3, based on the EMIF Mode bits in the EMIOCF register (SFR Definition 14.4). These modes are summarized below. More information about the different modes can be found in Section "14.6. Timing" on page 96.

Figure 14.3. EMIF Operating Modes

#### 14.5.1. Internal XRAM Only

When EMI0CF.[3:2] are set to 00, all MOVX instructions will target the internal XRAM space on the device. Memory accesses to addresses beyond the populated space will wrap on 2k or 4k boundaries (depending on the RAM available on the device). As an example, the addresses 0x1000 and 0x2000 both evaluate to address 0x0000 in on-chip XRAM space.

- 8-bit MOVX operations use the contents of EMI0CN to determine the high-byte of the effective address and R0 or R1 to determine the low-byte of the effective address.

- 16-bit MOVX operations use the contents of the 16-bit DPTR to determine the effective address.

#### 14.5.2. Split Mode without Bank Select

When EMI0CF.[3:2] are set to 01, the XRAM memory map is split into two areas, on-chip space and off-chip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is on-chip or off-chip. However, in the "No Bank Select" mode, an 8-bit MOVX operation will not drive the upper 8-bits A[15:8] of the Address Bus during an off-chip access. This allows the user to manipulate the upper address bits at will by setting the Port state directly via the port latches. This behavior is in contrast with "Split Mode with Bank Select" described below. The lower 8-bits of the Address Bus A[7:0] are driven, determined by R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and unlike 8-bit MOVX operations, the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

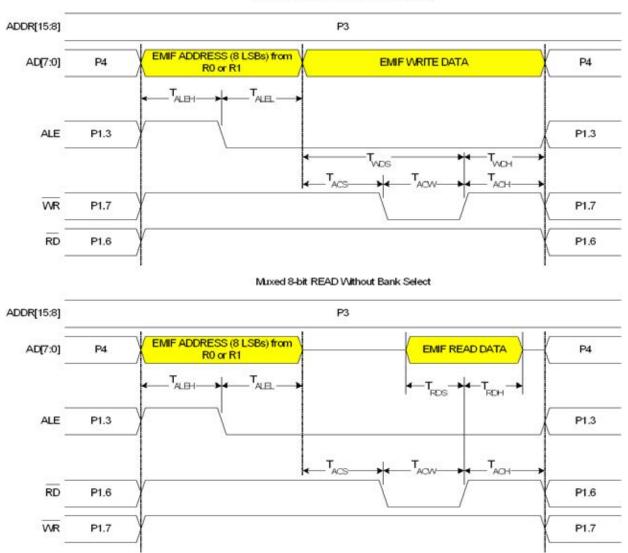

#### 14.6.2.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 001 or 011

Muxed 8-bit WRITE Without Bank Select

### SFR Definition 16.2. IP: Interrupt Priority

| Bit   | 7                                                                                                                                | 6                                                                                                           | 5                                                | 4               | 3            | 2             | 1   | 0   |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|--------------|---------------|-----|-----|--|

| Nam   | е                                                                                                                                | PSPI0                                                                                                       | PT2                                              | PS0             | PT1          | PX1           | PT0 | PX0 |  |

| Тур   | e R                                                                                                                              | R/W                                                                                                         | R/W                                              | R/W             | R/W          | R/W           | R/W | R/W |  |

| Rese  | et 1                                                                                                                             | t 1 0 0 0 0 0                                                                                               |                                                  |                 |              |               |     | 0   |  |

| SFR A | Address = 0                                                                                                                      | xB8; SFR Page                                                                                               | = All Pages                                      | ; Bit-Addres    | sable        |               |     | •   |  |

| Bit   | Name                                                                                                                             |                                                                                                             |                                                  |                 | Function     |               |     |     |  |

| 7     | Unused                                                                                                                           | Read = 1b, W                                                                                                | rite = Don't (                                   | Care.           |              |               |     |     |  |

| 6     | PSPI0                                                                                                                            | Serial Periph                                                                                               | eral Interfac                                    | ce (SPI0) Int   | terrupt Prio | rity Control. |     |     |  |

|       |                                                                                                                                  | This bit sets th                                                                                            |                                                  | . ,             | -            | •             |     |     |  |

|       |                                                                                                                                  | 0: SPI0 interru                                                                                             | pt set to low                                    | v priority leve | el.          |               |     |     |  |

|       |                                                                                                                                  | 1: SPI0 interru                                                                                             | pt set to hig                                    | h priority lev  | vel.         |               |     |     |  |

| 5     | PT2                                                                                                                              | Timer 2 Inter                                                                                               | upt Priority                                     | Control.        |              |               |     |     |  |

|       |                                                                                                                                  | This bit sets the priority of the Timer 2 interrupt.<br>0: Timer 2 interrupt set to low priority level.     |                                                  |                 |              |               |     |     |  |

|       |                                                                                                                                  |                                                                                                             |                                                  |                 |              |               |     |     |  |

|       |                                                                                                                                  | 1: Timer 2 inte                                                                                             | 1: Timer 2 interrupt set to high priority level. |                 |              |               |     |     |  |

| 4     | PS0                                                                                                                              | UART0 Interr                                                                                                | UART0 Interrupt Priority Control.                |                 |              |               |     |     |  |

|       |                                                                                                                                  | This bit sets the priority of the UART0 interrupt.                                                          |                                                  |                 |              |               |     |     |  |

|       |                                                                                                                                  | 0: UART0 interrupt set to low priority level.                                                               |                                                  |                 |              |               |     |     |  |

|       |                                                                                                                                  | 1: UART0 interrupt set to high priority level.                                                              |                                                  |                 |              |               |     |     |  |

| 3     | PT1                                                                                                                              | Timer 1 Inter                                                                                               | • •                                              |                 |              |               |     |     |  |

|       |                                                                                                                                  | This bit sets the priority of the Timer 1 interrupt.                                                        |                                                  |                 |              |               |     |     |  |

|       | 0: Timer 1 interrupt set to low priority level.                                                                                  |                                                                                                             |                                                  |                 |              |               |     |     |  |

|       |                                                                                                                                  | 1: Timer 1 interrupt set to high priority level.                                                            |                                                  |                 |              |               |     |     |  |

| 2     | PX1                                                                                                                              | External Interrupt 1 Priority Control.<br>This bit sets the priority of the External Interrupt 1 interrupt. |                                                  |                 |              |               |     |     |  |

|       |                                                                                                                                  |                                                                                                             |                                                  |                 |              | interrupt.    |     |     |  |

|       | <ul><li>0: External Interrupt 1 set to low priority level.</li><li>1: External Interrupt 1 set to high priority level.</li></ul> |                                                                                                             |                                                  |                 |              |               |     |     |  |

| 4     | DTO                                                                                                                              |                                                                                                             | •                                                | • •             |              |               |     |     |  |

| 1     | PT0                                                                                                                              | Timer 0 Intern                                                                                              | • •                                              |                 | intorrunt    |               |     |     |  |

|       |                                                                                                                                  | 0: Timer 0 inte                                                                                             |                                                  |                 | •            |               |     |     |  |

|       |                                                                                                                                  |                                                                                                             | nupi sei iu i                                    |                 |              |               |     |     |  |

#### 18.2. Non-Volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

#### 18.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to 1 before software can modify the Flash memory; both PSWE and PSEE must be set to 1 before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

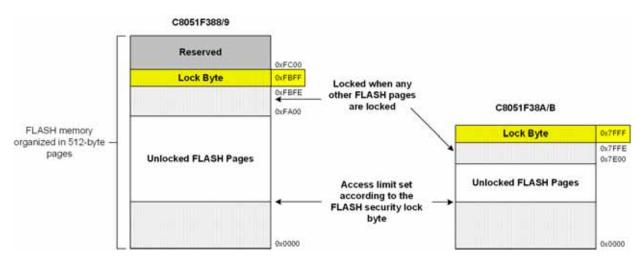

A Security Lock Byte located at the last byte of Flash user space offers protection of the Flash program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. The Flash security mechanism allows the user to lock n 512-byte Flash pages, starting at page 0 (addresses 0x0000 to 0x01FF), where n is the 1s complement number represented by the Security Lock Byte. Note that the page containing the Flash Security Lock Byte is also locked when any other Flash pages are locked. See example below.

| Security Lock Byte: | 11111101b                                                                                  |

|---------------------|--------------------------------------------------------------------------------------------|

| 1s Complement:      | 0000010b                                                                                   |

| Flash pages locked: | 3 (2 + Flash Lock Byte Page)                                                               |

| Addresses locked:   | First two pages of Flash: 0x0000 to 0x03FF                                                 |

|                     | Flash Lock Byte Page: (0xFA00 to 0xFBFF for 64k devices; 0x7E00 to 0x7FFF for 32k devices) |

Figure 18.1. Flash Program Memory Map and Security Byte

The level of FLASH security depends on the FLASH access method. The three FLASH access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages.

### SFR Definition 19.3. OSCICN: Internal H-F Oscillator Control

| Bit   | 7      | 6     | 5       | 4 | 3 | 2 | 1    | 0              |

|-------|--------|-------|---------|---|---|---|------|----------------|

| Name  | IOSCEN | IFRDY | SUSPEND |   |   |   | IFCN | <b>I</b> [1:0] |

| Туре  | R/W    | R     | R/W     | R | R | R | R/   | W              |

| Reset | 1      | 1     | 0       | 0 | 0 | 0 | 0    | 0              |

#### SFR Address = 0xB2; SFR Page = All Pages

| Bit | Name      | Function                                                                                                                                                                            |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IOSCEN    | Internal H-F Oscillator Enable Bit.                                                                                                                                                 |

|     |           | 0: Internal H-F Oscillator Disabled.                                                                                                                                                |

|     |           | 1: Internal H-F Oscillator Enabled.                                                                                                                                                 |

| 6   | IFRDY     | Internal H-F Oscillator Frequency Ready Flag.                                                                                                                                       |

|     |           | 0: Internal H-F Oscillator is not running at programmed frequency.                                                                                                                  |

|     |           | 1: Internal H-F Oscillator is running at programmed frequency.                                                                                                                      |

| 5   | SUSPEND   | Internal Oscillator Suspend Enable Bit.                                                                                                                                             |

|     |           | Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The inter-<br>nal oscillator resumes operation when one of the SUSPEND mode awakening<br>events occurs. |

| 4:2 | Unused    | Read = 000b; Write = don't care                                                                                                                                                     |

| 1:0 | IFCN[1:0] | Internal H-F Oscillator Frequency Divider Control Bits.                                                                                                                             |

|     |           | The Internal H-F Oscillator is divided by the IFCN bit setting after a divide-by-4 stage.                                                                                           |

|     |           | 00: SYSCLK can be derived from Internal H-F Oscillator divided by 8 (1.5 MHz).                                                                                                      |

|     |           | 01: SYSCLK can be derived from Internal H-F Oscillator divided by 4 (3 MHz).<br>10: SYSCLK can be derived from Internal H-F Oscillator divided by 2 (6 MHz).                        |

|     |           | 11: SYSCLK can be derived from Internal H-F Oscillator divided by 2 (0 MHz).                                                                                                        |

### SFR Definition 20.2. XBR1: Port I/O Crossbar Register 1

| Bit   | 7       | 6     | 5   | 4   | 3    | 2   | 1          | 0   |

|-------|---------|-------|-----|-----|------|-----|------------|-----|

| Name  | WEAKPUD | XBARE | T1E | T0E | ECIE | F   | PCA0ME[2:0 | ]   |

| Туре  | R/W     | R/W   | R/W | R/W | R/W  | R/W | R/W        | R/W |

| Reset | 0       | 0     | 0   | 0   | 0    | 0   | 0          | 0   |

### SFR Address = 0xE2; SFR Page = All Pages

| Bit | Name        | Function                                                                      |

|-----|-------------|-------------------------------------------------------------------------------|

| 7   | WEAKPUD     | Port I/O Weak Pullup Disable.                                                 |

|     |             | 0: Weak Pullups enabled (except for Ports whose I/O are configured for analog |

|     |             | mode).                                                                        |

|     |             | 1: Weak Pullups disabled.                                                     |

| 6   | XBARE       | Crossbar Enable.                                                              |

|     |             | 0: Crossbar disabled.                                                         |

|     |             | 1: Crossbar enabled.                                                          |

| 5   | T1E         | T1 Enable.                                                                    |

|     |             | 0: T1 unavailable at Port pin.                                                |

|     |             | 1: T1 routed to Port pin.                                                     |

| 4   | T0E         | T0 Enable.                                                                    |

|     |             | 0: T0 unavailable at Port pin.                                                |

|     |             | 1: T0 routed to Port pin.                                                     |

| 3   | ECIE        | PCA0 External Counter Input Enable.                                           |

|     |             | 0: ECI unavailable at Port pin.                                               |

|     |             | 1: ECI routed to Port pin.                                                    |

| 2:0 | PCA0ME[2:0] | PCA Module I/O Enable Bits.                                                   |

|     |             | 000: All PCA I/O unavailable at Port pins.                                    |

|     |             | 001: CEX0 routed to Port pin.                                                 |

|     |             | 010: CEX0, CEX1 routed to Port pins.                                          |

|     |             | 011: CEX0, CEX1, CEX2 routed to Port pins.                                    |

|     |             | 100: CEX0, CEX1, CEX2, CEX3 routed to Port pins.                              |

|     |             | 101: CEX0, CEX1, CEX2, CEX3 routed to Port pins.                              |

|     |             | 11x: Reserved.                                                                |

| Table 22.1. Timer Settings for Standard Baud Rates Using Internal Oscillator |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

|    | Target<br>Baud<br>Rate (bps)                                                 | Actual<br>Baud<br>Rate (bps) | Baud<br>Rate<br>Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select* | T1M | Timer 1<br>Reload<br>Value (hex) |  |

|----|------------------------------------------------------------------------------|------------------------------|-----------------------|--------------------------------|-----------------------|------------------------------------|-----|----------------------------------|--|

| No | <b>Note:</b> SCA1-SCA0 and T1M define the Timer Clock Source. X = Don't care |                              |                       |                                |                       |                                    |     |                                  |  |

### SFR Definition 23.4. SBCON1: UART1 Baud Rate Generator Control

| Bit   | 7   | 6      | 5   | 4   | 3   | 2   | 1    | 0      |

|-------|-----|--------|-----|-----|-----|-----|------|--------|

| Name  |     | SB1RUN |     |     |     |     | SB1P | S[1:0] |

| Туре  | R/W | R/W    | R/W | R/W | R/W | R/W | R/W  |        |

| Reset | 0   | 0      | 0   | 0   | 0   | 0   | 0    | 0      |

SFR Address = 0xAC; SFR Page = All Pages

| Bit | Name       | Function                                                     |  |  |  |

|-----|------------|--------------------------------------------------------------|--|--|--|

| 7   | Reserved   | Read = 0b. Must Write 0b.                                    |  |  |  |

| 6   | SB1RUN     | Baud Rate Generator Enable.                                  |  |  |  |

|     |            | ): Baud Rate Generator is disabled. UART1 will not function. |  |  |  |

|     |            | 1: Baud Rate Generator is enabled.                           |  |  |  |

| 5:2 | Reserved   | Read = 0000b. Must Write 0000b.                              |  |  |  |

| 1:0 | SB1PS[1:0] | Baud Rate Prescaler Select.                                  |  |  |  |

|     |            | 00: Prescaler = 12                                           |  |  |  |

|     |            | 01: Prescaler = 4                                            |  |  |  |

|     |            | 10: Prescaler = 48                                           |  |  |  |

|     |            | 11: Prescaler = 1                                            |  |  |  |

### SFR Definition 23.5. SBRLH1: UART1 Baud Rate Generator High Byte

| Bit                                      | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------|-----------------|---|---|---|---|---|---|---|

| Name                                     | SBRLH1[7:0]     |   |   |   |   |   |   |   |

| Туре                                     | R/W             |   |   |   |   |   |   |   |

| Reset                                    | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |   |

| SFR Address = 0xB5; SFR Page = All Pages |                 |   |   |   |   |   |   |   |

| Bit | Name        | Function                                                 |  |  |  |  |

|-----|-------------|----------------------------------------------------------|--|--|--|--|

| 7:0 | SBRLH1[7:0] | UART1 Baud Rate Reload High Bits.                        |  |  |  |  |

|     |             | High Byte of reload value for UART1 Baud Rate Generator. |  |  |  |  |

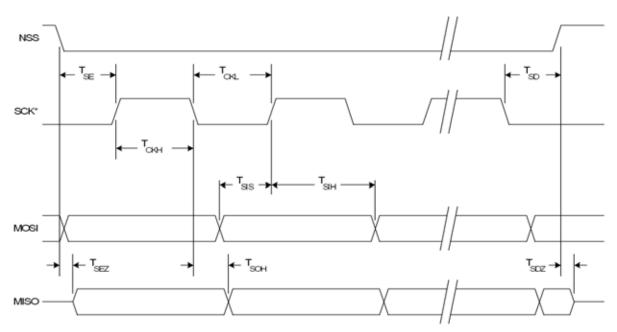

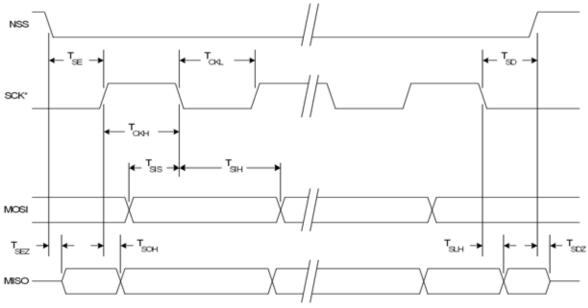

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

Figure 24.10. SPI Slave Timing (CKPHA = 0)

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

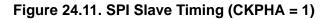

#### 25.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.5. Timer 2 8-Bit Mode Block Diagram

#### 25.2.3. Timer 2 Capture Modes: LFO Falling Edge

When T2CE = 1, Timer 2 will operate in a special capture mode with the LFO (T2CSS is set to 1). The LFO falling-edge capture mode can be used to calibrate the internal Low-Frequency Oscillator against the internal High-Frequency Oscillator or an external clock source. When T2SPLIT = 0, Timer 2 counts up and overflows from 0xFFFF to 0x0000. Each time a capture event is received, the contents of the Timer 2 registers (TMR2H:TMR2L) are latched into the Timer 2 Reload registers (TMR2RLH:TMR2RLL). A Timer 2 interrupt is generated if enabled.

### SFR Definition 25.23. TMR4H Timer 4 High Byte

| Bit                              | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------|------------|---|---|---|---|---|---|---|

| Name                             | TMR4H[7:0] |   |   |   |   |   |   |   |

| Туре                             | R/W        |   |   |   |   |   |   |   |

| Reset                            | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0x95; SFR Page = F |            |   |   |   |   |   |   |   |

| Bit | Name       | Function                                                                                                                                        |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR4H[7:0] | Timer 4 High Byte.                                                                                                                              |

|     |            | In 16-bit mode, the TMR4H register contains the high byte of the 16-bit Timer 4. In 8-bit mode, TMR4H contains the 8-bit high byte timer value. |

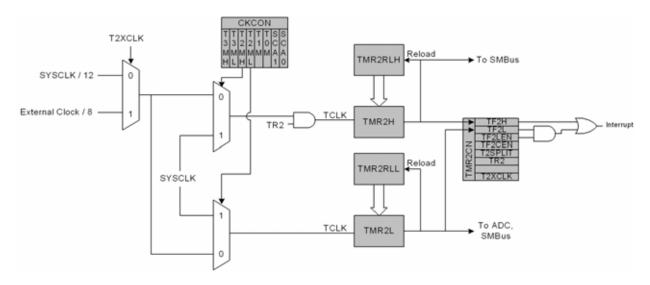

#### 26.3.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or fall-ing-edge caused the capture.

Figure 26.4. PCA Capture Mode Diagram

**Note:** The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

### 27. C2 Interface

C8051F388/9/A/B devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

#### 27.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

#### C2 Register Definition 27.1. C2ADD: C2 Address

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------|---|---|---|---|---|---|---|

| Name  | C2ADD[7:0] |   |   |   |   |   |   |   |

| Туре  | R/W        |   |   |   |   |   |   |   |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit | Name       |                                                                                                                                  | Function                                                                           |  |  |  |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| 7:0 | C2ADD[7:0] | C2 Address.                                                                                                                      |                                                                                    |  |  |  |

|     |            | The C2ADD register is accessed via the C2 interface to select the target Data register for C2 Data Read and Data Write commands. |                                                                                    |  |  |  |

|     |            | Address Description                                                                                                              |                                                                                    |  |  |  |

|     |            | 0x00                                                                                                                             | Selects the Device ID register for Data Read instructions                          |  |  |  |

|     |            | 0x01                                                                                                                             | Selects the Revision ID register for Data Read instructions                        |  |  |  |

|     |            | 0x02                                                                                                                             | Selects the C2 Flash Programming Control register for Data Read/Write instructions |  |  |  |

|     |            | 0xAD                                                                                                                             | Selects the C2 Flash Programming Data register for Data Read/Write instructions    |  |  |  |

Figure 28.2. Device Package – LQFP32

Figure 28.3. Device Package – QFN32

## **DOCUMENT CHANGE LIST**

#### **Revision 0.9 to Revision 0.91**

- Updated "Power" on page 33 to mention the INT2 pin may be left floating if it's not used.

- Added INT2 to Table 5.1, "Absolute Maximum Ratings," on page 34 and Table 5.3, "Port I/O DC Electrical Characteristics," on page 36.

- Added INT2 to Table 3.1, "Pin Definitions for the C8051F388/9/A/B," on page 21.

- Updated Figure 3.1, Figure 3.4, and Figure 3.7 to show the INT2 pin.

- Added "External Interrupt 2 (INT2)" on page 70.

- Updated SFR Definition 9.1 to include INT2.

- Added INT2 to Table 16.1, "Interrupt Summary," on page 114.

- Updated SFR Definition 16.5 and SFR Definition 16.6 to include INT2.

- Updated "Internal Oscillator Suspend Mode" on page 139 to mention INT2.

#### Revision 0.91 to Revision 1.0

- Updated Flash Endurance minimum specification, Flash Erase Cycle Time maximum specification, and added a note to Table 5.6 on page 37.

- Updated Figure 21.1 to show proper clock sources for SMBus0 and SMBus1.

#### **Revision 1.0 to Revision 1.1**

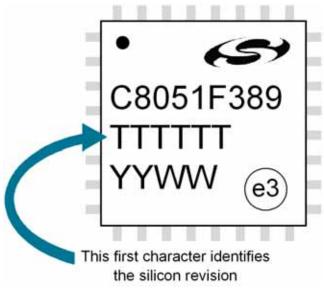

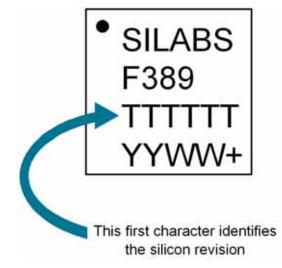

- Added revision B.

- Added "28. Revision Specific Behavior" .