Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 48 MIPS                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 2.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                     |

| Data Converters            | A/D 21x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 32-QFN (5x5)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f38b-b-gm |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Figures

| Figure 1.1. C8051F388/A Block Diagram                                    |    |

|--------------------------------------------------------------------------|----|

| Figure 1.2. C8051F389/B Block Diagram                                    | 18 |

| Figure 3.1. TQFP-48 (C8051F388/A) Pinout Diagram (Top View)              | 24 |

| Figure 3.2. TQFP-48 Package Diagram                                      | 25 |

| Figure 3.3. TQFP-48 Recommended PCB Land Pattern                         | 26 |

| Figure 3.4. LQFP-32 (C8051F389/B) Pinout Diagram (Top View)              | 27 |

| Figure 3.5. LQFP-32 Package Diagram                                      |    |

| Figure 3.6. LQFP-32 Recommended PCB Land Pattern                         |    |

| Figure 3.7. QFN-32 (C8051F389/B) Pinout Diagram (Top View)               | 30 |

| Figure 3.8. QFN-32 Package Drawing                                       | 31 |

| Figure 3.9. QFN-32 Recommended PCB Land Pattern                          |    |

| Figure 4.1. Connection Diagram with Voltage Regulator Used               | 33 |

| Figure 4.2. Connection Diagram with Voltage Regulator Not Used           | 33 |

| Figure 6.1. ADC0 Functional Block Diagram                                |    |

| Figure 6.2. Typical Temperature Sensor Transfer Function                 | 44 |

| Figure 6.3. Temperature Sensor Error with 1-Point Calibration            | 45 |

| Figure 6.4. 10-Bit ADC Track and Conversion Example Timing               |    |

| Figure 6.5. ADC0 Equivalent Input Circuits                               | 48 |

| Figure 6.6. ADC Window Compare Example: Right-Justified Data             | 54 |

| Figure 6.7. ADC Window Compare Example: Left-Justified Data              | 54 |

| Figure 7.1. Voltage Reference Functional Block Diagram                   |    |

| Figure 8.1. Comparator0 Functional Block Diagram                         |    |

| Figure 8.2. Comparator1 Functional Block Diagram                         |    |

| Figure 8.3. Comparator Hysteresis Plot                                   |    |

| Figure 8.4. Comparator Input Multiplexer Block Diagram                   |    |

| Figure 11.1. CIP-51 Block Diagram                                        |    |

| Figure 13.1. On-Chip Memory Map for 64 kB Devices (C8051F388/9)          |    |

| Figure 13.2. On-Chip Memory Map for 32 kB Devices (C8051F38A/B)          |    |

| Figure 14.1. Multiplexed Configuration Example                           |    |

| Figure 14.2. Non-multiplexed Configuration Example                       |    |

| Figure 14.3. EMIF Operating Modes                                        |    |

| Figure 14.4. Non-Multiplexed 16-bit MOVX Timing                          |    |

| Figure 14.5. Non-Multiplexed 8-bit MOVX without Bank Select Timing       |    |

| Figure 14.6. Non-Multiplexed 8-bit MOVX with Bank Select Timing 1        |    |

| Figure 14.7. Multiplexed 16-bit MOVX Timing 1                            |    |

| Figure 14.8. Multiplexed 8-bit MOVX without Bank Select Timing 1         |    |

| Figure 14.9. Multiplexed 8-bit MOVX with Bank Select Timing 1            |    |

| Figure 17.1. Reset Sources 1                                             |    |

| Figure 17.2. Power-On and VDD Monitor Reset Timing 1                     |    |

| Figure 18.1. Flash Program Memory Map and Security Byte 1                |    |

| Figure 19.1. Oscillator Options 1                                        | 36 |

| Figure 19.2. External Crystal Example 1                                  |    |

| Figure 20.1. Port I/O Functional Block Diagram (Port 0 through Port 3) 1 | 47 |

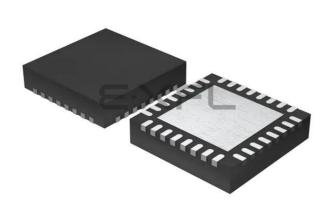

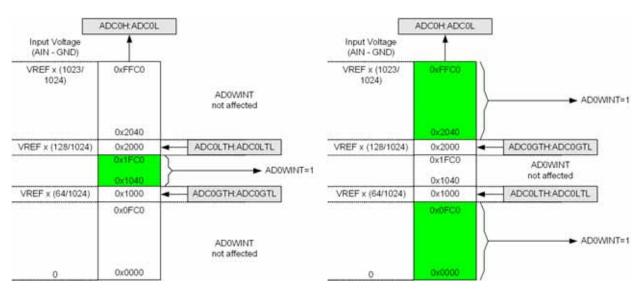

### 6.4.1. Window Detector Example

Figure 6.6 shows two example window comparisons for right-justified, single-ended data, with ADC0LTH:ADC0LTL = 0x0080 (128d) and ADC0GTH:ADC0GTL = 0x0040 (64d). The input voltage can range from 0 to VREF x (1023/1024) with respect to GND, and is represented by a 10-bit unsigned integer value. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0040 < ADC0H:ADC0L < 0x0080). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0040 or ADC0H:ADC0L > 0x0080). Figure 6.7 shows an example using left-justified data with the same comparison values.

Figure 6.6. ADC Window Compare Example: Right-Justified Data

Figure 6.7. ADC Window Compare Example: Left-Justified Data

## SFR Definition 8.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5             | 4      | 3 | 2 | 1    | 0      |

|-------|---|---|---------------|--------|---|---|------|--------|

| Name  |   |   | <b>CP0RIE</b> | CP0FIE |   |   | CP0M | D[1:0] |

| Туре  | R | R | R/W           | R/W    | R | R | R/W  |        |

| Reset | 0 | 0 | 0             | 0      | 0 | 0 | 1    | 0      |

### SFR Address = 0x9D; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 5   | CPORIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                        |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                     |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

| Mnemonic                   | Description                                                            | Bytes          | Clock<br>Cycles |

|----------------------------|------------------------------------------------------------------------|----------------|-----------------|

| ANL C, bit                 | AND direct bit to Carry                                                | 2              | 2               |

| ANL C, /bit                | AND complement of direct bit to Carry                                  | 2              | 2               |

| ORL C, bit                 | OR direct bit to carry                                                 | 2              | 2               |

| ORL C, /bit                | OR complement of direct bit to Carry                                   | 2              | 2               |

| MOV C, bit                 | Move direct bit to Carry                                               | 2              | 2               |

| MOV bit, C                 | Move Carry to direct bit                                               | 2              | 2               |

| Program Flow               |                                                                        | •              |                 |

| Timings are listed with th | e PFE on and FLRT = 0. Extra cycles are required for t                 | oranches if Fl | _RT = 1.        |

| JC rel                     | Jump if Carry is set                                                   | 2              | 2/4             |

| JNC rel                    | Jump if Carry is not set                                               | 2              | 2/4             |

| JB bit, rel                | Jump if direct bit is set                                              | 3              | 3/5             |

| JNB bit, rel               | Jump if direct bit is not set                                          | 3              | 3/5             |

| JBC bit, rel               | Jump if direct bit is set and clear bit                                | 3              | 3/5             |

| ACALL addr11               | Absolute subroutine call                                               | 2              | 4               |

| LCALL addr16               | Long subroutine call                                                   | 3              | 5               |

| RET                        | Return from subroutine                                                 | 1              | 6               |

| RETI                       | Return from interrupt                                                  | 1              | 6               |

| AJMP addr11                | Absolute jump                                                          | 2              | 4               |

| LJMP addr16                | Long jump                                                              | 3              | 5               |

| SJMP rel                   | Short jump (relative address)                                          | 2              | 4               |

| JMP @A+DPTR                | Jump indirect relative to DPTR                                         | 1              | 4               |

| JZ rel                     | Jump if A equals zero                                                  | 2              | 2/4             |

| JNZ rel                    | Jump if A does not equal zero                                          | 2              | 2/4             |

| CJNE A, direct, rel        | Compare direct byte to A and jump if not equal                         | 3              | 4/6             |

| CJNE A, #data, rel         | Compare immediate to A and jump if not equal                           | 3              | 3/5             |

| CJNE Rn, #data, rel        | Compare immediate to Register and jump if not equal                    | 3              | 3/5             |

| CJNE @Ri, #data, rel       | IE @Ri, #data, rel Compare immediate to indirect and jump if not equal |                | 4/6             |

| DJNZ Rn, rel               | Decrement Register and jump if not zero                                | 2              | 2/4             |

| DJNZ direct, rel           | Decrement direct byte and jump if not zero                             | 3              | 3/5             |

| NOP                        | No operation                                                           | 1              | 1               |

## Table 11.1. CIP-51 Instruction Set Summary (Continued)

# C8051F388/9/A/B

### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0–R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00– 0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

**bit** - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

# 12. Prefetch Engine

The C8051F388/9/A/B family of devices incorporate a 2-byte prefetch engine. Because the access time of the Flash memory is 40 ns, and the minimum instruction time is roughly 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from Flash memory two bytes at a time by the prefetch engine and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from Flash memory. It is recommended that the prefetch be used for optimal code execution timing.

Note: The prefetch engine can be disabled when the device is in suspend mode to save power.

### SFR Definition 12.1. PFE0CN: Prefetch Engine Control

| Bit   | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0     |

|-------|---|---|------|---|---|---|---|-------|

| Name  |   |   | PFEN |   |   |   |   | FLBWE |

| Туре  | R | R | R/W  | R | R | R | R | R/W   |

| Reset | 0 | 0 | 1    | 0 | 0 | 0 | 0 | 0     |

### SFR Address = 0xAF; SFR Page = All Pages

| Bit | Name   | Function                                                        |

|-----|--------|-----------------------------------------------------------------|

| 7:6 | Unused | Read = 00b, Write = don't care.                                 |

| 5   | PFEN   | Prefetch Enable.                                                |

|     |        | This bit enables the prefetch engine.                           |

|     |        | 0: Prefetch engine is disabled.                                 |

|     |        | 1: Prefetch engine is enabled.                                  |

| 4:1 | Unused | Read = 0000b. Write = don't care.                               |

| 0   | FLBWE  | Flash Block Write Enable.                                       |

|     |        | This bit allows block writes to Flash memory from software.     |

|     |        | 0: Each byte of a software Flash write is written individually. |

|     |        | 1: Flash bytes are written in groups of two.                    |

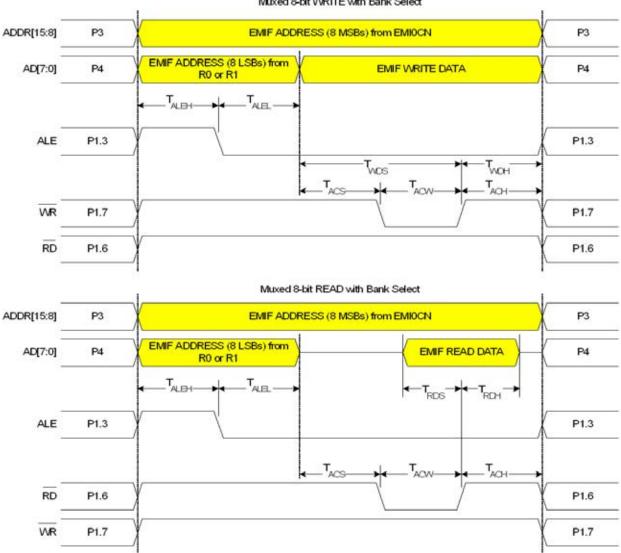

### 14.6.2.3. 8-bit MOVX with Bank Select: EMI0CF[4:2] = 010

Muxed 8-bit WRITE with Bank Select

Figure 14.9. Multiplexed 8-bit MOVX with Bank Select Timing

### 17.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "26.4. Watchdog Timer Mode" on page 269; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

### 17.7. Flash Error Reset

If a Flash program read, write, or erase operation targets an illegal address, a system reset is generated. This may occur due to any of the following:

- Programming hardware attempts to write or erase a Flash location which is above the user code space address limit.

- A Flash read from firmware is attempted above user code space. This occurs when a MOVC operation is attempted above the user code space address limit.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the user code space address limit.

- A Flash read, write, or erase attempt is restricted due to a Flash security setting.

- A Flash write or erase is attempted when the V<sub>DD</sub> monitor is not enabled.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

### 17.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

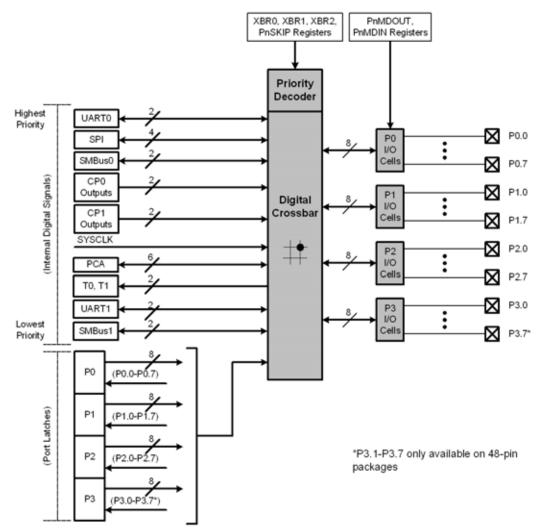

# 20. Port Input/Output

Digital and analog resources are available through 40 I/O pins (C8051F388/A) or 25 I/O pins (C8051F389/ B). Port pins are organized as shown in Figure 20.1. Each of the Port pins can be defined as general-purpose I/O (GPIO) or analog input; Port pins P0.0-P3.7 can be assigned to one of the internal digital resources as shown in Figure 20.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 20.3 and Figure 20.4). The registers XBR0, XBR1, and XBR2 defined in SFR Definition 20.1, SFR Definition 20.2, and SFR Definition 20.3, are used to select internal digital functions.

All Port I/Os are 5 V tolerant (refer to Figure 20.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1,2,3,4).

Figure 20.1. Port I/O Functional Block Diagram (Port 0 through Port 3)

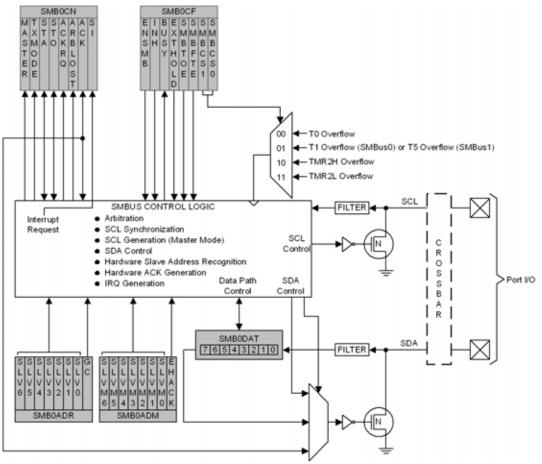

# 21. SMBus0 and SMBus1 (I<sup>2</sup>C Compatible)

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus. The C8051F388/9/A/B devices contain two SMBus interfaces, SMBus0 and SMBus1.

Reads and writes to the SMBus by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock as a master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The SMBus may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. The SMBus peripherals can be fully driven by software (i.e., software accepts/rejects slave addresses, and generates ACKs), or hardware slave address recognition and automatic ACK generation can be enabled to minimize software overhead. A block diagram of the SMBus0 peripheral and the associated SFRs is shown in Figure 21.1. SMBus1 is identical, with the exception of the available timer options for the clock source, and the timer used to implement the SCL low time-out feature. Refer to the specific SFR definitions for more details.

Figure 21.1. SMBus Block Diagram

### SFR Definition 21.11. SMB1DAT: SMBus Data

|       |                                  |                           |   | i |          |   |   | . <u> </u> |

|-------|----------------------------------|---------------------------|---|---|----------|---|---|------------|

| Bit   | 7                                | 6                         | 5 | 4 | 3        | 2 | 1 | 0          |

| Nam   | e                                | SMB1DAT[7:0]              |   |   |          |   |   |            |

| Туре  | e                                | R/W                       |   |   |          |   |   |            |

| Rese  | et 0                             | 0                         | 0 | 0 | 0        | 0 | 0 | 0          |

| SFR A | SFR Address = 0xC2; SFR Page = F |                           |   |   |          |   |   |            |

| Bit   | Name                             |                           |   |   | Function |   |   |            |

| 7:0   | SMB1DAT[7:0                      | SMB1DAT[7:0] SMBus1 Data. |   |   |          |   |   |            |

|       |                                  |                           |   |   |          |   |   | <b></b>    |

| 1.0 | Sindus i Data.                                                                                                                                                                                                                                                                                                                                                           |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | The SMB1DAT register contains a byte of data to be transmitted on the SMBus1 serial interface or a byte that has just been received on the SMBus1 serial inter-                                                                                                                                                                                                          |  |

|     | face. The CPU can read from or write to this register whenever the SI1 serial inter-<br>rupt flag (SMB1CN.0) is set to logic 1. The serial data in the register remains stable<br>as long as the SI1 flag is set. When the SI1 flag is not set, the system may be in the<br>process of shifting data in/out and the CPU should not attempt to access this regis-<br>ter. |  |

### SFR Definition 23.1. SCON1: UART1 Control

| Bit    | 7          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                                                                                                                                                                                                                                                          | 4             | 3        | 2 | 1   | 0   |

|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------|---|-----|-----|

| Name   | OVR1       | 1 PERR1 THRE1 REN1 TBX1 RBX1 TI1                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                            |               |          |   | TI1 | RI1 |

| Туре   | R/W        | R/W R/W R R/W R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                            |               |          |   | R/W |     |

| Reset  | 0          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                          | 0             | 0        | 0 | 0   | 0   |

| SFR Ad | ddress = 0 | xD2; SFR Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e = All Pages                                                                                                                                                                                                                                                                                                              | 6             |          |   | 1   |     |

| Bit    | Name       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |               | Function |   |     |     |

| 7      | OVR1       | This bit indicate<br>due to a full FIF<br>0: Receive FIF0                                                                                                                                                                                                                                                                                                                                                                                                                                    | Receive FIFO Overrun Flag.<br>This bit indicates a receive FIFO overrun condition, where an incoming character is discarded<br>due to a full FIFO. This bit must be cleared to 0 by software.<br>0: Receive FIFO Overrun has not occurred.<br>1: Receive FIFO Overrun has occurred.                                        |               |          |   |     |     |

| 6      | PERR1      | When parity is e<br>parity of the old<br>cleared to 0 by<br>0: Parity Error h                                                                                                                                                                                                                                                                                                                                                                                                                | Parity Error Flag.<br>When parity is enabled, this bit indicates that a parity error has occurred. It is set to 1 when the parity of the oldest byte in the FIFO does not match the selected Parity Type. This bit must be cleared to 0 by software.<br>0: Parity Error has not occurred.<br>1: Parity Error has occurred. |               |          |   |     |     |

| 5      | THRE1      | <b>Transmit Hold</b><br>0: Transmit Hold<br>1: Transmit Hold                                                                                                                                                                                                                                                                                                                                                                                                                                 | ding Register                                                                                                                                                                                                                                                                                                              | not Empty - c |          |   |     |     |

| 4      | REN1       | This bit enables<br>receive FIFO.<br>0: UART1 recept                                                                                                                                                                                                                                                                                                                                                                                                                                         | Receive Enable.<br>This bit enables/disables the UART receiver. When disabled, bytes can still be read from the receive FIFO.<br>0: UART1 reception disabled.<br>1: UART1 reception enabled.                                                                                                                               |               |          |   |     |     |

| 3      | TBX1       | The logic level of                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>Extra Transmission Bit.</b><br>The logic level of this bit will be assigned to the extra transmission bit when XBE1 = 1. This bit is not used when Parity is enabled.                                                                                                                                                   |               |          |   |     |     |

| 2      | RBX1       | <b>Extra Receive Bit.</b><br>RBX1 is assigned the value of the extra bit when XBE1 = 1. If XBE1 is cleared to 0, RBX1 is assigned the logic level of the first stop bit. This bit is not valid when Parity is enabled.                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |               |          |   |     |     |

| 1      | TI1        | <b>Transmit Interrupt Flag.</b><br>Set to a 1 by hardware after data has been transmitted at the beginning of the STOP bit. When the UART1 interrupt is enabled, setting this bit causes the CPU to vector to the UART1 interrupt service routine. This bit must be cleared manually by software.                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                            |               |          |   |     |     |

| 0      | RI1        | <b>Receive Interrupt Flag.</b><br>Set to 1 by hardware when a byte of data has been received by UART1 (set at the STOP bit sampling time). When the UART1 interrupt is enabled, setting this bit to 1 causes the CPU to vector to the UART1 interrupt service routine. This bit must be cleared manually by software. Note that RI1 will remain set to '1' as long as there is still data in the UART FIFO. After the last byte has been shifted from the FIFO to SBUF1, RI1 can be cleared. |                                                                                                                                                                                                                                                                                                                            |               |          |   |     |     |

# C8051F388/9/A/B

1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

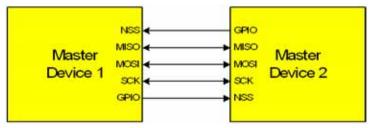

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 24.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 24.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 24.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

Figure 24.2. Multiple-Master Mode Connection Diagram

Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

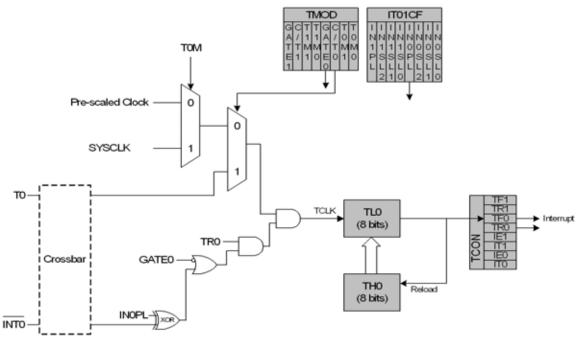

Figure 25.2. T0 Mode 2 Block Diagram

### 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates or overflow conditions for other peripherals. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

# C8051F388/9/A/B

## SFR Definition 25.7. TH0: Timer 0 High Byte

| Bit                                      | 7    | 6   | 5 | 4   | 3     | 2 | 1 | 0 |

|------------------------------------------|------|-----|---|-----|-------|---|---|---|

| Name                                     |      |     |   | TH0 | [7:0] |   |   |   |

| Туре                                     |      | R/W |   |     |       |   |   |   |

| Reset                                    | 0    | 0   | 0 | 0   | 0     | 0 | 0 | 0 |

| SFR Address = 0x8C; SFR Page = All Pages |      |     |   |     |       |   |   |   |

| Bit                                      | Name |     |   |     |       |   |   |   |

|     | Hanto    | - unotion                                                |

|-----|----------|----------------------------------------------------------|

| 7:0 | TH0[7:0] | Timer 0 High Byte.                                       |

|     |          | The TH0 register is the high byte of the 16-bit Timer 0. |

## SFR Definition 25.8. TH1: Timer 1 High Byte

| Bit   | 7                                        | 6           | 5        | 4 | 3        | 2 | 1 | 0 |

|-------|------------------------------------------|-------------|----------|---|----------|---|---|---|

| Nam   | me TH1[7:0]                              |             |          |   |          |   |   |   |

| Туре  | R/W                                      |             |          |   |          |   |   |   |

| Rese  | et 0                                     | 0           | 0        | 0 | 0        | 0 | 0 | 0 |

| SFR A | SFR Address = 0x8D; SFR Page = All Pages |             |          |   |          |   |   |   |

| Bit   | Name                                     |             |          |   | Function |   |   |   |

| 7:0   | TH1[7:0]                                 | Timer 1 Hig | gh Byte. |   |          |   |   |   |

| Th | a TH1 register  | is the high hyte | e of the 16-bit Timer 1. |

|----|-----------------|------------------|--------------------------|

|    | C IIII ICGISICI | 13 the high byte |                          |

# SFR Definition 25.13. TMR2H Timer 2 High Byte

| Bit                              | 7          | 6            | 5      | 4 | 3 | 2 | 1 | 0 |

|----------------------------------|------------|--------------|--------|---|---|---|---|---|

| Nam                              | e          | TMR2H[7:0]   |        |   |   |   |   |   |

| Туре                             | 9          | R/W          |        |   |   |   |   |   |

| Rese                             | et 0       | 0            | 0      | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0xCD; SFR Page = 0 |            |              |        |   |   |   |   |   |

| Bit                              | Name       | Function     |        |   |   |   |   |   |

| 7.0                              | TMR2H[7·0] | Timer 2 L ov | w Ryte |   |   |   |   |   |

| ĺ | 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                     |

|---|-----|------------|---------------------------------------------------------------------------------------|

|   |     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8 |

|   |     |            | bit mode, TMR2H contains the 8-bit high byte timer value.                             |

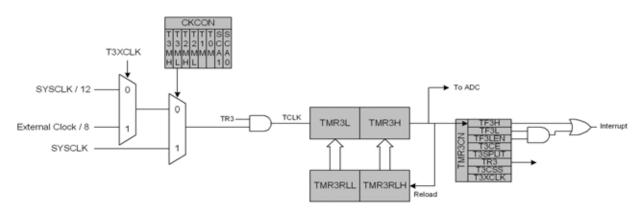

### 25.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode, (split) 8-bit auto-reload mode, or Low-Frequency Oscillator (LFO) Rising Edge capture mode. The Timer 3 operation mode is defined by the T3SPLIT (TMR3CN.3), T3CE (TMR3CN.4) bits, and T3CSS (TMR3CN.1) bits.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

### 25.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 25.8, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 25.8. Timer 3 16-Bit Mode Block Diagram

### 25.3.2. 8-bit Timers with Auto-Reload

When T3SPLIT is 1 and T3CE = 0, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 25.9. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control for TMR3H. TMR3L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bit (T3XCLK in TMR3CN), as follows:

| ТЗМН | T3XCLK | TMR3H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T3ML | T3XCLK | TMR3L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled, an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 25.9. Timer 3 8-Bit Mode Block Diagram

### 25.3.3. Timer 3 Capture Modes: LFO Falling Edge

When T3CE = 1, Timer 3 will operate in a special capture mode with the LFO (T3CSS is set to 1). The LFO falling-edge capture mode can be used to calibrate the internal Low-Frequency Oscillator against the internal High-Frequency Oscillator or an external clock source. When T3SPLIT = 0, Timer 3 counts up and overflows from 0xFFFF to 0x0000. Each time a capture event is received, the contents of the Timer 3 registers (TMR3H:TMR3L) are latched into the Timer 3 Reload registers (TMR3RLH:TMR3RLL). A Timer 3 interrupt is generated if enabled.

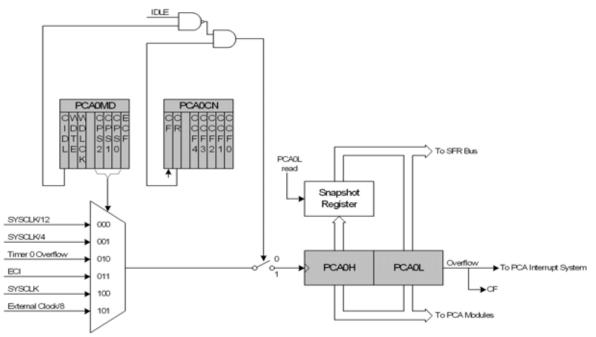

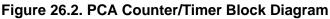

### 26.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2–CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 26.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2      | CPS1                                                                                 | CPS0 | Timebase                                                              |  |

|-----------|--------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------|--|

| 0         | 0                                                                                    | 0    | System clock divided by 12                                            |  |

| 0         | 0                                                                                    | 1    | System clock divided by 4                                             |  |

| 0         | 1                                                                                    | 0    | Timer 0 overflow                                                      |  |

| 0         | 1                                                                                    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |  |

| 1         | 0                                                                                    | 0    | System clock                                                          |  |

| 1         | 0                                                                                    | 1    | External oscillator source divided by 8 <sup>*</sup>                  |  |

| 1         | 1                                                                                    | Х    | Reserved                                                              |  |

| Note: Ext | lote: External oscillator source divided by 8 is synchronized with the system clock. |      |                                                                       |  |

Table 26.1. PCA Timebase Input Options

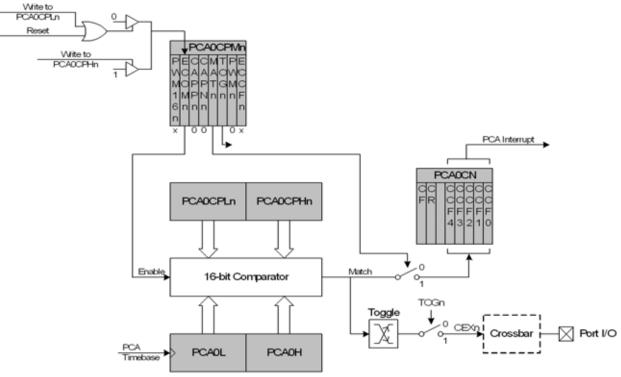

### 26.3.3. High-Speed Output Mode

In High-Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1. An interrupt request is generated if the CCFn interrupt for that module is enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode. If ECOMn is cleared, the associated pin will retain its state, and not toggle on the next match event.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.