Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 48 MIPS                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 25                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                   |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 2.25K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                     |

| Data Converters            | A/D 21x10b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 32-LQFP                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f38b-b-gq |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5. Electrical Characteristics

## 5.1. Absolute Maximum Specifications

## Table 5.1. Absolute Maximum Ratings

| Parameter                                                                 | Conditions                                                             | Min          | Тур | Max                          | Units  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|-----|------------------------------|--------|

| Junction Temperature Under Bias                                           |                                                                        | -55          | —   | 125                          | °C     |

| Storage Temperature                                                       |                                                                        | -65          |     | 150                          | °C     |

| Voltage on RST, INT2, or any Port<br>I/O Pin with Respect to GND          | V <sub>DD</sub> ≥ 2.2 V<br>V <sub>DD</sub> < 2.2 V                     | -0.3<br>-0.3 | _   | 5.8<br>V <sub>DD</sub> + 3.6 | V<br>V |

| Voltage on V <sub>DD</sub> with Respect to<br>GND                         | Regulator1 in Normal Mode<br>Regulator1 in Bypass Mode                 | -0.3<br>-0.3 |     | 4.2<br>1.98                  | V<br>V |

| Maximum Total Current through<br>V <sub>DD</sub> or GND                   |                                                                        | _            |     | 500                          | mA     |

| Maximum Output Current sunk by RST or any Port Pin                        |                                                                        |              |     | 100                          | mA     |

| Note: Stresses above those listed und<br>This is a stress rating only and | der "Absolute Maximum Ratings" i<br>functional operation of the device | •            | •   | •                            |        |

This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# SFR Definition 6.9. AMX0P: AMUX0 Positive Channel Select

| Bit  | 7          | 6        | 5                  | 4                  | 3                 | 2                | 1       | 0                |  |  |

|------|------------|----------|--------------------|--------------------|-------------------|------------------|---------|------------------|--|--|

| Nam  | е          |          |                    | 1                  | AMX0P             | [5:0]            | 1       |                  |  |  |

| Тур  | e R        | R        | R R/W              |                    |                   |                  |         |                  |  |  |

| Rese | et 0       | 0        | 0                  | 0                  | 0                 | 0                | 0       | 0                |  |  |

|      |            |          | Page = All Pages   |                    |                   | -                |         |                  |  |  |

| Bit  | Name       |          | age = All Pages    | >                  | Function          |                  |         |                  |  |  |

| 7:6  | Unused     | Read = 0 | 0b; Write = don    | 't care.           |                   |                  |         |                  |  |  |

| 5:0  | AMX0P[5:0] | AMUX0 F  | Positive Input S   | Selection.         |                   |                  |         |                  |  |  |

|      |            | AMX0P    | 32-pin<br>Packages | 48-pin<br>Packages | AMX0P             | 32-pin<br>Packag |         | 3-pin<br>ackages |  |  |

|      |            | 000000:  | P1.0               | P2.0               | 010010            | : P0.1           | P       | 0.4              |  |  |

|      |            | 000001:  | P1.1               | P2.1               | 010011            | : P0.4           | P       | 1.1              |  |  |

|      |            | 000010:  | P1.2               | P2.2               | 010100            | : P0.5           | P       | 1.2              |  |  |

|      |            | 000011:  | P1.3               | P2.3               | 010101:           | : Reserve        | ed P    | 1.0              |  |  |

|      |            | 000100:  | P1.4               | P2.5               | 010110            | : Reserve        | ed P    | 1.3              |  |  |

|      |            | 000101:  | P1.5               | P2.6               | 010111            |                  |         | 1.6              |  |  |

|      |            | 000110:  | P1.6               | P3.0               | 3.0 011000: Res   |                  | ed P    | 1.7              |  |  |

|      |            | 000111:  | P1.7               | P3.1               | 011001            |                  | ed P2.4 |                  |  |  |

|      |            | 001000:  | P2.0               | P3.4               | 011010: Reserved  |                  |         | 2.7              |  |  |

|      |            | 001001:  | P2.1               | P3.5               | 011011            |                  | ed P    | 3.2              |  |  |

|      |            | 001010:  | P2.2               | P3.7               | 011100            |                  |         | 3.3              |  |  |

|      |            | 001011:  | P2.3               | P4.0               | 011101            |                  |         | 3.6              |  |  |

|      |            | 001100:  | P2.4               | P4.3               | 011110            | '                |         | emp Sensor       |  |  |

|      |            | 001101:  | P2.5               | P4.4               | 011111:           |                  |         | DD               |  |  |

|      |            | 001110:  | P2.6               | P4.5               | 100000            |                  |         | 4.1              |  |  |

|      |            | 001111:  | P2.7               | P4.6               | 100001            |                  |         | 4.2              |  |  |

|      |            | 010000:  | P3.0               | Reserved           | 100010            |                  |         | 4.7              |  |  |

|      |            | 010001:  | P0.0               | P0.3               | 100011<br>111111: |                  | ed R    | eserved          |  |  |

# SFR Definition 9.1. REG01CN: Voltage Regulator Control

| Bit   | 7           | 6                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                        | 4                                | 3                     | 2            | 1            | 0             |  |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|--------------|--------------|---------------|--|

| Nam   | e REG0DI    | S INT2STAT                                                                                                                                                                                                                                                                                                                                                 | Reserved                                                                                                                                 | REG0MD                           | STOPCF                | Reserved     | REG1MD       | Reserved      |  |

| Туре  | e R/W       | R                                                                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                      | R/W                              | R/W                   | R/W          | R/W          | R/W           |  |

| Rese  | et 0        | 0                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                        | 0                                | 0                     | 0            | 0            | 0             |  |

| SFR A | Address = 0 | <c9; page<="" sfr="" td=""><td>e = All Pages</td><td>6</td><td></td><td></td><td></td><td></td></c9;>                                                                                                                                                                                                                                                      | e = All Pages                                                                                                                            | 6                                |                       |              |              |               |  |

| Bit   | Name        |                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |                                  | Function              |              |              |               |  |

| 7     | REG0DIS     | Voltage Regu<br>This bit enable<br>0: Voltage Reg<br>1: Voltage Reg                                                                                                                                                                                                                                                                                        | es or disable<br>gulator Enab                                                                                                            | s the REG0<br>led.               | Voltage Reg           | gulator.     |              |               |  |

| 6     | INT2STAT    | This bit indica<br>0: INT2 pin is                                                                                                                                                                                                                                                                                                                          | INT2 Signal Status.<br>This bit indicates the status of the INT2 pin.<br>0: INT2 pin is currently low.<br>1: INT2 pin is currently high. |                                  |                       |              |              |               |  |

| 5     | Reserved    | Must Write 0b                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |                                  |                       |              |              |               |  |

| 4     | REG0MD      | Voltage Regu                                                                                                                                                                                                                                                                                                                                               | lator (REG                                                                                                                               | )) Mode Sel                      | ect.                  |              |              |               |  |

|       |             | This bit select<br>REG0 voltage<br>0: REG0 Volta<br>1: REG0 Volta                                                                                                                                                                                                                                                                                          | regulator of<br>ige Regulato                                                                                                             | perates in lov<br>or in normal i | wer power (s<br>mode. |              |              | et to 1, the  |  |

| 3     | STOPCF      | Stop Mode C<br>This bit config<br>0: REG1 Regu<br>device.<br>1: REG1 Regu<br>reset the device                                                                                                                                                                                                                                                              | ures the RE<br>ulator is still a<br>ulator is shut                                                                                       | G1 regulator<br>active in STC    | )P mode. An           | y enabled re | set source w | ill reset the |  |

| 2     | Reserved    | Must Write 0b                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |                                  |                       |              |              |               |  |

| 1     | REG1MD      | Voltage Regu                                                                                                                                                                                                                                                                                                                                               | lator (REG                                                                                                                               | I) Mode.                         |                       |              |              |               |  |

|       |             | <ul> <li>This bit selects the Voltage Regulator mode for REG1. When REG1MD is set to 1, the REG1 voltage regulator operates in lower power mode.</li> <li>0: REG1 Voltage Regulator in normal mode.</li> <li>1: REG1 Voltage Regulator in low power mode.</li> <li>This bit should not be set to '1' if the REG0 Voltage Regulator is disabled.</li> </ul> |                                                                                                                                          |                                  |                       |              |              | et to 1, the  |  |

| 0     | Reserved    | Must Write 0b                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |                                  |                       |              |              |               |  |

# Table 11.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic             | Description                                | Bytes | Clock<br>Cycles |  |  |

|----------------------|--------------------------------------------|-------|-----------------|--|--|

| XRL direct, #data    | Exclusive-OR immediate to direct byte      | 3     | 3               |  |  |

| CLR A                | Clear A                                    | 1     | 1               |  |  |

| CPLA                 | CPL A Complement A                         |       |                 |  |  |

| RLA                  |                                            |       |                 |  |  |

| RLC A                | Rotate A left through Carry                | 1     | 1               |  |  |

| RR A                 | Rotate A right                             | 1     | 1               |  |  |

| RRC A                | Rotate A right through Carry               | 1     | 1               |  |  |

| SWAP A               | Swap nibbles of A                          | 1     | 1               |  |  |

| Data Transfer        |                                            |       |                 |  |  |

| MOV A, Rn            | Move Register to A                         | 1     | 1               |  |  |

| MOV A, direct        | Move direct byte to A                      | 2     | 2               |  |  |

| MOV A, @Ri           | Move indirect RAM to A                     | 1     | 2               |  |  |

| MOV A, #data         | Move immediate to A                        | 2     | 2               |  |  |

| MOV Rn, A            | Move A to Register                         | 1     | 1               |  |  |

| MOV Rn, direct       | Move direct byte to Register               | 2     | 2               |  |  |

| MOV Rn, #data        | Move immediate to Register                 | 2     | 2               |  |  |

| MOV direct, A        | Move A to direct byte                      | 2     | 2               |  |  |

| MOV direct, Rn       | Move Register to direct byte               | 2     | 2               |  |  |

| MOV direct, direct   | Move direct byte to direct byte            | 3     | 3               |  |  |

| MOV direct, @Ri      | Move indirect RAM to direct byte           | 2     | 2               |  |  |

| MOV direct, #data    | Move immediate to direct byte              | 3     | 3               |  |  |

| MOV @Ri, A           | Move A to indirect RAM                     | 1     | 2               |  |  |

| MOV @Ri, direct      | Move direct byte to indirect RAM           | 2     | 2               |  |  |

| MOV @Ri, #data       | Move immediate to indirect RAM             | 2     | 2               |  |  |

| MOV DPTR, #data16    | Load DPTR with 16-bit constant             | 3     | 3               |  |  |

| MOVC A, @A+DPTR      | Move code byte relative DPTR to A          | 1     | 3               |  |  |

| MOVC A, @A+PC        | Move code byte relative PC to A            | 1     | 3               |  |  |

| MOVX A, @Ri          | Move external data (8-bit address) to A    | 1     | 3               |  |  |

| MOVX @Ri, A          | Move A to external data (8-bit address)    | 1     | 3               |  |  |

| MOVX A, @DPTR        | Move external data (16-bit address) to A   | 1     | 3               |  |  |

| MOVX @DPTR, A        | Move A to external data (16-bit address)   | 1     | 3               |  |  |

| PUSH direct          | Push direct byte onto stack                | 2     | 2               |  |  |

| POP direct           | Pop direct byte from stack                 | 2     | 2               |  |  |

| XCH A, Rn            | Exchange Register with A                   | 1     | 1               |  |  |

| XCH A, direct        | Exchange direct byte with A                | 2     | 2               |  |  |

| XCH A, @Ri           | Exchange indirect RAM with A               | 1     | 2               |  |  |

| XCHD A, @Ri          | Exchange low nibble of indirect RAM with A | 1     | 2               |  |  |

| Boolean Manipulation |                                            | I     | <u>I</u>        |  |  |

| CLR C                | Clear Carry                                | 1     | 1               |  |  |

| CLR bit              | Clear direct bit                           | 2     | 2               |  |  |

| SETB C               | Set Carry                                  | 1     | 1               |  |  |

| SETB bit             | Set direct bit                             | 2     | 2               |  |  |

| CPL C                | Complement Carry                           | 1     | 1               |  |  |

| CPL bit              | Complement direct bit                      | 2     | 2               |  |  |

# 12. Prefetch Engine

The C8051F388/9/A/B family of devices incorporate a 2-byte prefetch engine. Because the access time of the Flash memory is 40 ns, and the minimum instruction time is roughly 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from Flash memory two bytes at a time by the prefetch engine and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from Flash memory. It is recommended that the prefetch be used for optimal code execution timing.

Note: The prefetch engine can be disabled when the device is in suspend mode to save power.

### SFR Definition 12.1. PFE0CN: Prefetch Engine Control

| Bit   | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0     |

|-------|---|---|------|---|---|---|---|-------|

| Name  |   |   | PFEN |   |   |   |   | FLBWE |

| Туре  | R | R | R/W  | R | R | R | R | R/W   |

| Reset | 0 | 0 | 1    | 0 | 0 | 0 | 0 | 0     |

#### SFR Address = 0xAF; SFR Page = All Pages

| Bit | Name   | Function                                                        |

|-----|--------|-----------------------------------------------------------------|

| 7:6 | Unused | Read = 00b, Write = don't care.                                 |

| 5   | PFEN   | Prefetch Enable.                                                |

|     |        | This bit enables the prefetch engine.                           |

|     |        | 0: Prefetch engine is disabled.                                 |

|     |        | 1: Prefetch engine is enabled.                                  |

| 4:1 | Unused | Read = 0000b. Write = don't care.                               |

| 0   | FLBWE  | Flash Block Write Enable.                                       |

|     |        | This bit allows block writes to Flash memory from software.     |

|     |        | 0: Each byte of a software Flash write is written individually. |

|     |        | 1: Flash bytes are written in groups of two.                    |

### 14.6. Timing

The timing parameters of the External Memory Interface can be configured to enable connection to devices having different setup and hold time requirements. The Address Setup time, Address Hold time, RD and WR strobe widths, and in multiplexed mode, the width of the ALE pulse are all programmable in units of SYSCLK periods through EMI0TC, shown in SFR Definition 14.3, and EMI0CF[1:0].

The timing for an off-chip MOVX instruction can be calculated by adding 4 SYSCLK cycles to the timing parameters defined by the EMI0TC register. Assuming non-multiplexed operation, the minimum execution time for an off-chip XRAM operation is 5 SYSCLK cycles (1 SYSCLK for RD or WR pulse + 4 SYSCLKs). For multiplexed operations, the Address Latch Enable signal will require a minimum of 2 additional SYSCLK cycles. Therefore, the minimum execution time for an off-chip XRAM operation in multiplexed mode is 7 SYSCLK cycles (2 for  $\overline{ALE}$  + 1 for  $\overline{RD}$  or  $\overline{WR}$  + 4). The programmable setup and hold times default to the maximum delay settings after a reset. Table 14.1 lists the AC parameters for the External Memory Interface, and Figure 14.4 through Figure 14.9 show the timing diagrams for the different External Memory Interface modes and MOVX operations.

# SFR Definition 14.3. EMI0TC: External Memory Timing Control

| Bit   | 7   | 6     | 5        | 4   | 3 | 2 | 1        | 0 |  |

|-------|-----|-------|----------|-----|---|---|----------|---|--|

| Name  | EAS | [1:0] | EWR[3:0] |     |   |   | EAH[1:0] |   |  |

| Туре  | R/W |       |          | R/\ | N |   | R/       | W |  |

| Reset | 1   | 1     | 1 1 1 1  |     |   | 1 | 1        |   |  |

SFR Address = 0x84; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | EAS[1:0] | EMIF Address Setup Time Bits.<br>00: Address setup time = 0 SYSCLK cycles.<br>01: Address setup time = 1 SYSCLK cycle.<br>10: Address setup time = 2 SYSCLK cycles.<br>11: Address setup time = 3 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5:2 | EWR[3:0] | EMIF WR and RD Pulse-Width Control Bits.         0000: WR and RD pulse width = 1 SYSCLK cycle.         0001: WR and RD pulse width = 2 SYSCLK cycles.         0010: WR and RD pulse width = 3 SYSCLK cycles.         0011: WR and RD pulse width = 4 SYSCLK cycles.         010: WR and RD pulse width = 5 SYSCLK cycles.         0101: WR and RD pulse width = 5 SYSCLK cycles.         0101: WR and RD pulse width = 6 SYSCLK cycles.         0111: WR and RD pulse width = 7 SYSCLK cycles.         0110: WR and RD pulse width = 8 SYSCLK cycles.         0111: WR and RD pulse width = 9 SYSCLK cycles.         1000: WR and RD pulse width = 10 SYSCLK cycles.         1011: WR and RD pulse width = 11 SYSCLK cycles.         1010: WR and RD pulse width = 12 SYSCLK cycles.         1011: WR and RD pulse width = 13 SYSCLK cycles.         1100: WR and RD pulse width = 14 SYSCLK cycles.         1101: WR and RD pulse width = 14 SYSCLK cycles.         1111: WR and RD pulse width = 15 SYSCLK cycles.         1111: WR and RD pulse width = 16 SYSCLK cycles. |

| 1:0 | EAH[1:0] | EMIF Address Hold Time Bits.<br>00: Address hold time = 0 SYSCLK cycles.<br>01: Address hold time = 1 SYSCLK cycle.<br>10: Address hold time = 2 SYSCLK cycles.<br>11: Address hold time = 3 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Parameter                    | Description                                       | Min*                    | Max*                     | Units |  |  |  |  |  |

|------------------------------|---------------------------------------------------|-------------------------|--------------------------|-------|--|--|--|--|--|

| T <sub>ACS</sub>             | Address/Control Setup Time                        | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |  |

| T <sub>ACW</sub>             | Address/Control Pulse Width                       | 1 x T <sub>SYSCLK</sub> | 16 x T <sub>SYSCLK</sub> | ns    |  |  |  |  |  |

| T <sub>ACH</sub>             | Address/Control Hold Time                         | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |  |

| T <sub>ALEH</sub>            | Address Latch Enable High Time                    | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |  |

| T <sub>ALEL</sub>            | Address Latch Enable Low Time                     | 1 x T <sub>SYSCLK</sub> | 4 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |  |

| T <sub>WDS</sub>             | Write Data Setup Time                             | 1 x T <sub>SYSCLK</sub> | 19 x T <sub>SYSCLK</sub> | ns    |  |  |  |  |  |

| T <sub>WDH</sub>             | Write Data Hold Time                              | 0                       | 3 x T <sub>SYSCLK</sub>  | ns    |  |  |  |  |  |

| T <sub>RDS</sub>             | Read Data Setup Time                              | 20                      |                          | ns    |  |  |  |  |  |

| T <sub>RDH</sub>             |                                                   |                         |                          |       |  |  |  |  |  |

| Note: T <sub>SYSCLK</sub> is | equal to one period of the device system clock (S | YSCLK).                 |                          |       |  |  |  |  |  |

### Table 14.1. AC Parameters for External Memory Interface

## SFR Definition 16.2. IP: Interrupt Priority

| Bit   | 7                                               | 6                                                                                                                          | 5                                                                                                         | 4               | 3            | 2             | 1   | 0   |  |  |

|-------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------|--------------|---------------|-----|-----|--|--|

| Nam   | е                                               | PSPI0                                                                                                                      | PT2                                                                                                       | PS0             | PT1          | PX1           | PT0 | PX0 |  |  |

| Тур   | e R                                             | R/W                                                                                                                        | R/W                                                                                                       | R/W             | R/W          | R/W           | R/W | R/W |  |  |

| Rese  | et 1                                            | 0                                                                                                                          | 0                                                                                                         | 0               | 0            | 0             | 0   | 0   |  |  |

| SFR A | Address = 0                                     | xB8; SFR Page                                                                                                              | = All Pages                                                                                               | ; Bit-Addres    | sable        |               |     | •   |  |  |

| Bit   | Name                                            |                                                                                                                            |                                                                                                           |                 | Function     |               |     |     |  |  |

| 7     | Unused                                          | Read = 1b, W                                                                                                               | rite = Don't (                                                                                            | Care.           |              |               |     |     |  |  |

| 6     | PSPI0                                           | Serial Periph                                                                                                              | eral Interfac                                                                                             | ce (SPI0) Int   | terrupt Prio | rity Control. |     |     |  |  |

|       |                                                 | This bit sets th                                                                                                           |                                                                                                           | . ,             | -            | •             |     |     |  |  |

|       |                                                 | 0: SPI0 interru                                                                                                            | pt set to low                                                                                             | v priority leve | el.          |               |     |     |  |  |

|       |                                                 | 1: SPI0 interru                                                                                                            | pt set to hig                                                                                             | h priority lev  | vel.         |               |     |     |  |  |

| 5     | PT2                                             | Timer 2 Inter                                                                                                              | upt Priority                                                                                              | Control.        |              |               |     |     |  |  |

|       |                                                 | This bit sets the priority of the Timer 2 interrupt.                                                                       |                                                                                                           |                 |              |               |     |     |  |  |

|       |                                                 | 0: Timer 2 inte                                                                                                            | •                                                                                                         |                 |              |               |     |     |  |  |

|       |                                                 | 1: Timer 2 inte                                                                                                            | rrupt set to                                                                                              | high priority   | level.       |               |     |     |  |  |

| 4     | PS0                                             | UART0 Interr                                                                                                               | upt Priority                                                                                              | Control.        |              |               |     |     |  |  |

|       |                                                 |                                                                                                                            | This bit sets the priority of the UART0 interrupt.                                                        |                 |              |               |     |     |  |  |

|       |                                                 | 0: UART0 inte                                                                                                              | •                                                                                                         |                 |              |               |     |     |  |  |

|       |                                                 | 1: UART0 inte                                                                                                              | rrupt set to h                                                                                            | high priority   | level.       |               |     |     |  |  |

| 3     | PT1                                             | Timer 1 Inter                                                                                                              | • •                                                                                                       |                 |              |               |     |     |  |  |

|       |                                                 | This bit sets th                                                                                                           |                                                                                                           |                 | •            |               |     |     |  |  |

|       |                                                 | <ul><li>0: Timer 1 interrupt set to low priority level.</li><li>1: Timer 1 interrupt set to high priority level.</li></ul> |                                                                                                           |                 |              |               |     |     |  |  |

|       |                                                 |                                                                                                                            | •                                                                                                         | • • •           |              |               |     |     |  |  |

| 2     | PX1                                             | External Inter                                                                                                             | -                                                                                                         | •               |              | ., ,          |     |     |  |  |

|       |                                                 | This bit sets th                                                                                                           |                                                                                                           |                 |              | interrupt.    |     |     |  |  |

|       |                                                 |                                                                                                                            | 0: External Interrupt 1 set to low priority level.<br>1: External Interrupt 1 set to high priority level. |                 |              |               |     |     |  |  |

| 4     | DTO                                             |                                                                                                                            | •                                                                                                         | • •             |              |               |     |     |  |  |

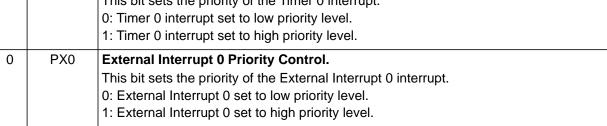

| 1     | PT0                                             | Timer 0 Intern                                                                                                             | • •                                                                                                       |                 | intorrunt    |               |     |     |  |  |

|       |                                                 |                                                                                                                            |                                                                                                           |                 | •            |               |     |     |  |  |

|       | 0: Timer 0 interrupt set to low priority level. |                                                                                                                            |                                                                                                           |                 |              |               |     |     |  |  |

## SFR Definition 16.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7   | 6    | 5    | 4     | 3     | 2      | 1        | 0     |

|-------|-----|------|------|-------|-------|--------|----------|-------|

| Name  | ET3 | ECP1 | ECP0 | EPCA0 | EADC0 | EWADC0 | Reserved | ESMB0 |

| Туре  | R/W | R/W  | R/W  | R/W   | R/W   | R/W    | R/W      | R/W   |

| Reset | 0   | 0    | 0    | 0     | 0     | 0      | 0        | 0     |

#### SFR Address = 0xE6; SFR Page = All Pages

| Bit | Name     | Function                                                                                                                                                                                                                                                                          |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ET3      | Enable Timer 3 Interrupt.<br>This bit sets the masking of the Timer 3 interrupt.<br>0: Disable Timer 3 interrupts.<br>1: Enable interrupt requests generated by the TF3L or TF3H flags.                                                                                           |

| 6   | ECP1     | <ul> <li>Enable Comparator1 (CP1) Interrupt.</li> <li>This bit sets the masking of the CP1 interrupt.</li> <li>0: Disable CP1 interrupts.</li> <li>1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags.</li> </ul>                                               |

| 5   | ECP0     | <ul> <li>Enable Comparator0 (CP0) Interrupt.</li> <li>This bit sets the masking of the CP0 interrupt.</li> <li>0: Disable CP0 interrupts.</li> <li>1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.</li> </ul>                                               |

| 4   | EPCA0    | <ul> <li>Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> </ul>                                              |

| 3   | EADC0    | <ul> <li>Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> </ul>          |

| 2   | EWADC0   | <ul> <li>Enable Window Comparison ADC0 Interrupt.</li> <li>This bit sets the masking of ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT).</li> </ul> |

| 1   | Reserved | Read = 0b, Must Write 0b.                                                                                                                                                                                                                                                         |

| 0   | ESMB0    | Enable SMBus0 Interrupt.<br>This bit sets the masking of the SMB0 interrupt.<br>0: Disable all SMB0 interrupts.<br>1: Enable interrupt requests generated by SMB0.                                                                                                                |

### **19.4.** Programmable Internal Low-Frequency (L-F) Oscillator

All C8051F388/9/A/B devices include a programmable low-frequency internal oscillator, which is calibrated to a nominal frequency of 80 kHz. The low-frequency oscillator circuit includes a divider that can be changed to divide the clock by 1, 2, 4, or 8, using the OSCLD bits in the OSCLCN register (see SFR Definition 19.5). Additionally, the OSCLF[3:0] bits can be used to adjust the oscillator's output frequency.

#### 19.4.1. Calibrating the Internal L-F Oscillator

Timers 2 and 3 include capture functions that can be used to capture the oscillator frequency, when running from a known time base. When either Timer 2 or Timer 3 is configured for L-F Oscillator Capture Mode, a falling edge (Timer 2) or rising edge (Timer 3) of the low-frequency oscillator's output will cause a capture event on the corresponding timer. As a capture event occurs, the current timer value (TMRnH:TMRnL) is copied into the timer reload registers (TMRnRLH:TMRnRLL). By recording the difference between two successive timer capture values, the low-frequency oscillator's period can be calculated. The OSCLF bits can then be adjusted to produce the desired oscillator frequency.

### SFR Definition 19.5. OSCLCN: Internal L-F Oscillator Control

| Bit   | 7      | 6       | 5          | 4      | 3      | 2      | 1    | 0      |

|-------|--------|---------|------------|--------|--------|--------|------|--------|

| Name  | OSCLEN | OSCLRDY | OSCLF[3:0] |        |        |        | OSCL | D[1:0] |

| Туре  | R/W    | R       |            | R.W    |        |        |      | W      |

| Reset | 0      | 0       | Varies     | Varies | Varies | Varies | 0    | 0      |

SFR Address = 0x86; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OSCLEN     | Internal L-F Oscillator Enable.                                                                                                                                                                                                                                                                                     |

|     |            | 0: Internal L-F Oscillator Disabled.                                                                                                                                                                                                                                                                                |

|     |            | 1: Internal L-F Oscillator Enabled.                                                                                                                                                                                                                                                                                 |

| 6   | OSCLRDY    | Internal L-F Oscillator Ready.                                                                                                                                                                                                                                                                                      |

|     |            | 0: Internal L-F Oscillator frequency not stabilized.                                                                                                                                                                                                                                                                |

|     |            | 1: Internal L-F Oscillator frequency stabilized.                                                                                                                                                                                                                                                                    |

|     |            | <b>Note:</b> OSCLRDY is only set back to 0 in the event of a device reset or a change to the OSCLD[1:0] bits.                                                                                                                                                                                                       |

| 5:2 | OSCLF[3:0] | Internal L-F Oscillator Frequency Control Bits.                                                                                                                                                                                                                                                                     |

|     |            | Fine-tune control bits for the Internal L-F oscillator frequency. When set to 0000b, the L-F oscillator operates at its fastest setting. When set to 1111b, the L-F oscillator operates at its slowest setting. The OSCLF bits should only be changed by firmware when the L-F oscillator is disabled (OSCLEN = 0). |

| 1:0 | OSCLD[1:0] | Internal L-F Oscillator Divider Select.                                                                                                                                                                                                                                                                             |

|     |            | 00: Divide by 8 selected.                                                                                                                                                                                                                                                                                           |

|     |            | 01: Divide by 4 selected.                                                                                                                                                                                                                                                                                           |

|     |            | 10: Divide by 2 selected.                                                                                                                                                                                                                                                                                           |

|     |            | 11: Divide by 1 selected.                                                                                                                                                                                                                                                                                           |

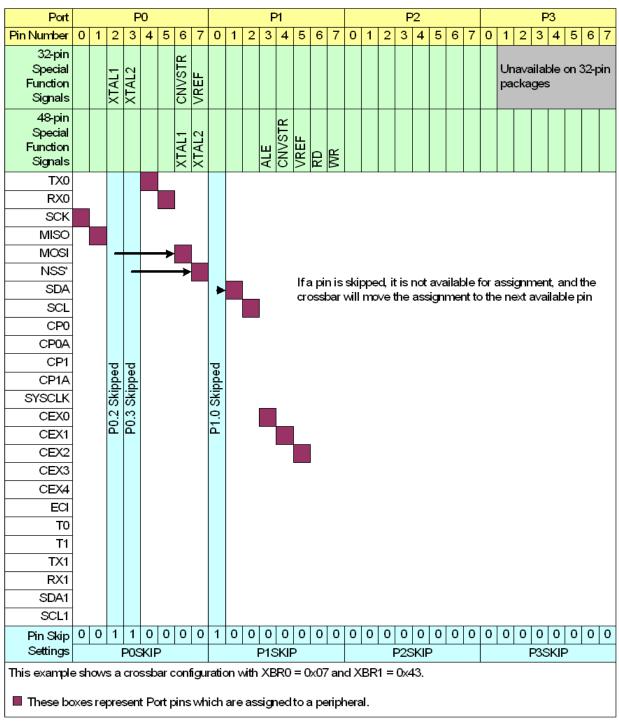

Figure 20.5. Crossbar Priority Decoder in Example Configuration (3 Pins Skipped)

|                 | Values Read      |                     | d |   |                                                                                       | Values to<br>Write                              |     |     | itus<br>iected |                                |   |   |   |                            |                                               |   |   |   |      |

|-----------------|------------------|---------------------|---|---|---------------------------------------------------------------------------------------|-------------------------------------------------|-----|-----|----------------|--------------------------------|---|---|---|----------------------------|-----------------------------------------------|---|---|---|------|

| Mode            | Status<br>Vector | Current SMbus State |   |   |                                                                                       | Typical Response Options                        | STA | STO | ACK            | Next Status<br>Vector Expected |   |   |   |                            |                                               |   |   |   |      |

|                 |                  | 0                   | 0 | x | A slave address + R/W was                                                             | If Write, Set ACK for first data byte.          | 0   | 0   | 1              | 0000                           |   |   |   |                            |                                               |   |   |   |      |

|                 |                  |                     |   |   | received; ACK sent.                                                                   | If Read, Load SMB0DAT with data byte            | 0   | 0   | X              | 0100                           |   |   |   |                            |                                               |   |   |   |      |

|                 | 0010             |                     |   |   | Lost arbitration as master;                                                           | If Write, Set ACK for first data byte.          | 0   | 0   | 1              | 0000                           |   |   |   |                            |                                               |   |   |   |      |

| iver            |                  | 0                   | 1 |   | slave address + R/W received;<br>ACK sent.                                            | If Read, Load SMB0DAT with data byte            | 0   | 0   | Х              | 0100                           |   |   |   |                            |                                               |   |   |   |      |

| ece             |                  |                     |   |   |                                                                                       | Reschedule failed transfer                      | 1   | 0   | Х              | 1110                           |   |   |   |                            |                                               |   |   |   |      |

| Slave Receiver  | 0001             | 0                   | 0 |   | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver. | Clear STO.                                      | 0   | 0   | Х              |                                |   |   |   |                            |                                               |   |   |   |      |

|                 |                  | 0                   | 1 | х | Lost arbitration while attempt-<br>ing a STOP.                                        | No action required (transfer complete/aborted). | 0   | 0   | 0              |                                |   |   |   |                            |                                               |   |   |   |      |

|                 | 0000             | 0                   | 0 | v |                                                                                       | Set ACK for next data byte;<br>Read SMB0DAT.    | 0   | 0   | 1              | 0000                           |   |   |   |                            |                                               |   |   |   |      |

|                 | 0000             |                     |   | ~ | X                                                                                     | ^                                               |     |     |                |                                | ^ | X | X | A slave byte was received. | Set NACK for next data byte;<br>Read SMB0DAT. | 0 | 0 | 0 | 0000 |

| uo              | 0010             | 0                   | 1 | x | Lost arbitration while attempt-                                                       | Abort failed transfer.                          | 0   | 0   | Х              | —                              |   |   |   |                            |                                               |   |   |   |      |

| nditi           | 0010             |                     |   |   | ing a repeated START.                                                                 | Reschedule failed transfer.                     | 1   | 0   | Х              | 1110                           |   |   |   |                            |                                               |   |   |   |      |

| Cor             | 0001             | 0                   | 1 | х | Lost arbitration due to a                                                             | Abort failed transfer.                          | 0   | 0   | Х              | —                              |   |   |   |                            |                                               |   |   |   |      |

| Error Condition | 2001             |                     |   |   | detected STOP.                                                                        | Reschedule failed transfer.                     | 1   | 0   | Х              | 1110                           |   |   |   |                            |                                               |   |   |   |      |

| ц               | 0000             | 0                   | 1 | x | Lost arbitration while transmit-                                                      | Abort failed transfer.                          | 0   | 0   | Х              | —                              |   |   |   |                            |                                               |   |   |   |      |

| Bus             | 0000             |                     |   |   | ting a data byte as master.                                                           | Reschedule failed transfer.                     | 1   | 0   | X              | 1110                           |   |   |   |                            |                                               |   |   |   |      |

## SFR Definition 23.1. SCON1: UART1 Control

| Bit    | 7          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                                                                                                                                                                   | 4             | 3        | 2    | 1         | 0                             |

|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------|------|-----------|-------------------------------|

| Name   | OVR1       | PERR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | THRE1                                                                                                                                                                                               | REN1          | TBX1     | RBX1 | TI1       | RI1                           |

| Туре   | R/W        | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R                                                                                                                                                                                                   | R/W           | R/W      | R/W  | R/W       | R/W                           |

| Reset  | 0          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                   | 0             | 0        | 0    | 0         | 0                             |

| SFR Ad | ddress = 0 | xD2; SFR Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | e = All Pages                                                                                                                                                                                       | 3             |          |      | 1         |                               |

| Bit    | Name       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                     |               | Function |      |           |                               |

| 7      | OVR1       | Receive FIFO Overrun Flag.         This bit indicates a receive FIFO overrun condition, where an incoming character is disc         due to a full FIFO. This bit must be cleared to 0 by software.         0: Receive FIFO Overrun has not occurred.         1: Receive FIFO Overrun has occurred.                                                                                                                                                                                                 |                                                                                                                                                                                                     |               |          |      | discarded |                               |

| 6      | PERR1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                     |               |          |      |           |                               |

| 5      | THRE1      | <b>Transmit Hold</b><br>0: Transmit Hold<br>1: Transmit Hold                                                                                                                                                                                                                                                                                                                                                                                                                                       | ding Register                                                                                                                                                                                       | not Empty - c |          |      |           |                               |

| 4      | REN1       | This bit enables<br>receive FIFO.<br>0: UART1 recept                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Receive Enable.</b><br>This bit enables/disables the UART receiver. When disabled, bytes can still be read from the receive FIFO.<br>0: UART1 reception disabled.<br>1: UART1 reception enabled. |               |          |      |           |                               |

| 3      | TBX1       | The logic level of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>Extra Transmission Bit.</b><br>The logic level of this bit will be assigned to the extra transmission bit when XBE1 = 1. This bit is not used when Parity is enabled.                            |               |          |      |           |                               |

| 2      | RBX1       | Extra Receive Bit.<br>RBX1 is assigned the value of the extra bit when XBE1 = 1. If XBE1 is cleared to 0, RBX1<br>assigned the logic level of the first stop bit. This bit is not valid when Parity is enabled.                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                     |               |          |      |           |                               |

| 1      | TI1        | <b>Transmit Interrupt Flag.</b><br>Set to a 1 by hardware after data has been transmitted at the beginning of the STOP bit. When the UART1 interrupt is enabled, setting this bit causes the CPU to vector to the UART1 interrupt service routine. This bit must be cleared manually by software.                                                                                                                                                                                                  |                                                                                                                                                                                                     |               |          |      |           |                               |

| 0      | RI1        | Receive Interrupt Flag.<br>Set to 1 by hardware when a byte of data has been received by UART1 (set at the STOP bit sam<br>pling time). When the UART1 interrupt is enabled, setting this bit to 1 causes the CPU to vector<br>to the UART1 interrupt service routine. This bit must be cleared manually by software. Note that<br>RI1 will remain set to '1' as long as there is still data in the UART FIFO. After the last byte has<br>been shifted from the FIFO to SBUF1, RI1 can be cleared. |                                                                                                                                                                                                     |               |          |      |           | PU to vector<br>re. Note that |

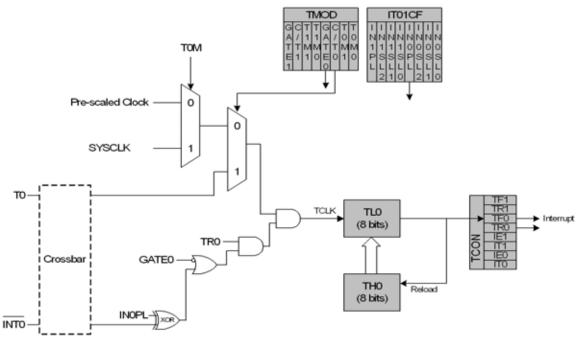

Figure 25.2. T0 Mode 2 Block Diagram

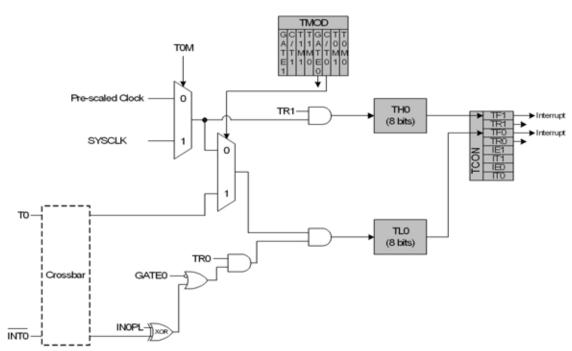

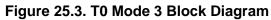

### 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates or overflow conditions for other peripherals. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

## SFR Definition 25.4. TMOD: Timer Mode

| Bit   | 7            | 6                                                                                                                                                                           | 5             | 4             | 3                   | 2             | 1              | 0            |

|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------------|---------------|----------------|--------------|