E·XFI

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                        |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 48 MIPS                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 2.25К х 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                    |

| Data Converters            | A/D 21x10b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-VFQFN Exposed Pad                                            |

| Supplier Device Package    | -                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f38b-gmr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 23.1. Baud Rate Generator                               |     |

|-----|---------------------------------------------------------|-----|

|     | 23.2. Data Format                                       |     |

|     | 23.3. Configuration and Operation                       |     |

|     | 23.3.1. Data Transmission                               | 204 |

|     | 23.3.2. Data Reception                                  |     |

|     | 23.3.3. Multiprocessor Communications                   |     |

| 24. | Enhanced Serial Peripheral Interface (SPI0)             | 211 |

|     | 24.1. Signal Descriptions                               |     |

|     | 24.1.1. Master Out, Slave In (MOSI)                     | 212 |

|     | 24.1.2. Master In, Slave Out (MISO)                     | 212 |

|     | 24.1.3. Serial Clock (SCK)                              |     |

|     | 24.1.4. Slave Select (NSS)                              | 212 |

|     | 24.2. SPI0 Master Mode Operation                        | 212 |

|     | 24.3. SPI0 Slave Mode Operation                         |     |

|     | 24.4. SPI0 Interrupt Sources                            |     |

|     | 24.5. Serial Clock Phase and Polarity                   |     |

|     | 24.6. SPI Special Function Registers                    |     |

| 25. | Timers                                                  |     |

|     | 25.1. Timer 0 and Timer 1                               | 227 |

|     | 25.1.1. Mode 0: 13-bit Counter/Timer                    |     |

|     | 25.1.2. Mode 1: 16-bit Counter/Timer                    |     |

|     | 25.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload    |     |

|     | 25.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) |     |

|     | 25.2. Timer 2                                           |     |

|     | 25.2.1. 16-bit Timer with Auto-Reload                   |     |

|     | 25.2.2. 8-bit Timers with Auto-Reload                   |     |

|     | 25.2.3. Timer 2 Capture Modes: LFO Falling Edge         |     |

|     | 25.3. Timer 3                                           |     |

|     | 25.3.1. 16-bit Timer with Auto-Reload                   |     |

|     | 25.3.2. 8-bit Timers with Auto-Reload                   |     |

|     | 25.3.3. Timer 3 Capture Modes: LFO Falling Edge         |     |

|     | 25.3.3. Timer 3 Capture Modes. LFO Failing Edge         |     |

|     | 25.4.1. 16-bit Timer with Auto-Reload                   |     |

|     | 25.4.2. 8-bit Timers with Auto-Reload                   |     |

|     |                                                         |     |

|     | 25.5. Timer 5<br>25.5.1. 16-bit Timer with Auto-Reload  |     |

|     |                                                         |     |

| ~~  | 25.5.2. 8-bit Timers with Auto-Reload                   |     |

| 26. | Programmable Counter Array                              |     |

|     | 26.1. PCA Counter/Timer                                 |     |

|     | 26.2. PCA0 Interrupt Sources                            |     |

|     | 26.3. Capture/Compare Modules                           |     |

|     | 26.3.1. Edge-triggered Capture Mode                     |     |

|     | 26.3.2. Software Timer (Compare) Mode                   |     |

|     | 26.3.3. High-Speed Output Mode                          |     |

|     | 26.3.4. Frequency Output Mode                           | 266 |

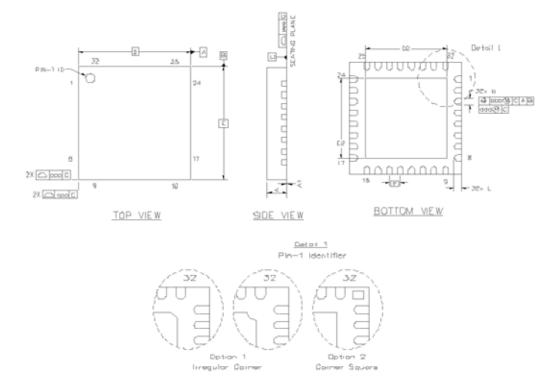

| Table 3.6. | <b>QFN-32</b> | Package  | Dimensions  |

|------------|---------------|----------|-------------|

|            |               | I uonugo | Difficition |

| Dimension | Min      | Тур      | Max  |   | Dimension | Min  | Тур  | Max  |

|-----------|----------|----------|------|---|-----------|------|------|------|

| A         | 0.80     | 0.85     | 0.90 |   | E2        | 3.20 | 3.30 | 3.40 |

| A1        | 0.00     | 0.02     | 0.05 | ĺ | L         | 0.35 | 0.40 | 0.45 |

| b         | 0.18     | 0.25     | 0.30 |   | aaa       | _    | _    | 0.10 |

| D         |          | 5.00 BSC |      |   | bbb       | _    |      | 0.10 |

| D2        | 3.20     | 3.30     | 3.40 |   | ddd       | _    |      | 0.05 |

| е         | 0.50 BSC |          |      |   | eee       | _    | _    | 0.08 |

| E         |          | 5.00 BSC |      |   |           |      |      |      |

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, and L which are toleranced per supplier designation.

- **4.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### Table 5.3. Port I/O DC Electrical Characteristics

$V_{DD}$  = 2.7 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameter                            | Test Condition                               | Min                   | Тур                   | Max | Unit |

|--------------------------------------|----------------------------------------------|-----------------------|-----------------------|-----|------|

| Output High Voltage                  | I <sub>OH</sub> = −3 mA, Port I/O push-pull  | V <sub>DD</sub> – 0.7 | _                     |     | V    |

|                                      | I <sub>OH</sub> = −10 μA, Port I/O push-pull | V <sub>DD</sub> – 0.1 | —                     | —   |      |

|                                      | I <sub>OH</sub> = −10 mA, Port I/O push-pull | —                     | V <sub>DD</sub> – 0.8 | —   |      |

| Output Low Voltage                   | I <sub>OL</sub> = 8.5 mA                     | —                     | _                     | 0.6 | V    |

|                                      | I <sub>OL</sub> = 10 μA                      |                       | —                     | 0.1 |      |

|                                      | I <sub>OL</sub> = 25 mA                      | -                     | 1.0                   | —   |      |

| Input High Voltage                   |                                              | 2.0                   | _                     |     | V    |

| Input Low Voltage                    |                                              | —                     | —                     | 0.8 | V    |

| Input Leakage                        | Weak Pullup Off                              | _                     | _                     | ±1  | μA   |

| Current                              | Weak Pullup On, V <sub>IN</sub> = 0 V        | -                     | 15                    | 50  |      |

| INT2 Detection Input                 |                                              | _                     |                       | 1.0 | V    |

| Low Voltage                          |                                              |                       |                       | 1.0 |      |

| INT2 Detection Input<br>High Voltage |                                              | 3.0                   | _                     |     | V    |

### **Table 5.4. Reset Electrical Characteristics**

-40 to +85 °C unless otherwise specified.

| Parameter                                                    | Test Condition                                                                        | Min                         | Тур  | Max                   | Unit |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|------|-----------------------|------|

| RST Output Low Voltage                                       | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 2.7 V to 3.6 V                         |                             |      | 0.6                   | V    |

| RST Input High Voltage                                       |                                                                                       | $0.7 	ext{ x V}_{	ext{DD}}$ |      |                       | V    |

| RST Input Low Voltage                                        |                                                                                       |                             | —    | 0.3 x V <sub>DD</sub> | V    |

| RST Input Pullup Current                                     | <del>RST</del> = 0.0 V                                                                |                             | 15   | 40                    | μA   |

| $V_{DD}$ Monitor Threshold ( $V_{RST}$ )                     |                                                                                       | 2.60                        | 2.65 | 2.70                  | V    |

| Missing Clock Detector Time-<br>out                          | Time from last system clock rising edge to reset initiation                           | 80                          | 580  | 800                   | μs   |

| Reset Time Delay                                             | Delay between release of any<br>reset source and code<br>execution at location 0x0000 | _                           |      | 250                   | μs   |

| Minimum $\overline{RST}$ Low Time to Generate a System Reset |                                                                                       | 15                          |      | —                     | μs   |

| V <sub>DD</sub> Monitor Turn-on Time                         |                                                                                       |                             | —    | 100                   | μs   |

| V <sub>DD</sub> Monitor Supply Current                       |                                                                                       |                             | 15   | 50                    | μA   |

## Table 5.11. Temperature Sensor Electrical Characteristics

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter                                              | Test Condition | Min | Тур   | Max | Unit  |  |  |  |  |

|--------------------------------------------------------|----------------|-----|-------|-----|-------|--|--|--|--|

| Linearity                                              |                | _   | ± 0.5 | _   | °C    |  |  |  |  |

| Slope                                                  |                | —   | 2.87  | _   | mV/°C |  |  |  |  |

| Slope Error*                                           |                | _   | ±120  | _   | µV/°C |  |  |  |  |

| Offset                                                 | Temp = 0 °C    | —   | 764   | _   | mV    |  |  |  |  |

| Offset Error*                                          | Temp = 0 °C    | —   | ±15   | _   | mV    |  |  |  |  |

| Note: Represents one standard deviation from the mean. |                |     |       |     |       |  |  |  |  |

### Table 5.12. Voltage Reference Electrical Characteristics

$V_{DD}$  = 3.0 V; -40 to +85 °C unless otherwise specified.

| Parameter                       | Test Condition                         | Min  | Тур  | Max             | Unit   |

|---------------------------------|----------------------------------------|------|------|-----------------|--------|

| Internal Reference (REFBE       | = 1)                                   |      |      | 1               | 1      |

| Output Voltage                  | 25 °C ambient                          | 2.38 | 2.42 | 2.46            | V      |

| VREF Short-Circuit Current      |                                        |      | _    | 8               | mA     |

| VREF Temperature<br>Coefficient |                                        |      | 35   | _               | ppm/°C |

| Load Regulation                 | Load = 0 to 200 µA to GND              |      | 1.5  |                 | ppm/µA |

| VREF Turn-on Time 1             | 4.7 μF tantalum, 0.1 μF ceramic bypass |      | 3    |                 | ms     |

| VREF Turn-on Time 2             | 0.1 µF ceramic bypass                  |      | 100  |                 | μs     |

| Power Supply Rejection          |                                        |      | 140  |                 | ppm/V  |

| External Reference (REFBI       | Ξ = 0)                                 |      |      |                 |        |

| Input Voltage Range             |                                        | 1    | _    | V <sub>DD</sub> | V      |

| Input Current                   | Sample Rate = 500 ksps; VREF = 3.0 V   |      | 9    |                 | μA     |

| Power Specifications            | •                                      |      |      |                 |        |

| Supply Current                  |                                        |      | 75   | _               | μA     |

### **Table 5.13. Comparator Electrical Characteristics**

$V_{DD}$  = 3.0 V, -40 to +85 °C unless otherwise noted.

| Parameter                                         | Test Condition        | Min   | Тур   | Max                    | Unit |

|---------------------------------------------------|-----------------------|-------|-------|------------------------|------|

| Response Time:                                    | CP0+ - CP0- = 100 mV  | _     | 100   |                        | ns   |

| Mode 0, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV | _     | 250   |                        | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | _     | 175   | _                      | ns   |

| Mode 1, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV | _     | 500   |                        | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | _     | 320   |                        | ns   |

| Mode 2, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV | _     | 1100  | _                      | ns   |

| Response Time:                                    | CP0+ - CP0- = 100 mV  | _     | 1050  |                        | ns   |

| Mode 3, Vcm <sup>*</sup> = 1.5 V                  | CP0+ - CP0- = -100 mV | _     | 5200  |                        | ns   |

| Common-Mode Rejection Ratio                       |                       | _     | 1.5   | 4                      | mV/V |

| Positive Hysteresis 1                             | CP0HYP1-0 = 00        | _     | 0     | 1                      | mV   |

| Positive Hysteresis 2                             | CP0HYP1-0 = 01        | 2     | 5     | 10                     | mV   |

| Positive Hysteresis 3                             | CP0HYP1-0 = 10        | 7     | 10    | 20                     | mV   |

| Positive Hysteresis 4                             | CP0HYP1-0 = 11        | 15    | 20    | 30                     | mV   |

| Negative Hysteresis 1                             | CP0HYN1-0 = 00        | _     | 0     | 1                      | mV   |

| Negative Hysteresis 2                             | CP0HYN1-0 = 01        | 2     | 5     | 10                     | mV   |

| Negative Hysteresis 3                             | CP0HYN1-0 = 10        | 7     | 10    | 20                     | mV   |

| Negative Hysteresis 4                             | CP0HYN1-0 = 11        | 15    | 20    | 30                     | mV   |

| Inverting or Non-Inverting Input<br>Voltage Range |                       | -0.25 |       | V <sub>DD</sub> + 0.25 | V    |

| Input Capacitance                                 |                       | _     | 4     |                        | pF   |

| Input Bias Current                                |                       | —     | 0.001 |                        | nA   |

| Input Offset Voltage                              |                       | -10   |       | +10                    | mV   |

| Power Supply                                      |                       |       |       | •                      |      |

| Power Supply Rejection                            |                       | _     | 0.1   |                        | mV/V |

| Power-up Time                                     |                       | —     | 10    |                        | μs   |

| Supply Current at DC                              | Mode 0                | _     | 20    |                        | μA   |

|                                                   | Mode 1                | —     | 10    |                        | μA   |

|                                                   | Mode 2                | —     | 4     | _                      | μA   |

|                                                   | Mode 3                | _     | 1     | —                      | μA   |

| Note: Vcm is the common-mode vol                  | tage on CP0+ and CP0  |       |       |                        |      |

## SFR Definition 6.7. ADC0LTH: ADC0 Less-Than Data High Byte

| Bit   | 7              | 6                                                    | 5             | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|----------------|------------------------------------------------------|---------------|---|---|---|---|---|--|--|--|

| Nam   | e              | ADC0LTH[7:0]                                         |               |   |   |   |   |   |  |  |  |

| Туре  | 9              | R/W                                                  |               |   |   |   |   |   |  |  |  |

| Rese  | et O           | 0                                                    | 0 0 0 0 0 0 0 |   |   |   |   |   |  |  |  |

| SFR A | Address = 0xC6 | ; SFR Page                                           | e = All Pages |   |   |   |   |   |  |  |  |

| Bit   | Name           | Name Function                                        |               |   |   |   |   |   |  |  |  |

| 7:0   | ADC0LTH[7:0    | C0LTH[7:0] ADC0 Less-Than Data Word High-Order Bits. |               |   |   |   |   |   |  |  |  |

## SFR Definition 6.8. ADC0LTL: ADC0 Less-Than Data Low Byte

| Bit   | 7              | 6                                                   | 5             | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|----------------|-----------------------------------------------------|---------------|---|---|---|---|---|--|--|

| Nam   | e              | ADC0LTL[7:0]                                        |               |   |   |   |   |   |  |  |

| Туре  | 9              | R/W                                                 |               |   |   |   |   |   |  |  |

| Rese  | et 0           | 0                                                   | 0             | 0 | 0 | 0 | 0 | 0 |  |  |

| SFR A | Address = 0xC5 | ; SFR Page                                          | e = All Pages | 5 |   |   |   |   |  |  |

| Bit   | Name           | Name Function                                       |               |   |   |   |   |   |  |  |

| 7:0   | ADC0LTL[7:0    | C0LTL[7:0] ADC0 Less-Than Data Word Low-Order Bits. |               |   |   |   |   |   |  |  |

## SFR Definition 8.2. CPT0MD: Comparator0 Mode Selection

| Bit   | 7 | 6 | 5             | 4      | 3 | 2 | 1          | 0 |

|-------|---|---|---------------|--------|---|---|------------|---|

| Name  |   |   | <b>CP0RIE</b> | CP0FIE |   |   | CP0MD[1:0] |   |

| Туре  | R | R | R/W           | R/W    | R | R | R/W        |   |

| Reset | 0 | 0 | 0             | 0      | 0 | 0 | 1          | 0 |

### SFR Address = 0x9D; SFR Page = All Pages

| Bit | Name       | Function                                                                                                                                                                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 5   | CPORIE     | Comparator0 Rising-Edge Interrupt Enable.<br>0: Comparator0 Rising-edge interrupt disabled.<br>1: Comparator0 Rising-edge interrupt enabled.                                                                                                                        |

| 4   | CP0FIE     | Comparator0 Falling-Edge Interrupt Enable.<br>0: Comparator0 Falling-edge interrupt disabled.<br>1: Comparator0 Falling-edge interrupt enabled.                                                                                                                     |

| 3:2 | Unused     | Read = 00b, Write = don't care.                                                                                                                                                                                                                                     |

| 1:0 | CP0MD[1:0] | Comparator0 Mode Select.<br>These bits affect the response time and power consumption for Comparator0.<br>00: Mode 0 (Fastest Response Time, Highest Power Consumption)<br>01: Mode 1<br>10: Mode 2<br>11: Mode 3 (Slowest Response Time, Lowest Power Consumption) |

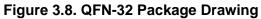

## 14.5. Memory Mode Selection

The external data memory space can be configured in one of four modes, shown in Figure 14.3, based on the EMIF Mode bits in the EMIOCF register (SFR Definition 14.4). These modes are summarized below. More information about the different modes can be found in Section "14.6. Timing" on page 96.

Figure 14.3. EMIF Operating Modes

#### 14.5.1. Internal XRAM Only

When EMI0CF.[3:2] are set to 00, all MOVX instructions will target the internal XRAM space on the device. Memory accesses to addresses beyond the populated space will wrap on 2k or 4k boundaries (depending on the RAM available on the device). As an example, the addresses 0x1000 and 0x2000 both evaluate to address 0x0000 in on-chip XRAM space.

- 8-bit MOVX operations use the contents of EMI0CN to determine the high-byte of the effective address and R0 or R1 to determine the low-byte of the effective address.

- 16-bit MOVX operations use the contents of the 16-bit DPTR to determine the effective address.

#### 14.5.2. Split Mode without Bank Select

When EMI0CF.[3:2] are set to 01, the XRAM memory map is split into two areas, on-chip space and off-chip space.

- Effective addresses below the internal XRAM size boundary will access on-chip XRAM space.

- Effective addresses above the internal XRAM size boundary will access off-chip space.

- 8-bit MOVX operations use the contents of EMI0CN to determine whether the memory access is on-chip or off-chip. However, in the "No Bank Select" mode, an 8-bit MOVX operation will not drive the upper 8-bits A[15:8] of the Address Bus during an off-chip access. This allows the user to manipulate the upper address bits at will by setting the Port state directly via the port latches. This behavior is in contrast with "Split Mode with Bank Select" described below. The lower 8-bits of the Address Bus A[7:0] are driven, determined by R0 or R1.

- 16-bit MOVX operations use the contents of DPTR to determine whether the memory access is on-chip or off-chip, and unlike 8-bit MOVX operations, the full 16-bits of the Address Bus A[15:0] are driven during the off-chip transaction.

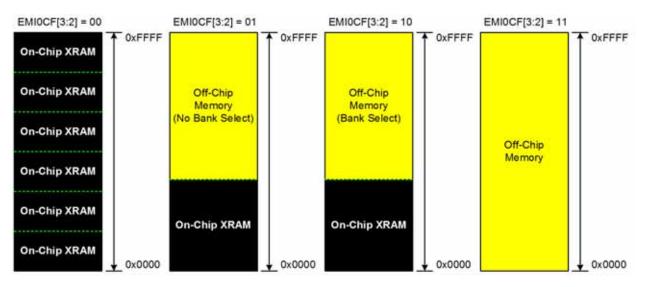

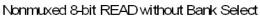

### 14.6.1.2. 8-bit MOVX without Bank Select: EMI0CF[4:2] = 101 or 111

Nonmuxed 8-bit WRITE without Bank Select

## Table 15.2. Special Function Registers (Continued)

| SFRs are liste | ed in alpha | betical order | r. All undefined SFR locations are reserved |

|----------------|-------------|---------------|---------------------------------------------|

|                |             |               |                                             |

| Register | Address | Page      | Description                     | Page |

|----------|---------|-----------|---------------------------------|------|

| TMR5RLL  | 0xCA    | F         | Timer/Counter 5 Reload Low      | 257  |

| VDM0CN   | 0xFF    | All Pages | V <sub>DD</sub> Monitor Control | 126  |

| XBR0     | 0xE1    | All Pages | Port I/O Crossbar Control 0     | 153  |

| XBR1     | 0xE2    | All Pages | Port I/O Crossbar Control 1     | 154  |

| XBR2     | 0xE3    | All Pages | Port I/O Crossbar Control 2     | 155  |

#### 19.5.2. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 19.1, "RC Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation, according to Equation 19.1, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and R = the pull-up resistor value in k $\Omega$ .

$$f = 1.23 \times 10^3 \S (R \times C)$$

### Equation 19.1. RC Mode Oscillator Frequency

For example: If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

f = 1.23(10<sup>3</sup>) / RC = 1.23(10<sup>3</sup>) / [246 x 50] = 0.1 MHz = 100 kHz

Referring to the table in SFR Definition 19.6, the required XFCN setting is 010b.

#### 19.5.3. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 19.1, "C Mode". The capacitor should be no greater than 100 pF; however, for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation according to Equation 19.2, where f = the frequency of oscillation in MHz, C = the capacitor value in pF, and V<sub>DD</sub> = the MCU power supply in Volts.

$$f = (KF)/(C \times V_{DD})$$

#### Equation 19.2. C Mode Oscillator Frequency

For example: Assume  $V_{DD}$  = 3.0 V and f = 150 kHz:

f = KF / (C x VDD) 0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 19.6 (OSCXCN) as KF = 22:

0.150 MHz = 22 / (C x 3.0) C x 3.0 = 22 / 0.150 MHz C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

## SFR Definition 20.18. P3MDOUT: Port 3 Output Mode

| Bit   | 7            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|-----|---|---|---|---|---|---|--|

| Name  | P3MDOUT[7:0] |     |   |   |   |   |   |   |  |

| Туре  |              | R/W |   |   |   |   |   |   |  |

| Reset | 0            | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xA7; SFR Page = All Pages

| Bit | Name         | Function                                                                                                                                                                    |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P3MDOUT[7:0] | Output Configuration Bits for P3.7–P3.0 (respectively).                                                                                                                     |

|     |              | These bits are ignored if the corresponding bit in register P3MDIN is logic 0.<br>0: Corresponding P3.n Output is open-drain.<br>1: Corresponding P3.n Output is push-pull. |

## SFR Definition 20.19. P3SKIP: Port 3 Skip

| Bit   | 7           | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------|-----|---|---|---|---|---|---|--|

| Name  | P3SKIP[7:0] |     |   |   |   |   |   |   |  |

| Туре  |             | R/W |   |   |   |   |   |   |  |

| Reset | 0           | 0   | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0xDF; SFR Page = All Pages

| Bit | Name        | Function                                                                                                                                                                                                                                                                                                           |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | P3SKIP[3:0] | Port 3 Crossbar Skip Enable Bits.                                                                                                                                                                                                                                                                                  |

|     |             | <ul> <li>These bits select Port 3 pins to be skipped by the Crossbar Decoder. Port pins used for analog, special functions or GPIO should be skipped by the Crossbar.</li> <li>0: Corresponding P3.n pin is not skipped by the Crossbar.</li> <li>1: Corresponding P3.n pin is skipped by the Crossbar.</li> </ul> |

## SFR Definition 21.7. SMB0ADM: SMBus0 Slave Address Mask

| Bit   | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|-----|---|---|---|---|---|---|--|

| Name  | SLVM0[6:0] |     |   |   |   |   |   |   |  |

| Туре  |            | R/W |   |   |   |   |   |   |  |

| Reset | 1          | 1   | 1 | 1 | 1 | 1 | 1 | 0 |  |

#### SFR Address = 0xCE; SFR Page = 0

| Bit | Name       | Function                                                                                                                                                                                                                                                                             |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLVM0[6:0] | SMBus0 Slave Address Mask.                                                                                                                                                                                                                                                           |

|     |            | Defines which bits of register SMB0ADR are compared with an incoming address byte, and which bits are ignored. Any bit set to 1 in SLVM0[6:0] enables comparisons with the corresponding bit in SLV0[6:0]. Bits set to 0 are ignored (can be either 0 or 1 in the incoming address). |

| 0   | EHACK0     | Hardware Acknowledge Enable.                                                                                                                                                                                                                                                         |

|     |            | <ul><li>Enables hardware acknowledgement of slave address and received data bytes.</li><li>0: Firmware must manually acknowledge all incoming address and data bytes.</li><li>1: Automatic Slave Address Recognition and Hardware Acknowledge is Enabled.</li></ul>                  |

## SFR Definition 21.8. SMB1ADR: SMBus1 Slave Address

| Bit   | 7         | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----------|-----|---|---|---|---|---|---|

| Name  | SLV1[6:0] |     |   |   |   |   |   |   |

| Туре  |           | R/W |   |   |   |   |   |   |

| Reset | 0         | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

#### SFR Address = 0xCF; SFR Page = F

| Bit | Name      | Function                                                                                                                                                                                                                                                                    |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1 | SLV1[6:0] | SMBus1 Hardware Slave Address.                                                                                                                                                                                                                                              |

|     |           | Defines the SMBus1 Slave Address(es) for automatic hardware acknowledgment.<br>Only address bits which have a 1 in the corresponding bit position in SLVM1[6:0] are checked against the incoming address. This allows multiple addresses to be recognized.                  |

| 0   | GC1       | General Call Address Enable.                                                                                                                                                                                                                                                |

|     |           | <ul> <li>When hardware address recognition is enabled (EHACK1 = 1), this bit will determine whether the General Call Address (0x00) is also recognized by hardware.</li> <li>0: General Call Address is ignored.</li> <li>1: General Call Address is recognized.</li> </ul> |

| Table 21.5. SMBus Status Decoding: Hardware ACK Disabled (EHACK = 0) (Contin | ued) |

|------------------------------------------------------------------------------|------|

|------------------------------------------------------------------------------|------|

|                   | Valu             | es l  | Rea                                                                                                                                 | d                                                          |                                                                                             |                                                            | Values to<br>Write |      |     | tus<br>ected                   |

|-------------------|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------|------|-----|--------------------------------|

| Mode              | Status<br>Vector | ACKRQ | ARBLOST                                                                                                                             | ACK                                                        | Current SMbus State                                                                         | Typical Response Options                                   | STA                | STO  | ACK | Next Status<br>Vector Expected |

| r                 |                  | 0     | 0                                                                                                                                   | 0                                                          | A slave byte was transmitted;<br>NACK received.                                             | No action required (expecting STOP condition).             | 0                  | 0    | Х   | 0001                           |

| smitte            | 0100             | 0     | 0                                                                                                                                   | 1                                                          | A slave byte was transmitted;<br>ACK received.                                              | Load SMB0DAT with next data byte to transmit.              | 0                  | 0    | Х   | 0100                           |

| Slave Transmitter |                  | 0     | 1                                                                                                                                   | x                                                          | A Slave byte was transmitted;<br>error detected.                                            | No action required (expecting Master to end transfer).     | 0                  | 0    | Х   | 0001                           |

| Slav              | 0101             | 0     | x                                                                                                                                   | x                                                          | An illegal STOP or bus error<br>was detected while a Slave<br>Transmission was in progress. | Clear STO.                                                 | 0                  | 0    | Х   | _                              |

|                   |                  | 1     |                                                                                                                                     |                                                            | A slave address + R/W was<br>received; ACK requested.                                       | If Write, Acknowledge received address                     | 0                  | 0    | 1   | 0000                           |

|                   |                  |       | 0                                                                                                                                   | X                                                          |                                                                                             | If Read, Load SMB0DAT with data byte; ACK received address | 0                  | 0    | 1   | 0100                           |

|                   |                  |       |                                                                                                                                     |                                                            |                                                                                             | NACK received address.                                     | 0                  | 0    | 0   |                                |

|                   | 0010             |       |                                                                                                                                     |                                                            |                                                                                             | If Write, Acknowledge received address                     | 0                  | 0    | 1   | 0000                           |

| iver              |                  | 1     | Lost arbitration as master;<br>1 1 X slave address + R/W received;<br>If Read, Load SMB0DAT with<br>data byte; ACK received address | If Read, Load SMB0DAT with data byte; ACK received address | 0                                                                                           | 0                                                          | 1                  | 0100 |     |                                |

| ece               |                  |       |                                                                                                                                     |                                                            | ACK requested.                                                                              | NACK received address.                                     | 0                  | 0    | 0   | —                              |

| Slave Receiver    |                  |       |                                                                                                                                     |                                                            |                                                                                             | Reschedule failed transfer;<br>NACK received address.      | 1                  | 0    | 0   | 1110                           |

|                   | 0001             | 0     | 0                                                                                                                                   | x                                                          | A STOP was detected while<br>addressed as a Slave Trans-<br>mitter or Slave Receiver.       | Clear STO.                                                 | 0                  | 0    | Х   | _                              |

|                   |                  | 1     | 1                                                                                                                                   | x                                                          | Lost arbitration while attempt-<br>ing a STOP.                                              | No action required (transfer complete/aborted).            | 0                  | 0    | 0   | —                              |

|                   | 0000             | 1     | 0                                                                                                                                   | x                                                          | A slave byte was received;<br>ACK requested.                                                | Acknowledge received byte;<br>Read SMB0DAT.                | 0                  | 0    | 1   | 0000                           |

|                   |                  |       |                                                                                                                                     |                                                            |                                                                                             | NACK received byte.                                        | 0                  | 0    | 0   | _                              |

| Table 22.1. Timer Settings for Standard Baud Rates Using Internal Oscillator |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

|    | Target<br>Baud<br>Rate (bps)                                                 | Actual<br>Baud<br>Rate (bps) | Baud<br>Rate<br>Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale<br>select* | T1M | Timer 1<br>Reload<br>Value (hex) |  |

|----|------------------------------------------------------------------------------|------------------------------|-----------------------|--------------------------------|-----------------------|------------------------------------|-----|----------------------------------|--|

| No | <b>Note:</b> SCA1-SCA0 and T1M define the Timer Clock Source. X = Don't care |                              |                       |                                |                       |                                    |     |                                  |  |

1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

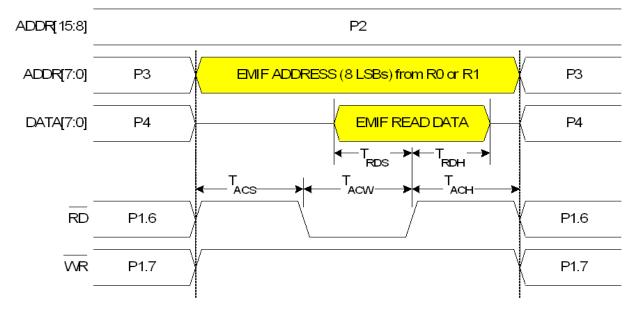

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 24.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used, and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 24.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin, and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 24.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

Figure 24.2. Multiple-Master Mode Connection Diagram

Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram

## SFR Definition 25.13. TMR2H Timer 2 High Byte

| Bit                              | 7             | 6                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|----------------------------------|---------------|------------------|---|---|---|---|---|---|--|--|--|--|

| Nam                              | e             | TMR2H[7:0]       |   |   |   |   |   |   |  |  |  |  |

| Туре                             | 9             | R/W              |   |   |   |   |   |   |  |  |  |  |

| Rese                             | et 0          | 0                | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

| SFR Address = 0xCD; SFR Page = 0 |               |                  |   |   |   |   |   |   |  |  |  |  |

| Bit                              | Name Function |                  |   |   |   |   |   |   |  |  |  |  |

| 7.0                              | TMR2H[7·0]    | Timer 2 Low Byte |   |   |   |   |   |   |  |  |  |  |

| ĺ | 7:0 | TMR2H[7:0] | Timer 2 Low Byte.                                                                     |

|---|-----|------------|---------------------------------------------------------------------------------------|

|   |     |            | In 16-bit mode, the TMR2H register contains the high byte of the 16-bit Timer 2. In 8 |

|   |     |            | bit mode, TMR2H contains the 8-bit high byte timer value.                             |

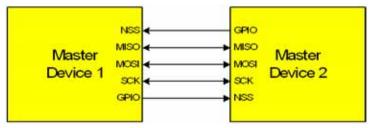

## 25.3. Timer 3

Timer 3 is a 16-bit timer formed by two 8-bit SFRs: TMR3L (low byte) and TMR3H (high byte). Timer 3 may operate in 16-bit auto-reload mode, (split) 8-bit auto-reload mode, or Low-Frequency Oscillator (LFO) Rising Edge capture mode. The Timer 3 operation mode is defined by the T3SPLIT (TMR3CN.3), T3CE (TMR3CN.4) bits, and T3CSS (TMR3CN.1) bits.

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the internal oscillator drives the system clock while Timer 3 (and/or the PCA) is clocked by an external precision oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

#### 25.3.1. 16-bit Timer with Auto-Reload

When T3SPLIT (TMR3CN.3) is zero, Timer 3 operates as a 16-bit timer with auto-reload. Timer 3 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 3 reload registers (TMR3RLH and TMR3RLL) is loaded into the Timer 3 register as shown in Figure 25.8, and the Timer 3 High Byte Overflow Flag (TMR3CN.7) is set. If Timer 3 interrupts are enabled (if EIE1.7 is set), an interrupt will be generated on each Timer 3 overflow. Additionally, if Timer 3 interrupts are enabled and the TF3LEN bit is set (TMR3CN.5), an interrupt will be generated each time the lower 8 bits (TMR3L) overflow from 0xFF to 0x00.

Figure 25.8. Timer 3 16-Bit Mode Block Diagram

## SFR Definition 25.23. TMR4H Timer 4 High Byte

| Bit                              | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------|-----|------------|---|---|---|---|---|---|

| Name                             |     | TMR4H[7:0] |   |   |   |   |   |   |

| Туре                             | R/W |            |   |   |   |   |   |   |

| Reset                            | 0   | 0          | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0x95; SFR Page = F |     |            |   |   |   |   |   |   |

| Bit | Name       | Function                                                                                                                                        |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | TMR4H[7:0] | Timer 4 High Byte.                                                                                                                              |

|     |            | In 16-bit mode, the TMR4H register contains the high byte of the 16-bit Timer 4. In 8-bit mode, TMR4H contains the 8-bit high byte timer value. |

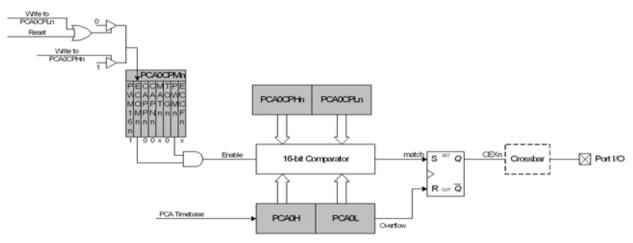

#### 26.3.6. 16-Bit Pulse Width Modulator Mode

A PCA module may also be operated in 16-Bit PWM mode. In this mode, the 16-bit capture/compare module defines the number of PCA clocks for the low time of the PWM signal. When the PCA counter matches the module contents, the output on CEXn is asserted high; when the 16-bit counter overflows, CEXn is asserted low. To output a varying duty cycle, new value writes should be synchronized with PCA CCFn match interrupts. 16-Bit PWM Mode is enabled by setting the ECOMn, PWMn, and PWM16n bits in the PCA0CPMn register. For a varying duty cycle, match interrupts should be enabled (ECCFn = 1 AND MATn = 1) to help synchronize the capture/compare register writes. If the MATn bit is set to 1, the CCFn flag for the module will be set each time a 16-bit comparator match (rising edge) occurs. The CF flag in PCA0CN can be used to detect the overflow (falling edge). The duty cycle for 16-Bit PWM Mode is given by Equation 26.3.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

#### Equation 26.3. 16-Bit PWM Duty Cycle

Using Equation 26.3, the largest duty cycle is 100% (PCA0CPn = 0), and the smallest duty cycle is 0.0015% (PCA0CPn = 0xFFFF). A 0% duty cycle may be generated by clearing the ECOMn bit to 0.

Figure 26.9. PCA 16-Bit PWM Mode