Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 8MHz                                                   |

| Connectivity               | -                                                      |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 14                                                     |

| Program Memory Size        | 512B (512 x 8)                                         |

| Program Memory Type        | ОТР                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 60 x 8                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                              |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Through Hole                                           |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e0308psc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **PIN DESCRIPTION**

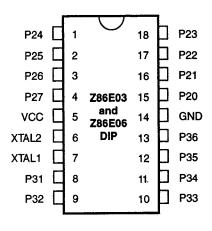

Table 1. 18-Pin DIP and SOIC Pin Identification

| No       | Symbol                    | Function                                | Direction    |

|----------|---------------------------|-----------------------------------------|--------------|

| 1-4<br>5 | P24-27<br>V <sub>20</sub> | Port 2, pins 4, 5, 6, 7<br>Power Supply | In/Output    |

| 6        | V <sub>cc</sub><br>XTAL2  | Crystal Oscillator Clock                | Output       |

| 7        | XTAL1                     | Crystal Oscillator Clock                | Input        |

| 8-10     | P31-33                    | Port 3, pins 1, 2, 3                    | Fixed Input  |

| 11-13    | P34-36                    | Port 3, pins 4, 5, 6                    | Fixed Output |

| 14       | GND                       | Ground                                  | •            |

| 15-18    | P20-23                    | Port 2, pins 0, 1, 2, 3                 | In/Output    |

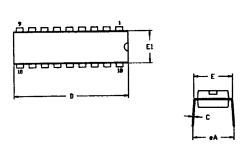

Figure 2. 18-Pin DIP Pin Configuration

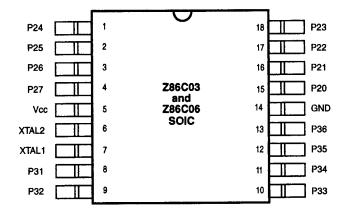

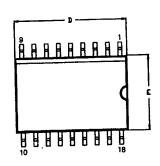

Figure 3. 18-Pin SOIC Pin Configuration

#### **PIN FUNCTIONS**

**XTAL1.** Crystal 1 (time-based input). This pin connects a parallel-resonant crystal, ceramic resonator, LC or RC network or an external single-phase clock to the on-chip oscillator input.

**XTAL2.** Crystal 2 (time-based output). This pin connects a parallel-resonant crystal, ceramic resonator, LC or RC network to the on-chip oscillator output.

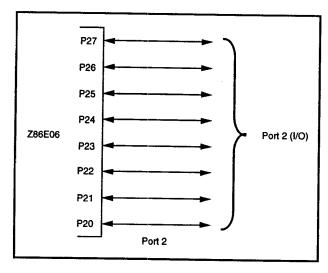

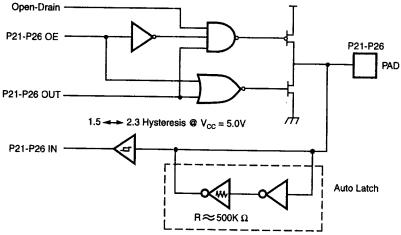

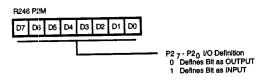

Port 2 (P27-P20). Port 2 is an 8-bit, bidirectional, CMOS compatible I/O port. These eight I/O lines can be configured under software control to be an input or output, independently. Input buffers are Schmitt-triggered and contain Auto Latches. Bits programmed as outputs may be globally programmed as either push-pull or open-drain (Figure 4a., 4b., and 4c.). Low EMI output buffers can be globally programmed by the software. In addition, when the SPI is enabled, P20 functions as data-in (DI), and P27 functions as data-out (DO) for the SPI (SPI on the Z86E06 only).

Figure 4a. Port 2 Configuration (Z86E06)

## **FUNCTIONAL DESCRIPTION (Continued)**

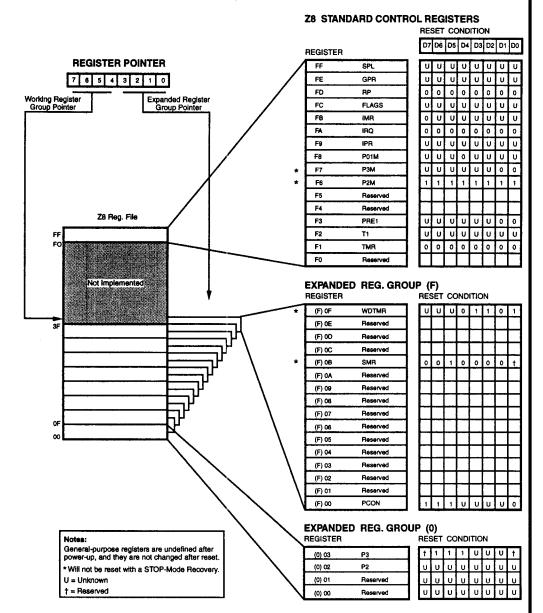

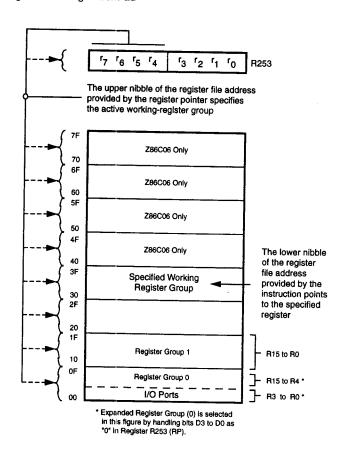

Figure 7a. Expanded Register File Architecture (Z86E03)

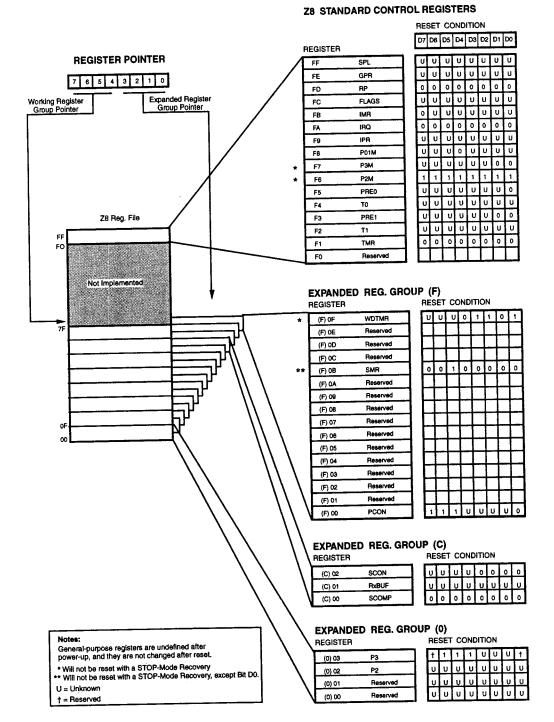

Figure 7b. Expanded Register File Architecture (Z86E06)

2-11

## **FUNCTIONAL DESCRIPTION (Continued)**

Note: Default Setting After Reset = 00000000

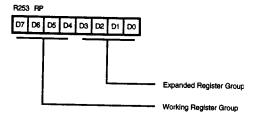

## Figure 8. Register Pointer Register

Register File. The Register File consists of two I/O port registers, 60/124 general-purpose registers, and 13/15 control and status registers. The Z86E03 General-Purpose Register file ranges from address 00 to 3F while the Z86E06 General-Purpose Register file ranges from ad-

dress 00 to 7F (see Figure 9). The instructions can access registers directly or indirectly via an 8-bit address field. This allows a short 4-bit register address using the Register Pointer (Figure 9). In the 4-bit mode, the Register File s divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working-register group.

**General-Purpose Registers (GPR).** These registers are undefined after the device is powered up. The registers keep their last value after any reset, as long as the reset occurs in the V<sub>CC</sub> voltage-specified operating range. **Note:** Register R254 has been designated as a general-purpose register.

**Stack.** An 8-bit Stack Pointer (R255) used for the internal stack that resides within the 60/124 general-purpose registers.

Figure 9. Register Pointer

Table 2. Interrupt Types, Sources, and Vectors

| Name  | Source                 | Vector Location | Comments                                        |  |  |

|-------|------------------------|-----------------|-------------------------------------------------|--|--|

| IRQ 0 | IRQ 0                  | 0, 1            | External (P32), Rising/Falling Edge Triggered   |  |  |

| IRQ 1 | IRQ 1                  | 2, 3            | External (P33), Falling Edge Triggered          |  |  |

| IRQ 2 | IRQ 2, T <sub>IN</sub> | 4,5             | External (P31), Rising/Falling Edge Triggered   |  |  |

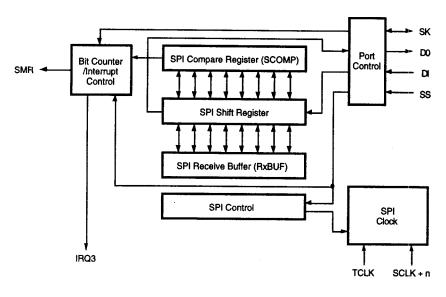

| IRQ 3 | IRQ 3                  | 6, 7            | Software Generated, SPI Receive                 |  |  |

| IRQ 4 | T0/IRQ 4               | 8, 9            | Internal for E06 and Software Generated for E03 |  |  |

| IRQ 5 | TI                     | 10, 11          | Internal                                        |  |  |

Note:

When enabled, the SPI receive interrupt is mapped to IRQ3 in the Z86E06.

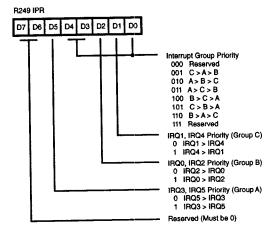

When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register. An interrupt machine cycle is activated when an interrupt request is granted. This disables all subsequent interrupts, saves the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. All Z86E03/E06 interrupts are vectored through locations in the program memory. This memory location and the next byte contain the 16-bit starting address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the interrupt request register is polled to determine which of the interrupt requests need service. In the Z86E06, when the SPI is disabled, IRQ3 has no hardware source but can be invoked by software (write to IRQ3 Register). When the SPI is enabled, an interrupt will be mapped to IRQ3 after a byte of data has been received by the SPI Shift Register.

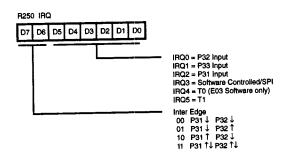

An interrupt resulting from AN1 is mapped into IRQ2, and an interrupt from AN2 is mapped into IRQ0. Interrupts IRQ2 and IRQ0 may be rising, falling, or both edge triggered, and are programmable by the user. The software can poll to identify the state of the pin.

The programming bits for the INTERRUPT EDGE SELECT are located in the IRQ register (R250), bits D7 and D6. The configuration is shown in Table 3.

Table 3. IRQ Register

| IR | Q | interru | pt Edge |

|----|---|---------|---------|

| D7 |   | P31     | P32     |

| 0  | 0 | F       | F       |

| ñ  | 1 | F       | R       |

| 1  | 0 | R       | F       |

| 1  | 1 | R/F     | R/F     |

Notes:

F = Falling Edge

R = Rising Edge

Figure 16. SPI Logic (Z86E06 Only)

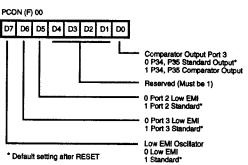

PORT Configuration Register (PCON). The PCON configures the ports individually for comparator output on Port 3, low EMI noise on Ports 2 and 3, and low EMI noise oscillator. The PCON Register is located in the Expanded Register File at bank F, location 00 (Figure 17).

Comparator Output Port 3 (D0). Bit 0 controls the comparator use in Port 3. A 1 in this location brings the comparator outputs to P34, and P35 and a 0 releases the Port to its standard I/O configuration.

Bits D4-D1. These bits are reserved and must be 1.

Low EMI Port 2 (D5). Port 2 is configured as a Low EMI Port by resetting this bit (D5=0) or configured as a Standard Port by setting D5=1. The default value is 1.

Low EMI Port 3 (D6). Port 3 is configured as a Low EMI Port by resetting this bit (D6=0) or configured as a Standard Port by setting D6=1. The default value is 1.

Low EMI OSC (D7). This bit of the PCON Register controls the low EMI noise oscillator. A 1 in this location configures the oscillator with standard drive. While a 0 configures the oscillator with low noise drive, it does not affect the relationship of SCLK and XTAL.

Figure 17. Port Configuration Register (PCON) (Write Only)

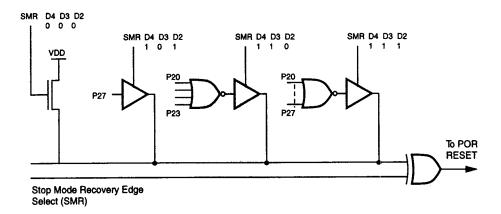

**STOP-Mode Recovery Source (D2,D3,D4).** These three bits of the SMR specify the wake-up source of the STOP-Mode Recovery (Figure 19 and Table 5).

Table 5. STOP-Mode Recovery Source

| • | D4 | SMR<br>D3 | D2 | Operation<br>Description of Action |

|---|----|-----------|----|------------------------------------|

| • | 0  | 0         | 0  | POR recovery only                  |

|   | 0  | 0         | 1  | POR recovery only (E03 = Reserved) |

|   | 0  | 1         | 0  | P31 transition (E03 = Reserved)    |

|   | 0  | 1         | 1  | P32 transition (E03 = Reserved)    |

| • | 1  | 0         | 0  | P33 transition (E03 = Reserved)    |

|   | 1  | 0         | 1  | P27 transition                     |

|   | 1  | 1         | 0  | Logical NOR of Port 2 bits 0:3     |

|   | 1  | 1         | 1  | Logical NOR of Port 2 bits 0:7     |

P31-P33 cannot wake up from STOP Mode if the input lines are configured as analog inputs. In the Z86E06, when the SPI is enabled and the Compare feature is active, a SMR is generated upon a comparison in the SPI Shift Register and SCOMP Register, regardless of the above SMR Reg-

ister settings. If SPI Compare is used to wake up the part from STOP Mode, it is still possible to have one of the other STOP-Mode Recovery sources active. **Note:** These other STOP- Mode Recovery sources must be active level Low (bit D6 in SMR set to 0 if P31, P32, P33, and P27 selected, or bit D6 in SMR set to 1 if logical NOR of Port 2 is selected).

**STOP-Mode Recovery Delay Select (D5).** This bit disables the 5 ms RESET delay after STOP-Mode Recovery. The default condition of this bit is 1. If the 'fast' wake up is selected, the STOP-Mode Recovery source needs to be kept active for at least 5 TpC.

**STOP-Mode Recovery Level Select (D6).** A 1 in this bit position indicates that a high level on any one of the recovery sources wakes the device from STOP Mode. A 0 indicates low level recovery. The default is 0 on POR (Figure 19).

Cold or Warm Start (D7). This bit is set by the device upon entering STOP Mode. It is active High, and is 0 (cold) on POR/WDT RESET. This bit is Read Only. A 1 in this bit (warm) indicates that the device awakens by a SMR source.

Figure 19a. STOP Mode Recovery Source (Z86E03)

Internal Address Counter. The address of Z86E03/E06 is generated internally with a counter clocked through pin P01 (Clock). Each clock signal increases the address by one and the high level of pin P00 (Clear) will reset the address to zero. Figure 16 shows the setup time of the serial address input.

**Programming Waveform.** Figures 24, 25 and 26 show the programming waveforms of each mode. Table 7 shows the timing of programming waveforms.

**Programming Algorithm.** Figure 27 shows the flow chart of the Z86E03/E06 programming algorithm.

**Table 8. Timing of Programming Waveforms**

| Parameters | Name                       | Min  | Max | Units |

|------------|----------------------------|------|-----|-------|

| -1         | Address Setup Time         | 2    |     | μs    |

| 1          | Data Setup Time            | 2    |     | μs    |

| 2          |                            | 2    |     | μs    |

| 3          | V <sub>PP</sub> Setup      | 2    |     | μs    |

| 4          | V <sub>cc</sub> Setup Time |      |     |       |

| 5          | Chip Enable Setup Time     | 2    |     | μs    |

|            | Program Pulse Width        | 0.95 |     | ms    |

| 6          | Data Hold Time             | 2    |     | μs    |

| 7          |                            | 2    |     | μs    |

| 8          | /OE Setup Time             |      |     |       |

| 9          | Data Access Time           |      | 200 | ns    |

| -          | Data Output Float Time     |      | 100 | ns    |

| 10         | Overprogram Pulse Width    | 2.85 |     | ms    |

| 11         | Overprogram ruise width    | 2    |     | μs    |

| 12         | EPM Setup Time             |      |     |       |

| 13         | /PGM Setup Time            | 2    |     | μs    |

| 14         | Address to /OE Setup Time  | 2    |     | μs    |

| 15         | Option Program Pulse Width | 78   |     | ms    |

|                  |                                                   | V <sub>cc</sub> | tô - | : 0°C<br>:70°C | to + | -40°C<br>105°C | Typical<br>@ 25°C | Units | Conditions                                                            | Notes       |

|------------------|---------------------------------------------------|-----------------|------|----------------|------|----------------|-------------------|-------|-----------------------------------------------------------------------|-------------|

| Symbol           | Parameter                                         | Note [3]        | Min  | Max            | Min  | Max            | @ 25°C            |       |                                                                       | MULCS       |

| $V_{0L3}$        | P36                                               | 5.0V            |      | 1.0            |      | 1.0            |                   | ٧     | l <sub>ot</sub> = 24 mA                                               |             |

| CC1              | Standby Current                                   | 3.3V            |      | 3.0            |      | 3.0            | 1.3               | mA    | HALT Mode $V_{IN} = 0V$ , $V_{CC} @ 8 MHz$                            | [4, 5,12]   |

|                  |                                                   | 5.0V            |      | 5              |      | 5              | 3.0               | mA    | HALT Mode $V_{N} = 0V$ , $V_{CC} @ 8 MHz$                             | [4, 5,12]   |

|                  |                                                   | 3.3V            |      | 4.5            |      | 4.5            | 2.0               | mA    | HALT Mode V <sub>IN</sub> = 0V,<br>V <sub>CC</sub> @ 12 MHz           | [4,5,13]    |

|                  |                                                   | 5.0V            |      | 7.0            |      | 7.0            | 4.0               | mA    | HÄLT Mode V <sub>IN</sub> = 0V,<br>V <sub>cc</sub> @ 12 MHz           | [4,5,13]    |

|                  |                                                   | 3.3V            |      | 1.4            |      | 1.4            | 0.7               | mA    | Clock Divide-by-16<br>@ 8 MHz                                         | [4, 5, 12]  |

|                  |                                                   | 5.0V            |      | 3.5            |      | 3.5            | 2.0               | mA    | Clock Divide-by-16<br>@ 8 MHz                                         | [4, 5,12]   |

|                  |                                                   | 3.3V            |      | 2.0            |      | 2.0            | 1.0               | mA    | Clock Divide-by-16<br>@ 12 MHz                                        | [4, 5, 13]  |

|                  |                                                   | 5.0V            |      | 4.5            |      | 4.5            | 2.5               | mA    | Clock Divide-by-16<br>@ 12 MHz                                        | [4, 5,13]   |

|                  |                                                   | 5.0V            |      | 1.0            |      | 1.0            |                   | mA    | HALT Mode @ 12 kHz                                                    | [4,5,11,13] |

| I <sub>CC2</sub> | Standby Current                                   | 3.0V            |      | 10             |      | 20             | 1.0               | μА    | STOP Mode V <sub>IN</sub> = OV,<br>V <sub>CC</sub> WDT is not Running | [6, 9]      |

|                  |                                                   | 5.0V            |      | 10             |      | 20             | 3.0               | μA    | STOP Mode V <sub>IN</sub> = OV,<br>V <sub>cc</sub> WDT is not Running | [6, 9]      |

|                  |                                                   | 3.3V            |      | 600            |      | 600            | 400               | μA    | STOP Mode V <sub>IN</sub> = 0V,<br>V <sub>cc</sub> WDT is Running     | [6, 9,12]   |

|                  |                                                   | 5.0V            |      | 1000           |      | 1000           | 800               | μA    | STOP Mode V <sub>N</sub> = OV,<br>V <sub>cc</sub> WDT is Running      | [6, 9,12]   |

| IALL             | Auto Latch Low<br>Current                         | 3.3V            |      | 7.0            |      | 14.0           | 4.0               | μA    | OV < V <sub>IN</sub> < V <sub>CC</sub>                                |             |

|                  | COHER                                             | 5.0V            |      | 20.0           |      | 30.0           | 10                | μA    | $0V < V_{IN} < V_{CC}$                                                |             |

| I <sub>ALH</sub> | Auto Latch High                                   | 3.3V            | -    | -4.0           |      | -8.0           | -2.0              | μA    | OV < V <sub>IN</sub> < V <sub>CC</sub>                                |             |

| ALH              | Current                                           | 5.0V            |      | -9.0           |      | -16.0          | -5.0              | μA    | 0V < V <sub>IN</sub> < V <sub>CC</sub>                                |             |

| T <sub>POR</sub> | Power-On Reset                                    | 3.3V            | 7    | 24             | 6    | 25             | 13                | ms    |                                                                       |             |

| POR              |                                                   | 5.0V            | 3    | 13             | 2    | 14             | 7                 | ms    |                                                                       |             |

| V <sub>LV</sub>  | V <sub>cc</sub> Low Voltage<br>Protection Voltage |                 | 2.2  | 2.8            | 1.7  | 3.0            | 2.6               | V     | 6 MHz max Int. CLK Fre                                                | eq. [3      |

| Not | • |  |

|-----|---|--|

| [1] | l <sub>oo</sub> ,            | Тур | Max | Unit | Freq  |

|-----|------------------------------|-----|-----|------|-------|

|     | Clock Driven on XTAL         | 0.3 | 5.0 | mΑ   | 8 MHz |

|     | Crystal or Ceramic Resonator | 3.0 | 5.0 | mΑ   | 8 MHz |

Crystal or Ceramic Resonator 5.0 5.0 mA  $V_{\rm ss}=0$ V = GND  $V_{\rm cc}=3.0$ V to 5.5V. The  $V_{\rm LV}$  increases as the temperature decreases. Typical values measured at 3.3V and 5.0V. All ourputs unloaded, I/O pins floating, inputs at rail. [2] [3]

<sup>[4]</sup> [5] [6]  $C_{L_1} = C_{L_2} = 100 \text{ pF}$ Same as note [4] except inputs at  $V_{cc}$ .

<sup>[7]</sup> For analog comparator inputs when analog comparators are enabled.

[8] Excludes clock pins.

[9] Clock must be forced Low when XTAL1 is clock-driven and XTAL2 is floating.

[10] STD mode (not low EMI mode).

[11] Low EMI Oscillator enabled.

[12] Z86E03 only.

<sup>[12]</sup> Z86E03 only.

<sup>[13]</sup> Z86E06 only.

# AC ELECTRICAL CHARACTERISTICS Z86E03/E06

Figure 29. Additional Timing

## **AC ELECTRICAL CHARACTERISTICS**

(SCLK/TCLK = EXTERNAL/2)

| No | Symbol     | Parameter                          | V <sub>cc</sub> | 8 1          | T <sub>A</sub> = 0°C | 12 M         | Hz (11)  | 8 1          | _= -40°(<br>MHz <sup>[11]</sup> |              | 05°C<br>1Hz <sup>[11]</sup> |          |                    |

|----|------------|------------------------------------|-----------------|--------------|----------------------|--------------|----------|--------------|---------------------------------|--------------|-----------------------------|----------|--------------------|

|    | Oyilluut . | rarameter                          | Note[3]         | Min          | Max                  | Min          | Max      | Min          | Max                             | Min          | Max                         | Units    | Notes              |

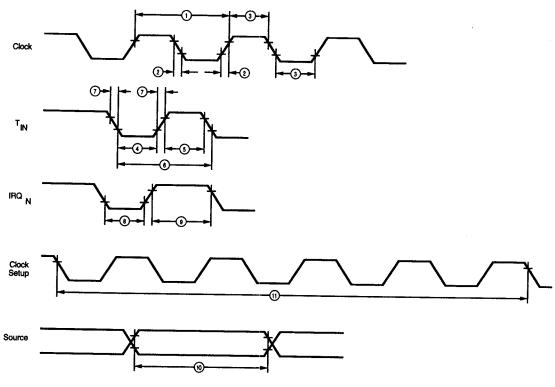

| 1  | ТрС        | Input Clock Period                 | 3.0V<br>5.5V    | 125<br>125   | DC<br>DC             | 83<br>83     | DC<br>DC | 125<br>125   | DC<br>DC                        | 83<br>83     | DC<br>DC                    | ns<br>ns | [1,7,8]<br>[1,7,8] |

| 2  | TrC,TfC    | Clock Input Rise<br>and Fall Times | 3.0V<br>5.5V    |              | 25<br>25             |              | 15<br>15 | ·            | 25<br>25                        |              | 15<br>15                    | ns<br>ns | [1,7,8]<br>[1,7,8] |

| 3  | TwC        | Input Clock Width                  | 3.0V<br>5.5V    | 62<br>62     |                      | 41<br>41     |          | 62<br>62     |                                 | 41<br>41     | ·                           | ns<br>ns | [1,7,8]<br>[1,7,8] |

| 4  | TwTinL     | Timer Input Low Width              | 3.0V<br>5.5V    | 100<br>70    |                      | 100<br>70    |          | 100<br>70    |                                 | 100<br>70    |                             | ns<br>ns | [1,7,8]<br>[1,7,8] |

| 5  | TwTinH     | Timer Input High Width             | 3.0V<br>5.5V    | 5TpC<br>5TpC |                      | 5TpC<br>5TpC |          | 5TpC<br>5TpC | - 11                            | 5TpC<br>5TpC |                             |          | [1,7,8]<br>[1,7,8] |

|    |                 |                                    | V <sub>C</sub> (2) | 8 M          | = 0°C<br>Hz <sup>(11)</sup><br>Max | TO +76<br>12 M<br>Min | D°C<br>Hz <sup>(11)</sup><br>Max | T, =<br>8 Mi<br>Min | -40°C<br>Iz <sup>(11)</sup><br>Max | TO +10<br>12 M<br>Min | )5°C<br>Hz <sup>[11]</sup><br>Max | Units    | Notes                    |

|----|-----------------|------------------------------------|--------------------|--------------|------------------------------------|-----------------------|----------------------------------|---------------------|------------------------------------|-----------------------|-----------------------------------|----------|--------------------------|

| No | Symbol          | Parameter                          | Note [3]           | Min          | max                                | 171111                | Max                              |                     | Max                                |                       | IVILLA                            |          |                          |

| 6  | TpTin           | Timer Input Period                 | 3.0V<br>5.5V       | 8TpC<br>8TpC |                                    | 8TpC<br>8TpC          |                                  | 8TpC<br>8TpC        |                                    | 8TpC<br>8TpC          |                                   |          | [1,7,8]<br>[1,7,8]       |

| 7  | TrTin,<br>TtTin | Timer Input Rise<br>and Fall Timer | 3.0V               |              | 100                                |                       | 100                              |                     | 100                                |                       | 100                               | ns       | [1,7,8]                  |

|    | 111111          | ara ran rano                       | 5.5V               |              | 100                                |                       | 100                              |                     | 100                                |                       | 100                               | ns       | [1,7,8]                  |

| 8  | TwlL            | Int. Request Input<br>Low Time     | 3.0V               | 100          |                                    | 100                   |                                  | 100                 |                                    | 100                   |                                   | ns       | [1,2,7,8]                |

|    |                 | LOW TIME                           | 5.5V               | 70           |                                    | 70                    |                                  | 70                  |                                    | 70                    |                                   | ns       | [1,2,7,8]                |

| 9  | TwlH            | Int. Request Input<br>High Time    | 3.0V               | 5TpC         |                                    | 5TpC                  |                                  | 5TpC                |                                    | 5TpC                  |                                   |          | [1,2,7,8]                |

|    |                 | raga rano                          | 5.5V               | 5TpC         |                                    | 5TpC                  |                                  | 5TpC                |                                    | 5TpC                  |                                   |          | [1,2,7,8]                |

| 10 | Twsm            | STOP Mode Recovery<br>Width Spec   | 3.0V               | 12           |                                    | 12                    |                                  | 12                  |                                    | 12                    |                                   |          | [1,8,10]                 |

|    |                 | Trial open                         | 5.5V               | 12           |                                    | 12                    |                                  | 12                  |                                    | 12                    |                                   |          | [1,8,10]                 |

| 11 | Tost            | Oscillator Startup Time            | 3.0V<br>5.5V       | 5TpC<br>5TpC | <del></del>                        | 5TpC<br>5TpC          |                                  | 5TpC<br>5TpC        |                                    | 5TpC<br>5TpC          |                                   | ns<br>ns | [1,3,4,9]<br>[1,3,4,9]   |

| 12 | Twdt            | Watch-Dog Timer                    |                    |              |                                    | 45                    |                                  | 10                  |                                    | 12                    |                                   | ms       | D0 = 0 [5.               |

|    |                 | Refresh Time                       | 3.0V<br>5.5V       | 15<br>5      |                                    | 15<br>5               |                                  | 12<br>3             |                                    | 3                     |                                   | ms       | D0 = 0 [5,<br>D1 = 0 [5, |

|    |                 |                                    | 3.0V               | 30           |                                    | 30                    |                                  | 25                  |                                    | 25                    |                                   | ms       | D0 = 1 [5,               |

|    |                 |                                    | 5.5V               | 16           |                                    | 16                    |                                  | 12                  |                                    | 12                    |                                   | ms       | D1 = 0 [5]               |

|    |                 |                                    | 3.0V               | 60           |                                    | 60                    |                                  | 50                  |                                    | 50                    |                                   | ms       | D0 = 0 [5]               |

|    |                 |                                    | 5.5V               | 25           |                                    | 25                    |                                  | 30                  |                                    | 30                    |                                   | ms       | D1 = 1 [5]               |

|    |                 |                                    | 3.0V               | 250          |                                    | 250                   |                                  | 200                 |                                    | 200                   |                                   | ms       | D0 = 1 [5                |

|    |                 |                                    | 5.5V               | 120          |                                    | 120                   |                                  | 100                 |                                    | 100                   |                                   | ms       | D1 = 1 [5]               |

#### Notes:

- Notes:

[1] Timing Reference uses 0.7 V<sub>cc</sub> for a logic 1 and 0.2 V<sub>cc</sub> for a logic 0.

[2] Interrupt request via Port 3 (P31-P33).

[3] V<sub>cc</sub> = 3.0V to 5.5V.

[4] SMR-D5 = 0, POR delay is off.

[5] WDTMR Register

[6] Internal RC Oscillator only.

[7] SMR D1 = 0, SCLK = External/2

[8] Maximum frequency for internal system cloc

- [8] Maximum frequency for internal system clock is 4 MHz when using SCLK = EXTERNAL clock mode.

[9] For RC and LC oscillator and for clock-driven oscillator.

[10] SMR-D5 = 1, STOP-Mode Recovery delay is on.

[11] Z86E03 = 8 MHz; Z86E06 = 12 MHz.

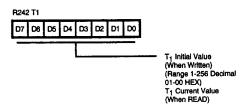

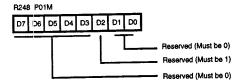

R243 PRE1

## **EXPANDED REGISTER FILE CONTROL REGISTERS** (Continued)

SCOMP (C) 00 D7 D6 D5 D4 D3 D2 D1 D0 PUBUFF (C) 01

D7 D6 D5 D4 D3 D2 D1 D0

Figure 34. SPI Compare Register (Z86E06 Only)

Figure 35. SPI Receive Buffer (Z86E06 Only)

#### **Z8 CONTROL REGISTER DIAGRAMS**

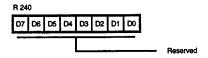

Figure 36. Reserved

D7 D6 D5 D4 D3 D2 D1 D0

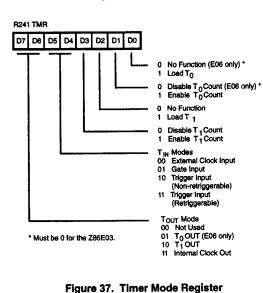

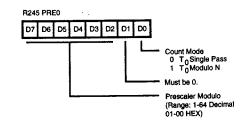

Count Mode

0 T 1 Single Pass

1 T 1 Modulo-N

Clock Source

1 T 1 Internal

0 T 1 External Timing Input

(TN) Mode

Prescaler Modulo

(Range: 1-64 Decimal

01-00 HEX)

Figure 39. Prescaler 1 Register (F3<sub>x</sub>: Write Only)

Figure 40. Counter/Timer 0 Register (F4<sub>H</sub>: Read/Write; Z86E06 Only)

(F1<sub>H</sub>: Read/Write)

Figure 38. Counter Timer 1 Register (F2,: Read/Write)

Figure 41. Prescaler 0 Register (F5<sub>H</sub>: Write Only; Z86E06 Only)

Figure 42. Port 2 Mode Register (F6<sub>u</sub>: Write Only)

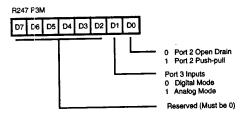

Figure 43. Port 3 Mode Register (F7<sub>H</sub>: Write Only)

Figure 44. Port 0 and 1 Mode Register (F8<sub>H</sub>: Write Only)

Figure 45. Interrupt Priority Register (F9<sub>H</sub>: Write Only)

Figure 46. Interrupt Request Register (FA<sub>n</sub>: Read/Write)

## **INSTRUCTION SET NOTATION**

**Addressing Modes.** The following notation is used to describe the addressing modes and instruction operations as shown in the instruction summary.

| Symbol  | Meaning                                                              |

|---------|----------------------------------------------------------------------|

| IRR     | Indirect register pair or indirect working-<br>register pair address |

| Irr     | Indirect working-register pair only                                  |

| X       | Indexed address                                                      |

| DA      | Direct address                                                       |

| RA      | Relative address                                                     |

| IM      | Immediate                                                            |

| R       | Register or working-register address                                 |

| r       | Working-register address only                                        |

| IR .    | Indirect-register or indirect                                        |

|         | working-register address                                             |

| 1r      | Indirect working-register address only                               |

| RR      | Register pair or working register pair                               |

| address |                                                                      |

**Symbols.** The following symbols are used in describing the instruction set.

| Symbol | Meaning                              |  |  |

|--------|--------------------------------------|--|--|

| dst    | Destination location or contents     |  |  |

| src    | Source location or contents          |  |  |

| CC     | Condition code                       |  |  |

| @      | Indirect address prefix              |  |  |

| SP     | Stack Pointer                        |  |  |

| PC     | Program Counter                      |  |  |

| FLAGS  | Flag register (Control Register 252) |  |  |

| RP     | Register Pointer (R253)              |  |  |

| IMR    | Interrupt mask register (R251)       |  |  |

**Flags.** Control register (R252) contains the following six flags:

| Symbol       | Meaning                             |

|--------------|-------------------------------------|

| С            | Carry flag                          |

| Z            | Zero flag                           |

| S            | Sign flag                           |

| V            | Overflow flag                       |

| D            | Decimal-adjust flag                 |

| H ·          | Half-carry flag                     |

| Affected fla | gs are indicated by:                |

| 0            | Clear to zero                       |

| 1            | Set to one                          |

| *            | Set to clear according to operation |

| _            | Unaffected                          |

|              | Undefined                           |

## **CONDITION CODES**

| Value Mnemonic                       |                               | Meaning                                                                                                                                   | Flags Set                                                                               |  |  |

|--------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| 1000<br>0111<br>1111<br>0110<br>1110 | C<br>NC<br>Z<br>NZ            | Always True<br>Carry<br>No Carry<br>Zero<br>Not Zero                                                                                      | C = 1<br>C = 0<br>Z = 1<br>Z = 0                                                        |  |  |

| 1101<br>0101<br>0100<br>1100<br>0110 | PL<br>MI<br>OV<br>NOV<br>EQ   | Plus<br>Minus<br>Overflow<br>No Overflow<br>Equal                                                                                         | S = 0<br>S = 1<br>V = 1<br>V = 0<br>Z = 1                                               |  |  |

| 1110<br>1001<br>0001<br>1010<br>0010 | NE<br>GE<br>LT<br>GT<br>LE    | Not Equal<br>Greater Than or Equal<br>Less than<br>Greater Than<br>Less Than or Equal                                                     | Z = 0<br>(S XOR V) = 0<br>(S XOR V) = 1<br>[Z OR (S XOR V)] = 0<br>[Z OR (S XOR V)] = 1 |  |  |

| 1111<br>0111<br>1011<br>0011<br>0000 | UGE<br>ULT<br>UGT<br>ULE<br>F | Unsigned Greater Than or Equal<br>Unsigned Less Than<br>Unsigned Greater Than<br>Unsigned Less Than or Equal<br>Never True (Always False) | C = 0<br>C = 1<br>(C = 0 AND Z = 0) = 1<br>(C OR Z) = 1                                 |  |  |

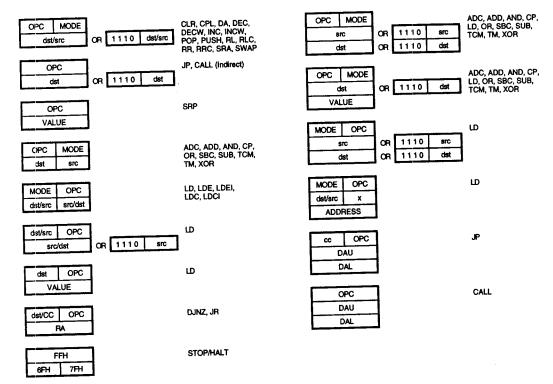

## INSTRUCTION FORMATS

CCF, DI, EI, IRET, NOP, RCF, RET, SCF

OPC dst

#### One-Byte Instructions

Two-Byte instructions

Three-Byte Instructions

## INSTRUCTION SUMMARY

Note: Assignment of a value is indicated by the symbol " ← ". For example:

dst (7)

dst ← dst + src

indicates that the source data is added to the destination data and the result is stored in the destination location. The notation "addr (n)" is used to refer to bit (n) of a given operand location. For example:

refers to bit 7 of the destination operand.

## INSTRUCTION SUMMARY (Continued)

| Instruction and Operation                                                    | Address<br>Mode<br>dst src | Opcode          |   |   | Af<br>S | fect |   | Н |

|------------------------------------------------------------------------------|----------------------------|-----------------|---|---|---------|------|---|---|

| ADC dst, src<br>dst←dst + src +C                                             | t                          | 1[]             | * | * | *       | *    | 0 | * |

| ADD dst, src<br>dst←dst + src                                                | t                          | 0[]             | * | * | *       | *    | 0 | * |

| AND dst, src<br>dst←dst AND src                                              | †                          | 5[]             | • | * | *       | 0    |   | - |

| CALL dst<br>SP←SP - 2<br>@SP←PC,<br>PC←dst                                   | DA<br>IRR                  | D6<br>D4        |   | - | -       | -    | • | - |

| CCF<br>C←NOT C                                                               |                            | EF              | * | - | -       | -    | - | - |

| CLR dst<br>dst←0                                                             | R<br>IR                    | B0<br>B1        | - | - | -       | -    | - | - |

| COM dst<br>dst←NOT dst                                                       | R<br>IR                    | 60<br>61        | - | * | *       | 0    | - | - |

| CP dst, src<br>dst - src                                                     | t                          | A[ ]            | * | * | *       | *    | - | - |

| DA dst<br>dst←DA dst                                                         | R<br>IR                    | 40<br>41        | * | * | *       | Х    | - | - |

| DEC dst<br>dst←dst - 1                                                       | R<br>IR                    | 00<br>01        | - | * | *       | *    |   | - |

| DECW dst<br>dst←dst - 1                                                      | RR<br>IR                   | 80<br>81        | - | * | *       | *    | - | - |

| <b>Di</b><br>IMR(7)←0                                                        |                            | 8F              | - | - | -       | -    |   | - |

| <b>DJNZ</b> r, dst<br>r←r - 1<br>if r ≠ 0<br>PC←PC + dst<br>Range: +127, 128 | RA                         | rA<br>r = 0 - F | - | • | -       | -    |   | - |

| <b>EI</b><br>IMR(7)←1                                                        |                            | 9F              | - | - | -       |      | - | - |

| HALT                                                                         |                            | 7F              | - | - | _       |      |   | _ |

| Instruction        | M       | ddress<br>lode | Opcode    |            | Fl | ags |     | ect | ed |   |

|--------------------|---------|----------------|-----------|------------|----|-----|-----|-----|----|---|

| and Operation      | d       | st src         | Byte (He) | ()         | C  | Z   | S   | ٧   | D  | H |

| INC dst            | ſ       |                | rE        |            | -  | *   | *   | *   | _  | _ |

| dst←dst + 1        |         |                | f = 0 - F |            |    |     |     |     |    |   |

|                    | R       |                | 20        |            |    |     |     |     |    |   |

|                    | IR      | ŀ              | 21        |            |    |     |     |     |    |   |

| INCW dst           | RI      | R              | A0        | -          | -  | *   | *   | *   | _  | _ |

| dst←dst + 1        | IR      |                | A1        |            |    |     |     | •   |    |   |

| IRET               |         |                | BF        | ;          | *  | *   | *   | *   | *  | * |

| FLAGS←@SP;         |         |                |           |            |    |     |     |     |    |   |

| SP←SP+1<br>PC←@SP: |         |                |           |            |    |     |     |     |    |   |

| SP←SP + 2;         |         |                |           |            |    |     |     |     |    |   |

| IMR(7)←1           |         |                |           |            |    |     |     |     |    |   |

| JP cc, dst         | D/      | <del></del>    | cD        |            | _  |     |     |     |    | _ |

| if cc is true,     | Ur      | •              | c=0-F     | -          |    | •   | -   | -   | -  | - |

| PC←dst             | IRI     | R              | 30        |            |    |     |     |     |    |   |

| JR cc, dst         | RA      |                | сВ        |            |    |     | _   |     |    | _ |

| if cc is true.     | 11/     | •              | C=0-F     | •          |    | -   | -   | -   | 7  | - |

| PC←PC + dst        |         |                | 0-0 :     |            |    |     |     |     |    |   |

| Range: +127, -128  |         |                |           |            |    |     |     |     |    |   |

| LD dst, src        | r       | lm             | rС        | — <u>-</u> |    |     |     |     |    | _ |

| dst←src            | r       | R              | r8        |            |    |     |     |     | -  | - |

|                    | R       | ſ              | r9        |            |    |     |     |     |    |   |

|                    |         |                | r=0-F     |            |    |     |     |     |    |   |

|                    | ſ       | Χ              | C7        |            |    |     |     |     |    |   |

|                    | Х       | r              | D7        |            |    |     |     |     |    |   |

|                    | ŗ       | lr             | E3        |            |    |     |     |     |    |   |

|                    | ļr      | ľ              | F3        |            |    |     |     |     |    |   |

|                    | R       | R              | E4        |            |    |     |     |     |    |   |

|                    | R<br>R  | IR<br>IM       | E5        |            |    |     |     |     |    |   |

|                    | n<br>IR | IM<br>IM       | E6<br>E7  |            |    |     |     |     |    |   |

|                    | IR      | R              | F5        |            |    |     |     |     |    |   |

| LDC dst, src       | . r     | Irr            | C2        |            |    |     |     |     |    | _ |

| dst←src            |         | n i            | 02        | -          |    | •   | - ' | -   |    | • |

| LDCI dst, src      | lr      | Irr            | C3        |            | _  |     |     |     |    | _ |

| dst←src            |         |                | •         |            |    |     |     |     |    |   |

| '←r + 1;rr←rr + 1  |         |                |           |            |    |     |     |     |    |   |

| NOP                |         |                | FF        | _          |    |     |     |     | _  | _ |

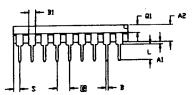

## **PACKAGE INFORMATION**

| JUSHYZ   | MILLI | METER . | INCH |      |  |

|----------|-------|---------|------|------|--|

| 3 : HBUL | MIN   | MAX     | MIN  | HAX  |  |

| A1       | 0.51  | 0.81    | .020 | .032 |  |

| A2       | 3.25  | 3.43    | .128 | .135 |  |

| В        | 0.38  | 0.53    | .015 | .021 |  |

| B1       | 1.14  | 1.65    | .045 | .065 |  |

| С        | 0.23  | 0.38    | .009 | .015 |  |

| D        | 22.35 | 23.37   | .880 | .920 |  |

| E        | 7.62  | 9.13    | .300 | .320 |  |

| E1       | 6.22  | 6.48    | .245 | .255 |  |

| 2        | 2.54  | TYP     | .100 | TYP  |  |

| eA       | 7.87  | 8.89    | .310 | .350 |  |

| L        | 3.18  | 3.81    | .125 | .150 |  |

| Q1       | 1.52  | 1.65    | .060 | .065 |  |

| 2        | 0.89  | 1.65    | .035 | .065 |  |

CONTROLLING DIMENSIONS : INCH

18-Pin DIP Package Diagram

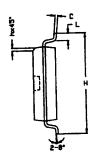

CONTROLLING BINENSIONS : HH LEADS ARE COPLANAR VITHIN .004 INCH.

| SYMBOL   | MILLI | HETER | INCH     |      |  |

|----------|-------|-------|----------|------|--|

|          | MIN   | MAX   | HIDN     | MAX  |  |

| ٨        | 2.40  | 2.65  | .094     | .104 |  |

| AL       | 0.10  | 0.30  | .004     | .012 |  |

| A2       | 2.24  | 2.44  | .088     | .096 |  |

| 1        | 0.36  | 0.46  | .014     | .018 |  |

| c        | 0.23  | 0.30  | .009     | 210. |  |

| D        | 11.40 | 11.75 | .449     | .463 |  |

| E        | 7.40  | 7.68  | .291     | .299 |  |

| <u> </u> |       | TYP   | .050 TYP |      |  |

| H -      | 10.00 | 10.65 | .394     | .419 |  |

| <u> </u> | 0.30  | 0.40  | .012     | .016 |  |

| 1        | 0.60  | 1.00  | .024     | .039 |  |

| 01       | 0.97  | 1.87  | .038     | .042 |  |

18-Pin SOIC Package Diagram

#### **ORDERING INFORMATION**

Z86E03 (8 MHz)

Standard Temperature

**18-Pin DIP** Z86E0308PSC

**18-Pin SOIC Z86E0308SSC**

18-Pin DIP

Extended Temperature in DIP 18-Pin SOIC

Z86E0308PEC

Z86E0308SEC

Z86E06 (12 MHz)

Standard Temperature

18-Pin DIP 18-Pin

18-Pin SOIC

Extended Temperature

18-Pin DIP 18-Pin

18-Pin SOIC

Z86E0612PSC

Z86E0612SSC

Z86E0612PEC

Z86E0612SEC

For fast results, contact your local Zilog sales office for assistance in ordering the part(s) desired.

#### **CODES**

## **Preferred Package**

P = Plastic DIP

#### **Longer Lead Time**

S = Plastic SOIC

## **Preferred Temperature**

S = 0°C to +70°C

#### **Longer Lead Time**

$E = -40^{\circ}C \text{ to } + 105^{\circ}C$

#### **Speeds**

08 = 8 MHz

$12 = 12 \, MHz$

## **Environmental**

C = Plastic Standard

#### Example:

Z 86E03 08 P S C is a Z86E03, 8 MHz, DIP, 0°C to +70°C, Plastic Standard Flow

Environmental Flow

Temperature

Package

Speed

Product Number

Zilog Prefix