Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                               |

|----------------------------|--------------------------------------------------------|

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 12MHz                                                  |

| Connectivity               | SPI                                                    |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 14                                                     |

| Program Memory Size        | 1KB (1K x 8)                                           |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 124 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                              |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                         |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e0612ssc |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# © Zilos

# **PIN FUNCTIONS**

**XTAL1.** *Crystal 1* (time-based input). This pin connects a parallel-resonant crystal, ceramic resonator, LC or RC network or an external single-phase clock to the on-chip oscillator input.

**XTAL2.** *Crystal 2*(time-based output). This pin connects a parallel-resonant crystal, ceramic resonator, LC or RC network to the on-chip oscillator output.

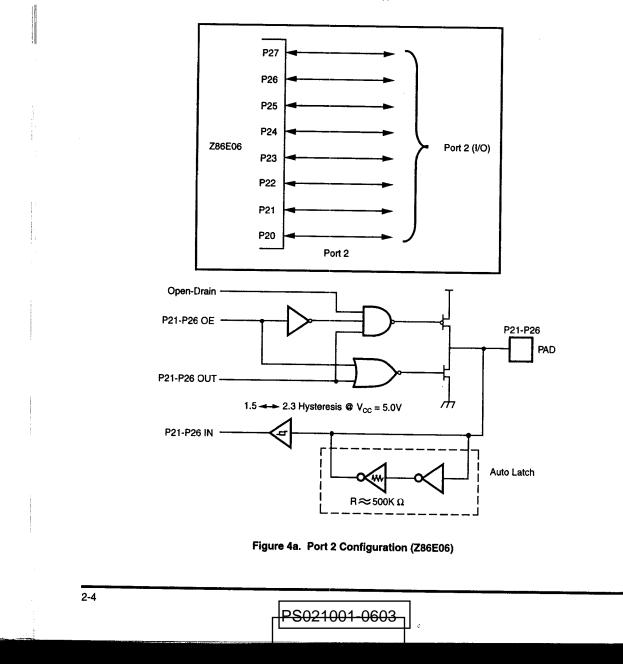

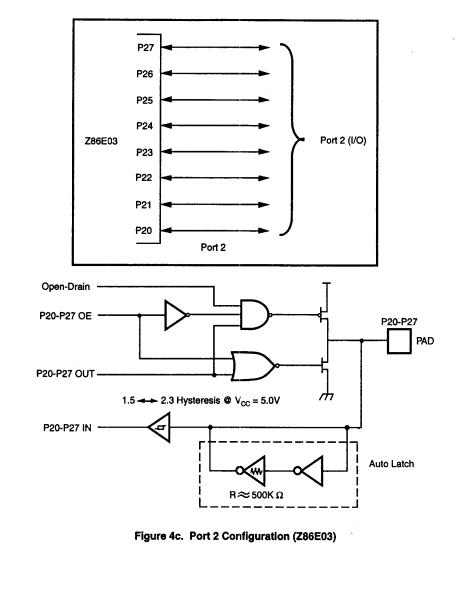

**Port 2 (P27-P20).** Port 2 is an 8-bit, bidirectional, CMOS compatible I/O port. These eight I/O lines can be configured under software control to be an input or output, independently. Input buffers are Schmitt-triggered and contain Auto Latches. Bits programmed as outputs may be globally programmed as either push-pull or open-drain (Figure 4a., 4b., and 4c.). Low EMI output buffers can be globally programmed by the software. In addition, when the SPI is enabled, P20 functions as data-in (DI), and P27 functions as data-out (DO) for the SPI (SPI on the Z86E06 only).

Silas

ADVANCE INFORMATION

# **PIN FUNCTIONS** (Continued)

2-6

@ Zilos

#### ADVANCE INFORMATION

#### Z86E03/E06 CMOS Z8<sup>®</sup> 8-Bit OTP Consumer Controller Processor

2

Auto Latch. The Auto Latch puts valid CMOS levels on all CMOS inputs (except P33, P32, P31) that are not externally driven. Whether this level is 0 or 1 cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

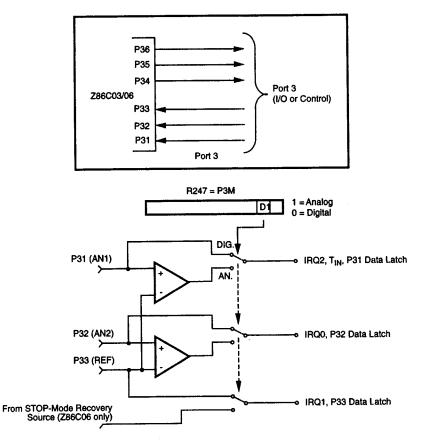

**Port 3 (P36-P31).** Port 3 is a 6-bit, CMOS compatible port. These six lines consist of three fixed inputs (P31-P33) and three fixed outputs (P34-P36). Pins P31, P32, and P33 are standard CMOS inputs (no auto latches) and pins P34, P35, and P36 are push-pull outputs. Low EMI output buffers can be globally programmed by the software. Two on-board comparators can process analog signals on P31 and P32 with reference to the voltage on P33. The analog function is enabled by programming Port 3 Mode Register (P3M-bit D1). Pins P31 and P32 are programmable as falling, rising, or both edge triggered interrupts (IRQ register bits 6 and 7). P33 is the comparator reference voltage input when the analog mode is selected. P33 is a falling edge interrupt input only. **Note:** P33 is available as an interrupt input only in the digital mode. P31 and P32 are valid interrupt inputs and P31 is the  $T_{\rm IN}$  input when the analog or digital input mode is selected.

The outputs from the analog comparator can be globally programmed to output from P34 and P35 by setting PCON (F) 00 bit D0 = 1.

Access to Counter/Timer 1 is made through P31 (T\_{\_{\rm IN}}) and P36 (T\_{\_{\rm OUT}}).

In the Z86E06, pin P34 can also be configured as SPI clock (SK), input and output, and pin P35 can be configured as Slave Select (SS) in slave mode only, when the SPI is enabled (Figures 5a and 5b).

Figure 5a. Port 3 Configuration

\$2ilos

# ADVANCE INFORMATION

Z86E03/E06 CMOS Z8<sup>®</sup> 8-BIT OTP CONSUMER CONTROLLER PROCESSOR

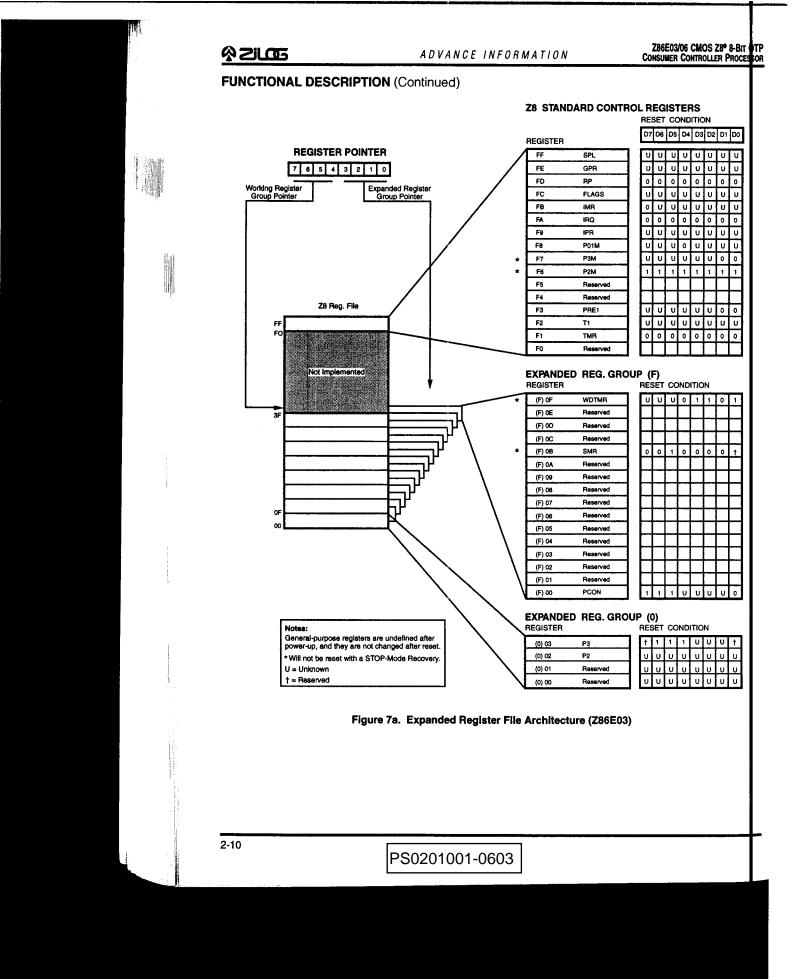

Figure 7b. Expanded Register File Architecture (286E06)

⊗ ZiLOE

#### ADVANCE INFORMATION

#### Z86E03/E06 CMOS Z8<sup>®</sup> 8-Bit OTP Consumer Controller Processor

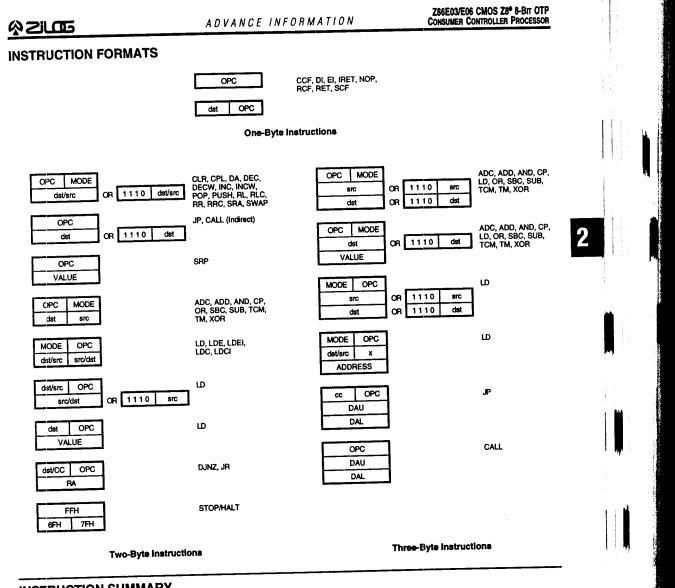

**STOP.** This instruction turns off the internal clock and external crystal oscillation and reduces the standby current. The STOP mode is terminated by a RESET only, either by WDT time-out, POR, SPI compare; or SMR recovery. This causes the processor to restart the application program at address 000C (HEX). Note, the crystal remains active in STOP mode if bits 3 and 4 of the WDTMR are enabled. In this mode, only the Watch-Dog Timer runs in STOP mode.

In order to enter STOP or HALT mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user executes a NOP (opcode=FFH) immediately before the appropriate SLEEP instruction, i.e.:

| FF<br>6F | NOP<br>STOP | ; clear the pipeline<br>; enter STOP mode |

|----------|-------------|-------------------------------------------|

| or       |             |                                           |

| FF       | NOP         | ; clear the pipeline                      |

| 7F       | HALT        | ; enter HALT mode                         |

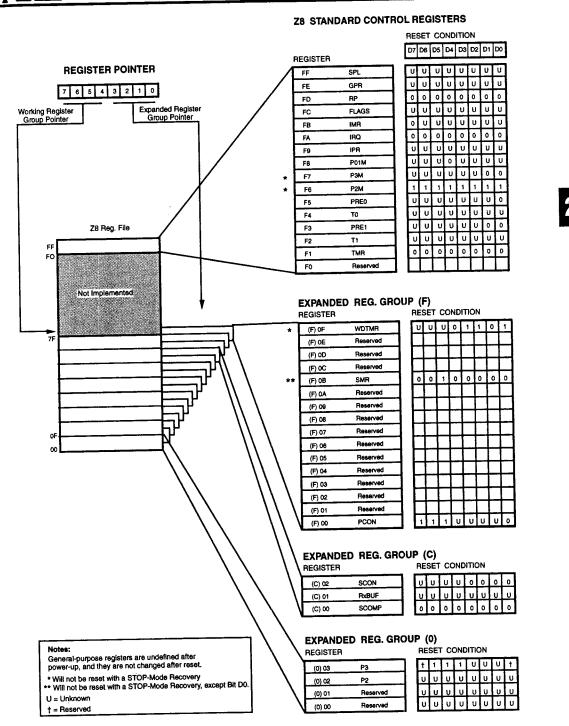

Serial Peripheral Interface (SPI)—Z86E06 Only. The Z86E06 incorporates a serial peripheral interface for communication with other microcontrollers and peripherals. **The SPI does not exist on the Z86E03**. The SPI includes features such as STOP-Mode Recovery, Master/Slave selection, and Compare mode. Table 4 contains the pin configuration for the SPI feature when it is enabled. The SPI consists of four registers: SPI Control Register (SCON), SPI Compare Register (SCOMP), SPI Receive/Buffer Register (RxBUF), and SPI Shift Register. SCON is located in bank (C) of the Expanded Register Group at address 02.

| Table 4. SPI Pin Configuration |              |              |  |  |  |  |  |  |

|--------------------------------|--------------|--------------|--|--|--|--|--|--|

| Name                           | Function     | Pin Location |  |  |  |  |  |  |

| DI                             | Data-In      | P20          |  |  |  |  |  |  |

| DO                             | Data-Out     | P27          |  |  |  |  |  |  |

| SS                             | Slave Select | P35          |  |  |  |  |  |  |

| SK                             | SPI Clock    | P34          |  |  |  |  |  |  |

The SPI Control Register (SCON) (Figure 13) is a read/write register that controls; Master/Slave selection, interrupts, clock source and phase selection, and error flag. Bit 0 enables/disables the SPI with the default being SPI disabled. A 1 in this location will enable the SPI, and a 0 will disable the SPI. Bits 1 and 2 of the SCON register in Master mode select the clock rate. The user may choose whether internal clock is divide-by-2, -4, -8, or -16. In slave mode, Bit 1 of this register flags the user if an overrun of the RxBUF Register has occurred. The RxCharOverrun flag is only reset by writing a 0 to this bit. In slave mode, bit 2 of the Control Register disables the data-out I/O function. If a 1 is written to this bit, the data-out pin is released to its original port configuration. If a 0 is written to this bit, the SPI shifts out one bit for each bit received. Bit 3 of the SCON Register enables the compare feature of the SPI, with the default being disabled. When the compare feature is enabled, a comparison of the value in the SCOMP Register is made with the value in the RxBUF Register. Bit 4 signals that a receive character is available in the RxBUF Register.

#### Figure 13. SPI Control Register (SCON) (Z86E06 Only)

If the associated IRQ3 is enabled, an interrupt is generated. Bit 5 controls the clock phase of the SPI. A 1 in Bit 5 allows for receiving data on the clock's falling edge and transmitting data on the clock's rising edge. A 0 allows receiving data on the clock's rising edge and transmitting on the clock's falling edge. The SPI clock source is defined in bit 6. A 1 uses Timer0 output for the SPI clock, and a 0 uses TCLK for clocking the SPI. Finally, bit 7 determines whether the SPI is used as a Master or a Slave. A 1 puts the SPI into Master mode and a 0 puts the SPI into Slave mode.

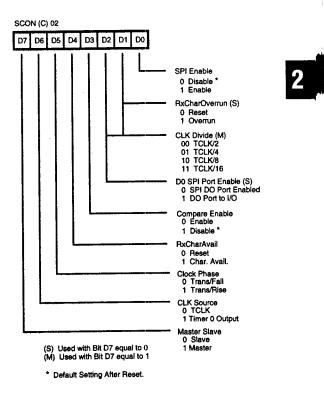

# FUNCTIONAL DESCRIPTION (Continued)

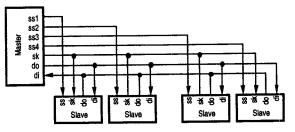

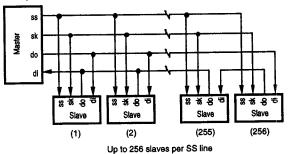

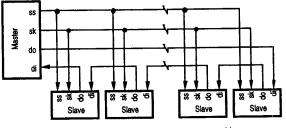

SPI Operation (Z86E06 only). The SPI is used in one of two modes: either as system slave, or as system master. Several of the possible system configurations are shown in Figure 14. In the slave mode, data transfer starts when the slave select (SS) pin goes active. Data is transferred into the slave's SPI Shift Register through the DI pin, which has the same address as the RxBUF Register. After a byte of data has been received by the SPI Shift Register, a Receive Character Available (RCA/IRQ3) flag and interrupt is generated. The next byte of data will be received at this time. The RxBUF Register must be cleared, or a Receive Character Overrun (RxCharOverrun) flag will be set in the SCON Register, and the data in the RxBUF Register will be overwritten. When the communication between the master and slave is complete, the SS goes inactive.

Unless disconnected, for every bit that is transferred into the slave through the DI pin, a bit is transferred out through the DO pin on the opposite clock edge. During slave operation, the SPI clock pin (SK) is an input. In master mode, the CPU must first activate a SS through one of it's I/O ports. Next, data is transferred through the master's DO pin one bit per master clock cycle. Loading data into the shift register initiates the transfer. In master mode, the clock will drive the slave's clock. At the conclusion of a transfer, a Receive Character Available (RCA/ IRQ3) flag and interrupt is generated. Before data is transferred via the DO pin, the SPI Enable bit in the SCON Register must be enabled. **SPI Compare (Z86E06 only).** When the SPI Compare Enable bit, D3 of the SCON Register is set to 1, the SPI Compare feature is enabled. The compare feature is only valid for slave mode. A compare transaction begins when the (SS) line goes active. Data is received as if it were a normal transaction, but there is no data transmitted to avoid bus contention with other slave devices. When the compare byte is received, IRQ3 is not generated. Instead, the data is compared with the contents of the SCOMP Register. If the data does not match, DO remains inactive and the slave ignores all data until the (SS) signal is reset. If the data received matches the data in the SCOMP register, then a SMR signal is generated. D0 is activated if it is not tri-stated by D2 in the SCON Register, and data is received the same as any other SPI slave transaction.

When the SPI is activated as a slave, it operates in all system modes; STOP, HALT, and RUN. Slaves' not comparing remain in their current mode, whereas slaves' comparing wake from a STOP or HALT mode by means of an SMR.

**SPI Clock (Z86E06 only).** The SPI clock maybe driven by three sources: Timer0, a division of the internal system clock, or the external master when in slave mode. Bit D6 of the SCON Register controls what source drives the SPI clock. A 0 in bit D6 of the SCON Register determines the division of the internal system clock if this is used as the SPI clock source. Divide by 2, 4, 8, or 16 is chosen as the scaler.

2-18

# <sup>®</sup>Silæ

#### ADVANCE INFORMATION

#### Z86E03/E06 CMOS Z8º 8-BIT OTP CONSUMER CONTROLLER PROCESSOR

2

Standard Serial Setup

Standard Parallel Setup

Setup For Compare

#### Three Wire Compare Setup

Multiple slaves may have the same address.

Figure 14. SPI System Configuration (Z86E06 Only)

# <sup>⊗</sup>ZiL05

2-20

# ADVANCE INFORMATION

# FUNCTIONAL DESCRIPTION (Continued)

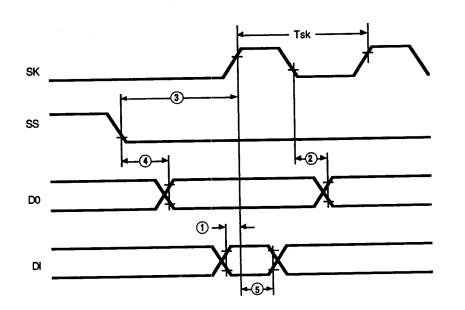

Receive Character Available and Overrun (Z86E06 Only). When a complete data stream is received, an interrupt is generated and the RxCharAvail bit in the SCON Register is set. Bit 4 in the SCON Register is for enabling or disabling the RxCharAvail interrupt. The RxCharAvail bit is available for interrupt polling purposes and is reset when the RxBUF Register is read. RxCharAvail is generated in both master and slave modes. While in slave mode, if the RxBUF is not read before the next data stream is received and loaded into the RxBUF Register, Receive Character Overrun (RxCharOverrun) occurs. Since there is no need for clock control in slave mode, bit D1 in the SPI Contro Register is used to log any RxCharOverrun (Figure 15 and Figure 16).

| No  | Parameter          | Min    | Units |

|-----|--------------------|--------|-------|

| • 1 | DI to SK Setup     | 10     | ns    |

| 2   | SK to D0 Valid     | 15     | ns    |

| 3   | SS to SK Setup     | .5 Tsk | ns    |

| 4   | SS to D0 Valid     | 15     | ns    |

| 5   | SK to DI Hold Time | 10     | ns    |

Figure 15. SPI Timing (Z86E06 Only)

# <sup>⊗</sup>Silas

# FUNCTIONAL DESCRIPTION (Continued)

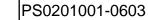

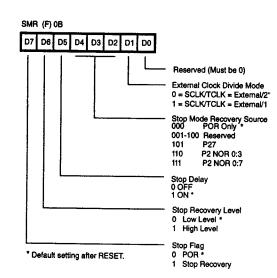

STOP-Mode Recovery Register (SMR). This register selects the clock divide value and determines the mode of STOP-Mode Recovery (Figure 18). All bits are Write Only except bit 7, which is Read Only. Bit 7 is a flag bit that is hardware set on the condition of a STOP recovery and reset on a power-on cycle. Bit 6 controls whether a low level or high level is required from the recovery source. The recovery level must be active Low to work with SPI. Bit 5 controls the reset delay after recovery. Bits 2, 3, and 4 of the SMR specify the source of the STOP-Mode Recovery signal. Bit 1 determines whether the XTAL is divided by 1 or 2. A 0 in this location uses XTAL divide-by-two, and a 1 uses XTAL. The default for this bit is XTAL divide-by-two. Bit 0 controls the divide-by-16 prescaler of SCLK/TCLK. The SMR is located in bank F of the Expanded Register Group at address 0BH.

Figure 18a. STOP-Mode Recovery Register (Write Only except bit D7, which is Read Only.) (Z86E03)

\*\* Default setting after RESET, and STOP-Mode Recovery.

#### Figure 18b. STOP-Mode Recovery Register (Write Only except bit D7, which is Read Only.) (Z86E06)

SCLK/TCLK Divide-by-16 Select (D0)—Z86E06 Only. D0 of the SMR controls a divide-by-16 prescaler of SCLK/ TCLK. The purpose of this control is to selectively reduce device power consumption during normal processor execution (SCLK control) and/or HALT mode (where TCLK sources the counter/timers and interrupt logic).

External Clock Divide Mode (D1). This bit can eliminate the oscillator divide-by-two circuitry. When this bit is 0, SCLK (System Clock) and TCLK (Timer Clock) are equal to the external clock frequency divided by two. The SCLK/ TCLK is equal to the external clock frequency when this bit is set (D1=1). Using this bit, together with D7 of PCON, helps further lower EMI [i.e., D7 (PCON)=0, D1 (SMR=1]. The default setting is 0.

2-22

# ⊗ZiLOG

#### ADVANCE INFORMATION

#### FUNCTIONAL DESCRIPTION (Continued) SMR D4 D3 D2 0 0 0 0 0 0 SMR D4 D3 D2 SP 0 0 0 ō õ VDD 1 1 n õ P20 P31 P32 P33 P23 ΤοP RESE Stop Mode Recovery Edge Select (SMR) To P33 Data Latch and IRQ1 XUN P33 From Pads Digital/Analog Mode Select (P3M) \*Note: P31, P32 and P33 are not in Analog Mode. Figure 19b. STOP-Mode Recovery Source (Z86E06)

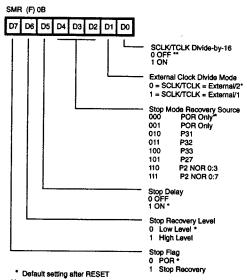

Watch-Dog Timer Mode Register (WDTMR). The WDT is a retriggerable one-shot timer that resets the Z8 if it reaches its terminal count. The WDT is initially enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction. The WDT cannot be disabled after it has been initially enabled. The WDT circuit is driven by an on-board RC oscillator or external oscillator from XTAL1 pin. The POR clock source is selected with bit 4 of the WDTMR register.

Note: Execution of the WDT instruction affects the Z (zero), S (sign), and V (overflow) flags.

Bits 0 and 1 control a tap circuit that determines the timeout period (on Z86E06 only). Bit 2 determines whether the WDT is active during HALT and bit 3 determines WDT activity during STOP. If bits 3 and 4 of this register are both set to 1, the WDT is only driven by the external clock during STOP mode. This feature makes it possible to wake up from STOP mode from an internal source. Bits 5 through 7 of the WDTMR are reserved (Figure 20). This register is accessible only during the first 64 internal system clock cycles from the execution of the first instruction after Power-On Reset, Watch-Dog Reset or a STOP Mode Recovery (Figure 21). After this point, the regis-

ter cannot be modified by any means, intentional c otherwise. The WDTMR cannot be read and is located in bank F of the Expanded Register Group at addres location 0FH.

\* Default setting after RESET † Must be 01 for Z86E03

Figure 20. Watch-Dog Timer Mode Register (Write Only)

2-24

# <sup>⊗</sup> 2iLOG

# FUNCTIONAL DESCRIPTION (Continued)

**WDT Time Select (D1,D0).** Bits 0 and 1 control a tap circuit that determines the time-out period. Table 6 shows the different values that can be obtained. The default value of D0 and D1 are 1 and 0, respectively. These select bits are present in the Z86E06 only.

## Table 6. Time-Out Period of the WDT (Z86E06 Only)

| D1 | D0 | Tim <del>e</del> -Out of<br>Internal RC OSC | Time-Out of<br>XTAL Clock |

|----|----|---------------------------------------------|---------------------------|

| 0  | 0  | 5 ms min                                    | 256TpC                    |

| 0  | 1  | 15 ms min                                   | 512TpC                    |

| 1  | 0  | 25 ms min                                   | 1024TpC                   |

| 1  | 1  | 100 ms min                                  | 4096TpC                   |

Notes:

TpC = XTAL clock cycle

The default on reset is 15 ms, D0 = 1 and D1 = 0. The values given are for  $V_{cc} = 5.0V$

For the Z86E03, the WDT time-out value is fixed at 1024 TpC (depending on WDTMR bit D4) period. When writing to the WDTMR in the Z86E03, bit D0 must be 1 and D1 must be 0.

WDT During HALT (D2). This bit determines whether or not the WDT is active during HALT mode. A 1 indicates active during HALT. The default is 1.

**WDT During STOP (D3).** This bit determines whether or not the WDT is active during STOP mode. Since XTAL clock is stopped during STOP Mode, unless as specified below, the on-board RC must be selected as the clock source to the POR counter. A 1 indicates active during STOP. The default is 1. If bits D3 and D4 are both set to 1, the WDT only, is driven by the external clock during STOP mode. **Clock Source for WDT (D4).** This bit determines which oscillator source is used to clock the internal POR and WDT counter chain. If the bit is a 1, the internal RC oscillator is bypassed and the POR and WDT clock source is driven from the external pin, XTAL1. The default configuration of this bit is 0, which selects the internal RC oscillator.

## Bits 5, 6 and 7. These bits are reserved.

$V_{cc}$  Voltage Comparator. An on-board Voltage Comparator checks that  $V_{cc}$  is at the required level to ensure correct operation of the device. Reset is globally driven if  $V_{cc}$  is below the specified voltage (typically 2.6V).

**Low Voltage Protection (V**<sub>Lv</sub>). The Low Voltage Protection trip point (V<sub>Lv</sub>) will be less than 3 volts and above 1.8 volts under the following conditions.

Maximum (V<sub>1v</sub>) Conditions:

- Case 1:  $T_A = -40^{\circ}$  to +105°C, Internal Clock (SCLK) Frequency equal or less than 1 MHz

- **Case 2:**  $T_A = -40^{\circ}$  to +85°C, Internal Clock (SCLK) Frequency equal or less than 2 MHz

- Note: The internal clock frequency (SCLK) is determined by SMR (F) 0BH bit D1.

The device functions normally at or above 3.0V under all conditions. Below 3.0V, the device is guaranteed to function normally until the Low Voltage Protection trip point ( $V_{LV}$ ) is reached, for the temperatures and operating frequencies in cases 1 and 2 above. The actual low voltage trip point is a function of temperature and process parameters (Figure 22).

2-26

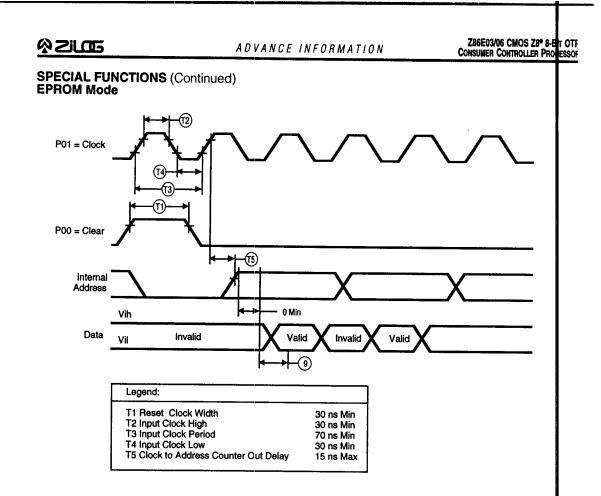

Figure 23. Z86E03/E06 Address Counter Waveform

2-30

| ۵ | 21 |  |

|---|----|--|

|   |    |  |

ADVANCE INFORMATION

Z86E03/06 CMOS Z8º 8-Bit O'P Consumer Controller Process R

# <sup>⊗</sup>2los

# ADVANCE INFORMATION

# **AC ELECTRICAL CHARACTERISTICS**

Additional Timing Table (Divide-By-One Mode, SCLK/TCLK = EXTERNAL)

| No | Symbol          | Parameter                     | V <sub>cc</sub><br>Note (6) | T <sub>A</sub> = 0°C to +70°C<br>4 MHz<br>Min Max | T <sub>A</sub> = −40°C to +105°C<br>4 MHz<br>Min Max | Units    | Notes               |

|----|-----------------|-------------------------------|-----------------------------|---------------------------------------------------|------------------------------------------------------|----------|---------------------|

| 1  | ТрС             | Input Clock Period            | 3.0V<br>5.5V                | 250 DC<br>250 DC                                  | 250 DC<br>250 DC                                     | ns<br>ns | [1,7,8<br>[1,7,8    |

| 2  | TrC,TfC         | Clock Input Rise & Fall Times | 3.0V<br>5.5V                | 25<br>25                                          | 25<br>25                                             | NS<br>NS | [1,7,8]<br>[1,7,8]  |

| 3  | TwC             | Input Clock Width             | 3.0V<br>5.5V                | 125<br>125                                        | 125<br>125                                           | ns<br>ns | [1,7,8]<br>[1,7,8]  |

| 4  | TwTinL          | Timer Input Low Width         | 3.0V<br>5.5V                | 100<br>70                                         | 100<br>70                                            | ns<br>ns | [1,7,8]<br>[1,7,8]  |

| 5  | TwTinH          | Timer Input High Width        | 3.0V<br>5.5V                | 3TpC<br>3TpC                                      | 3TpC<br>3TpC                                         |          | [1,7,8]             |

| 6  | TpTin           | Timer Input Period            | 3.0V<br>5.5V                | 4TpC<br>4TpC                                      | 4TpC<br>4TpC                                         |          | [1,7,8]             |

| 7  | TrTin,<br>TfTin | Timer Input Rise & Fall Timer | 3.0V<br>5.5V                | 100                                               | 100                                                  | NS<br>NS | [1,7,8]<br>[1,7,8]  |

| 8  | TwiL            | Int. Request Low Time         | 3.0V<br>5.5V                | 100<br>70                                         | 100<br>70                                            | ns<br>ns | [1,2,7,8<br>[1,7,8] |

| 9  | TwiH            | Int. Request Input High Time  | 3.0V<br>5.5V                | 3TpC<br>3TpC                                      | 3TpC<br>3TpC                                         |          | [1,2,7,8]           |

| 10 | Twsm            | Stop-Mode Recovery Width Spec | 3.0V<br>5.5V                | 12<br>12                                          | 12<br>12                                             | ns<br>ns | [1,4,]<br>[1,4]     |

| 11 | Tost            | Oscillator Startup Time       | 3.0V<br>5.5V                | 5TpC<br>5TpC                                      | 5TpC<br>5TpC                                         |          | [1,3,8,9]           |

Notes: [1] Timing Reference uses  $0.7 V_{cc}$  for a logic 1 and  $0.2 V_{cc}$  for a logic 0. [2] Interrupt request via Port 3 (P33-P31). [3] SMR-D5 = 0. [4] SMR-D5 = 1, POR STOP mode delay is on. [5] Reg. WDTMR. [6] V\_{cc} = 2.00 to 5 SV

[6]  $V_{cc} = 3.0V$  to 5.5V. [7] SMR D1 = 1.

[8] Maximum frequency for internal system clock is 4 MHz when using

XTAL divide-by-one mode. [9] For RC and LC oscillator, and for oscillator driven by clock driver.

2-40

# INSTRUCTION SUMMARY

**Note:** Assignment of a value is indicated by the symbol " $\leftarrow$ ". For example:

dst ← dst + src

notation "addr (n)" is used to refer to bit (n) of a given operand location. For example:

dst (7)

indicates that the source data is added to the destination refers to bi data and the result is stored in the destination location. The

refers to bit 7 of the destination operand.

# <sup>®</sup>ZiL05

# ADVANCE INFORMATION

Z86E03/06 CMOS Z8<sup>®</sup> 8-Bit OT Consumer Controller Processo

# **INSTRUCTION SUMMARY** (Continued)

| Instruction<br>and Operation                      | Address<br>Mode<br>dst src                   | Opcode<br>Byte (Hex) |   | - | s Al |     |     |   | H | Instruction<br>and Operation                                          | M           | ddress<br>lode<br>st src | Opcode<br>Byte (Hex)  |   | ags<br>Z |   |   |   |          |

|---------------------------------------------------|----------------------------------------------|----------------------|---|---|------|-----|-----|---|---|-----------------------------------------------------------------------|-------------|--------------------------|-----------------------|---|----------|---|---|---|----------|

| ADC dst, src<br>dst←dst + src +C                  | t                                            | 1[]                  | * | * | *    | : ; | *   | 0 | * | INC dst<br>dst←dst + 1                                                | ſ           |                          | rE<br>r = 0 - F       | - |          |   | * |   | -        |

| ADD dst, src<br>dst←dst + src                     | t                                            | 0[]                  | * | * | *    | ; > | *   | 0 | * |                                                                       | R<br>IR     |                          | 20<br>21              |   |          |   |   |   |          |

| AND dst, src<br>dst←dst AND src                   | †                                            | 5[]                  | - | * | *    | C   | ) . |   | - | INCW dst<br>dst←dst + 1                                               | RI          |                          | A0<br>A1              | - | *        | * | * | - | -        |

| CALL dst<br>SP←SP - 2<br>@SP←PC,<br>PC←dst<br>CCF | DA<br>IRR                                    | D6<br>D4             | - | - | -    | -   |     |   | - | IRET<br>FLAGS←@SP;<br>SP←SP + 1<br>PC←@SP;<br>SP←SP + 2;<br>bter = 2; |             |                          | BF                    | * | *        | * | * | * | : *      |

| CCF<br>C←NOT C                                    |                                              | EF                   | * | - | -    | -   | -   | • | - | IMR(7)←1<br>JP cc, dst                                                | DA          |                          | cD                    |   |          | _ |   |   | <u> </u> |

| CLR dst<br>dst←0                                  | R<br>IR                                      | B0<br>B1             | - | - | -    | -   | -   |   | - | if cc is true,<br>PC←dst                                              | IRI         |                          | c = 0 - F<br>30       |   |          |   | - | - | -        |

| COM dst<br>Jst←NOT dst                            | R<br>IR                                      | 60<br>61             | - | * | *    | 0   | -   |   | - | JR cc, dst<br>if cc is true,<br>PC←PC + dst                           | RA          |                          | cB<br>c = 0 - F       | • | -        | - | - | - | -        |

| CP dst, src<br>ist - src                          | t                                            | A[ ]                 | * | * | *    | *   | -   |   | - | Range: +127, -128                                                     |             |                          |                       |   |          |   |   |   |          |

| DA dst<br>Ist←DA dst                              | R<br>IR                                      | 40<br>41             | * | * | *    | X   | -   |   |   | LD dst, src<br>dst←src                                                | r<br>r<br>R | lm<br>R<br>r             | rC<br>81<br>19        | - | -        | - | - | - | -        |

| DEC dst<br>Ist←dst - 1                            | R<br>IR                                      | 00<br>01             | - | * | *    | *   | -   | - |   |                                                                       | r<br>X      | X                        | r = 0 - F<br>C7<br>D7 |   |          |   |   |   |          |

| DECW dst<br>lst←dst - 1                           |                                              | 80<br>81             | - | * | *    | *   | -   | - |   |                                                                       | r<br>Ir     | lr<br>r                  | E3<br>F3              |   |          |   |   |   |          |

| 01<br>MR(7)←0                                     |                                              | 8F                   | - | - | -    | -   | -   | - |   |                                                                       | R<br>R<br>R | r<br>Ir<br>IM            | E4<br>E5<br>E6        |   |          |   |   |   |          |

| <b>UNZ</b> r, dst<br>←r - 1<br>r ≠ 0              |                                              | rA<br>r = 0 - F      | - | - | -    | -   | -   | - | - |                                                                       | ir<br>Ir    | IM<br>R                  | E7<br>F5              |   |          |   |   |   |          |

| r≠0<br>C←PC + dst<br>ange: +127, 128              |                                              |                      |   |   |      |     |     |   |   | LDC dst, src<br>dst←src                                               | . <b>r</b>  | lrr                      | C2                    |   |          | - | - | - | -        |

| I<br>∕IR(7)←1                                     |                                              | 9F                   | - | - | -    | -   | -   | - | - | LDCI dst, src<br>dst←src<br>r←r + 1;rr←rr + 1                         | Ir          | Irr                      | C3                    |   |          | - | + | - | -        |

| ALT                                               | <u>.                                    </u> | 7F                   |   |   | -    | -   | -   | - | - | NOP                                                                   |             |                          | FF                    |   |          |   |   |   |          |

2-48

# <sup>®</sup>SICE

100 m

Arances and a

# ADVANCE INFORMATION

Z86E03/06 CMOS Z8º 8-BIT-OTF CONSUMER CONTROLLER PROCESSO

|                    |   | )<br>0                   | 1                        | 2                       | 3                            |                              |                        |                              | .ower Ni                     | •        | •  |               |                                        |         |                  |                    |       |                      |       |           |             |

|--------------------|---|--------------------------|--------------------------|-------------------------|------------------------------|------------------------------|------------------------|------------------------------|------------------------------|----------|----|---------------|----------------------------------------|---------|------------------|--------------------|-------|----------------------|-------|-----------|-------------|

|                    |   | 6.5                      | 6.5                      | 6.5                     | 6.5                          | 4                            | 5<br>10.5              | 6<br>10.5                    | 7                            | 6.5      | -  | 9             | A<br>12/10.                            |         | B                | C                  |       | D                    | _     | E         | _           |

|                    | 0 | DEC<br>R1                | DEC<br>IR1               | ADD<br>r1, r2           | ADD<br>r1, Ir2               | ADD                          | ADD                    | ADD                          | ADD                          | L D      | ι  | .5<br>D<br>R1 | DJNZ<br>r1, RA                         |         | 10.0<br>IR<br>RA | 6.9<br>LC<br>r1, 1 | >     | 12.10<br>JP<br>cc, D | 1     | 6.5<br>NC |             |

|                    | 1 | 6.5<br>RLC               | 6.5<br>RLC               | 6.5<br>ADC              | 6.5<br>ADC                   | 10.5<br>ADC                  | 10.5<br>ADC            | 10.5<br>ADC                  | 10.5<br>ADC                  |          |    |               |                                        |         |                  |                    |       |                      | ~     |           | ┢─          |

|                    |   | R1<br>6.5                | IR1<br>6.5               | r1, r2<br>6.5           | r1, lr2<br>6.5               | R2, R1<br>10.5               | IR2, R1<br>10.5        | R1, IM                       | IR1, IM<br>10.5              |          |    |               |                                        |         |                  |                    |       |                      |       |           |             |

|                    | 2 | INC<br>R1                | INC<br>IR1               | <b>SUB</b><br>r1, r2    | SUB<br>r1, Ir2               | <b>SUB</b><br>R2, R1         | <b>SUB</b><br>IR2, R1  | SUB<br>R1, IM                | SUB<br>IR1, IM               |          |    |               |                                        |         |                  |                    |       |                      |       |           |             |

|                    | 3 | 8.0<br><b>JP</b><br>IRR1 | 6.1<br>SRP<br>IM         | 6.5<br>SBC<br>r1, r2    | 6.5<br>SBC<br>r1, ir2        | 10.5<br><b>SBC</b><br>R2, R1 | 10.5<br>SBC<br>IR2, R1 | 10.5<br>SBC<br>R1, IM        | 10.5<br>SBC                  |          |    |               |                                        |         |                  |                    |       |                      |       |           |             |

|                    | 4 | 8.5<br>DA                | 8.5<br>DA                | 6.5<br>OR               | 6.5<br>OR                    | 10.5<br><b>OR</b>            | 10.5<br>OR             | 10.5<br>OR                   | IR1, IM<br>10.5<br><b>OR</b> |          |    |               |                                        |         |                  |                    |       |                      |       |           |             |

|                    |   | R1<br>10.5               | IR1<br>10.5              | r1, r2<br>6.5           | r1, lr2<br>6.5               | R2, R1                       | IR2, R1<br>10.5        | R1, IM                       | IR1, IM<br>10.5              |          |    |               |                                        |         |                  |                    |       |                      |       |           |             |

|                    | 5 | POP<br>R1                | POP<br>IR1               | AND<br>r1, r2           | AND<br>r1, ir2               | AND<br>R2, R1                | AND<br>IR2, R1         | AND<br>R1, IM                | AND<br>IR1, IM               |          |    |               |                                        |         |                  |                    |       |                      |       |           | 6.<br>WI    |

| Q                  | 6 | 6.5<br><b>COM</b><br>R1  | 6.5<br>COM<br>IR1        | 6.5<br>TCM<br>r1, r2    | 6.5<br><b>TCM</b><br>r1, lr2 | 10.5<br>TCM                  | 10.5<br>TCM            | 10.5<br>TCM                  | 10.5<br>TCM                  |          |    |               |                                        |         |                  |                    |       |                      |       |           | 6.<br>ST    |

| Upper Nibble (Hex) | 7 | 10/12.1<br>PUSH          | 12/14.1<br>PUSH          | 6.5<br>TM               | 6.5<br>TM                    | R2, R1<br>10.5<br>TM         | 1R2, R1<br>10.5<br>TM  | R1, IM<br>10.5<br>TM         | IR1, IM<br>10.5<br>TM        |          |    |               |                                        |         |                  |                    |       |                      |       |           | 7.(         |

| Inddin'            |   | R2<br>10.5               | IR2<br>10.5              | r1, r2                  | r1, ir2                      | R2, R1                       | IR2, R1                | R1, IM                       | IR1, IM                      |          |    |               |                                        |         |                  |                    |       |                      |       |           | HA          |

| Upper              | 8 | DECW<br>RR1              | DECW<br>IR1              |                         |                              |                              |                        |                              |                              |          |    |               |                                        |         |                  |                    |       |                      |       |           | 6.<br>D     |

| _                  | 9 | 6.5<br><b>RL</b><br>R1   | 6.5<br><b>RL</b>         |                         |                              |                              |                        |                              |                              |          |    |               |                                        |         |                  |                    |       |                      |       | ł         | 6.<br>E     |

|                    |   | 10.5                     | IR1<br>10.5<br>INCW      | 6.5<br>CP               | 6.5<br>CP                    | 10.5<br>CP                   | 10.5                   | 10.5                         | 10.5                         |          |    |               |                                        |         |                  |                    |       |                      |       | ╞         | 14.         |

|                    |   | RR1<br>6.5               | IR1<br>6.5               | r1, r2<br>6.5           | r1, Ir2<br>6.5               |                              | CP<br>IR2, R1<br>10.5  | CP<br>R1, IM<br>10.5         | CP<br>IR1, IM<br>10.5        |          |    |               |                                        |         |                  |                    |       |                      |       |           | RE          |

|                    | в | CLR<br>R1                | CLR<br>IR1               | <b>XOR</b><br>r1, r2    | <b>XOR</b><br>r1, lr2        | <b>XOR</b><br>R2, R1         | <b>XOR</b><br>IR2, R1  | 10.5<br><b>XOR</b><br>R1, IM | 10.5<br>XOR<br>IR1, IM       |          |    |               |                                        |         |                  |                    |       |                      |       |           | 16.0<br>IRE |

|                    | c | 6.5<br><b>RRC</b><br>R1  | 6.5<br><b>RRC</b><br>IR1 | 12.0<br>LDC<br>r1, Irr2 | 18.0<br>LDCI                 |                              |                        |                              | 10.5<br>LD                   |          |    |               |                                        |         |                  |                    |       |                      |       | ľ         | 6.5<br>RC   |

|                    | ь | 6.5<br>SRA               | 6.5<br>SRA               | .,                      | lr1, lrr2                    | 20.0<br>CALL*                |                        | 20.0                         | r1,x,R2<br>10.5              |          |    |               |                                        |         |                  |                    |       |                      |       | ┢         | 6.5         |

|                    | ╞ | R1 6.5                   | IR1<br>6.5               |                         | 6.5                          | IRR1<br>10.5                 | 10.5                   | DA<br>10.5                   | LD<br>r2,x,R1                |          |    |               |                                        |         |                  |                    |       |                      |       |           | SCI         |

| l                  | E | RR<br>R1                 | RR<br>IR1                |                         | LD                           | LD                           | ID.5<br>LD<br>IR2, R1  | LD                           | 10.5<br>LD<br>IR1, IM        |          |    |               |                                        |         |                  |                    |       |                      |       |           | 6.5<br>CCI  |

| í                  | F | 8.5<br>SWAP              | 8.5<br>SWAP              |                         | 6.5<br>LD                    |                              | 10.5<br>LD             |                              |                              |          |    |               |                                        |         |                  |                    |       |                      |       | ŀ         | 6.0<br>NOF  |

|                    | Ę | R1                       |                          |                         | lr1, r2                      |                              | R2, IR1                |                              | <u> </u>                     |          |    |               |                                        |         |                  | V                  | Ŧ     | I_                   | Ļ     |           |             |

|                    |   |                          | 2                        |                         |                              |                              | 3                      | Byt                          | es per ir                    | nstructi | on |               | 2                                      |         |                  |                    |       | 3                    | _     |           |             |

|                    |   |                          |                          |                         |                              |                              |                        | .ower<br>pcode               |                              |          |    |               | .egeno                                 |         | den -            | _                  |       |                      |       |           |             |

|                    |   |                          |                          |                         | E                            | xecution                     | n N                    | libble                       | Pipel                        |          |    | r             | ₹ = 8-b<br>= 4-bi<br>8 <sub>1</sub> or | t add   | ress             | -                  | (Acc  |                      |       |           |             |

|                    |   |                          |                          |                         |                              | Cycles                       | الم                    | 4                            | Cýcle                        |          |    |               | 1 01<br>2 or                           |         |                  |                    |       |                      |       |           |             |

|                    |   |                          |                          |                         | Upp<br>Opcod                 | de                           | - A                    | 10.5                         | Mn                           | emonic   |    | 0             | <b>equer</b>                           | e, Firs |                  |                    | d,    |                      |       |           |             |

|                    |   |                          |                          |                         | Nibb                         | le                           | کلر ا                  | 1, R2                        |                              |          |    |               | iecond<br>lote: T                      |         |                  |                    | s are | 9 (894               | arved |           |             |

|                    |   |                          |                          |                         | 0                            | First <sup>2</sup><br>perand |                        |                              | Seco                         |          |    |               | 2-byte                                 | e inst  | ructio           | on ap              | opea  |                      |       |           |             |

|                    |   |                          |                          |                         | ч<br>Ч                       |                              |                        |                              | Ope                          | rand     |    |               | as a 3                                 | s-byt€  | ə insti          | ructio             | on    |                      |       |           |             |

| -50                |   |                          |                          |                         |                              |                              |                        |                              | _                            |          |    |               |                                        |         |                  |                    | -     |                      |       |           |             |

|                    |   |                          |                          |                         |                              | Б                            | 0000                   | 0100                         | 4 0.04                       |          |    |               |                                        |         |                  |                    |       |                      |       |           |             |

# <u> Reilos</u>

#### ADVANCE INFORMATION

Z86E03/E06 CMOS Z8º 8-BIT OTP CONSUMER CONTROLLER PROCESSOR

2

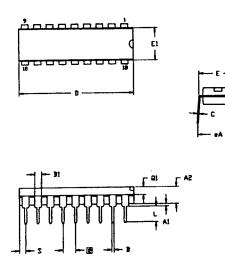

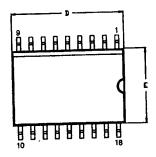

# PACKAGE INFORMATION

| SYMBOL    | MILLI | METER | IN   | CH   |

|-----------|-------|-------|------|------|

|           | MIN   | MAX   | MIN  | HAX  |

| A1        | 0.51  | 0.81  | .020 | .032 |

| 5A        | 3.25  | 3.43  | .128 | .135 |

| B         | 0.38  | 0.53  | .015 | .021 |

| B1        | 1.14  | 1.65  | .045 | .065 |

| С         | 0.23  | 0.38  | .009 | .015 |

| D         | 22.35 | 23.37 | .880 | .920 |

| E         | 7.62  | 8.13  | .300 | .320 |

| El        | 6.22  | 6.48  | .245 | .255 |

| 2         | 2.54  | TYP   | .100 | TYP  |

| eA        | 7.87  | 8.89  | .310 | .350 |

| L         | 3.18  | 3.61  | .125 | .150 |

| <b>Q1</b> | 1.52  | 1.65  | .060 | .065 |

| s         | 0.89  | 1.65  | .035 | .065 |

CONTROLLING DIMENSIONS + INCH

18-Pin DIP Package Diagram

, ç

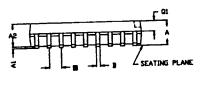

|        | MILLI | HETER | ĮN   | СН   |

|--------|-------|-------|------|------|

| SYMBOL | MIN   | MAX   | HEN  | MAX  |

|        | 2.40  | 2.65  | .094 | .104 |

| AL     | 0.10  | 0.30  | .004 | .012 |

| 82     | 224   | 2.44  | .068 | .0%  |

| 1      | 0.36  | 0.46  | .014 | .018 |

| c      | 0.23  | 0.30  | .009 | .012 |

| D      | 11.40 | 11.75 | .449 | .463 |

| E      | 7.40  | 7.60  | .291 | .299 |

| -      |       | TYP   | .050 | TYP  |

| н      | 10.00 | 10.65 | .394 | .419 |

| h      | 0.30  | 0.40  | .012 | .016 |

| 1      | 0.60  | 1.00  | .024 | .039 |

| 01     | 0.97  | 1.07  | .038 | .042 |

2-8

CONTROLLING DIMENSIONS ( ) HH LEADS ARE COPLANAR VITHIN .004 INCH.

#### 18-Pin SOIC Package Diagram

# PS0201001-0603

2-51

# & Silas

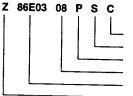

# **ORDERING INFORMATION**

#### Z86E03 (8 MHz)

Standard Temperature 18-Pin DIP Z86E0308PSC

18-Pin SOIC Z86E0308SSC

**Extended Temperature** 18-Pin DIP Z86E0308PEC

**18-Pin SOIC** Z86E0308SEC

Z86E06 (12 MHz)

Standard Temperature 18-Pin DIP 18-Pin SOIC Z86E0612PSC Z86E0612SSC

**Extended Temperature** 18-Pin DIP Z86E0612PEC

**18-Pin SOIC** Z86E0612SEC

For fast results, contact your local Zilog sales office for assistance in ordering the part(s) desired.

# CODES

**Preferred Package** P = Plastic DIP

Longer Lead Time S = Plastic SOIC

**Preferred Temperature**  $S = 0^{\circ}C$  to  $+70^{\circ}C$

Longer Lead Time  $E = -40^{\circ}C \text{ to } + 105^{\circ}C$

Speeds 08 = 8 MHz

12 = 12 MHz

# Environmental

C = Plastic Standard

#### Example:

is a Z86E03, 8 MHz, DIP, 0°C to +70°C, Plastic Standard Flow

**Environmental Flow** Temperature Package Speed Product Number Zilog Prefix

2-52