# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               |                                                                         |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 11                                                                      |

| Program Memory Size        | 1.5KB (1K x 12)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | ·                                                                       |

| RAM Size                   | 67 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 3x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 14-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f526-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F526

### 14-Pin, 8-Bit Flash Microcontroller

#### High-Performance RISC CPU:

- Only 33 Single-Word Instructions

- All Single-Cycle Instructions except for Program Branches which are Two-Cycle

- Two-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- · Operating Speed:

- DC 20 MHz crystal oscillator

- DC 200 ns instruction cycle

- On-chip Flash Program Memory:

- 1024 x 12

- · General Purpose Registers (SRAM):

- 67 x 8

- · Flash Data Memory:

- 64 x 8

#### **Special Microcontroller Features:**

- 8 MHz Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debugging (ICD) Support

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

- Internal Weak Pull-ups on I/O Pins

- · Power-Saving Sleep mode

- Wake-Up from Sleep on Pin Change

- Selectable Oscillator Options:

- INTRC: 4 MHz or 8 MHz precision Internal RC oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- HS: High-speed crystal/resonator

- LP: Power-saving, low-frequency crystal

- EC: High-speed external clock input

#### Low-Power Features/CMOS Technology:

- Standby current:

- 100 nA @ 2.0V, typical

- Operating current:

- 11  $\mu\text{A}$  @ 32 kHz, 2.0V, typical

- 175 μA @ 4 MHz, 2.0V, typical

- Watchdog Timer current:

- 1 μA @ 2.0V, typical

- 7 μA @ 5.0V, typical

- High Endurance Program and Flash Data Memory cells:

- 100,000 write Program Memory endurance

- 1,000,000 write Flash Data Memory endurance

- Program and Flash Data retention: >40 years

- Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V:

- Wide temperature range

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

#### **Peripheral Features:**

- 12 I/O Pins:

- 11 I/O pins with individual direction control

- 1 input-only pin

- High current sink/source for direct LED drive

- Wake-up on change

- Weak pull-ups

- 8-bit Real-time Clock/Counter (TMR0) with 8-bit Programmable Prescaler

- Two Analog Comparators:

- Comparator inputs and output accessible externally

- One comparator with 0.6V fixed on-chip absolute voltage reference (VREF)

- One comparator with programmable on-chip voltage reference (VREF)

- Analog-to-Digital (A/D) Converter:

- 8-bit resolution

- 3-channel external programmable inputs

- 1-channel internal input to internal absolute 0.6 voltage reference

| Device    | Program<br>Memory | Data Memory  |                  | 1/0 | Comparators | Timers 8-bit | 8-bit A/D |  |

|-----------|-------------------|--------------|------------------|-----|-------------|--------------|-----------|--|

| Device    | Flash (words)     | SRAM (bytes) | Flash<br>(bytes) | 1/0 | Comparators | Timers o-bit | Channels  |  |

| PIC16F526 | 1024              | 67           | 64               | 12  | 2           | 1            | 3         |  |

### PIC16F526

NOTES:

| Addr               | Name    | Bit 7       | Bit 6                | Bit 5         | Bit 4         | Bit 3         | Bit 2        | Bit 1   | Bit 0     | Value on<br>Power-on<br>Reset | Page # |

|--------------------|---------|-------------|----------------------|---------------|---------------|---------------|--------------|---------|-----------|-------------------------------|--------|

| N/A                | TRIS    | _           | —                    | I/O Control   | Register (PC  | ORTB, PORT    | IC)          |         |           | 11 1111                       | 27     |

| N/A                | OPTION  | Contains co | ontrol bits to c     | onfigure Tim  | ner0 and Tim  | er0/WDT pre   | escaler      |         |           | 1111 1111                     | 19     |

| 00h                | INDF    | Uses conte  | nts of FSR to        | Address Da    | ata Memory (i | not a physica | al register) |         |           | XXXX XXXX                     | 22     |

| 01h/41h            | TMR0    | Timer0 Mo   | dule Register        |               |               |               |              |         |           | XXXX XXXX                     | 37     |

| 02h <sup>(1)</sup> | PCL     | Low order   | 3 bits of PC         |               |               |               |              |         |           | 1111 1111                     | 21     |

| 03h                | STATUS  | RBWUF       | CWUF                 | PA0           | TO            | PD            | Z            | DC      | С         | 0001 1xxx                     | 18     |

| 04h                | FSR     | Indirect Da | ta Memory Ac         | Idress Pointe | er            |               | •            |         |           | 100x xxxx                     | 22     |

| 05h/45h            | OSCCAL  | CAL6        | CAL5                 | CAL4          | CAL3          | CAL2          | CAL1         | CAL0    | _         | 1111 111-                     | 20     |

| 06h/46h            | PORTB   | —           | —                    | RB5           | RB4           | RB3           | RB2          | RB1     | RB0       | xx xxxx                       | 27     |

| 07h                | PORTC   |             | _                    | RC5           | RC4           | RC3           | RC2          | RC1     | RC0       | xx xxxx                       | 28     |

| 08h                | CM1CON0 | C1OUT       | C10UTEN              | C1POL         | C1T0CS        | C10N          | C1NREF       | C1PREF  | C1WU      | q111 1111                     | 63     |

| 09h                | ADCON0  | ANS1        | ANS0                 | ADCS1         | ADCS0         | CHS1          | CHS0         | GO/DONE | ADON      | 1111 1100                     | 61     |

| 0Ah                | ADRES   | ADC Conv    | ersion Result        |               |               |               | •            |         |           | XXXX XXXX                     | 62     |

| 0Bh                | CM2CON0 | C2OUT       | C2OUTEN              | C2POL         | C2PREF2       | C2ON          | C2NREF       | C2PREF1 | C2WU      | q111 1111                     | 64     |

| 0Ch                | VRCON   | VREN        | VROE                 | VRR           |               | VR3           | VR2          | VR1     | VR0       | 001- 1111                     | 69     |

| 21h/61h            | EECON   | —           | —                    | _             | FREE          | WRERR         | WREN         | WR      | RD        | 0 x000                        | 23     |

| 25h/65h            | EEDATA  | SELF REA    | SELF READ/WRITE DATA |               |               |               |              |         | XXXX XXXX | 23                            |        |

| 26h/66h            | EEADR   |             | —                    | SELF REA      | D/WRITE AD    | DRESS         |              |         |           | xx xxxx                       | 23     |

**TABLE 4-1:** SPECIAL FUNCTION REGISTER (SFR) SUMMARY

Legend:

x = unknown, u = unchanged, - = unimplemented, read as '0' (if applicable), q = value depends on condition. Shaded cells = unimplemented or unused

Note 1:

The upper byte of the Program Counter is not directly accessible. See Section 4.6 "Program Counter" for an explanation of how to

access these bits.

#### 4.4 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the <code>OPTION</code> instruction, the contents of the W register will be transferred to the <code>OPTION</code> register. A Reset sets the <code>OPTION <7:0></code> bits.

| Note: | If TRIS bit is set to '0', the wake-up on    |  |  |

|-------|----------------------------------------------|--|--|

|       | change and pull-up functions are disabled    |  |  |

|       | for that pin (i.e., note that TRIS overrides |  |  |

|       | Option control of RBPU and RBWU).            |  |  |

#### REGISTER 4-2: OPTION: OPTION REGISTER

| W-1   | W-1  | W-1                 | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|------|---------------------|------|-----|-----|-----|-------|

| RBWU  | RBPU | T0CS <sup>(1)</sup> | T0SE | PSA | PS2 | PS1 | PS0   |

| bit 7 | •    |                     |      | •   |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>RBWU:</b> Enable Wake-up On Pin Change bit (RB0, RB1, RB3, RB4)<br>1 = Disabled<br>0 = Enabled                                                          |                             |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|

| bit 6   | <b>RBPU:</b> Enable Weak Pull-ups bit (RB0, RB1, RB3, RB4)<br>1 = Disabled<br>0 = Enabled                                                                  |                             |  |  |  |  |  |

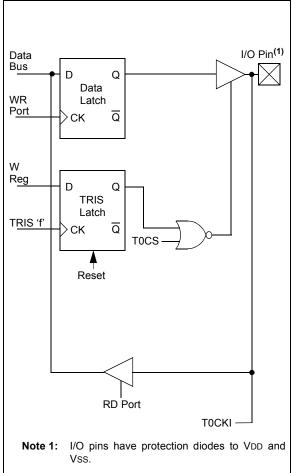

| bit 5   | <b>TOCS:</b> Timer0 Clock Source Select bit <sup>(1)</sup><br>1 = Transition on T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                 | 1 = Transition on T0CKI pin |  |  |  |  |  |

| bit 4   | <b>TOSE:</b> Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin |                             |  |  |  |  |  |

| bit 3   | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler assigned to the WDT</li> <li>0 = Prescaler assigned to Timer0</li> </ul>                     |                             |  |  |  |  |  |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                                                                        |                             |  |  |  |  |  |

|         | Bit Value Timer0 Rate WDT Rate                                                                                                                             |                             |  |  |  |  |  |

|         | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                     |                             |  |  |  |  |  |

Note 1: If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

#### 4.5 OSCCAL Register

The Oscillator Calibration (OSCCAL) register is used to calibrate the 8 MHz internal oscillator macro. It contains 7 bits of calibration that uses a two's complement scheme for controlling the oscillator speed. See Register 4-3 for details.

#### REGISTER 4-3: OSCCAL: OSCILLATOR CALIBRATION REGISTER

| R/W-1 | U-0   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | —     |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-1 CAL<6:0>: Oscillator Calibration bits 0111111 = Maximum frequency

bit 0

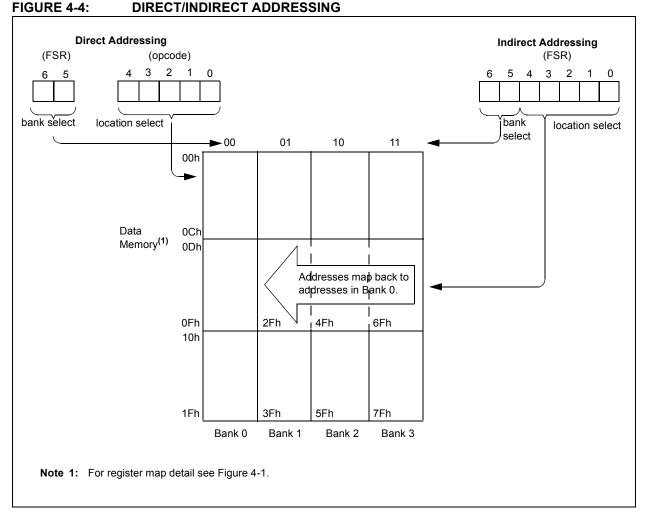

#### 4.8 Indirect Data Addressing: INDF and FSR Registers

The INDF Register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF Register indirectly results in a no-operation (although Status bits may be affected).

The FSR is an 8-bit wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = Bank 0, 01 = Bank 1, 10 = Bank 2, 11 = Bank 3).

FSR<7> is unimplemented and read as '1'.

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-1.

#### EXAMPLE 4-1: HOW TO CLEAR RAM **USING INDIRECT** ADDRESSING

| NEXT    | MOVLW<br>MOVWF<br>CLRF<br>INCF<br>BTFSC<br>GOTO | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | <pre>;initialize pointer ;to RAM ;clear INDF ;register ;inc pointer ;all done? ;NO, clear next</pre> |

|---------|-------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------|

| CONTINU | JE                                              |                                               |                                                                                                      |

|         | :                                               |                                               | ;YES, continue                                                                                       |

|         | :                                               |                                               |                                                                                                      |

|         |                                                 |                                               |                                                                                                      |

#### 5.0 FLASH DATA MEMORY CONTROL

The Flash data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFRs).

#### 5.1 Reading Flash Data Memory

To read a Flash data memory location the user must:

- Write the EEADR register

- · Set the RD bit of the EECON register

The value written to the EEADR register determines which Flash data memory location is read. Setting the RD bit of the EECON register initiates the read. Data from the Flash data memory read is available in the EEDATA register immediately. The EEDATA register will hold this value until another read is initiated or it is modified by a write operation. Program execution is suspended while the read cycle is in progress. Execution will continue with the instruction following the one that sets the WR bit. See Example 1 for sample code.

#### EXAMPLE 1: READING FROM FLASH DATA MEMORY

| BANKSEL EEADR        | ;                |

|----------------------|------------------|

| MOVF DATA_EE_ADDR, W | ;                |

| MOVWF EEADR          | ;Data Memory     |

|                      | ;Address to read |

| BANKSEL EECON1       | ;                |

|                      |                  |

| BSF EECON, RD        | ;EE Read         |

| MOVF EEDATA, W       | ;W = EEDATA      |

|                      |                  |

Note: Only a BSF command will work to enable the Flash data memory read documented in Example 1. No other sequence of commands will work, no exceptions.

#### 5.2 Writing and Erasing Flash Data Memory

Flash data memory is erased one row at a time and written one byte at a time. The 64-byte array is made up of eight rows. A row contains eight sequential bytes. Row boundaries exist every eight bytes.

Generally, the procedure to write a byte of data to Flash data memory is:

- 1. Identify the row containing the address where the byte will be written.

- 2. If there is other information in that row that must be saved, copy those bytes from Flash data memory to RAM.

- 3. Perform a row erase of the row of interest.

- 4. Write the new byte of data and any saved bytes back to the appropriate addresses in Flash data memory.

To prevent accidental corruption of the Flash data memory, an unlock sequence is required to initiate a write or erase cycle. This sequence requires that the bit set instructions used to configure the EECON register happen exactly as shown in Example 2 and Example 3, depending on the operation requested.

#### 5.2.1 ERASING FLASH DATA MEMORY

A row must be manually erased before writing new data. The following sequence must be performed for a single row erase.

- 1. Load EEADR with an address in the row to be erased.

- 2. Set the FREE bit to enable the erase.

- 3. Set the WREN bit to enable write access to the array.

- 4. Set the WR bit to initiate the erase cycle.

If the WREN bit is not set in the instruction cycle after the FREE bit is set, the FREE bit will be cleared in hardware.

If the WR bit is not set in the instruction cycle after the WREN bit is set, the WREN bit will be cleared in hardware.

Sample code that follows this procedure is included in Example 2.

Program execution is suspended while the erase cycle is in progress. Execution will continue with the instruction following the one that sets the WR bit.

#### EXAMPLE 2: ERASING A FLASH DATA MEMORY ROW

| BANKSEL | EEADR        |                          |

|---------|--------------|--------------------------|

| MOVLW   | EE_ADR_ERASE | ; LOAD ADDRESS OF ROW TO |

|         |              | ; ERASE                  |

| MOVWF   | EEADR        | ;                        |

| BSF     | EECON, FREE  | ; SELECT ERASE           |

| BSF     | EECON, WREN  | ; ENABLE WRITES          |

| BSF     | EECON, WR    | ; INITITATE ERASE        |

|         |              |                          |

- Note 1: The FREE bit may be set by any command normally used by the core. However, the WREN and WR bits can only be set using a series of BSF commands, as documented in Example 1. No other sequence of commands will work, no exceptions.

- **2:** Bits <5:3> of the EEADR register indicate which row is to be erased.

### PIC16F526

#### 7.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select:

- Edge select for external clock

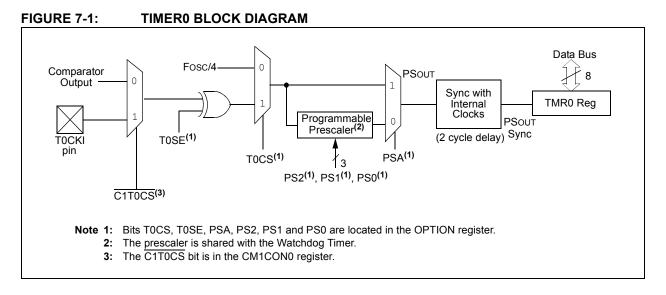

Figure 7-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit of the OPTION register. In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

There are two types of Counter mode. The first Counter mode uses the T0CKI pin to increment Timer0. It is selected by setting the T0CS bit of the OPTION register, setting the <u>C1T0CS</u> bit of the CM1CON0 register and setting the <u>C1OUTEN</u> bit of the CM1CON0 register. In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit of the OPTION register determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in **Section 7.1 "Using Timer0 with an External Clock"**.

The second Counter mode uses the output of the comparator to increment Timer0. It can be entered in two different ways. The first way is selected by setting the T0CS bit of the OPTION register, and clearing the C1T0CS bit of the CM1CON0 register (C10UTEN [CM1CON0<6>] does not affect this mode of operation). This enables an internal connection between the comparator and the Timer0.

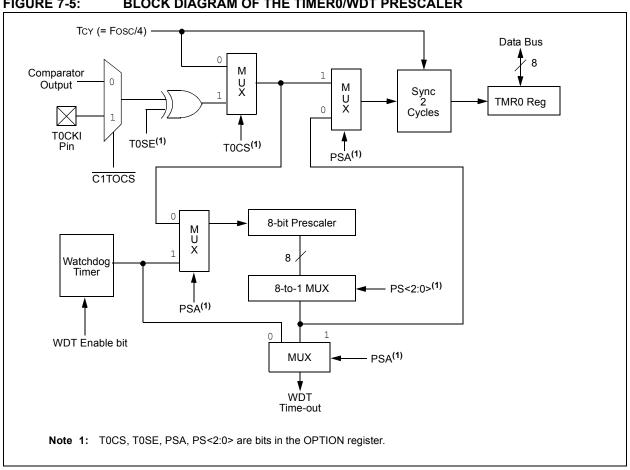

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA of the OPTION register. Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 7.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 7-1.

FIGURE 7-5: **BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER**

### 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of real-time applications. The PIC16F526 microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These features are:

- Oscillator Selection

- Reset:

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from Sleep on Pin Change

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- · ID Locations

- In-Circuit Serial Programming<sup>™</sup>

- Clock Out

The PIC16F526 device has a Watchdog Timer, which can be shut off only through Configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using HS, XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in Reset until the crystal oscillator is stable. If using INTRC or EXTRC, there is a 1 ms delay only on VDD power-up. With this timer on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low current Power-Down mode. The user can wake-up from Sleep through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4/8 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options.

#### 8.1 Configuration Bits

The PIC16F526 Configuration Words consist of 12 bits. Configuration bits can be programmed to select various device configurations. Three bits are for the selection of the oscillator type; one bit is the Watchdog Timer enable bit, one bit is the MCLR enable bit and one bit is for code protection (Register 8-1).

#### TABLE 8-4: RESET CONDITION FOR SPECIAL REGISTERS

|                                         | STATUS Addr: 03h |

|-----------------------------------------|------------------|

| Power-on Reset                          | 0001 1xxx        |

| MCLR Reset during normal operation      | 000u uuuu        |

| MCLR Reset during Sleep                 | 0001 0uuu        |

| WDT Reset during Sleep                  | 0000 Ouuu        |

| WDT Reset normal operation              | 0000 uuuu        |

| Wake-up from Sleep on pin change        | 1001 Ouuu        |

| Wake-up from Sleep on comparator change | 0101 Ouuu        |

**Legend:** u = unchanged, x = unknown, – = unimplemented bit, read as '0'.

| R-1           | R/W-1                                                                                                                                    | R/W-1           | R/W-1            | R/W-1                       | R/W-1           | R/W-1           | R/W-1 |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------------------|-----------------|-----------------|-------|--|--|--|

| C2OUT         | C2OUTEN                                                                                                                                  | C2POL           | C2PREF2          | C2ON                        | C2NREF          | C2PREF1         | C2WU  |  |  |  |

| bit 7         |                                                                                                                                          |                 |                  |                             |                 |                 | bit ( |  |  |  |

|               |                                                                                                                                          |                 |                  |                             |                 |                 |       |  |  |  |

| Legend:       |                                                                                                                                          |                 |                  |                             |                 |                 |       |  |  |  |

| R = Readable  |                                                                                                                                          | W = Writable    |                  | -                           | nented bit, rea |                 |       |  |  |  |

| -n = Value at | POR                                                                                                                                      | '1' = Bit is se | t                | '0' = Bit is cle            | ared            | x = Bit is unkn | own   |  |  |  |

| bit 7         | C2OUT: Com                                                                                                                               | parator Outpu   | t bit            |                             |                 |                 |       |  |  |  |

|               | 1 = VIN+ > VII                                                                                                                           | • •             |                  |                             |                 |                 |       |  |  |  |

|               | 0 = VIN + < VII                                                                                                                          | -               |                  |                             |                 |                 |       |  |  |  |

| bit 6         |                                                                                                                                          |                 | itput Enable bit |                             |                 |                 |       |  |  |  |

|               | <ul> <li>1 = Output of comparator is NOT placed on the C2OUT pin</li> <li>0 = Output of comparator is placed in the C2OUT pin</li> </ul> |                 |                  |                             |                 |                 |       |  |  |  |

|               | •                                                                                                                                        | •               | •                | C2OUT pin                   |                 |                 |       |  |  |  |

| bit 5         | <b>C2POL</b> : Comparator Output Polarity bit <sup>(2)</sup>                                                                             |                 |                  |                             |                 |                 |       |  |  |  |

|               | <ul> <li>1 = Output of comparator not inverted</li> <li>0 = Output of comparator inverted</li> </ul>                                     |                 |                  |                             |                 |                 |       |  |  |  |

| bit 4         | •                                                                                                                                        | •               | sitive Reference | e Select bit <sup>(2)</sup> |                 |                 |       |  |  |  |

|               | 1 = C1IN+ pir                                                                                                                            | •               |                  |                             |                 |                 |       |  |  |  |

|               | 0 = C2IN- pin                                                                                                                            |                 |                  |                             |                 |                 |       |  |  |  |

| bit 3         | C2ON: Comp                                                                                                                               | arator Enable   | bit              |                             |                 |                 |       |  |  |  |

|               | 1 = Comparator is on                                                                                                                     |                 |                  |                             |                 |                 |       |  |  |  |

|               | 0 = Compara                                                                                                                              |                 |                  |                             |                 |                 |       |  |  |  |

| bit 2         |                                                                                                                                          |                 | ative Reference  | e Select bit <sup>(2)</sup> |                 |                 |       |  |  |  |

|               | 1 = C2IN- pin<br>0 = CVREF                                                                                                               |                 |                  |                             |                 |                 |       |  |  |  |

| bit 1         |                                                                                                                                          | omparator Pos   | sitive Reference | a Salact hit(2)             |                 |                 |       |  |  |  |

|               | 1 = C2IN+ pir                                                                                                                            | •               |                  | e Select bit.               |                 |                 |       |  |  |  |

|               |                                                                                                                                          |                 | og input select  | ion                         |                 |                 |       |  |  |  |

| bit 0         | C2WU: Comp                                                                                                                               | parator Wake-   | up on Change     | Enable bit <sup>(2)</sup>   |                 |                 |       |  |  |  |

|               | 1 = Wake-up                                                                                                                              | on Comparato    | or change is dis | abled                       |                 |                 |       |  |  |  |

|               | 0 = Wake-up                                                                                                                              |                 | ,                | ablad                       |                 |                 |       |  |  |  |

#### REGISTER 10-2: CM2CON0: COMPARATOR C2 CONTROL REGISTER

2: When comparator is turned on, these control bits assert themselves. Otherwise, the other registers have precedence.

| Name    | Bit 7 | Bit 6   | Bit 5      | Bit 4                               | Bit 3 | Bit 2  | Bit 1   | Bit 0 | Value on POR | Value on All<br>Other Resets |

|---------|-------|---------|------------|-------------------------------------|-------|--------|---------|-------|--------------|------------------------------|

| STATUS  | RBWUF | CWUF    | PA0        | TO                                  | PD    | Z      | DC      | С     | 0001 1xxx    | qq0q quuu                    |

| CM1CON0 | C1OUT | C10UTEN | C1POL      | C1T0CS                              | C10N  | C1NREF | C1PREF  | C1WU  | q111 1111    | quuu uuuu                    |

| CM2CON0 | C2OUT | C2OUTEN | C2POL      | C2PREF2                             | C2ON  | C2NREF | C2PREF1 | C2WU  | q111 1111    | quuu uuuu                    |

| TRIS    | _     | —       | I/O Contro | I/O Control Register (PORTB, PORTC) |       |        |         |       | 11 1111      | 11 1111                      |

Legend: x = Unknown, u = Unchanged, - = Unimplemented, read as '0', q = Depends on condition.

#### 14.3 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

| 2. TppS |                                          |        |                |

|---------|------------------------------------------|--------|----------------|

| т       |                                          |        |                |

| F F     | requency                                 | T Time |                |

| Lower   | case subscripts (pp) and their meanings: |        |                |

| рр      |                                          |        |                |

| 2       | to                                       | mc     | MCLR           |

| ck      | CLKOUT                                   | osc    | Oscillator     |

| су      | Cycle time                               | OS     | OSC1           |

| drt     | Device Reset Timer                       | tO     | ТОСКІ          |

| io      | I/O port                                 | wdt    | Watchdog Timer |

| Uppero  | case letters and their meanings:         |        |                |

| S       |                                          |        |                |

| F       | Fall                                     | Р      | Period         |

| н       | High                                     | R      | Rise           |

| I       | Invalid (high-impedance)                 | V      | Valid          |

| L       | Low                                      | Z      | High-impedance |

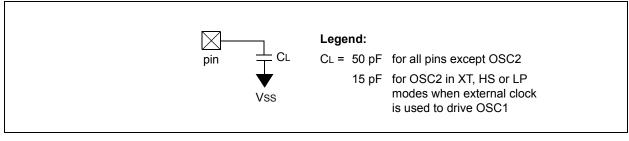

#### FIGURE 14-3: LOAD CONDITIONS

#### **16.0 PACKAGING INFORMATION**

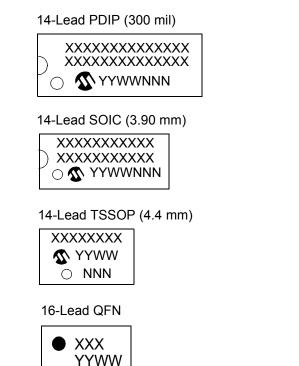

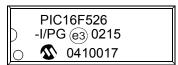

#### 16.1 Package Marking Information

Example

Example

| •           |  |

|-------------|--|

| PIC16F526-E |  |

| /SLG0125    |  |

| 🐼 0431017   |  |

Example

| -            |

|--------------|

| 16F526-I     |

| <b></b> 0431 |

| 017          |

|              |

Example

#### TABLE 16-1: 16-LEAD 3X3 QFN (MG) TOP MARKING

NNN

| Part Number    | Marking |

|----------------|---------|

| PIC16F526-I/MG | MG1     |

| PIC16F526-E/MG | MG2     |

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|-------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carried of                               | t the full Microchip part number cannot be marked on one line, it will<br>over to the next line thus limiting the number of available characters<br>er specific information.                                                                                                                                                                                                   |

\* Standard PIC<sup>®</sup> device marking consists of Microchip part number, year code, week code, and traceability code. For PIC device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

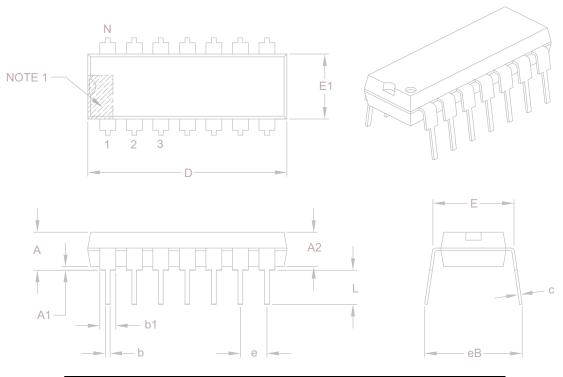

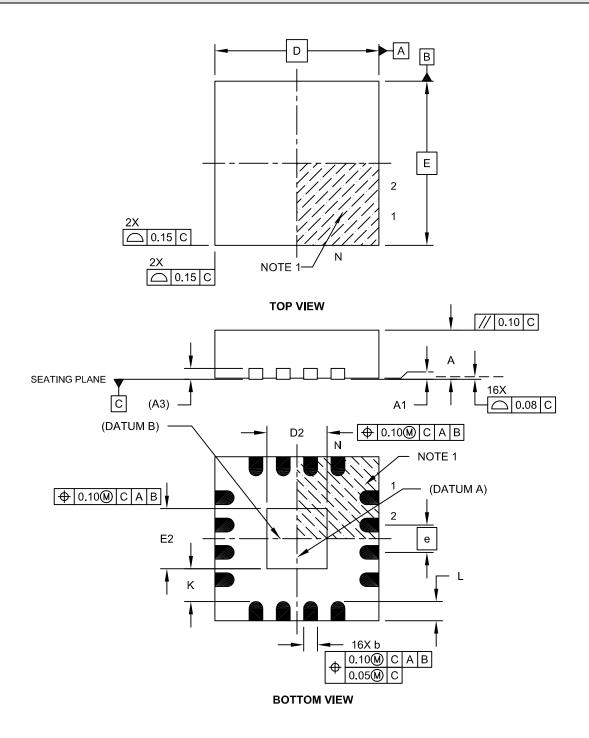

#### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      | INCHES   |      |

|----------------------------|----------|------|----------|------|

| Dimensio                   | n Limits | MIN  | NOM      | MAX  |

| Number of Pins             | Ν        |      | 14       |      |

| Pitch                      | е        |      | .100 BSC |      |

| Top to Seating Plane       | А        | -    | -        | .210 |

| Molded Package Thickness   | A2       | .115 | .130     | .195 |

| Base to Seating Plane      | A1       | .015 | -        | -    |

| Shoulder to Shoulder Width | E        | .290 | .310     | .325 |

| Molded Package Width       | E1       | .240 | .250     | .280 |

| Overall Length             | D        | .735 | .750     | .775 |

| Tip to Seating Plane       | L        | .115 | .130     | .150 |

| Lead Thickness             | с        | .008 | .010     | .015 |

| Upper Lead Width           | b1       | .045 | .060     | .070 |

| Lower Lead Width           | b        | .014 | .018     | .022 |

| Overall Row Spacing §      | eB       | _    | _        | .430 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

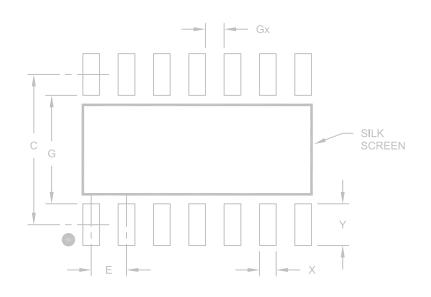

#### RECOMMENDED LAND PATTERN

|                       | Units        | MILLIMETERS |      |      |  |

|-----------------------|--------------|-------------|------|------|--|

| Dime                  | nsion Limits | MIN         | NOM  | MAX  |  |

| Contact Pitch         | E            | 1.27 BSC    |      |      |  |

| Contact Pad Spacing   | С            |             | 5.40 |      |  |

| Contact Pad Width     | Х            |             |      | 0.60 |  |

| Contact Pad Length    | Y            |             |      | 1.50 |  |

| Distance Between Pads | Gx           | 0.67        |      |      |  |

| Distance Between Pads | G            | 3.90        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

#### 16-Lead Plastic Quad Flat, No Lead Package (MG) - 3x3x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-142A Sheet 1 of 2

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com