# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 67 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 3x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f526-i-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 PIC16F526 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC16F526 Product Identification System at the back of this data sheet to specify the correct part number.

# 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

# 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry code, password or ID number.

| Addr               | Name    | Bit 7       | Bit 6                | Bit 5         | Bit 4         | Bit 3         | Bit 2        | Bit 1   | Bit 0 | Value on<br>Power-on<br>Reset | Page # |

|--------------------|---------|-------------|----------------------|---------------|---------------|---------------|--------------|---------|-------|-------------------------------|--------|

| N/A                | TRIS    | _           | —                    | I/O Control   | Register (PC  | ORTB, PORT    | IC)          |         |       | 11 1111                       | 27     |

| N/A                | OPTION  | Contains co | ontrol bits to c     | onfigure Tim  | ner0 and Tim  | er0/WDT pre   | escaler      |         |       | 1111 1111                     | 19     |

| 00h                | INDF    | Uses conte  | nts of FSR to        | Address Da    | ata Memory (i | not a physica | al register) |         |       | XXXX XXXX                     | 22     |

| 01h/41h            | TMR0    | Timer0 Mo   | dule Register        |               |               |               |              |         |       | XXXX XXXX                     | 37     |

| 02h <sup>(1)</sup> | PCL     | Low order   | 3 bits of PC         |               |               |               |              |         |       | 1111 1111                     | 21     |

| 03h                | STATUS  | RBWUF       | CWUF                 | PA0           | TO            | PD            | Z            | DC      | С     | 0001 1xxx                     | 18     |

| 04h                | FSR     | Indirect Da | ta Memory Ac         | Idress Pointe | er            |               | •            |         |       | 100x xxxx                     | 22     |

| 05h/45h            | OSCCAL  | CAL6        | CAL5                 | CAL4          | CAL3          | CAL2          | CAL1         | CAL0    | _     | 1111 111-                     | 20     |

| 06h/46h            | PORTB   | —           | —                    | RB5           | RB4           | RB3           | RB2          | RB1     | RB0   | xx xxxx                       | 27     |

| 07h                | PORTC   |             | _                    | RC5           | RC4           | RC3           | RC2          | RC1     | RC0   | xx xxxx                       | 28     |

| 08h                | CM1CON0 | C1OUT       | C10UTEN              | C1POL         | C1T0CS        | C10N          | C1NREF       | C1PREF  | C1WU  | q111 1111                     | 63     |

| 09h                | ADCON0  | ANS1        | ANS0                 | ADCS1         | ADCS0         | CHS1          | CHS0         | GO/DONE | ADON  | 1111 1100                     | 61     |

| 0Ah                | ADRES   | ADC Conve   | ersion Result        |               |               |               | •            |         |       | XXXX XXXX                     | 62     |

| 0Bh                | CM2CON0 | C2OUT       | C2OUTEN              | C2POL         | C2PREF2       | C2ON          | C2NREF       | C2PREF1 | C2WU  | q111 1111                     | 64     |

| 0Ch                | VRCON   | VREN        | VROE                 | VRR           |               | VR3           | VR2          | VR1     | VR0   | 001- 1111                     | 69     |

| 21h/61h            | EECON   | —           | —                    | _             | FREE          | WRERR         | WREN         | WR      | RD    | 0 x000                        | 23     |

| 25h/65h            | EEDATA  | SELF REA    | SELF READ/WRITE DATA |               |               |               |              |         |       | XXXX XXXX                     | 23     |

| 26h/66h            | EEADR   |             | —                    | SELF REA      | D/WRITE AD    | DRESS         |              |         |       | xx xxxx                       | 23     |

**TABLE 4-1:** SPECIAL FUNCTION REGISTER (SFR) SUMMARY

Legend:

x = unknown, u = unchanged, - = unimplemented, read as '0' (if applicable), q = value depends on condition. Shaded cells = unimplemented or unused

Note 1:

The upper byte of the Program Counter is not directly accessible. See Section 4.6 "Program Counter" for an explanation of how to

access these bits.

# 5.2.2 WRITING TO FLASH DATA MEMORY

Once a cell is erased, new data can be written. Program execution is suspended during the write cycle. The following sequence must be performed for a single byte write.

- 1. Load EEADR with the address.

- 2. Load EEDATA with the data to write.

- 3. Set the WREN bit to enable write access to the array.

- 4. Set the WR bit to initiate the erase cycle.

If the WR bit is not set in the instruction cycle after the WREN bit is set, the WREN bit will be cleared in hardware.

Sample code that follows this procedure is included in Example 3.

# EXAMPLE 3: WRITING A FLASH DATA MEMORY ROW

| BANKSEL | EEADR            |   |                      |

|---------|------------------|---|----------------------|

| MOVLW   | EE_ADR_WRITE     | ; | LOAD ADDRESS         |

| MOVWF   | EEADR            | ; |                      |

| MOVLW   | EE_DATA_TO_WRITE | ; | LOAD DATA            |

| MOVWF   | EEDATA           | ; | INTO EEDATA REGISTER |

| BSF     | EECON, WREN      | ; | ENABLE WRITES        |

| BSF     | EECON,WR         | ; | INITITATE ERASE      |

|         |                  |   |                      |

- Note 1: Only a series of BSF commands will work to enable the memory write sequence documented in Example 2. No other sequence of commands will work, no exceptions.

- 2: For reads, erases and writes to the Flash data memory, there is no need to insert a NOP into the user code as is done on mid-range devices. The instruction immediately following the "BSF EECON, WR/RD" will be fetched and executed properly.

# 5.3 Write Verify

Depending on the application, good programming practice may dictate that data written to the Flash data memory be verified. Example 4 is an example of a write verify.

# EXAMPLE 4: WRITE VERIFY OF FLASH DATA MEMORY

| MOVF  | EEDATA, W | ;EEDATA has not changed |

|-------|-----------|-------------------------|

|       |           | ;from previous write    |

| BSF   | EECON, RD | ;Read the value written |

| XORWF | EEDATA, W | ;                       |

| BTFSS | STATUS, Z | ;Is data the same       |

| GOTO  | WRITE_ERR | ;No, handle error       |

|       |           | ;Yes, continue          |

|       |           |                         |

## REGISTER 5-1: EEDATA: FLASH DATA REGISTER

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| EEDATA7 | EEDATA6 | EEDATA5 | EEDATA4 | EEDATA3 | EEDATA2 | EEDATA1 | EEDATA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 EEDATA<7:0>: 8-bits of data to be read from/written to data Flash

# REGISTER 5-2: EEADR: FLASH ADDRESS REGISTER

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | EEADR5 | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'.

bit 5-0 EEADR<5:0>: 6-bits of data to be read from/written to data Flash

# REGISTER 6-2: PORTC: PORTC REGISTER

| – RC5                              |     |                                         |                                    |     |       |  |  |

|------------------------------------|-----|-----------------------------------------|------------------------------------|-----|-------|--|--|

| 1.00                               | RC4 | RC3                                     | RC2                                | RC1 | RC0   |  |  |

|                                    | ·   | - <b>·</b>                              | ·                                  |     | bit 0 |  |  |

|                                    |     |                                         |                                    |     |       |  |  |

|                                    |     |                                         |                                    |     |       |  |  |

| R = Readable bit W = Writable bit  |     |                                         | U = Unimplemented bit, read as '0' |     |       |  |  |

| -n = Value at POR '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                                    |     |       |  |  |

| -                                  |     |                                         |                                    |     | • •   |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RC<5:0>: PORTC I/O Pin bits

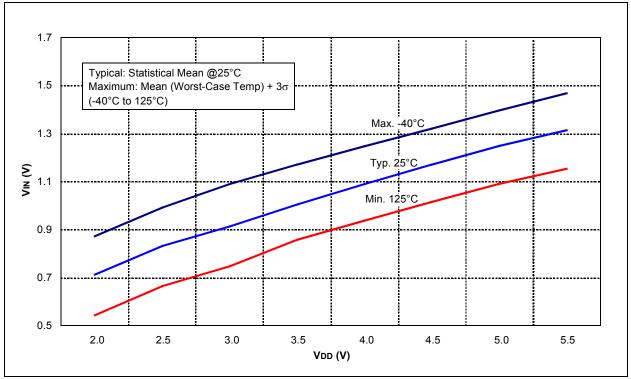

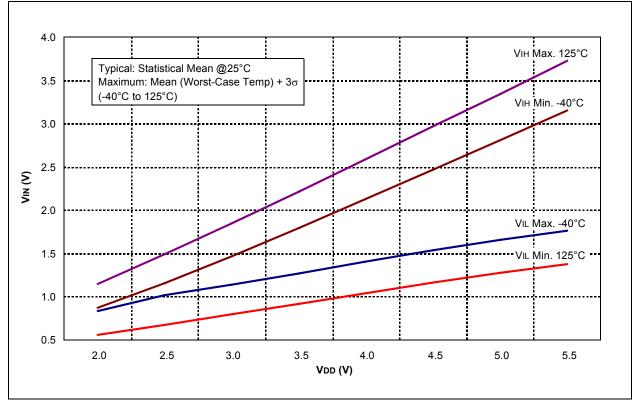

1 = Port pin is >VIH min.

0 = Port pin is <VIL max.

# PIC16F526

# 7.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select:

- Edge select for external clock

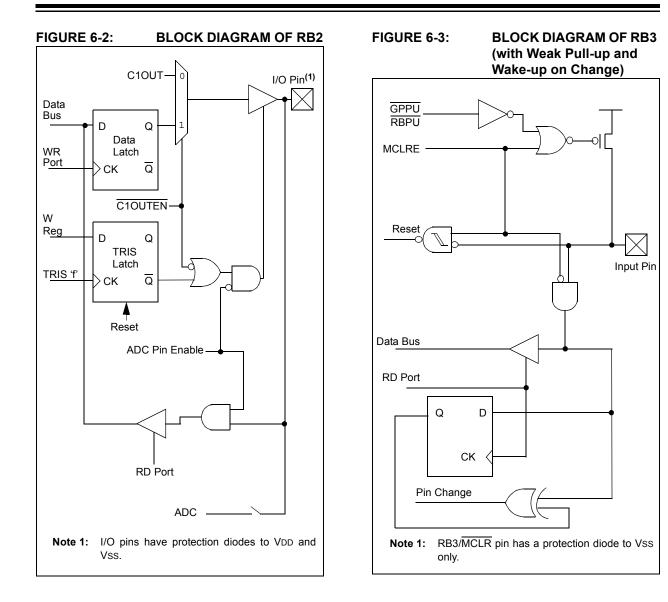

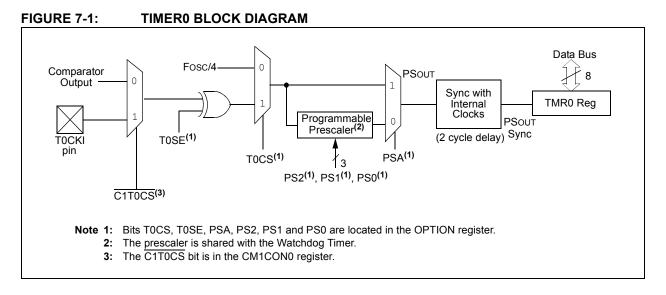

Figure 7-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit of the OPTION register. In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

There are two types of Counter mode. The first Counter mode uses the T0CKI pin to increment Timer0. It is selected by setting the T0CS bit of the OPTION register, setting the <u>C1T0CS</u> bit of the CM1CON0 register and setting the <u>C1OUTEN</u> bit of the CM1CON0 register. In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit of the OPTION register determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in **Section 7.1 "Using Timer0 with an External Clock"**.

The second Counter mode uses the output of the comparator to increment Timer0. It can be entered in two different ways. The first way is selected by setting the T0CS bit of the OPTION register, and clearing the C1T0CS bit of the CM1CON0 register (C10UTEN [CM1CON0<6>] does not affect this mode of operation). This enables an internal connection between the comparator and the Timer0.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA of the OPTION register. Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 7.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 7-1.

# 7.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see **Section 8.6** "Watchdog Timer (WDT)"). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the Timer0 module or the WDT, but not both. |

|-------|---------------------------------------------------------------------------------|

|       | Thus, a prescaler assignment for the Timer0 module means that there is no       |

|       | prescaler for the WDT and vice versa.                                           |

The PSA and PS<2:0> bits of the OPTION register determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

## 7.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| CLRWDT |             | ;Clear WDT              |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| MOVLW  | b'00xx1111' |                         |

| CLRWDT |             | ;PS<2:0> are 000 or 001 |

| MOVLW  | b'00xx1xxx' | ;Set Postscaler to      |

| OPTION |             | ;desired WDT rate       |

|        |             |                         |

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

| EXAMPLE 7-2: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (WDT $\rightarrow$ TIMER0) |

| CLRWDT  |            | ;Clear WDT and      |

|---------|------------|---------------------|

|         |            | ;prescaler          |

| MOVLW b | 'xxxx0xxx' | ;Select TMR0, new   |

|         |            | ;prescale value and |

|         |            | ;clock source       |

| OPTION  |            |                     |

## TABLE 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR<sup>(2)</sup>

| Osc<br>Type | Resonator<br>Freq.                           | Cap. Range<br>C1                                                                                     | Cap. Range<br>C2                               |

|-------------|----------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------|

| LP          | 32 kHz <sup>(1)</sup>                        | 15 pF                                                                                                | 15 pF                                          |

| ХТ          | 200 kHz<br>1 MHz<br>4 MHz                    | 47-68 pF<br>15 pF<br>15 pF                                                                           | 47-68 pF<br>15 pF<br>15 pF                     |

| HS          | 20 MHz                                       | 15-47 pF                                                                                             | 15-47 pF                                       |

| Note 1:     | For VDD > 4<br>recommend                     | .5V, C1 = C2 ≈<br>ed.                                                                                | 30 pF is                                       |

| 2:          | only. Rs ma<br>driving cryst<br>cation. Sinc | es are for design<br>y be required to<br>als with low drive<br>e each crystal h<br>ics, the user sho | avoid over-<br>ve level specifi-<br>as its own |

8.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

the crystal manufacturer for appropriate values of external components.

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

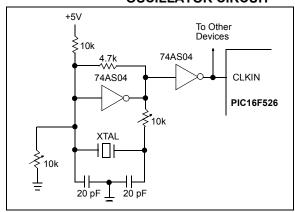

Figure 8-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

### FIGURE 8-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

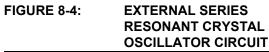

Figure 8-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

# 8.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit-to-unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 8-5 shows how the R/C combination is connected to the PIC16F526 device. For REXT values below 3.0 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 5.0 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

**Section 14.0 "Electrical Characteristics"** shows RC frequency variation from part-to-part due to normal process variation. The variation is larger for larger values of R (since leakage current variation will affect RC frequency more for large R) and for smaller values of C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications section for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

FIGURE 8-5: EXTERNAL RC OSCILLATOR MODE

# 8.2.5 INTERNAL 4/8 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4/8 MHz (nominal) system clock at VDD = 5V and  $25^{\circ}C$ , (see **Section 14.0** "**Electrical Characteristics**" for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal RC oscillator. This location is always non-code protected, regardless of the codeprotect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

Note: Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part so it can be reprogrammed correctly later.

For the PIC16F526 device, only bits 7:1 of OSCCAL are used for calibration. See Register 4-3 for more information.

Note: The bit 0 of the OSCCAL register is unimplemented and should be written as '0' when modifying OSCCAL for compatibility with future devices.

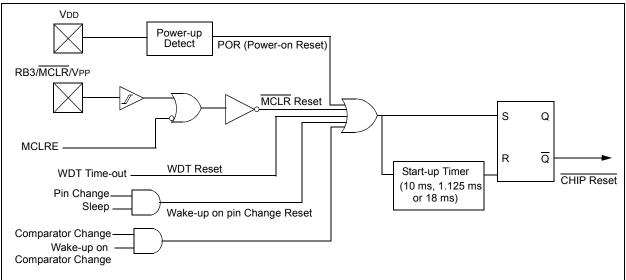

# 8.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Time-out Reset during normal operation

- WDT Time-out Reset during Sleep

- · Wake-up from Sleep on pin change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They are not affected by a WDT Reset during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are TO, PD and RBWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 8-3 for a full description of Reset states of all registers.

| Register | Address | Power-on Reset                  | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change |

|----------|---------|---------------------------------|----------------------------------------------------|

| W        | _       | qqqq qqq <b>0<sup>(1)</sup></b> | qqqq qqq0 <sup>(1)</sup>                           |

| INDF     | 00h     | XXXX XXXX                       | սսսս սսսս                                          |

| TMR0     | 01h     | XXXX XXXX                       | սսսս սսսս                                          |

| PCL      | 02h     | 1111 1111                       | 1111 1111                                          |

| STATUS   | 03h     | 0001 1xxx                       | qq0q quuu <sup>(2)</sup>                           |

| FSR      | 04h     | 100x xxxx                       | 1uuu uuuu                                          |

| OSCCAL   | 05h     | 1111 111-                       | uuuu uuu-                                          |

| PORTB    | 06h     | xx xxxx                         | uu uuuu                                            |

| PORTC    | 07h     | xx xxxx                         | uu uuuu                                            |

| CMICON0  | 08h     | q111 1111                       | quuu uuuu                                          |

| ADCON0   | 09h     | 1111 1100                       | 1111 1100                                          |

| ADRES    | 0Ah     | XXXX XXXX                       | นนนน นนนน                                          |

| CM2CON0  | 0Bh     | q111 1111                       | quuu uuuu                                          |

| VRCON    | 0Ch     | 001-1111                        | นนน-นนนน                                           |

| OPTION   | -       | 1111 1111                       | 1111 1111                                          |

| TRISB    | -       | 11 1111                         | 11 1111                                            |

| TRISC    | -       | 11 1111                         | 11 1111                                            |

| EECON    | 21h/61h | 0 x000                          | 0 q000                                             |

| EEDATA   | 25h/65h | XXXX XXXX                       | սսսս սսսս                                          |

| EEADR    | 26h/66h | xx xxxx                         | uu uuuu                                            |

# TABLE 8-3: RESET CONDITIONS FOR REGISTERS

**Legend:** u = unchanged, x = unknown, – = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:1> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 8-4 for Reset value for specific conditions.

# TABLE 8-4: RESET CONDITION FOR SPECIAL REGISTERS

|                                         | STATUS Addr: 03h |

|-----------------------------------------|------------------|

| Power-on Reset                          | 0001 1xxx        |

| MCLR Reset during normal operation      | 000u uuuu        |

| MCLR Reset during Sleep                 | 0001 Ouuu        |

| WDT Reset during Sleep                  | 0000 Ouuu        |

| WDT Reset normal operation              | 0000 uuuu        |

| Wake-up from Sleep on pin change        | 1001 Ouuu        |

| Wake-up from Sleep on comparator change | 0101 0uuu        |

**Legend:** u = unchanged, x = unknown, – = unimplemented bit, read as '0'.

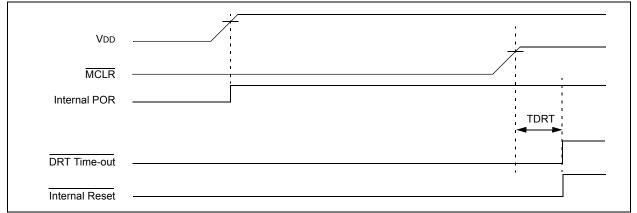

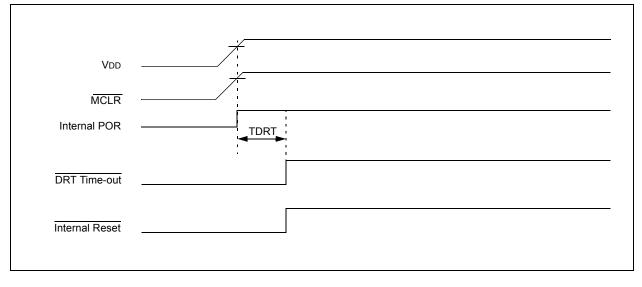

# FIGURE 8-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

# PIC16F526

# 9.1.5 SLEEP

This ADC does not have a dedicated ADC clock, and therefore, no conversion in Sleep is possible. If a conversion is underway and a Sleep command is executed, the GO/DONE and ADON bit will be cleared. This will stop any conversion in process and powerdown the ADC module to conserve power. Due to the nature of the conversion process, the ADRES may contain a partial conversion. At least 1 bit must have been converted prior to Sleep to have partial conversion data in ADRES. The ADCS and CHS bits are reset to their default condition; ANS<1:0> = 11 and CHS<1:0> = 11.

- For accurate conversions, TAD must meet the following:

- + 500 ns < TAD < 50  $\mu s$

- TAD = 1/(FOSC/divisor)

Shaded areas indicate TAD out of range for accurate conversions. If analog input is desired at these frequencies, use INTOSC/8 for the ADC clock source.

| Source | ADCS<br><1:0> | Divisor | 20<br>MHz | 16<br>MHz | 8 MHz        | 4 MHz | 1 MHz | 500<br>kHz    | 350<br>kHz | 200<br>kHz | 100<br>kHz | 32 kHz |

|--------|---------------|---------|-----------|-----------|--------------|-------|-------|---------------|------------|------------|------------|--------|

| INTOSC | 11            | 4       |           |           | .5 μs        | 1 μs  |       |               |            |            | _          |        |

| FOSC   | 10            | 4       | .2 μs     | .25 μs    | .5 μs        | 1 μs  | 4 μs  | 8 μ <b>s</b>  | 11 μs      | 20 μs      | 40 μs      | 125 μs |

| FOSC   | 01            | 8       | .4 μs     | .5 μs     | 1 μs         | 2 μs  | 8 μs  | 16 μs         | 23 μs      | 40 μs      | 80 μs      | 250 μs |

| FOSC   | 00            | 16      | .8 μs     | 1 μs      | 2 μ <b>s</b> | 4 μs  | 16 μs | 32 μ <b>s</b> | 46 μs      | 80 µS      | 160 μs     | 500 μs |

TABLE 9-2: TAD FOR ADCS SETTINGS WITH VARIOUS OSCILLATORS

# TABLE 9-3: EFFECTS OF SLEEP ON ADCON0

|                   | ANS1      | ANS0      | ADCS1 | ADCS0 | CHS1 | CHS0 | GO/DONE | ADON |

|-------------------|-----------|-----------|-------|-------|------|------|---------|------|

| Entering<br>Sleep | Unchanged | Unchanged | 1     | 1     | 1    | 1    | 0       | 0    |

| Wake or<br>Reset  | 1         | 1         | 1     | 1     | 1    | 1    | 0       | 0    |

| Name    | Bit 7 | Bit 6   | Bit 5      | Bit 4                               | Bit 3 | Bit 2  | Bit 1   | Bit 0 | Value on POR | Value on All<br>Other Resets |

|---------|-------|---------|------------|-------------------------------------|-------|--------|---------|-------|--------------|------------------------------|

| STATUS  | RBWUF | CWUF    | PA0        | TO                                  | PD    | Z      | DC      | С     | 0001 1xxx    | qq0q quuu                    |

| CM1CON0 | C1OUT | C10UTEN | C1POL      | C1T0CS                              | C10N  | C1NREF | C1PREF  | C1WU  | q111 1111    | quuu uuuu                    |

| CM2CON0 | C2OUT | C2OUTEN | C2POL      | C2PREF2                             | C2ON  | C2NREF | C2PREF1 | C2WU  | q111 1111    | quuu uuuu                    |

| TRIS    | _     | —       | I/O Contro | I/O Control Register (PORTB, PORTC) |       |        |         |       | 11 1111      | 11 1111                      |

Legend: x = Unknown, u = Unchanged, - = Unimplemented, read as '0', q = Depends on condition.

# 14.2 DC Characteristics: PIC16F526 (Extended)

| DC Cha       | aracteris      | tics                                                            |       |                     |             |          | has (unless otherwise specified)<br>$\leq TA \leq +125^{\circ}C$ (extended)                               |

|--------------|----------------|-----------------------------------------------------------------|-------|---------------------|-------------|----------|-----------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym.           | Characteristic                                                  | Min.  | Тур. <sup>(1)</sup> | Max.        | Units    | Conditions                                                                                                |

| D001         | Vdd            | Supply Voltage                                                  | 2.0   |                     | 5.5         | V        | See Figure 14-1                                                                                           |

| D002         | Vdr            | RAM Data Retention Voltage <sup>(2)</sup>                       |       | 1.5*                |             | V        | Device in Sleep mode                                                                                      |

| D003         | VPOR           | VDD Start Voltage to ensure<br>Power-on Reset                   | -     | Vss                 |             | V        | See Section 8.4 "Power-on<br>Reset (POR)" for details                                                     |

| D004         | SVDD           | VDD Rise Rate to ensure<br>Power-on Reset                       | 0.05* | —                   |             | V/ms     | See Section 8.4 "Power-on<br>Reset (POR)" for details                                                     |

| D005         | IDDP           | Supply Current During Prog/<br>Erase                            | —     | 250*                |             | μA       |                                                                                                           |

| D010         | IDD            | Supply Current <sup>(3,4,6)</sup>                               | _     | 175<br>400          | 250<br>700  | μΑ<br>μΑ | Fosc = 4 MHz, Vdd = 2.0V<br>Fosc = 4 MHz, Vdd = 5.0V                                                      |

|              |                |                                                                 | _     | 250<br>0.75         | 400<br>1.2  | μA<br>mA | Fosc = 8 MHz, VDD = 2.0V<br>Fosc = 8 MHz, VDD = 5.0V                                                      |

|              |                |                                                                 |       | 1.4                 | 2.2         | mA       | Fosc = 20 MHz, VDD = 5.0V                                                                                 |

|              |                |                                                                 | _     | 11<br>38            | 26<br>110   | μA<br>μA | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                                                    |

| D020         | IPD            | Power-down Current <sup>(5)</sup>                               | _     | 0.1<br>0.35         | 9.0<br>15.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                                                  |

| D022         | Iwdt           | WDT Current <sup>(5)</sup>                                      | _     | 1.0<br>7.0          | 18<br>22    | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                                                  |

| D023         | ICMP           | Comparator Current <sup>(5)</sup>                               | _     | 15<br>60            | 26<br>76    | μΑ<br>μΑ | VDD = 2.0V (per comparator)<br>VDD = 5.0V (per comparator)                                                |

| D022         | ICVREF         | CvREF Current <sup>(5)</sup>                                    | _     | 30<br>75            | 75<br>135   | μΑ<br>μΑ | VDD = 2.0V (high range)<br>VDD = 5.0V (high range)                                                        |

| D023         | IFVR           | Internal 0.6V Fixed Voltage<br>Reference Current <sup>(5)</sup> |       | 100<br>175          | 130<br>220  | μΑ<br>μΑ | V <sub>DD</sub> = 2.0V (reference and 1<br>comparator enabled)<br>V <sub>DD</sub> = 5.0V (reference and 1 |

| D004         | 414-5*         |                                                                 |       | 400                 | 450         | •        | comparator enabled)                                                                                       |

| D024         | $\Delta IAD^*$ | A/D Conversion Current                                          |       | 120                 | 150         | μA       | 2.0V                                                                                                      |

|              |                |                                                                 | —     | 200                 | 250         | μA       | 5.0V                                                                                                      |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**2:** This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

**3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

**4:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

**5:** For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

**6:** For EXTRC mode, does not include current through REXT. The current through the resistor can be estimated by the formula:

I = VDD/2REXT (mA) with REXT in  $k\Omega$ .

| AC CH        | ARACTE | ERISTICS                                | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ (industrial)}, \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ (extended)} \end{array}$ |        |        |     |                       |  |  |  |

|--------------|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-----|-----------------------|--|--|--|

|              |        |                                         | Operating Voltage VDD range is described in Section 14.1 "DC Characteristics: PIC16F526 (Industrial)"                                                                                                                                                        |        |        |     |                       |  |  |  |

| Param<br>No. | Sym.   | Characteristic                          | Conditions                                                                                                                                                                                                                                                   |        |        |     |                       |  |  |  |

| 1A           | Fosc   | External CLKIN Frequency <sup>(2)</sup> | DC                                                                                                                                                                                                                                                           | —      | 4      | MHz | XT Oscillator mode    |  |  |  |

|              |        |                                         | DC                                                                                                                                                                                                                                                           | —      | 20     | MHz | HS/EC Oscillator mode |  |  |  |

|              |        |                                         | DC                                                                                                                                                                                                                                                           | —      | 200    | kHz | LP Oscillator mode    |  |  |  |

|              |        | Oscillator Frequency <sup>(2)</sup>     | -                                                                                                                                                                                                                                                            | —      | 4      | MHz | EXTRC Oscillator mode |  |  |  |

|              |        |                                         | 0.1                                                                                                                                                                                                                                                          | —      | 4      | MHz | XT Oscillator mode    |  |  |  |

|              |        |                                         | 4                                                                                                                                                                                                                                                            | —      | 20     | MHz | HS/EC Oscillator mode |  |  |  |

|              |        |                                         | —                                                                                                                                                                                                                                                            | _      | 200    | kHz | LP Oscillator mode    |  |  |  |

| 1            | Tosc   | External CLKIN Period <sup>(2)</sup>    | 250                                                                                                                                                                                                                                                          | —      | —      | ns  | XT Oscillator mode    |  |  |  |

|              |        |                                         | 50                                                                                                                                                                                                                                                           | —      | —      | ns  | HS/EC Oscillator mode |  |  |  |

|              |        |                                         | 5                                                                                                                                                                                                                                                            | _      | _      | μS  | LP Oscillator mode    |  |  |  |

|              |        | Oscillator Period <sup>(2)</sup>        | 250                                                                                                                                                                                                                                                          | —      | —      | ns  | EXTRC Oscillator mode |  |  |  |

|              |        |                                         | 250                                                                                                                                                                                                                                                          | —      | 10,000 | ns  | XT Oscillator mode    |  |  |  |

|              |        |                                         | 50                                                                                                                                                                                                                                                           | —      | 250    | ns  | HS/EC Oscillator mode |  |  |  |

|              |        |                                         | 5                                                                                                                                                                                                                                                            | —      | —      | μS  | LP Oscillator mode    |  |  |  |

| 2            | Тсү    | Instruction Cycle Time                  | 200                                                                                                                                                                                                                                                          | 4/Fosc | —      | ns  |                       |  |  |  |

| 3            | TosL,  | Clock in (OSC1) Low or High             | 50*                                                                                                                                                                                                                                                          | _      | _      | ns  | XT Oscillator         |  |  |  |

|              | TosH   | Time                                    | 2*                                                                                                                                                                                                                                                           | —      | —      | μS  | LP Oscillator         |  |  |  |

|              |        |                                         | 10*                                                                                                                                                                                                                                                          | —      | —      | ns  | HS/EC Oscillator      |  |  |  |

| 4            | TosR,  | Clock in (OSC1) Rise or Fall            | —                                                                                                                                                                                                                                                            | _      | 25*    | ns  | XT Oscillator         |  |  |  |

|              | TosF   | Time                                    | —                                                                                                                                                                                                                                                            | —      | 50*    | ns  | LP Oscillator         |  |  |  |

|              |        |                                         | —                                                                                                                                                                                                                                                            | _      | 15*    | ns  | HS/EC Oscillator      |  |  |  |

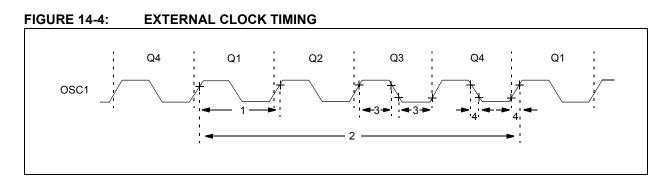

## TABLE 14-6: EXTERNAL CLOCK TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

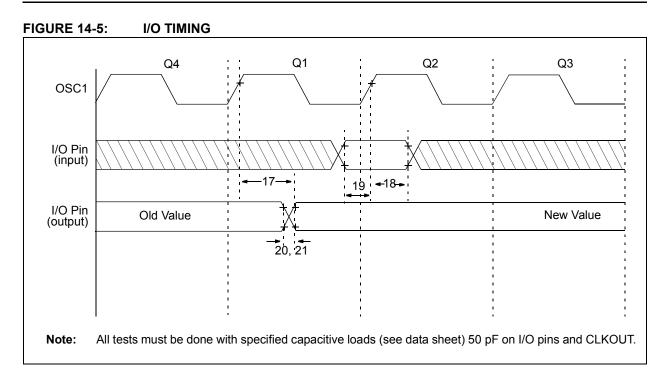

# TABLE 14-8: TIMING REQUIREMENTS

| AC       Operating Temperature       -40°C ≤ TA ≤ +85°C (industrial)         -40°C ≤ TA ≤ +125°C (extended)         Operating Voltage VDD range is described in Section 14.1 "DC Characteristics: PIC"         (Industrial)" |                                              |                                                                                      |    |      |      | 16F526 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|----|------|------|--------|--|

| Param<br>No.                                                                                                                                                                                                                 | Sym.                                         | Characteristic Min. Typ. <sup>(1)</sup> Max.                                         |    |      |      |        |  |

| 17                                                                                                                                                                                                                           | TosH2ıoV                                     | OSC1↑ (Q1 cycle) to Port Out Valid <sup>(2), (3)</sup>                               | _  | _    | 100* | ns     |  |

| 18                                                                                                                                                                                                                           | TosH2iol                                     | OSC1 <sup>↑</sup> (Q2 cycle) to Port Input Invalid (I/O in hold time) <sup>(2)</sup> | 50 | —    | _    | ns     |  |

| 19                                                                                                                                                                                                                           | TIOV20sH                                     | Port Input Valid to OSC1 <sup>↑</sup> (I/O in setup time)                            | 20 |      | _    | ns     |  |

| 20                                                                                                                                                                                                                           | 20 TIOR Port Output Rise Time <sup>(3)</sup> |                                                                                      | _  | 10   | 50** | ns     |  |

| 21 TIOF Port Output Fall Time <sup>(3)</sup>                                                                                                                                                                                 |                                              |                                                                                      | 10 | 58** | ns   |        |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: Measurements are taken in EXTRC mode.

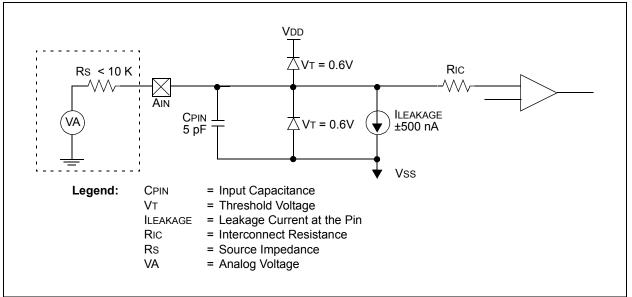

**3:** See Figure 14-3 for loading conditions.

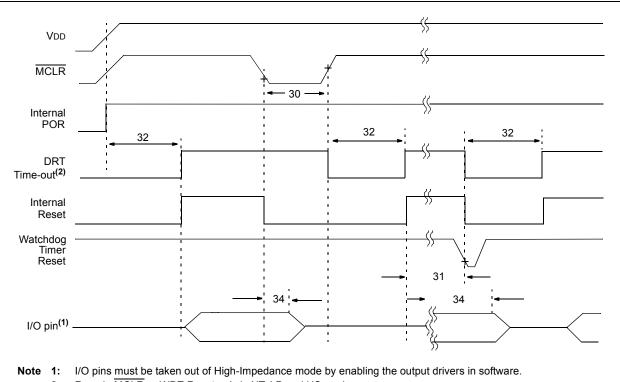

#### FIGURE 14-6: **RESET, WATCHDOG TIMER AND DEVICE RESET TIMER TIMING**

Runs in MCLR or WDT Reset only in XT, LP and HS modes. 2:

# TABLE 14-9: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER

|      |                                               |                                                                                                                                                                                | Standard Operating Conditions (unless otherwise specifiedOperating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)Operating Voltage VDD range is described inSection 14.1 "DC Characteristics: PIC16F526 (Industrial)"                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Sym. | Characteristic                                | Min.                                                                                                                                                                           | Typ. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                      | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Units                                                                                                                                                                                                                                                                                                                                          | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TMCL | MCLR Pulse Width (low)                        | 2000*                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                             | VDD = 5.0V                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Twdt | Watchdog Timer Time-out Period (no prescaler) | 9*<br>9*                                                                                                                                                                       | 18*<br>18*                                                                                                                                                                                                                                                                                                                                               | 30*<br>40*                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ms<br>ms                                                                                                                                                                                                                                                                                                                                       | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended)                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TDRT | Device Reset Timer Period                     |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|      | Standard                                      | 9*<br>9*                                                                                                                                                                       | 18*<br>18*                                                                                                                                                                                                                                                                                                                                               | 30*<br>40*                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ms<br>ms                                                                                                                                                                                                                                                                                                                                       | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended)                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|      | Short                                         | 0.5*<br>0.5*                                                                                                                                                                   | 1.125*<br>1.125*                                                                                                                                                                                                                                                                                                                                         | 2*<br>2.5*                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ms<br>ms                                                                                                                                                                                                                                                                                                                                       | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended)                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Tioz | I/O High-impedance from MCLR low              | —                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                                                        | 2000*                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ns                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|      | Sym.<br>TMCL<br>TWDT<br>TDRT                  | Sym.CharacteristicTMCLMCLR Pulse Width (low)TWDTWatchdog Timer Time-out Period<br>(no prescaler)TDRTDevice Reset Timer PeriodStandardStandardShortI/O High-impedance from MCLR | ARACTERISTICS     Operating       Sym.     Characteristic     Operating       TMCL     MCLR Pulse Width (low)     2000*       TWDT     Watchdog Timer Time-out Period (no prescaler)     9*       TDRT     Device Reset Timer Period     9*       Standard     9*       9*     9*       Short     0.5*       TIOZ     I/O High-impedance from MCLR     — | ARACTERISTICS       Operating Temp         Sym.       Characteristic       Min.       Typ.(1)         TMCL       MCLR Pulse Width (low)       2000*       —         TWDT       Watchdog Timer Time-out Period<br>(no prescaler)       9*       18*         TDRT       Device Reset Timer Period       9*       18*         Standard       9*       18*         Short       0.5*       1.125*         TIOZ       I/O High-impedance from MCLR       —       — | ARACTERISTICSOperating Temperature<br>Operating Voltage VDD in<br>Section 14.1 "DC CharaSym.CharacteristicMin.Typ.(1)Max.TMCLMCLR Pulse Width (low)2000*TWDTWatchdog Timer Time-out Period<br>(no prescaler)9*18*30*<br>40*TDRTDevice Reset Timer Period9*18*40*Standard9*18*40*Short0.5*1.125*2*<br>2.5*TIOZI/O High-impedance from MCLR2000* | Operating Temperature $-40^{\circ}C \le -40^{\circ}C \le -40^{\circ}C \le 0$<br>Operating Voltage VDD range is of Section 14.1 "UC CharacteristicSym.CharacteristicMin.Typ.(1)Max.UnitsTMCLMCLR Pulse Width (low) $2000^{\circ}$ ——nsTWDTWatchdog Timer Time-out Period<br>(no prescaler)9*18*30*msTDRTDevice Reset Timer Period9*18*40*msTDRTStandard9*18*40*msShort $0.5^{*}$ $1.125^{*}$ 2*msTIOZI/O High-impedance from MCLR——2000*ns |  |  |  |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

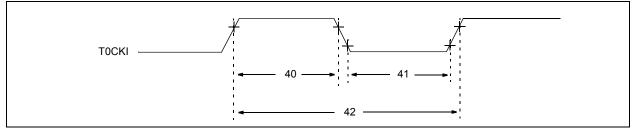

# FIGURE 14-7: TIMER0 CLOCK TIMINGS

# TABLE 14-10: TIMER0 CLOCK REQUIREMENT

| AC CHARACTERISTICS |      |                           | $\label{eq:standard operating Conditions (unless otherwise specified)} Operating Temperature -40°C \leq Ta \leq +85°C (industrial) \\ -40°C \leq Ta \leq +125°C (extended) \\ Operating Voltage VDD range is described in \\ Section 14.1 "DC Characteristics: PIC16F526 (Industrial)"$ |                   |                     |      |       |                                                                |

|--------------------|------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------|-------|----------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic            |                                                                                                                                                                                                                                                                                         | Min.              | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |

| 40                 | Tt0H | T0CKI High Pulse<br>Width | No Prescaler                                                                                                                                                                                                                                                                            | 0.5 Tcy + 20*     | _                   | _    | ns    |                                                                |

|                    |      |                           | With Prescaler                                                                                                                                                                                                                                                                          | 10*               | _                   | _    | ns    |                                                                |

| 41                 | TtOL | T0CKI Low Pulse<br>Width  | No Prescaler                                                                                                                                                                                                                                                                            | 0.5 Tcy + 20*     | _                   | —    | ns    |                                                                |

|                    |      |                           | With Prescaler                                                                                                                                                                                                                                                                          | 10*               | —                   |      | ns    |                                                                |

| 42                 | Tt0P | T0CKI Period              |                                                                                                                                                                                                                                                                                         | 20 or Tcy + 40* N |                     |      | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.