Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core ProcessorPICCore Size8-BitSpeed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                             | Details                    |                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size8-BitCore Size20MHzSpeed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14.TSSOP (0.173", 4.40mm Width)Supplier Device Package14.TSSOP | Product Status             | Active                                                                   |

| Speed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                            | Core Processor             | PIC                                                                      |

| Connectivity-Connectivity-PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                         | Core Size                  | 8-Bit                                                                    |

| PeripheralsPOR, WDTNumber of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                   | Speed                      | 20MHz                                                                    |

| Number of I/O11Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                      | Connectivity               | -                                                                        |

| Program Memory Size1.5KB (1K x 12)Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                                     | Peripherals                | POR, WDT                                                                 |

| Program Memory TypeFLASHEEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                                                                       | Number of I/O              | 11                                                                       |

| EEPROM Size-RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                | Program Memory Size        | 1.5KB (1K x 12)                                                          |

| RAM Size67 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                            | Program Memory Type        | FLASH                                                                    |

| Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                          | EEPROM Size                | -                                                                        |

| Data ConvertersA/D 3x8bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                             | RAM Size                   | 67 x 8                                                                   |

| Oscillator Type     Internal       Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     14-TSSOP (0.173", 4.40mm Width)       Supplier Device Package     14-TSSOP                                                                                                                                                                               | Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                           | Data Converters            | A/D 3x8b                                                                 |

| Mounting Type     Surface Mount       Package / Case     14-TSSOP (0.173", 4.40mm Width)       Supplier Device Package     14-TSSOP                                                                                                                                                                                                                                                                    | Oscillator Type            | Internal                                                                 |

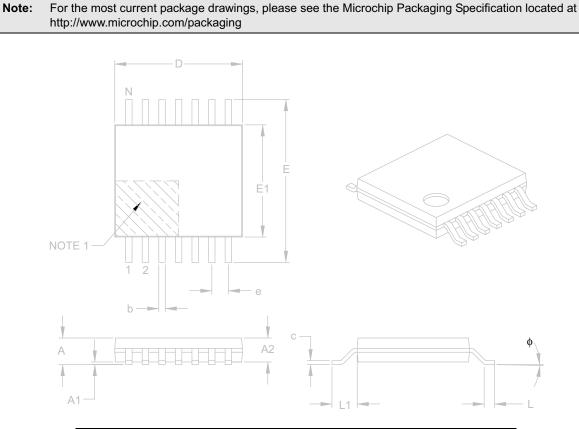

| Package / Case 14-TSSOP (0.173", 4.40mm Width) Supplier Device Package 14-TSSOP                                                                                                                                                                                                                                                                                                                        | Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Supplier Device Package 14-TSSOP                                                                                                                                                                                                                                                                                                                                                                       | Mounting Type              | Surface Mount                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                        | Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic16f526-i-st                                                                                                                                                                                                                                                                                                                  | Supplier Device Package    | 14-TSSOP                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                        | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f526-i-st |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16F526 device can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16F526 device uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architectures where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide, making it possible to have all single-word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (200 ns @ 20 MHz, 1 µs @ 4 MHz) except for program branches.

Table 3-1 below lists memory supported by the PIC16F526 device.

TABLE 3-1: PIC16F526 MEMORY

| Device    | Program<br>Memory | Data Me         | emory            |

|-----------|-------------------|-----------------|------------------|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | Flash<br>(bytes) |

| PIC16F526 | 1024              | 67              | 64               |

The PIC16F526 device can directly or indirectly address its register files and data memory. All Special Function Registers (SFR), including the PC, are mapped in the data memory. The PIC16F526 device has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any Addressing mode. This symmetrical nature and lack of "special optimal situations" make programming with the PIC16F526 device simple, yet efficient. In addition, the learning curve is reduced significantly.

The PIC16F526 device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, one operand is typically the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC) and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-2, with the corresponding device pins described in Table 3-2.

| Name                       | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                                                                                                                                               |

|----------------------------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0//C1IN+/AN0/<br>ICSPDAT | RB0      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                         |

|                            | C1IN+    | AN            |                | Comparator 1 input.                                                                                                                                                                                                                                                       |

|                            | AN0      | AN            |                | ADC channel input.                                                                                                                                                                                                                                                        |

|                            | ICSPDAT  | ST            | CMOS           | ICSP™ mode Schmitt Trigger.                                                                                                                                                                                                                                               |

| RB1/C1IN-/AN1/<br>ICSPCLK  | RB1      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                         |

|                            | C1IN-    | AN            |                | Comparator 1 input.                                                                                                                                                                                                                                                       |

|                            | AN1      | AN            |                | ADC channel input.                                                                                                                                                                                                                                                        |

|                            | ICSPCLK  | ST            | CMOS           | ICSP mode Schmitt Trigger.                                                                                                                                                                                                                                                |

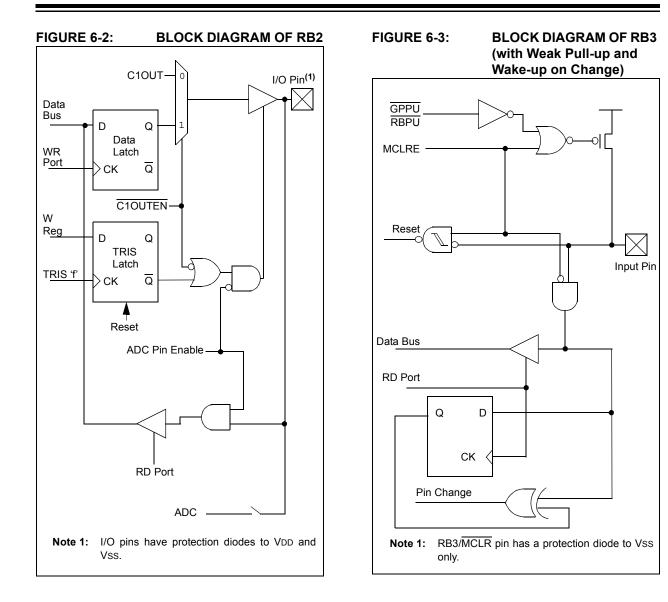

| RB2/C1OUT/AN2              | RB2      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                    |

|                            | C10UT    | _             | CMOS           | Comparator 1 output.                                                                                                                                                                                                                                                      |

|                            | AN2      | AN            | —              | ADC channel input.                                                                                                                                                                                                                                                        |

| RB3/MCLR/VPP               | RB3      | TTL           | —              | Input pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                     |

|                            | MCLR     | ST            | _              | Master Clear (Reset). When configured as MCLR, this pin is<br>an active-low Reset to the device. Voltage on MCLR/VPP must<br>not exceed VDD during normal device operation or the device<br>will enter Programming mode. Weak pull-up always on if<br>configured as MCLR. |

|                            | VPP      | HV            | _              | Programming voltage input.                                                                                                                                                                                                                                                |

| RB4/OSC2/CLKOUT            | RB4      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                         |

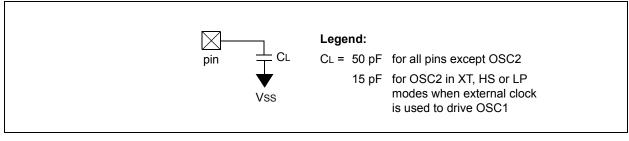

|                            | OSC2     | —             | XTAL           | Oscillator crystal output. Connections to crystal or resonator in Crystal Oscillator mode (XT, HS and LP modes only, PORTB in other modes).                                                                                                                               |

|                            | CLKOUT   |               | CMOS           | EXTRC/INTRC CLKOUT pin (Fosc/4).                                                                                                                                                                                                                                          |

| RB5/OSC1/CLKIN             | RB5      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                    |

|                            | OSC1     | XTAL          |                | Oscillator crystal input.                                                                                                                                                                                                                                                 |

|                            | CLKIN    | ST            |                | External clock source input.                                                                                                                                                                                                                                              |

| RC0/C2IN+                  | RC0      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | C2IN+    | AN            |                | Comparator 2 input.                                                                                                                                                                                                                                                       |

| RC1/C2IN-                  | RC1      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | C2IN-    | AN            | —              | Comparator 2 input.                                                                                                                                                                                                                                                       |

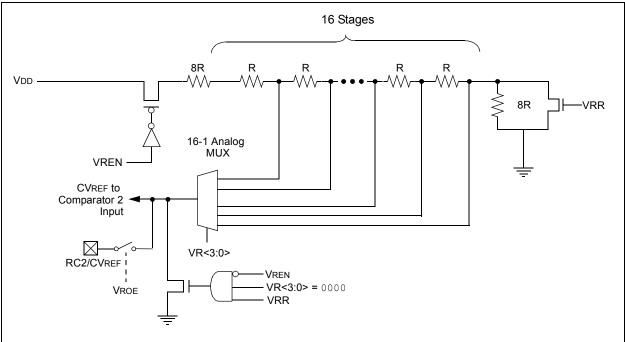

| RC2/CVREF                  | RC2      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | CVREF    |               | AN             | Programmable Voltage Reference output.                                                                                                                                                                                                                                    |

| RC3                        | RC3      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

| RC4/C2OUT                  | RC4      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | C2OUT    |               | CMOS           | Comparator 2 output.                                                                                                                                                                                                                                                      |

| RC5/T0CKI                  | RC5      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | TOCKI    | ST            |                | Timer0 Schmitt Trigger input pin.                                                                                                                                                                                                                                         |

| Vdd                        | Vdd      |               | Р              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                   |

| Vss                        | Vss      |               | Р              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                  |

TABLE 3-2: PIC16F526 PINOUT DESCRIPTION

**Legend:** I = Input, O = Output, I/O = Input/Output, P = Power, — = Not used, TTL = TTL input, ST = Schmitt Trigger input, HV = High Voltage

# 4.0 MEMORY ORGANIZATION

The PIC16F526 memories are organized into program memory and data memory (SRAM). The self-writable portion of the program memory called Flash data memory is located at addresses at 400h-43Fh. All Program mode commands that work on the normal Flash memory work on the Flash data memory. This includes bulk erase, row/column/cycling toggles, Load and Read data commands (Refer to Section 5.0 "Flash Data Memory Control" for more details). For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one STATUS register bit. For the PIC16F526, with data memory register files of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Select Register (FSR).

# 4.1 Program Memory Organization for the PIC16F526

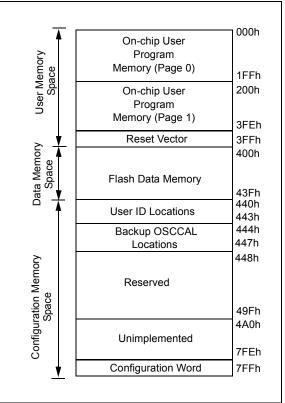

The PIC16F526 device has an 11-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space. Program memory is partitioned into user memory, data memory and configuration memory spaces.

The user memory space is the on-chip user program memory. As shown in Figure 4-1, it extends from 0x000 to 0x3FF and partitions into pages, including Reset vector at address 0x3FF.

The data memory space is the Flash data memory block and is located at addresses PC = 400h-43Fh. All Program mode commands that work on the normal Flash memory work on the Flash data memory block. This includes bulk erase, Load and Read data commands.

The configuration memory space extends from 0x440 to 0x7FF. Locations from 0x448 through 0x49F are reserved. The user ID locations extend from 0x440 through 0x443. The Backup OSCCAL locations extend from 0x444 through 0x447. The Configuration Word is physically located at 0x7FF.

Refer to "*PIC16F526 Memory Programming Specification*" (DS41317) for more details.

#### FIGURE 4-1:

MEMORY MAP

| U-0                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                | R/W-0                                                                                                               | R/W-0                                                                       | R/W-0            | R/W-0           | R/W-0          |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------|-----------------|----------------|

| _                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                  | FREE                                                                                                                | WRERR                                                                       | WREN             | WR              | RD             |

| bit 7                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                    |                                                                                                                     |                                                                             |                  |                 | bit (          |

| Legend:                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                    |                                                                                                                     |                                                                             |                  |                 |                |

| S = Bit can o                    | onlv be set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |                                                                                                                     |                                                                             |                  |                 |                |

| R = Readab                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable k                                                                                                                                                                                                                     | oit                                                                                                                 | U = Unimpler                                                                | nented bit, read | as '0'          |                |

| -n = Value a                     | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                                                                   |                                                                                                                     | '0' = Bit is cle                                                            | ared             | x = Bit is unkr | nown           |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                    |                                                                                                                     |                                                                             |                  |                 |                |

| bit 7-5                          | Unimpleme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nted: Read as '0                                                                                                                                                                                                                   | )'.                                                                                                                 |                                                                             |                  |                 |                |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Data Maman / D                                                                                                                                                                                                                     |                                                                                                                     | able Dit                                                                    |                  |                 |                |

| dit 4                            | FREE: Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data Memory F                                                                                                                                                                                                                      | kow Erase Er                                                                                                        | iable Bit                                                                   |                  |                 |                |

| bit 4                            | 1 = Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | m memory row b                                                                                                                                                                                                                     | eing pointed                                                                                                        | to by EEADR w                                                               |                  |                 | cycle. No writ |

| DIT 4                            | 1 = Program<br>will be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | m memory row b<br>performed. This                                                                                                                                                                                                  | eing pointed                                                                                                        | to by EEADR w                                                               |                  |                 | cycle. No writ |

|                                  | 1 = Program<br>will be p<br>0 = Perform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | m memory row b<br>performed. This<br>n write only                                                                                                                                                                                  | eing pointed<br>bit is cleared                                                                                      | to by EEADR w                                                               |                  |                 | cycle. No writ |

|                                  | 1 = Program<br>will be p<br>0 = Perforn<br>WRERR: Wr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit                                                                                                                                                            | eing pointed<br>bit is cleared                                                                                      | to by EEADR w<br>at the complet                                             | ion of the erase |                 | cycle. No writ |

|                                  | 1 = Program<br>will be  <br>0 = Perform<br><b>WRERR:</b> Wr<br>1 = A write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termir                                                                                                                                        | eing pointed<br>bit is cleared<br>nated premati                                                                     | to by EEADR w<br>at the complet<br>urely (by device                         | ion of the erase |                 | cycle. No writ |

| bit 3                            | <ol> <li>Program<br/>will be p</li> <li>Perform</li> <li>WRERR: Wr</li> <li>A write</li> <li>Write o</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple                                                                                                                     | eing pointed<br>bit is cleared<br>nated premati                                                                     | to by EEADR w<br>at the complet<br>urely (by device                         | ion of the erase |                 | cycle. No writ |

| bit 3                            | <ol> <li>Program<br/>will be p</li> <li>Perform</li> <li>WRERR: Wr</li> <li>A write</li> <li>Write o</li> <li>WREN: Write</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit                                                                                                     | eing pointed<br>bit is cleared<br>nated premate<br>ted successfu                                                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully                 | ion of the erase |                 | cycle. No writ |

| bit 3                            | <ol> <li>Program will be point with a second with the point will be point will be point with the point will be point wi</li></ol> | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit<br>write cycle to Fla                                                                               | eing pointed<br>bit is cleared<br>nated prematu<br>ted successfu                                                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully<br>nory         | ion of the erase |                 | cycle. No writ |

| bit 3                            | <ol> <li>Program will be point with a second with the point will be point will be point with the point will be point wi</li></ol> | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit                                                                                                     | eing pointed<br>bit is cleared<br>nated prematu<br>ted successfu                                                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully<br>nory         | ion of the erase |                 | cycle. No writ |

| bit 3<br>bit 2                   | <ol> <li>Program will be point with a second with the point will be point will be point with the point will be point wi</li></ol> | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit<br>write cycle to Fla<br>write cycle to Fla                                                         | eing pointed<br>bit is cleared<br>nated prematu<br>ted successfu                                                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully<br>nory         | ion of the erase |                 | cycle. No writ |