# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 67 x 8                                                                    |

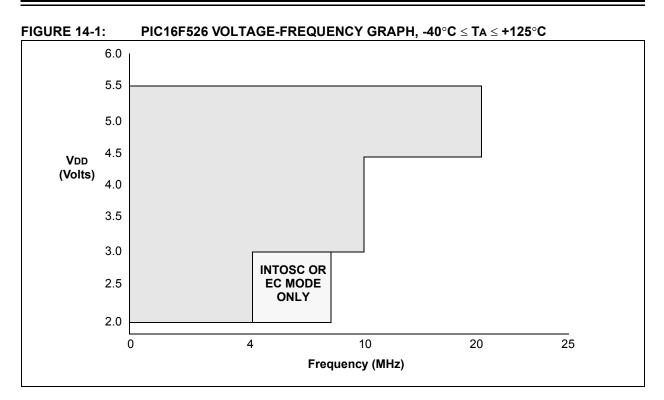

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 3x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (3x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f526t-i-mg |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 14-Pin, 8-Bit Flash Microcontroller

#### High-Performance RISC CPU:

- Only 33 Single-Word Instructions

- All Single-Cycle Instructions except for Program Branches which are Two-Cycle

- Two-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- · Operating Speed:

- DC 20 MHz crystal oscillator

- DC 200 ns instruction cycle

- On-chip Flash Program Memory:

- 1024 x 12

- · General Purpose Registers (SRAM):

- 67 x 8

- · Flash Data Memory:

- 64 x 8

#### **Special Microcontroller Features:**

- 8 MHz Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debugging (ICD) Support

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

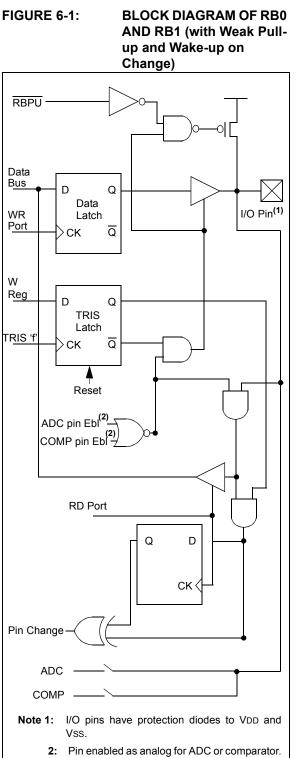

- Internal Weak Pull-ups on I/O Pins

- · Power-Saving Sleep mode

- Wake-Up from Sleep on Pin Change

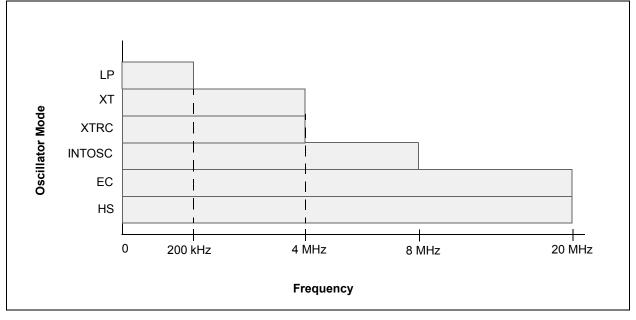

- Selectable Oscillator Options:

- INTRC: 4 MHz or 8 MHz precision Internal RC oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- HS: High-speed crystal/resonator

- LP: Power-saving, low-frequency crystal

- EC: High-speed external clock input

#### Low-Power Features/CMOS Technology:

- Standby current:

- 100 nA @ 2.0V, typical

- Operating current:

- 11  $\mu\text{A}$  @ 32 kHz, 2.0V, typical

- 175 μA @ 4 MHz, 2.0V, typical

- Watchdog Timer current:

- 1 μA @ 2.0V, typical

- 7 μA @ 5.0V, typical

- High Endurance Program and Flash Data Memory cells:

- 100,000 write Program Memory endurance

- 1,000,000 write Flash Data Memory endurance

- Program and Flash Data retention: >40 years

- Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V:

- Wide temperature range

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

#### **Peripheral Features:**

- 12 I/O Pins:

- 11 I/O pins with individual direction control

- 1 input-only pin

- High current sink/source for direct LED drive

- Wake-up on change

- Weak pull-ups

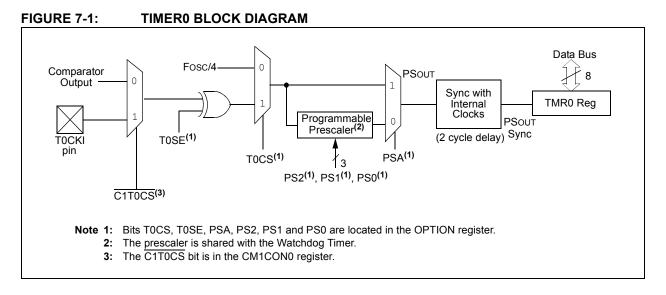

- 8-bit Real-time Clock/Counter (TMR0) with 8-bit Programmable Prescaler

- Two Analog Comparators:

- Comparator inputs and output accessible externally

- One comparator with 0.6V fixed on-chip absolute voltage reference (VREF)

- One comparator with programmable on-chip voltage reference (VREF)

- Analog-to-Digital (A/D) Converter:

- 8-bit resolution

- 3-channel external programmable inputs

- 1-channel internal input to internal absolute 0.6 voltage reference

| Dovico    | Program<br>Memory                 | Data Me | mory             | I/O | Comparators | Timers 8-bit | 8-bit A/D |

|-----------|-----------------------------------|---------|------------------|-----|-------------|--------------|-----------|

| Device    | Device Flash (words) SRAM (bytes) |         | Flash<br>(bytes) | 1/0 | Comparators |              | Channels  |

| PIC16F526 | 526 1024 67                       |         | 64               | 12  | 2           | 1            | 3         |

NOTES:

| Name                       | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                                                                                                                                               |

|----------------------------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0//C1IN+/AN0/<br>ICSPDAT | RB0      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                         |

|                            | C1IN+    | AN            |                | Comparator 1 input.                                                                                                                                                                                                                                                       |

|                            | AN0      | AN            |                | ADC channel input.                                                                                                                                                                                                                                                        |

|                            | ICSPDAT  | ST            | CMOS           | ICSP™ mode Schmitt Trigger.                                                                                                                                                                                                                                               |

| RB1/C1IN-/AN1/<br>ICSPCLK  | RB1      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                         |

|                            | C1IN-    | AN            |                | Comparator 1 input.                                                                                                                                                                                                                                                       |

|                            | AN1      | AN            |                | ADC channel input.                                                                                                                                                                                                                                                        |

|                            | ICSPCLK  | ST            | CMOS           | ICSP mode Schmitt Trigger.                                                                                                                                                                                                                                                |

| RB2/C1OUT/AN2              | RB2      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                    |

|                            | C10UT    | _             | CMOS           | Comparator 1 output.                                                                                                                                                                                                                                                      |

|                            | AN2      | AN            | —              | ADC channel input.                                                                                                                                                                                                                                                        |

| RB3/MCLR/VPP               | RB3      | TTL           | —              | Input pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                     |

|                            | MCLR     | ST            | _              | Master Clear (Reset). When configured as MCLR, this pin is<br>an active-low Reset to the device. Voltage on MCLR/VPP must<br>not exceed VDD during normal device operation or the device<br>will enter Programming mode. Weak pull-up always on if<br>configured as MCLR. |

|                            | VPP      | HV            | _              | Programming voltage input.                                                                                                                                                                                                                                                |

| RB4/OSC2/CLKOUT            | RB4      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                         |

|                            | OSC2     | —             | XTAL           | Oscillator crystal output. Connections to crystal or resonator in Crystal Oscillator mode (XT, HS and LP modes only, PORTB in other modes).                                                                                                                               |

|                            | CLKOUT   |               | CMOS           | EXTRC/INTRC CLKOUT pin (Fosc/4).                                                                                                                                                                                                                                          |

| RB5/OSC1/CLKIN             | RB5      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                    |

|                            | OSC1     | XTAL          |                | Oscillator crystal input.                                                                                                                                                                                                                                                 |

|                            | CLKIN    | ST            |                | External clock source input.                                                                                                                                                                                                                                              |

| RC0/C2IN+                  | RC0      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | C2IN+    | AN            |                | Comparator 2 input.                                                                                                                                                                                                                                                       |

| RC1/C2IN-                  | RC1      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | C2IN-    | AN            | —              | Comparator 2 input.                                                                                                                                                                                                                                                       |

| RC2/CVREF                  | RC2      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | CVREF    |               | AN             | Programmable Voltage Reference output.                                                                                                                                                                                                                                    |

| RC3                        | RC3      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

| RC4/C2OUT                  | RC4      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | C2OUT    |               | CMOS           | Comparator 2 output.                                                                                                                                                                                                                                                      |

| RC5/T0CKI                  | RC5      | TTL           | CMOS           | Bidirectional I/O port.                                                                                                                                                                                                                                                   |

|                            | TOCKI    | ST            |                | Timer0 Schmitt Trigger input pin.                                                                                                                                                                                                                                         |

| Vdd                        | Vdd      |               | Р              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                   |

| Vss                        | Vss      |               | Р              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                  |

TABLE 3-2: PIC16F526 PINOUT DESCRIPTION

**Legend:** I = Input, O = Output, I/O = Input/Output, P = Power, — = Not used, TTL = TTL input, ST = Schmitt Trigger input, HV = High Voltage

### 3.1 Clocking Scheme/Instruction Cycle

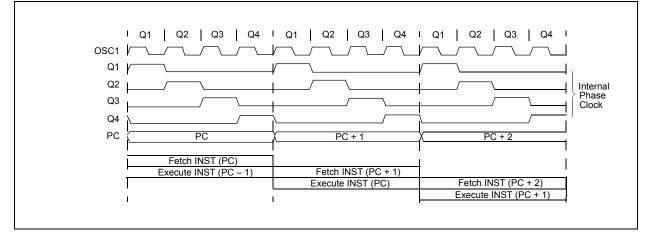

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

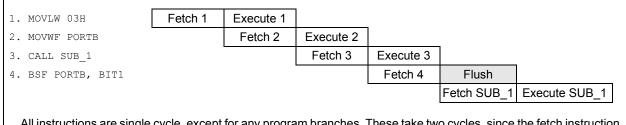

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

### 5.2.2 WRITING TO FLASH DATA MEMORY

Once a cell is erased, new data can be written. Program execution is suspended during the write cycle. The following sequence must be performed for a single byte write.

- 1. Load EEADR with the address.

- 2. Load EEDATA with the data to write.

- 3. Set the WREN bit to enable write access to the array.

- 4. Set the WR bit to initiate the erase cycle.

If the WR bit is not set in the instruction cycle after the WREN bit is set, the WREN bit will be cleared in hardware.

Sample code that follows this procedure is included in Example 3.

#### EXAMPLE 3: WRITING A FLASH DATA MEMORY ROW

| BANKSEL | EEADR            |   |                      |

|---------|------------------|---|----------------------|

| MOVLW   | EE_ADR_WRITE     | ; | LOAD ADDRESS         |

| MOVWF   | EEADR            | ; |                      |

| MOVLW   | EE_DATA_TO_WRITE | ; | LOAD DATA            |

| MOVWF   | EEDATA           | ; | INTO EEDATA REGISTER |

| BSF     | EECON, WREN      | ; | ENABLE WRITES        |

| BSF     | EECON,WR         | ; | INITITATE ERASE      |

|         |                  |   |                      |

- Note 1: Only a series of BSF commands will work to enable the memory write sequence documented in Example 2. No other sequence of commands will work, no exceptions.

- 2: For reads, erases and writes to the Flash data memory, there is no need to insert a NOP into the user code as is done on mid-range devices. The instruction immediately following the "BSF EECON, WR/RD" will be fetched and executed properly.

#### 5.3 Write Verify

Depending on the application, good programming practice may dictate that data written to the Flash data memory be verified. Example 4 is an example of a write verify.

#### EXAMPLE 4: WRITE VERIFY OF FLASH DATA MEMORY

| MOVF  | EEDATA, W | ;EEDATA has not changed |

|-------|-----------|-------------------------|

|       |           | ;from previous write    |

| BSF   | EECON, RD | ;Read the value written |

| XORWF | EEDATA, W | ;                       |

| BTFSS | STATUS, Z | ;Is data the same       |

| GOTO  | WRITE_ERR | ;No, handle error       |

|       |           | ;Yes, continue          |

|       |           |                         |

#### REGISTER 5-1: EEDATA: FLASH DATA REGISTER

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| EEDATA7 | EEDATA6 | EEDATA5 | EEDATA4 | EEDATA3 | EEDATA2 | EEDATA1 | EEDATA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 EEDATA<7:0>: 8-bits of data to be read from/written to data Flash

#### REGISTER 5-2: EEADR: FLASH ADDRESS REGISTER

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | EEADR5 | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'.

bit 5-0 EEADR<5:0>: 6-bits of data to be read from/written to data Flash

| U-0                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                | R/W-0                                                                                                               | R/W-0                                                                       | R/W-0            | R/W-0           | R/W-0          |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------|-----------------|----------------|

| _                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                  | FREE                                                                                                                | WRERR                                                                       | WREN             | WR              | RD             |

| bit 7                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                    |                                                                                                                     |                                                                             |                  |                 | bit (          |

| Legend:                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                    |                                                                                                                     |                                                                             |                  |                 |                |

| S = Bit can o                    | onlv be set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |                                                                                                                     |                                                                             |                  |                 |                |

| R = Readab                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable k                                                                                                                                                                                                                     | oit                                                                                                                 | U = Unimpler                                                                | nented bit, read | as '0'          |                |

| -n = Value a                     | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                                                                   |                                                                                                                     | '0' = Bit is cle                                                            | ared             | x = Bit is unkr | nown           |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                    |                                                                                                                     |                                                                             |                  |                 |                |

| bit 7-5                          | Unimpleme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nted: Read as '0                                                                                                                                                                                                                   | )'.                                                                                                                 |                                                                             |                  |                 |                |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Data Maman / D                                                                                                                                                                                                                     |                                                                                                                     |                                                                             |                  |                 |                |

| dit 4                            | FREE: Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Data Memory F                                                                                                                                                                                                                      | kow Erase Er                                                                                                        | iable Bit                                                                   |                  |                 |                |

| bit 4                            | 1 = Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | m memory row b                                                                                                                                                                                                                     | eing pointed                                                                                                        | to by EEADR w                                                               |                  |                 | cycle. No writ |

| DIT 4                            | 1 = Program<br>will be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | m memory row b<br>performed. This                                                                                                                                                                                                  | eing pointed                                                                                                        | to by EEADR w                                                               |                  |                 | cycle. No writ |

|                                  | 1 = Program<br>will be p<br>0 = Perform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | m memory row b<br>performed. This<br>n write only                                                                                                                                                                                  | eing pointed<br>bit is cleared                                                                                      | to by EEADR w                                                               |                  |                 | cycle. No writ |

|                                  | 1 = Program<br>will be p<br>0 = Perforn<br>WRERR: Wr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit                                                                                                                                                            | eing pointed<br>bit is cleared                                                                                      | to by EEADR w<br>at the complet                                             | ion of the erase |                 | cycle. No writ |

|                                  | 1 = Program<br>will be  <br>0 = Perform<br><b>WRERR:</b> Wr<br>1 = A write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termir                                                                                                                                        | eing pointed<br>bit is cleared<br>nated premati                                                                     | to by EEADR w<br>at the complet<br>urely (by device                         | ion of the erase |                 | cycle. No writ |

| bit 3                            | <ol> <li>Program<br/>will be p</li> <li>Perform</li> <li>WRERR: Wr</li> <li>A write</li> <li>Write o</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple                                                                                                                     | eing pointed<br>bit is cleared<br>nated premati                                                                     | to by EEADR w<br>at the complet<br>urely (by device                         | ion of the erase |                 | cycle. No writ |

| bit 3                            | <ol> <li>Program<br/>will be p</li> <li>Perform</li> <li>WRERR: Wr</li> <li>A write</li> <li>Write o</li> <li>WREN: Write</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit                                                                                                     | eing pointed<br>bit is cleared<br>nated premate<br>ted successfu                                                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully                 | ion of the erase |                 | cycle. No writ |

| bit 3                            | <ol> <li>Program will be point with a second with the point will be point will be point with the point will be point wi</li></ol> | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit<br>write cycle to Fla                                                                               | eing pointed<br>bit is cleared<br>nated prematu<br>ted successfu                                                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully<br>nory         | ion of the erase |                 | cycle. No writ |

| bit 3                            | <ol> <li>Program will be point with a second with the point will be point will be point with the point will be point wi</li></ol> | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit                                                                                                     | eing pointed<br>bit is cleared<br>nated prematu<br>ted successfu                                                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully<br>nory         | ion of the erase |                 | cycle. No writ |

| bit 3<br>bit 2                   | <ol> <li>Program will be point with a second with the point will be point will be point with the point will be point wi</li></ol> | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit<br>write cycle to Fla<br>write cycle to Fla                                                         | eing pointed<br>bit is cleared<br>nated prematu<br>ted successfu                                                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully<br>nory         | ion of the erase |                 | cycle. No writ |

| bit 3<br>bit 2                   | <ol> <li>Programwill be point</li> <li>Perform</li> <li>WRERR: Write</li> <li>A write</li> <li>Write of</li> <li>WREN: Write</li> <li>Allows</li> <li>Inhibits</li> <li>WR: Write C</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | m memory row b<br>performed. This<br>n write only<br>ite Error Flag bit<br>operation termin<br>peration comple<br>e Enable bit<br>write cycle to Fla<br>write cycle to Fla                                                         | eing pointed<br>bit is cleared<br>nated premati<br>ted successfi<br>ash data men<br>ash data mer                    | to by EEADR w<br>at the complet<br>urely (by device<br>ully<br>nory         | ion of the erase |                 | cycle. No writ |