# E·XFL

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 67 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 3x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f526t-i-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-60932-355-4

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

NOTES:

| Addr               | Name    | Bit 7       | Bit 6                                | Bit 5        | Bit 4         | Bit 3         | Bit 2        | Bit 1   | Bit 0     | Value on<br>Power-on<br>Reset | Page # |

|--------------------|---------|-------------|--------------------------------------|--------------|---------------|---------------|--------------|---------|-----------|-------------------------------|--------|

| N/A                | TRIS    | _           | —                                    | I/O Control  | Register (PC  | ORTB, PORT    | IC)          |         |           | 11 1111                       | 27     |

| N/A                | OPTION  | Contains co | ontrol bits to c                     | onfigure Tim | ner0 and Tim  | er0/WDT pre   | escaler      |         |           | 1111 1111                     | 19     |

| 00h                | INDF    | Uses conte  | nts of FSR to                        | Address Da   | ata Memory (i | not a physica | al register) |         |           | XXXX XXXX                     | 22     |

| 01h/41h            | TMR0    | Timer0 Mo   | dule Register                        |              |               |               |              |         |           | XXXX XXXX                     | 37     |

| 02h <sup>(1)</sup> | PCL     | Low order   | 3 bits of PC                         |              |               |               |              |         |           | 1111 1111                     | 21     |

| 03h                | STATUS  | RBWUF       | CWUF                                 | PA0          | TO            | PD            | Z            | DC      | С         | 0001 1xxx                     | 18     |

| 04h                | FSR     | Indirect Da | Indirect Data Memory Address Pointer |              |               |               |              |         |           | 100x xxxx                     | 22     |

| 05h/45h            | OSCCAL  | CAL6        | CAL5                                 | CAL4         | CAL3          | CAL2          | CAL1         | CAL0    | _         | 1111 111-                     | 20     |

| 06h/46h            | PORTB   | —           | —                                    | RB5          | RB4           | RB3           | RB2          | RB1     | RB0       | xx xxxx                       | 27     |

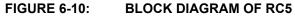

| 07h                | PORTC   |             | _                                    | RC5          | RC4           | RC3           | RC2          | RC1     | RC0       | xx xxxx                       | 28     |

| 08h                | CM1CON0 | C1OUT       | C10UTEN                              | C1POL        | C1T0CS        | C10N          | C1NREF       | C1PREF  | C1WU      | q111 1111                     | 63     |

| 09h                | ADCON0  | ANS1        | ANS0                                 | ADCS1        | ADCS0         | CHS1          | CHS0         | GO/DONE | ADON      | 1111 1100                     | 61     |

| 0Ah                | ADRES   | ADC Conve   | ADC Conversion Result                |              |               |               |              |         | XXXX XXXX | 62                            |        |

| 0Bh                | CM2CON0 | C2OUT       | C2OUTEN                              | C2POL        | C2PREF2       | C2ON          | C2NREF       | C2PREF1 | C2WU      | q111 1111                     | 64     |

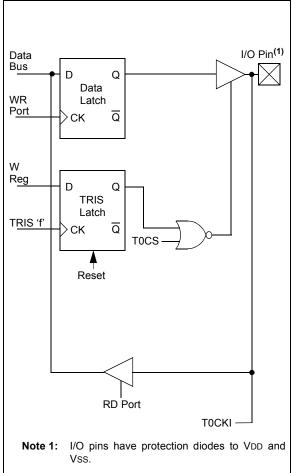

| 0Ch                | VRCON   | VREN        | VROE                                 | VRR          |               | VR3           | VR2          | VR1     | VR0       | 001- 1111                     | 69     |

| 21h/61h            | EECON   | —           | —                                    | _            | FREE          | WRERR         | WREN         | WR      | RD        | 0 x000                        | 23     |

| 25h/65h            | EEDATA  | SELF REA    | D/WRITE DA                           | ΓA           | •             |               | •            |         |           | XXXX XXXX                     | 23     |

| 26h/66h            | EEADR   |             | —                                    | SELF REA     | D/WRITE AD    | DRESS         |              |         |           | xx xxxx                       | 23     |

**TABLE 4-1:** SPECIAL FUNCTION REGISTER (SFR) SUMMARY

Legend:

x = unknown, u = unchanged, - = unimplemented, read as '0' (if applicable), q = value depends on condition. Shaded cells = unimplemented or unused

Note 1:

The upper byte of the Program Counter is not directly accessible. See Section 4.6 "Program Counter" for an explanation of how to

access these bits.

Also, see the Electrical Specifications section for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

FIGURE 8-5: EXTERNAL RC OSCILLATOR MODE

## 8.2.5 INTERNAL 4/8 MHz RC OSCILLATOR

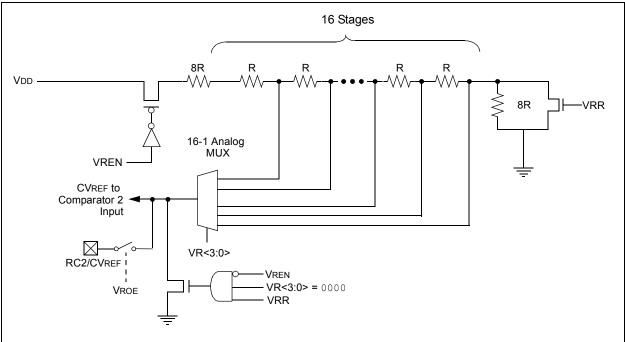

The internal RC oscillator provides a fixed 4/8 MHz (nominal) system clock at VDD = 5V and  $25^{\circ}C$ , (see **Section 14.0** "**Electrical Characteristics**" for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal RC oscillator. This location is always non-code protected, regardless of the codeprotect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

Note: Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part so it can be reprogrammed correctly later.

For the PIC16F526 device, only bits 7:1 of OSCCAL are used for calibration. See Register 4-3 for more information.

Note: The bit 0 of the OSCCAL register is unimplemented and should be written as '0' when modifying OSCCAL for compatibility with future devices.

# 8.9 Power-down Mode (Sleep)

A device may be powered down (Sleep) and later powered up (wake-up from Sleep).

## 8.9.1 SLEEP

The Power-Down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit of the STATUS register is set, the PD bit of the STATUS register is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

**Note:** A Reset generated by a WDT time-out does not drive the MCLR pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or VSS and the RB3/ MCLR/VPP pin must be at a logic high level if MCLR is enabled.

## 8.9.2 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. An external Reset input on RB3/MCLR/VPP pin, when configured as MCLR.

- 2. A Watchdog Timer Time-out Reset (if WDT was enabled).

- 3. A change on input pin RB0, RB1, RB3 or RB4 when wake-up on change is enabled.

- A change in one of the comparator output bits, C1OUT or C2OUT (if comparator wake-up is enabled).

These events cause a device Reset. The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  and CWUF/RBWUF bits can be used to determine the cause of device Reset. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The CWUF bit indicates a change in a comparator output state while the device was in Sleep. The RBWUF bit indicates a change in state while in Sleep at pins RB0, RB1, RB3 or RB4 (since the last file or bit operation on RB port).

| Note: | Caution: Right before entering Sleep,      |

|-------|--------------------------------------------|

|       | read the input pins. When in Sleep,        |

|       | wake-up occurs when the values at the      |

|       | pins change from the state they were in at |

|       | the last reading. If a wake-up on change   |

|       | occurs and the pins are not read before    |

|       | re-entering Sleep, a wake-up will occur    |

|       | immediately even if no pins change while   |

|       | in Sleep mode.                             |

The WDT is cleared when the device wakes from Sleep, regardless of the wake-up source.

Note: Caution: Right before entering Sleep, read the comparator Configuration register(s) CM1CON0 and CM2CON0. When in Sleep, wake-up occurs when the comparator output bit C1OUT and C2OUT change from the state they were in at the last reading. If a wake-up on comparator change occurs and the pins are not read before re-entering Sleep, a wake-up will occur immediately, even if no pins change while in Sleep mode.

NOTES:

### TABLE 11-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name    | Bit 7 | Bit 6   | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1   | Bit 0 | Value on POR | Value on all other Resets |

|---------|-------|---------|-------|---------|-------|--------|---------|-------|--------------|---------------------------|

| VRCON   | VREN  | VROE    | VRR   | —       | VR3   | VR2    | VR1     | VR0   | 001- 1111    | uuu- uuuu                 |

| CM1CON0 | C1OUT | C10UTEN | C1POL | C1T0CS  | C10N  | C1NREF | C1PREF  | C1WU  | q111 1111    | quuu uuuu                 |

| CM2CON0 | C2OUT | C2OUTEN | C2POL | C2PREF2 | C2ON  | C2NREF | C2PREF1 | C2WU  | q111 1111    | quuu uuuu                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends on condition.

# 12.0 INSTRUCTION SET SUMMARY

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories.

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 12-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 12-1, while the various opcode fields are summarized in Table 12-1.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

# TABLE 12-1: OPCODE FIELD DESCRIPTIONS

| Field   | Description                                                                                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f       | Register file address (0x00 to 0x7F)                                                                                                                                                |

| W       | Working register (accumulator)                                                                                                                                                      |

| b       | Bit address within an 8-bit file register                                                                                                                                           |

| k       | Literal field, constant data or label                                                                                                                                               |

| х       | Don't care location (= $0$ or $1$ )<br>The assembler will generate code with x = $0$ . It is<br>the recommended form of use for compatibility with<br>all Microchip software tools. |

| d       | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                                   |

| label   | Label name                                                                                                                                                                          |

| TOS     | Top-of-Stack                                                                                                                                                                        |

| PC      | Program Counter                                                                                                                                                                     |

| WDT     | Watchdog Timer counter                                                                                                                                                              |

| TO      | Time-out bit                                                                                                                                                                        |

| PD      | Power-down bit                                                                                                                                                                      |

| dest    | Destination, either the W register or the specified register file location                                                                                                          |

| []      | Options                                                                                                                                                                             |

| ( )     | Contents                                                                                                                                                                            |

| Æ       | Assigned to                                                                                                                                                                         |

| < >     | Register bit field                                                                                                                                                                  |

| Œ       | In the set of                                                                                                                                                                       |

| italics | User defined term (font is courier)                                                                                                                                                 |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 12-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

### FIGURE 12-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-o  | riented file regi                                                                     | ster   | oper  | ations          |     |  |

|---------|---------------------------------------------------------------------------------------|--------|-------|-----------------|-----|--|

| 11      | 6                                                                                     | 5      | 4     |                 | 0   |  |

|         | OPCODE                                                                                | d      |       | f (FILE #)      |     |  |

| d       | d = 0 for destination W<br>d = 1 for destination f<br>f = 5-bit file register address |        |       |                 |     |  |

| Bit-ori | ented file regist                                                                     | er op  | erat  | ions            |     |  |

| 11      | 8                                                                                     | 7      | 5     | 4               | 0   |  |

|         | OPCODE                                                                                | b (Bl  | T #)  | f (FILE #)      |     |  |

|         | and control op                                                                        |        |       |                 |     |  |

| 11      |                                                                                       | 8      | 7     |                 | 0   |  |

|         | OPCODE                                                                                |        |       | k (literal)     |     |  |

| k       | = 8-bit immedia                                                                       | ite va | lue   |                 |     |  |

| Literal | and control op                                                                        | eratio | ons - | - GOTO instruct | ion |  |

| 11      |                                                                                       | 9      | 8     |                 | 0   |  |

| 11      |                                                                                       |        | -     |                 | •   |  |

|         | OPCODE                                                                                |        |       | k (literal)     |     |  |

| ADDWF            | Add W and f                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                   |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                         |

| Description:     | Add the contents of the W register<br>and register 'f'. If 'd' is'0', the result<br>is stored in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                        |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                        |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is cleared.                                |

| ANDLW            | AND literal with W                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | (W).AND. (k) $\rightarrow$ (W)                                                                                             |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                          |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                        |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is set.                                    |

| ANDWF            | AND W with f                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                                         |

| Description:     | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is '0',<br>the result is stored in the W register.<br>If 'd' is '1', the result is stored back<br>in register 'f'. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSC f,b                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                            |

| Operation:       | <b>skip if (f<b>) =</b> 0</b>                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is skipped.                                                                                                                      |

|                  | If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded,<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b < 7 \end{array}$                                                                                                                               |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is skipped.                                                                                                                      |

|                  | If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |

| CLRW             | Clear W                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                           |

| Operands:        | None                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The W register is cleared. Zero bit (Z) is set.                        |

| CALL             | Subroutine Call                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                                                                  |

| Operation:       | (PC) + 1 $\rightarrow$ Top-of-Stack;<br>k $\rightarrow$ PC<7:0>;<br>(STATUS<6:5>) $\rightarrow$ PC<10:9>;<br>0 $\rightarrow$ PC<8>                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                 |

| Description:     | Subroutine call. First, return<br>address (PC + 1) is PUSHed onto<br>the stack. The eight-bit immediate<br>address is loaded into PC<br>bits <7:0>. The upper bits<br>PC<10:9> are loaded from<br>STATUS<6:5>, PC<8> is cleared.<br>CALL is a two-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                        |

| Operands:        | None                                                                                                                                                                                  |

| Operation:       | 00h $\rightarrow$ WDT;<br>0 $\rightarrow$ WDT prescaler (if assigned);<br>1 $\rightarrow$ TO;<br>1 $\rightarrow$ PD                                                                   |

| Status Affected: | TO, PD                                                                                                                                                                                |

| Description:     | The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits $\overline{TO}$ and $\overline{PD}$ are set. |

| CLRF             | Clear f                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                                |

| Operands:        | $0 \leq f \leq 31$                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.         |

| COMF             | Complement f                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                  |

| Operation:       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                            |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is placed back in register<br>'f'. |

| MOVWF            | Move W to f                                    |

|------------------|------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                       |

| Operands:        | $0 \leq f \leq 31$                             |

| Operation:       | $(W) \rightarrow (f)$                          |

| Status Affected: | None                                           |

| Description:     | Move data from the W register to register 'f'. |

| MOVF             | Move f                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                       |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>moved to destination 'd'. If 'd' is '0',<br>destination is the W register. If 'd'<br>is '1', the destination is file<br>register 'f'. 'd' = 1 is useful as a<br>test of a file register, since status<br>flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                                 |

| Operands:        | $0 \le k \le 255$                                                                                        |

| Operation:       | $k \rightarrow (W)$                                                                                      |

| Status Affected: | None                                                                                                     |

| Description:     | The eight-bit literal 'k' is loaded<br>into the W register. The "don't<br>cares" will assembled as '0's. |

| OPTION           | Load OPTION Register                                              |

|------------------|-------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                    |

| Operands:        | None                                                              |

| Operation:       | $(W) \rightarrow OPTION$                                          |

| Status Affected: | None                                                              |

| Description:     | The content of the W register is loaded into the OPTION register. |

# TABLE 14-2: COMPARATOR SPECIFICATIONS.

| Comparator Specifications                  | Standard Operating Conditions (unless otherwise stated)           Operating temperature         -40°C to 125°C |      |       |           |       |          |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|-------|-----------|-------|----------|

| Characteristics                            | Sym.                                                                                                           | Min. | Тур.  | Max.      | Units | Comments |

| Internal Voltage Reference                 | VIVRF                                                                                                          | 0.50 | 0.60  | 0.70      | V     |          |

| Input offset voltage                       | Vos                                                                                                            | _    | ± 5.0 | ± 10      | mV    |          |

| Input common mode voltage*                 | Vсм                                                                                                            | 0    | —     | Vdd – 1.5 | V     |          |

| CMRR*                                      | CMRR                                                                                                           | 55   | —     | _         | db    |          |

| Response Time <sup>(1)*</sup>              | Trt                                                                                                            | _    | 150   | 400       | ns    |          |

| Comparator Mode Change to<br>Output Valid* | TMC2COV                                                                                                        | _    | _     | 10        | μS    |          |

\* These parameters are characterized but not tested.

**Note 1:** Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD - 1.5V.

| Sym.  | Characteristics                  | Min. | Тур.              | Max.           | Units      | Comments                                    |

|-------|----------------------------------|------|-------------------|----------------|------------|---------------------------------------------|

| CVRES | Resolution                       |      | VDD/24*<br>VDD/32 | _              | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

|       | Absolute Accuracy <sup>(2)</sup> |      |                   | ±1/2*<br>±1/2* | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

|       | Unit Resistor Value (R)          |      | 2K*               | —              | Ω          |                                             |

|       | Settling Time <sup>(1)</sup>     | _    | —                 | 10*            | μS         |                                             |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

**2:** Do not use reference externally when VDD < 2.7V. Under this condition, reference should only be used with comparator Voltage Common mode observed.

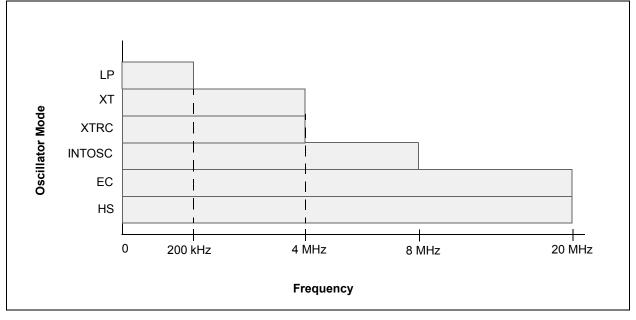

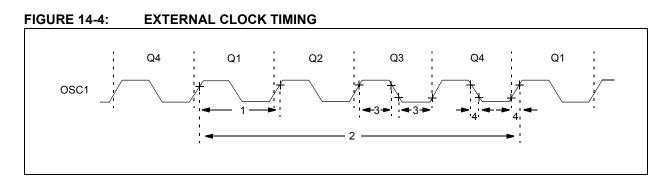

| AC CHARACTERISTICS |       |                                         |                                                                                                                         | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ (industrial),} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ (extended)} \end{array} $ |        |     |                       |  |  |  |

|--------------------|-------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----------------------|--|--|--|

|                    |       |                                         | Operating Voltage VDD range is described in <b>Section 14.1 "DC</b><br><b>Characteristics: PIC16F526 (Industrial)</b> " |                                                                                                                                                                                                                                                                |        |     |                       |  |  |  |

| Param<br>No.       | Sym.  | Characteristic                          | Min. Typ. <sup>(1)</sup> Max. Units Conditions                                                                          |                                                                                                                                                                                                                                                                |        |     |                       |  |  |  |

| 1A                 | Fosc  | External CLKIN Frequency <sup>(2)</sup> | DC                                                                                                                      |                                                                                                                                                                                                                                                                | 4      | MHz | XT Oscillator mode    |  |  |  |

|                    |       |                                         | DC                                                                                                                      |                                                                                                                                                                                                                                                                | 20     | MHz | HS/EC Oscillator mode |  |  |  |

|                    |       |                                         | DC                                                                                                                      |                                                                                                                                                                                                                                                                | 200    | kHz | LP Oscillator mode    |  |  |  |

|                    |       | Oscillator Frequency <sup>(2)</sup>     | -                                                                                                                       |                                                                                                                                                                                                                                                                | 4      | MHz | EXTRC Oscillator mode |  |  |  |

|                    |       |                                         | 0.1                                                                                                                     | —                                                                                                                                                                                                                                                              | 4      | MHz | XT Oscillator mode    |  |  |  |

|                    |       |                                         | 4                                                                                                                       |                                                                                                                                                                                                                                                                | 20     | MHz | HS/EC Oscillator mode |  |  |  |

|                    |       |                                         | —                                                                                                                       |                                                                                                                                                                                                                                                                | 200    | kHz | LP Oscillator mode    |  |  |  |

| 1                  | Tosc  | External CLKIN Period <sup>(2)</sup>    | 250                                                                                                                     |                                                                                                                                                                                                                                                                | —      | ns  | XT Oscillator mode    |  |  |  |

|                    |       |                                         | 50                                                                                                                      |                                                                                                                                                                                                                                                                | —      | ns  | HS/EC Oscillator mode |  |  |  |

|                    |       |                                         | 5                                                                                                                       | _                                                                                                                                                                                                                                                              | —      | μS  | LP Oscillator mode    |  |  |  |

|                    |       | Oscillator Period <sup>(2)</sup>        | 250                                                                                                                     | —                                                                                                                                                                                                                                                              | —      | ns  | EXTRC Oscillator mode |  |  |  |

|                    |       |                                         | 250                                                                                                                     |                                                                                                                                                                                                                                                                | 10,000 | ns  | XT Oscillator mode    |  |  |  |

|                    |       |                                         | 50                                                                                                                      |                                                                                                                                                                                                                                                                | 250    | ns  | HS/EC Oscillator mode |  |  |  |

|                    |       |                                         | 5                                                                                                                       | —                                                                                                                                                                                                                                                              | —      | μS  | LP Oscillator mode    |  |  |  |

| 2                  | Тсү   | Instruction Cycle Time                  | 200                                                                                                                     | 4/Fosc                                                                                                                                                                                                                                                         | —      | ns  |                       |  |  |  |

| 3                  | TosL, | Clock in (OSC1) Low or High             | 50*                                                                                                                     | _                                                                                                                                                                                                                                                              | —      | ns  | XT Oscillator         |  |  |  |

|                    | TosH  | Time                                    | 2*                                                                                                                      |                                                                                                                                                                                                                                                                | —      | μS  | LP Oscillator         |  |  |  |

|                    |       |                                         | 10*                                                                                                                     | —                                                                                                                                                                                                                                                              | —      | ns  | HS/EC Oscillator      |  |  |  |

| 4                  | TosR, | Clock in (OSC1) Rise or Fall            | —                                                                                                                       |                                                                                                                                                                                                                                                                | 25*    | ns  | XT Oscillator         |  |  |  |

|                    | TosF  | Time                                    | —                                                                                                                       | —                                                                                                                                                                                                                                                              | 50*    | ns  | LP Oscillator         |  |  |  |

|                    |       |                                         | —                                                                                                                       | —                                                                                                                                                                                                                                                              | 15*    | ns  | HS/EC Oscillator      |  |  |  |

### TABLE 14-6: EXTERNAL CLOCK TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

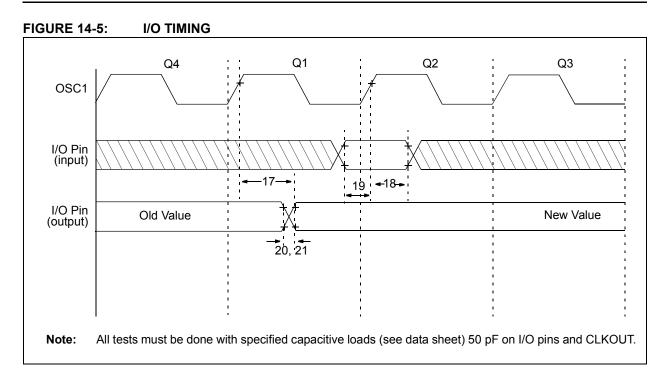

# TABLE 14-8: TIMING REQUIREMENTS

| AC<br>CHARAC | TERISTICS | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)Operating Voltage VDD range is described in Section 14.1 "DC Characteristics: PIC16F526(Industrial)" |    |                     |      |       |  |  |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------|------|-------|--|--|

| Param<br>No. | Sym.      | Characteristic                                                                                                                                                                                                                                                                             |    | Тур. <sup>(1)</sup> | Max. | Units |  |  |

| 17           | TosH2ıoV  | OSC1↑ (Q1 cycle) to Port Out Valid <sup>(2), (3)</sup>                                                                                                                                                                                                                                     | _  | _                   | 100* | ns    |  |  |

| 18           | TosH2iol  | OSC1 <sup>↑</sup> (Q2 cycle) to Port Input Invalid (I/O in hold time) <sup>(2)</sup>                                                                                                                                                                                                       | 50 | —                   | _    | ns    |  |  |

| 19           | TIOV20sH  | Port Input Valid to OSC1 <sup>↑</sup> (I/O in setup time)                                                                                                                                                                                                                                  | 20 | _                   |      | ns    |  |  |

| 20           | TIOR      | Port Output Rise Time <sup>(3)</sup>                                                                                                                                                                                                                                                       |    | 10                  | 50** | ns    |  |  |

| 21           | TIOF      | Port Output Fall Time <sup>(3)</sup>                                                                                                                                                                                                                                                       | _  | 10                  | 58** | ns    |  |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: Measurements are taken in EXTRC mode.

**3:** See Figure 14-3 for loading conditions.

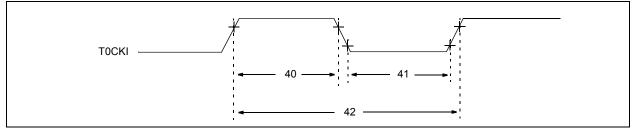

## FIGURE 14-7: TIMER0 CLOCK TIMINGS

# TABLE 14-10: TIMER0 CLOCK REQUIREMENT

| AC CHARACTERISTICS |      |                    | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)Operating Voltage VDD range is described inSection 14.1 "DC Characteristics: PIC16F526 (Industrial)" |                   |                     |      |       |                                                                |  |       |                |     |   |  |    |  |

|--------------------|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------|-------|----------------------------------------------------------------|--|-------|----------------|-----|---|--|----|--|

| Param<br>No.       | Sym. | Characteristic     |                                                                                                                                                                                                                                                                                            | Min.              | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |  |       |                |     |   |  |    |  |

| 40 Tt0H            |      | H TOCKI High Pulse | No Prescaler                                                                                                                                                                                                                                                                               | 0.5 Tcy + 20*     | _                   | _    | ns    |                                                                |  |       |                |     |   |  |    |  |

|                    |      | Width              | With Prescaler                                                                                                                                                                                                                                                                             | 10*               | _                   | _    | ns    |                                                                |  |       |                |     |   |  |    |  |

| 41                 | Tt0L | T0CKI Low Pulse    | No Prescaler                                                                                                                                                                                                                                                                               | 0.5 Tcy + 20*     | _                   | —    | ns    |                                                                |  |       |                |     |   |  |    |  |

|                    |      |                    |                                                                                                                                                                                                                                                                                            |                   |                     |      |       |                                                                |  | Width | With Prescaler | 10* | — |  | ns |  |

| 42                 | Tt0P | T0CKI Period       |                                                                                                                                                                                                                                                                                            | 20 or Tcy + 40* N |                     |      | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |       |                |     |   |  |    |  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

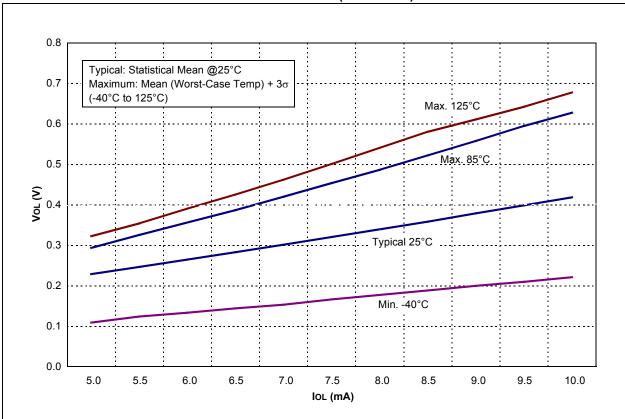

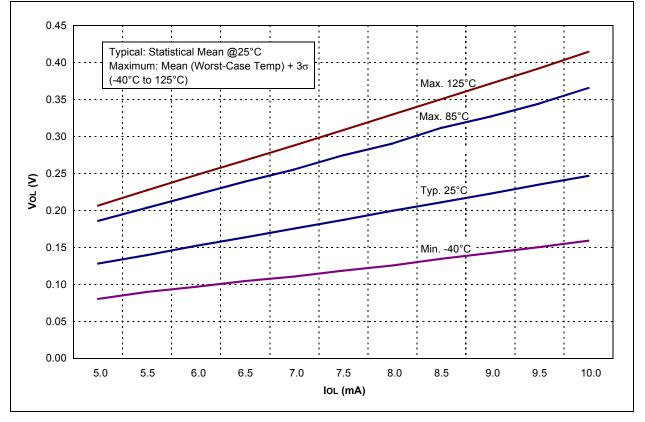

FIGURE 15-11: Vol vs. IoL OVER TEMPERATURE (VDD = 3.0V)

For the most current package drawings, please see the Microchip Packaging Specification located at

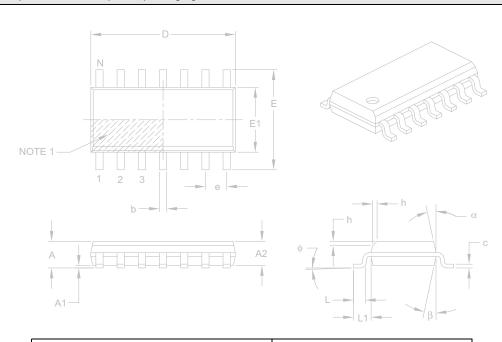

## 14-Lead Plastic Small Outline (SL) – Narrow, 3.90 mm Body [SOIC]

http://www.microchip.com/packaging

Units MILLIMETERS NOM **Dimension Limits** MIN MAX Number of Pins Ν 14 Pitch 1.27 BSC е **Overall Height** А 1.75 Molded Package Thickness A2 1.25 \_ \_ Standoff § A1 0.10 0.25 Overall Width 6.00 BSC Е Molded Package Width E1 3.90 BSC 8.65 BSC **Overall Length** D Chamfer (optional) 0.25 0.50 h Foot Length L 0.40 1.27 Footprint L1 1.04 REF Foot Angle Ô° 8° ø \_ Lead Thickness 0.17 0.25 С \_ Lead Width 0.31 0.51 b \_ Mold Draft Angle Top 5° 15° α \_ Mold Draft Angle Bottom 5° 15° β \_

Notes:

Note:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-065B

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:   | Technical Publications Manager         | Total Pages Sent                                       |

|-------|----------------------------------------|--------------------------------------------------------|

| RE:   | Reader Response                        |                                                        |

| From  | i: Name                                |                                                        |

|       | Company                                |                                                        |

|       | Address                                |                                                        |

|       | City / State / ZIP / Country           |                                                        |

|       | Telephone: ()                          | FAX: ()                                                |

| Appli | cation (optional):                     |                                                        |

| Woul  | ld you like a reply? <u>Y</u>          |                                                        |

| Devi  | ce: PIC16F526                          | Literature Number: DS41326E                            |

| Ques  | stions:                                |                                                        |

| 1. V  | What are the best features of this do  | cument?                                                |

|       |                                        |                                                        |

|       |                                        |                                                        |

| 2. ⊦  | low does this document meet your l     | hardware and software development needs?               |

| _     |                                        |                                                        |

| _     |                                        |                                                        |

| 3. E  | Do you find the organization of this d | locument easy to follow? If not, why?                  |

| _     |                                        |                                                        |

| _     |                                        |                                                        |

| 4. V  | What additions to the document do y    | you think would enhance the structure and subject?     |

| _     |                                        |                                                        |

| _     |                                        |                                                        |

| 5. V  | What deletions from the document c     | ould be made without affecting the overall usefulness? |

| -     |                                        |                                                        |

| -     |                                        | · · · · · · · · · · · · · · · · · · ·                  |

| 6. I  | s there any incorrect or misleading i  | nformation (what and where)?                           |

| _     |                                        |                                                        |

| 7 1   | low would you improve this desume      | hat?                                                   |

| 7. F  | low would you improve this docume      | 211.1                                                  |

| _     |                                        |                                                        |

| _     |                                        |                                                        |