Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | CIP-51 8051                                                            |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 72MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 20                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1.25K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                            |

| Data Converters            | A/D 12x14b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 24-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 24-QFN (3x3)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8lb10f16e-b-qfn24 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Feature List

The EFM8LB1 device family are fully integrated, mixed-signal system-on-a-chip MCUs. Highlighted features are listed below.

- Core:

- Pipelined CIP-51 Core

- · Fully compatible with standard 8051 instruction set

- 70% of instructions execute in 1-2 clock cycles

- 72 MHz maximum operating frequency

- Memory:

- Up to 64 kB flash memory (63 kB user-accessible), in-system re-programmable from firmware in 512-byte sectors

- Up to 4352 bytes RAM (including 256 bytes standard 8051 RAM and 4096 bytes on-chip XRAM)

- · Power:

- Internal LDO regulator for CPU core voltage

- · Power-on reset circuit and brownout detectors

- I/O: Up to 29 total multifunction I/O pins:

- Up to 25 pins 5 V tolerant under bias

- Selectable state retention through reset events

- · Flexible peripheral crossbar for peripheral routing

- 5 mA source, 12.5 mA sink allows direct drive of LEDs

- · Clock Sources:

- Internal 72 MHz oscillator with accuracy of ±2%

- Internal 24.5 MHz oscillator with ±2% accuracy

- · Internal 80 kHz low-frequency oscillator

- External CMOS clock option

- External crystal/RC oscillator (up to 25 MHz)

- Analog:

- 14/12/10-Bit Analog-to-Digital Converter (ADC)

- Internal calibrated temperature sensor (±3 °C)

- 4 x 12-Bit Digital-to-Analog Converters (DAC)

- 2 x Low-current analog comparators with adjustable reference

- Communications and Digital Peripherals:

- 2 x UART, up to 3 Mbaud

- SPI™ Master / Slave, up to 12 Mbps

- SMBus™/I2C™ Master / Slave, up to 400 kbps

- I<sup>2</sup>C High-Speed Slave, up to 3.4 Mbps

- 16-bit CRC unit, supporting automatic CRC of flash at 256byte boundaries

- 4 Configurable Logic Units

- Timers/Counters and PWM:

- 6-channel Programmable Counter Array (PCA) supporting PWM, capture/compare, and frequency output modes

- 6 x 16-bit general-purpose timers

- Independent watchdog timer, clocked from the low frequency oscillator

- On-Chip, Non-Intrusive Debugging

- · Full memory and register inspection

- Four hardware breakpoints, single-stepping

- Pre-programmed UART or SMBus bootloader

With on-chip power-on reset, voltage supply monitor, watchdog timer, and clock oscillator, the EFM8LB1 devices are truly standalone system-on-a-chip solutions. The flash memory is reprogrammable in-circuit, providing nonvolatile data storage and allowing field upgrades of the firmware. The on-chip debugging interface (C2) allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging. Device operation is specified from 2.2 V up to a 3.6 V supply. Devices are AEC-Q100 qualified (pending) and available in 4x4 mm 32-pin QFN, 3x3 mm 24-pin QFN, 32-pin QFP, or 24-pin QSOP packages. All package options are lead-free and RoHS compliant.

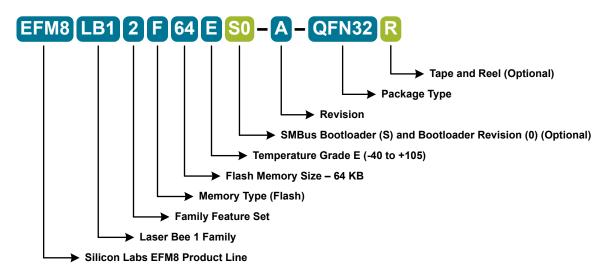

## 2. Ordering Information

Figure 2.1. EFM8LB1 Part Numbering

All EFM8LB1 family members have the following features:

- CIP-51 Core running up to 72 MHz

- Three Internal Oscillators (72 MHz, 24.5 MHz and 80 kHz)

- SMBus

- I2C Slave

- SPI

- 2 UARTs

- · 6-Channel Programmable Counter Array (PWM, Clock Generation, Capture/Compare)

- Six 16-bit Timers

- Four Configurable Logic Units

- 14-bit Analog-to-Digital Converter with integrated multiplexer, voltage reference, temperature sensor, channel sequencer, and directto-XRAM data transfer

- Two Analog Comparators

- 16-bit CRC Unit

- AEC-Q100 qualified (pending)

In addition to these features, each part number in the EFM8LB1 family has a set of features that vary across the product line. The product selection guide shows the features available on each family member.

| Ordering Part Number | Flash Memory (kB) | RAM (Bytes) | Digital Port I/Os (Total) | ADC0 Channels | Voltage DACs | Comparator 0 Inputs | Comparator 1 Inputs | Bootloader Type | Pb-free (RoHS Compliant) | Temperature Range | Package |

|----------------------|-------------------|-------------|---------------------------|---------------|--------------|---------------------|---------------------|-----------------|--------------------------|-------------------|---------|

| EFM8LB12F64E-B-QFN32 | 64                | 4352        | 29                        | 20            | 4            | 10                  | 9                   | UART            | Yes                      | -40 to +105 °C    | QFN32   |

| EFM8LB12F64E-B-QFP32 | 64                | 4352        | 28                        | 20            | 4            | 10                  | 9                   | UART            | Yes                      | -40 to +105 °C    | QFP32   |

| EFM8LB12F64E-B-QFN24 | 64                | 4352        | 20                        | 12            | 4            | 6                   | 6                   | UART            | Yes                      | -40 to +105 °C    | QFN24   |

### Table 2.1. Product Selection Guide

### 3.2 Power

All internal circuitry draws power from the VDD supply pin. External I/O pins are powered from the VIO supply voltage (or VDD on devices without a separate VIO connection), while most of the internal circuitry is supplied by an on-chip LDO regulator. Control over the device power can be achieved by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and placed in low power mode. Digital peripherals, such as timers and serial buses, have their clocks gated off and draw little power when they are not in use.

### Table 3.1. Power Modes

| Power Mode | Details                                                                                                                                                                                                                                                        | Mode Entry                                                                            | Wake-Up Sources                                                                                                                                                                                  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal     | Core and all peripherals clocked and fully operational                                                                                                                                                                                                         |                                                                                       |                                                                                                                                                                                                  |

| ldle       | <ul> <li>Core halted</li> <li>All peripherals clocked and fully operational</li> <li>Code resumes execution on wake event</li> </ul>                                                                                                                           | Set IDLE bit in PCON0                                                                 | Any interrupt                                                                                                                                                                                    |

| Suspend    | <ul> <li>Core and peripheral clocks halted</li> <li>HFOSC0 and HFOSC1 oscillators stopped</li> <li>Regulator in normal bias mode for fast wake</li> <li>Timer 3 and 4 may clock from LFOSC0</li> <li>Code resumes execution on wake event</li> </ul>           | <ol> <li>Switch SYSCLK to<br/>HFOSC0</li> <li>Set SUSPEND bit in<br/>PCON1</li> </ol> | <ul> <li>Timer 4 Event</li> <li>SPI0 Activity</li> <li>I2C0 Slave Activity</li> <li>Port Match Event</li> <li>Comparator 0 Falling<br/>Edge</li> <li>CLUn Interrupt-Enabled<br/>Event</li> </ul> |

| Stop       | <ul> <li>All internal power nets shut down</li> <li>Pins retain state</li> <li>Exit on any reset source</li> </ul>                                                                                                                                             | 1. Clear STOPCF bit in<br>REG0CN<br>2. Set STOP bit in<br>PCON0                       | Any reset source                                                                                                                                                                                 |

| Snooze     | <ul> <li>Core and peripheral clocks halted</li> <li>HFOSC0 and HFOSC1 oscillators stopped</li> <li>Regulator in low bias current mode for energy savings</li> <li>Timer 3 and 4 may clock from LFOSC0</li> <li>Code resumes execution on wake event</li> </ul> | <ol> <li>Switch SYSCLK to<br/>HFOSC0</li> <li>Set SNOOZE bit in<br/>PCON1</li> </ol>  | <ul> <li>Timer 4 Event</li> <li>SPI0 Activity</li> <li>I2C0 Slave Activity</li> <li>Port Match Event</li> <li>Comparator 0 Falling<br/>Edge</li> <li>CLUn Interrupt-Enabled<br/>Event</li> </ul> |

| Shutdown   | <ul> <li>All internal power nets shut down</li> <li>Pins retain state</li> <li>Exit on pin or power-on reset</li> </ul>                                                                                                                                        | 1. Set STOPCF bit in<br>REG0CN<br>2. Set STOP bit in<br>PCON0                         | <ul><li>RSTb pin reset</li><li>Power-on reset</li></ul>                                                                                                                                          |

### 3.3 I/O

Digital and analog resources are externally available on the device's multi-purpose I/O pins. Port pins P0.0-P2.3 can be defined as general-purpose I/O (GPIO), assigned to one of the internal digital resources through the crossbar or dedicated channels, or assigned to an analog function. Port pins P2.4 to P3.7 can be used as GPIO. Additionally, the C2 Interface Data signal (C2D) is shared with P3.0 or P3.7, depending on the package option.

The port control block offers the following features:

- Up to 29 multi-functions I/O pins, supporting digital and analog functions.

- · Flexible priority crossbar decoder for digital peripheral assignment.

- Two drive strength settings for each port.

- State retention feature allows pins to retain configuration through most reset sources.

- Two direct-pin interrupt sources with dedicated interrupt vectors (INT0 and INT1).

- Up to 24 direct-pin interrupt sources with shared interrupt vector (Port Match).

### 3.4 Clocking

The CPU core and peripheral subsystem may be clocked by both internal and external oscillator resources. By default, the system clock comes up running from the 24.5 MHz oscillator divided by 8.

The clock control system offers the following features:

- Provides clock to core and peripherals.

- 24.5 MHz internal oscillator (HFOSC0), accurate to ±2% over supply and temperature corners.

- 72 MHz internal oscillator (HFOSC1), accurate to ±2% over supply and temperature corners.

- 80 kHz low-frequency oscillator (LFOSC0).

- External RC, CMOS, and high-frequency crystal clock options (EXTCLK).

- · Clock divider with eight settings for flexible clock scaling:

- Divide the selected clock source by 1, 2, 4, 8, 16, 32, 64, or 128.

- HFOSC0 and HFOSC1 include 1.5x pre-scalers for further flexibility.

### 3.5 Counters/Timers and PWM

### Programmable Counter Array (PCA0)

The programmable counter array (PCA) provides multiple channels of enhanced timer and PWM functionality while requiring less CPU intervention than standard counter/timers. The PCA consists of a dedicated 16-bit counter/timer and one 16-bit capture/compare module for each channel. The counter/timer is driven by a programmable timebase that has flexible external and internal clocking options. Each capture/compare module may be configured to operate independently in one of five modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, or Pulse-Width Modulated (PWM) Output. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the crossbar to port I/O when enabled.

- 16-bit time base

- Programmable clock divisor and clock source selection

- · Up to six independently-configurable channels

- 8, 9, 10, 11 and 16-bit PWM modes (center or edge-aligned operation)

- Output polarity control

- Frequency output mode

- · Capture on rising, falling or any edge

- · Compare function for arbitrary waveform generation

- · Software timer (internal compare) mode

- · Can accept hardware "kill" signal from comparator 0 or comparator 1

# 4.1.10 Voltage Reference

| Parameter                           | Symbol                    | Test Condition                                         | Min   | Тур  | Мах   | Unit   |

|-------------------------------------|---------------------------|--------------------------------------------------------|-------|------|-------|--------|

| Internal Fast Settling Reference    |                           |                                                        |       |      |       |        |

| Output Voltage                      | V <sub>REFFS</sub>        |                                                        | 1.62  | 1.65 | 1.68  | V      |

| (Full Temperature and Supply Range) |                           |                                                        |       |      |       |        |

| Temperature Coefficient             | TC <sub>REFFS</sub>       |                                                        | _     | 50   | _     | ppm/°C |

| Turn-on Time                        | t <sub>REFFS</sub>        |                                                        | _     | —    | 1.5   | μs     |

| Power Supply Rejection              | PSRR <sub>REF</sub><br>FS |                                                        | —     | 400  | _     | ppm/V  |

| On-chip Precision Reference         | 1                         |                                                        |       | 1    |       |        |

| Valid Supply Range                  | V <sub>DD</sub>           | 1.2 V Output                                           | 2.2   |      | 3.6   | V      |

|                                     |                           | 2.4 V Output                                           | 2.7   | _    | 3.6   | V      |

| Output Voltage                      | V <sub>REFP</sub>         | 1.2 V Output, V <sub>DD</sub> = 3.3 V, T = 25<br>°C    | 1.195 | 1.2  | 1.205 | V      |

|                                     |                           | 1.2 V Output                                           | 1.18  | 1.2  | 1.22  | V      |

|                                     |                           | 2.4 V Output, V <sub>DD</sub> = 3.3 V, T = 25<br>°C    | 2.39  | 2.4  | 2.41  | V      |

|                                     |                           | 2.4 V Output                                           | 2.36  | 2.4  | 2.44  | V      |

| Turn-on Time, settling to 0.5 LSB   | t <sub>VREFP</sub>        | 4.7 μF tantalum + 0.1 μF ceramic<br>bypass on VREF pin | —     | 3    | _     | ms     |

|                                     |                           | 0.1 μF ceramic bypass on VREF pin                      | —     | 100  | _     | μs     |

| Load Regulation                     | LR <sub>VREFP</sub>       | VREF = 2.4 V, Load = 0 to 200 $\mu$ A to GND           | —     | 8    | _     | μV/μΑ  |

|                                     |                           | VREF = 1.2 V, Load = 0 to 200 μA<br>to GND             | —     | 5    | _     | μV/μΑ  |

| Load Capacitor                      | C <sub>VREFP</sub>        | Load = 0 to 200 µA to GND                              | 0.1   | _    | _     | μF     |

| Short-circuit current               | ISC <sub>VREFP</sub>      |                                                        | _     |      | 8     | mA     |

| Power Supply Rejection              | PSRR <sub>VRE</sub><br>FP |                                                        | _     | 75   | _     | dB     |

| External Reference                  |                           |                                                        |       |      |       |        |

| Input Current                       | I <sub>EXTREF</sub>       | ADC Sample Rate = 1 Msps;<br>VREF = 3.0 V              | _     | 5    | _     | μΑ     |

### 4.1.11 Temperature Sensor

| Parameter                                                | Symbol           | Test Condition        | Min  | Тур             | Max | Unit  |

|----------------------------------------------------------|------------------|-----------------------|------|-----------------|-----|-------|

| Uncalibrated Offset                                      | V <sub>OFF</sub> | T <sub>A</sub> = 0 °C |      | 751             |     | mV    |

| Uncalibrated Offset Error <sup>1</sup>                   | EOFF             | T <sub>A</sub> = 0 °C |      | 19              |     | mV    |

| Slope                                                    | м                |                       |      | 2.82            | _   | mV/°C |

| Slope Error <sup>1</sup>                                 | E <sub>M</sub>   |                       | _    | 29              | _   | µV/°C |

| Linearity                                                | LIN              | T = 0 °C to 70 °C     | -    | -0.1 to<br>0.15 | _   | °C    |

|                                                          |                  | T = -20 °C to 85 °C   | -    | -0.2 to<br>0.35 | _   | °C    |

|                                                          |                  | T = -40 °C to 105 °C  | _    | -0.4 to 0.8     | _   | °C    |

| Turn-on Time                                             | t <sub>ON</sub>  |                       | _    | 3.5             | _   | μs    |

| Temp Sensor Error Using Typical                          | Етот             | T = 0 °C to 70 °C     | -2.6 | _               | 1.8 | °C    |

| Slope and Factory-Calibrated Off-<br>set <sup>2, 3</sup> |                  | T = -20 °C to 85 °C   | -2.9 | _               | 2.7 | °C    |

|                                                          |                  | T = -40 °C to 105 °C  | -3.2 | _               | 4.2 | °C    |

### Table 4.11. Temperature Sensor

### Note:

1. Represents one standard deviation from the mean.

2. The factory-calibrated offset value is stored in the read-only area of flash in locations 0xFFD4 (low byte) and 0xFFD5 (high byte). The 14-bit result represents the output of the ADC when sampling the temp sensor using the 1.65 V internal voltage reference.

3. The temp sensor error includes the offset calibration error, slope error, and linearity error. The values are based upon characterization and are not tested across temperature in production. The values represent three standard deviations above and below the mean. Additional information on achieving high measurement accuracy is available in AN929: Accurate Temperature Sensing with the EFM8 Laser Bee MCU Family.

### 4.1.13 Comparators

| Parameter                      | Symbol             | Test Condition       | Min | Тур  | Max | Unit |

|--------------------------------|--------------------|----------------------|-----|------|-----|------|

| Response Time, CPMD = 00       | t <sub>RESP0</sub> | +100 mV Differential | _   | 100  | _   | ns   |

| (Highest Speed)                |                    | -100 mV Differential | _   | 150  | _   | ns   |

| Response Time, CPMD = 11 (Low- | t <sub>RESP3</sub> | +100 mV Differential |     | 1.5  | _   | μs   |

| est Power)                     |                    | -100 mV Differential | _   | 3.5  | _   | μs   |

| Positive Hysteresis            | HYS <sub>CP+</sub> | CPHYP = 00           | _   | 0.4  | _   | mV   |

| Mode 0 (CPMD = 00)             |                    | CPHYP = 01           | _   | 8    | _   | mV   |

|                                |                    | CPHYP = 10           | _   | 16   | _   | mV   |

|                                |                    | CPHYP = 11           |     | 32   | _   | mV   |

| Negative Hysteresis            | HYS <sub>CP-</sub> | CPHYN = 00           | _   | -0.4 | _   | mV   |

| Mode 0 (CPMD = 00)             |                    | CPHYN = 01           | _   | -8   | _   | mV   |

|                                |                    | CPHYN = 10           |     | -16  | _   | mV   |

|                                |                    | CPHYN = 11           | _   | -32  | _   | mV   |

| Positive Hysteresis            | HYS <sub>CP+</sub> | CPHYP = 00           |     | 0.5  | _   | mV   |

| Mode 1 (CPMD = 01)             |                    | CPHYP = 01           | _   | 6    | _   | mV   |

|                                |                    | CPHYP = 10           | _   | 12   | _   | mV   |

|                                |                    | CPHYP = 11           |     | 24   | _   | mV   |

| Negative Hysteresis            | HYS <sub>CP-</sub> | CPHYN = 00           | _   | -0.5 | _   | mV   |

| Mode 1 (CPMD = 01)             |                    | CPHYN = 01           | _   | -6   | _   | mV   |

|                                |                    | CPHYN = 10           |     | -12  | _   | mV   |

|                                |                    | CPHYN = 11           |     | -24  | _   | mV   |

| Positive Hysteresis            | HYS <sub>CP+</sub> | CPHYP = 00           |     | 0.7  | _   | mV   |

| Mode 2 (CPMD = 10)             |                    | CPHYP = 01           |     | 4.5  | _   | mV   |

|                                |                    | CPHYP = 10           |     | 9    | _   | mV   |

|                                |                    | CPHYP = 11           |     | 18   | _   | mV   |

| Negative Hysteresis            | HYS <sub>CP-</sub> | CPHYN = 00           |     | -0.6 | _   | mV   |

| Mode 2 (CPMD = 10)             |                    | CPHYN = 01           |     | -4.5 | _   | mV   |

|                                |                    | CPHYN = 10           |     | -9   | _   | mV   |

|                                |                    | CPHYN = 11           | _   | -18  | _   | mV   |

| Positive Hysteresis            | HYS <sub>CP+</sub> | CPHYP = 00           | _   | 1.5  | _   | mV   |

| Mode 3 (CPMD = 11)             |                    | CPHYP = 01           |     | 4    | _   | mV   |

|                                |                    | CPHYP = 10           | _   | 8    | _   | mV   |

|                                |                    | CPHYP = 11           |     | 16   | _   | mV   |

### Table 4.13. Comparators

| Parameter                         | Symbol             | Test Condition         | Min   | Тур  | Max                   | Unit |

|-----------------------------------|--------------------|------------------------|-------|------|-----------------------|------|

| Negative Hysteresis               | HYS <sub>CP-</sub> | CPHYN = 00             | —     | -1.5 | —                     | mV   |

| Mode 3 (CPMD = 11)                |                    | CPHYN = 01             | —     | -4   | _                     | mV   |

|                                   |                    | CPHYN = 10             | —     | -8   | —                     | mV   |

|                                   |                    | CPHYN = 11             | —     | -16  | —                     | mV   |

| Input Range (CP+ or CP-)          | V <sub>IN</sub>    |                        | -0.25 | _    | V <sub>IO</sub> +0.25 | V    |

| Input Pin Capacitance             | C <sub>CP</sub>    |                        | —     | 7.5  | —                     | pF   |

| Internal Reference DAC Resolution | N <sub>bits</sub>  |                        |       | 6    | 1                     | bits |

| Common-Mode Rejection Ratio       | CMRR <sub>CP</sub> |                        | —     | 70   | _                     | dB   |

| Power Supply Rejection Ratio      | PSRR <sub>CP</sub> |                        | —     | 72   | _                     | dB   |

| Input Offset Voltage              | V <sub>OFF</sub>   | T <sub>A</sub> = 25 °C | -10   | 0    | 10                    | mV   |

| Input Offset Tempco               | TC <sub>OFF</sub>  |                        | _     | 3.5  | _                     | μV/° |

# 4.1.14 Configurable Logic

## Table 4.14. Configurable Logic

| Parameter                           | Symbol           | Test Condition               | Min | Тур | Max   | Unit |

|-------------------------------------|------------------|------------------------------|-----|-----|-------|------|

| Propagation Delay                   | t <sub>DLY</sub> | Through single CLU           | _   | —   | 35.3  | ns   |

|                                     |                  | Using an external pin        |     |     |       |      |

|                                     |                  | Through single CLU           | _   | 3   | _     | ns   |

|                                     |                  | Using an internal connection |     |     |       |      |

| Clocking Frequency F <sub>CLK</sub> |                  | 1 or 2 CLUs Cascaded         | —   | —   | 73.5  | MHz  |

|                                     |                  | 3 or 4 CLUs Cascaded         |     |     | 36.75 | MHz  |

#### 4.3 Absolute Maximum Ratings

Stresses above those listed in Table 4.19 Absolute Maximum Ratings on page 30 may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

### Table 4.19. Absolute Maximum Ratings

| Parameter                                                                    | Symbol            | Test Condition                    | Min     | Мах                  | Unit |

|------------------------------------------------------------------------------|-------------------|-----------------------------------|---------|----------------------|------|

| Ambient Temperature Under Bias                                               | T <sub>BIAS</sub> |                                   | -55     | 125                  | °C   |

| Storage Temperature                                                          | T <sub>STG</sub>  |                                   | -65     | 150                  | °C   |

| Voltage on VDD                                                               | V <sub>DD</sub>   |                                   | GND-0.3 | 4.2                  | V    |

| Voltage on VIO <sup>2</sup>                                                  | V <sub>IO</sub>   |                                   | GND-0.3 | V <sub>DD</sub> +0.3 | V    |

| Voltage on I/O pins or RSTb, excluding                                       |                   | V <sub>IO</sub> > 3.3 V           | GND-0.3 | 5.8                  | V    |

| P2.0-P2.3 (QFN24 and QSOP24) or P3.0-P3.3 (QFN32 and QFP32)                  |                   | V <sub>IO</sub> < 3.3 V           | GND-0.3 | V <sub>IO</sub> +2.5 | V    |

| Voltage on P2.0-P2.3 (QFN24 and<br>QSOP24) or P3.0-P3.3 (QFN32 and<br>QFP32) | V <sub>IN</sub>   |                                   | GND-0.3 | V <sub>DD</sub> +0.3 | V    |

| Total Current Sunk into Supply Pin                                           | I <sub>VDD</sub>  |                                   | _       | 400                  | mA   |

| Total Current Sourced out of Ground<br>Pin                                   | I <sub>GND</sub>  |                                   | 400     | _                    | mA   |

| Current Sourced or Sunk by any I/O<br>Pin or RSTb                            | I <sub>IO</sub>   |                                   | -100    | 100                  | mA   |

| Operating Junction Temperature                                               | TJ                | T <sub>A</sub> = -40 °C to 105 °C | -40     | 130                  | °C   |

#### Note:

1. Exposure to maximum rating conditions for extended periods may affect device reliability.

2. In certain package configurations, the VIO and VDD supplies are bonded to the same pin.

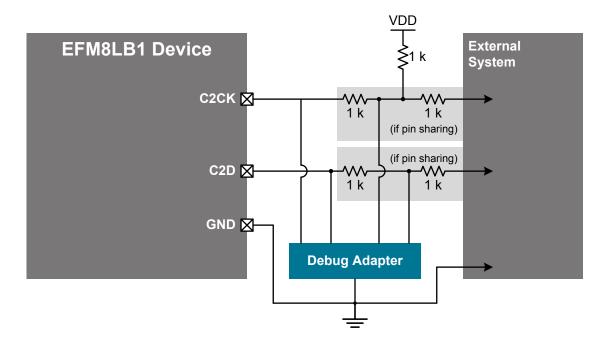

### 5.2 Debug

The diagram below shows a typical connection diagram for the debug connections pins. The pin sharing resistors are only required if the functionality on the C2D (a GPIO pin) and the C2CK (RSTb) is routed to external circuitry. For example, if the RSTb pin is connected to an external switch with debouncing filter or if the GPIO sharing with the C2D pin is connected to an external circuit, the pin sharing resistors and connections to the debug adapter must be placed on the hardware. Otherwise, these components and connections can be omitted.

For more information on debug connections, see the example schematics and information available in AN127: "Pin Sharing Techniques for the C2 Interface." Application notes can be found on the Silicon Labs website (http://www.silabs.com/8bit-appnotes) or in Simplicity Studio.

Figure 5.2. Debug Connection Diagram

### 5.3 Other Connections

Other components or connections may be required to meet the system-level requirements. Application Note AN203: "8-bit MCU Printed Circuit Board Design Notes" contains detailed information on these connections. Application Notes can be accessed on the Silicon Labs website (www.silabs.com/8bit-appnotes).

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 23            | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                         | ADC0.8           |

|               |          |                   |                     | CLU0A.13                        | CMP0P.8          |

|               |          |                   |                     | CLU1A.11                        | CMP0N.8          |

|               |          |                   |                     | CLU2B.10                        |                  |

|               |          |                   |                     | CLU3A.12                        |                  |

| 24            | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                         | ADC0.7           |

|               |          |                   |                     | CLU0B.12                        | CMP0P.7          |

|               |          |                   |                     | CLU1B.10                        | CMP0N.7          |

|               |          |                   |                     | CLU2A.11                        |                  |

|               |          |                   |                     | CLU3B.13                        |                  |

| 25            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                         | ADC0.6           |

|               |          |                   |                     | CLU1OUT                         | CMP0P.6          |

|               |          |                   |                     | CLU0A.12                        | CMP0N.6          |

|               |          |                   |                     | CLU1A.10                        | CMP1P.1          |

|               |          |                   |                     | CLU2A.10                        | CMP1N.1          |

|               |          |                   |                     | CLU3B.12                        |                  |

| 26            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                         | ADC0.5           |

|               |          |                   |                     | INT0.7                          | CMP0P.5          |

|               |          |                   |                     | INT1.7                          | CMP0N.5          |

|               |          |                   |                     | CLU0B.11                        | CMP1P.0          |

|               |          |                   |                     | CLU1B.9                         | CMP1N.0          |

|               |          |                   |                     | CLU3A.11                        |                  |

| 27            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                         | ADC0.4           |

|               |          |                   |                     | CNVSTR                          | CMP0P.4          |

|               |          |                   |                     | INT0.6                          | CMP0N.4          |

|               |          |                   |                     | INT1.6                          |                  |

|               |          |                   |                     | CLU0A.11                        |                  |

|               |          |                   |                     | CLU1B.8                         |                  |

|               |          |                   |                     | CLU3A.10                        |                  |

| 28            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                         | ADC0.3           |

|               |          |                   |                     | INT0.5                          | CMP0P.3          |

|               |          |                   |                     | INT1.5                          | CMP0N.3          |

|               |          |                   |                     | UART0_RX                        |                  |

|               |          |                   |                     | CLU0B.10                        |                  |

|               |          |                   |                     | CLU1A.9                         |                  |

|               |          |                   |                     | CLU3B.11                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 29            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.2           |

|               |          |                   |                     | INT0.4                          | CMP0P.2          |

|               |          |                   |                     | INT1.4                          | CMP0N.2          |

|               |          |                   |                     | UART0_TX                        |                  |

|               |          |                   |                     | CLU0A.10                        |                  |

|               |          |                   |                     | CLU1A.8                         |                  |

|               |          |                   |                     | CLU3B.10                        |                  |

| 30            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | XTAL2            |

|               |          |                   |                     | EXTCLK                          |                  |

|               |          |                   |                     | INT0.3                          |                  |

|               |          |                   |                     | INT1.3                          |                  |

|               |          |                   |                     | CLU0B.9                         |                  |

|               |          |                   |                     | CLU2B.9                         |                  |

|               |          |                   |                     | CLU3A.9                         |                  |

| 31            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | XTAL1            |

|               |          |                   |                     | INT0.2                          | ADC0.1           |

|               |          |                   |                     | INT1.2                          | CMP0P.1          |

|               |          |                   |                     | CLU0OUT                         | CMP0N.1          |

|               |          |                   |                     | CLU0A.9                         |                  |

|               |          |                   |                     | CLU2B.8                         |                  |

|               |          |                   |                     | CLU3A.8                         |                  |

| 32            | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                         | ADC0.0           |

|               |          |                   |                     | INT0.1                          | CMP0P.0          |

|               |          |                   |                     | INT1.1                          | CMP0N.0          |

|               |          |                   |                     | CLU0B.8                         | AGND             |

|               |          |                   |                     | CLU2A.9                         |                  |

|               |          |                   |                     | CLU3B.9                         |                  |

| Center        | GND      | Ground            |                     |                                 |                  |

| Pin<br>Number | Pin Name  | Description         | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|-----------|---------------------|---------------------|---------------------------------|------------------|

| 2             | P0.0      | Multifunction I/O   | Yes                 | P0MAT.0                         | VREF             |

|               |           |                     |                     | INT0.0                          |                  |

|               |           |                     |                     | INT1.0                          |                  |

|               |           |                     |                     | CLU0A.8                         |                  |

|               |           |                     |                     | CLU2A.8                         |                  |

|               |           |                     |                     | CLU3B.8                         |                  |

| 3             | GND       | Ground              |                     |                                 |                  |

| 4             | VDD / VIO | Supply Power Input  |                     |                                 |                  |

| 5             | RSTb /    | Active-low Reset /  |                     |                                 |                  |

|               | C2CK      | C2 Debug Clock      |                     |                                 |                  |

| 6             | P3.0 /    | Multifunction I/O / |                     |                                 |                  |

|               | C2D       | C2 Debug Data       |                     |                                 |                  |

| 7             | P2.3      | Multifunction I/O   | Yes                 | P2MAT.3                         | DAC3             |

|               |           |                     |                     | CLU1B.15                        |                  |

|               |           |                     |                     | CLU2B.15                        |                  |

|               |           |                     |                     | CLU3A.15                        |                  |

| 8             | P2.2      | Multifunction I/O   | Yes                 | P2MAT.2                         | DAC2             |

|               |           |                     |                     | CLU1A.15                        |                  |

|               |           |                     |                     | CLU2B.14                        |                  |

|               |           |                     |                     | CLU3A.14                        |                  |

| 9             | P2.1      | Multifunction I/O   | Yes                 | P2MAT.1                         | DAC1             |

|               |           |                     |                     | CLU1B.14                        |                  |

|               |           |                     |                     | CLU2A.15                        |                  |

|               |           |                     |                     | CLU3B.15                        |                  |

| 10            | P2.0      | Multifunction I/O   | Yes                 | P2MAT.0                         | DAC0             |

|               |           |                     |                     | CLU1A.14                        |                  |

|               |           |                     |                     | CLU2A.14                        |                  |

|               |           |                     |                     | CLU3B.14                        |                  |

| 11            | P1.6      | Multifunction I/O   | Yes                 | P1MAT.6                         | ADC0.11          |

|               |           |                     |                     | CLU3OUT                         | CMP1P.5          |

|               |           |                     |                     | CLU0A.15                        | CMP1N.5          |

|               |           |                     |                     | CLU1B.12                        |                  |

|               |           |                     |                     | CLU2A.12                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 11            | P2.1     | Multifunction I/O | Yes                 | P2MAT.1                         | DAC1             |

|               |          |                   |                     | CLU1B.14                        |                  |

|               |          |                   |                     | CLU2A.15                        |                  |

|               |          |                   |                     | CLU3B.15                        |                  |

| 12            | P2.0     | Multifunction I/O | Yes                 | P2MAT.0                         | DAC0             |

|               |          |                   |                     | CLU1A.14                        |                  |

|               |          |                   |                     | CLU2A.14                        |                  |

|               |          |                   |                     | CLU3B.14                        |                  |

| 13            | P1.7     | Multifunction I/O | Yes                 | P1MAT.7                         | ADC0.12          |

|               |          |                   |                     | CLU0B.15                        | CMP1P.6          |

|               |          |                   |                     | CLU1B.13                        | CMP1N.6          |

|               |          |                   |                     | CLU2A.13                        |                  |

| 14            | P1.6     | Multifunction I/O | Yes                 | P1MAT.6                         | ADC0.11          |

|               |          |                   |                     | CLU3OUT                         | CMP1P.5          |

|               |          |                   |                     | CLU0A.15                        | CMP1N.5          |

|               |          |                   |                     | CLU1B.12                        |                  |

|               |          |                   |                     | CLU2A.12                        |                  |

| 15            | P1.5     | Multifunction I/O | Yes                 | P1MAT.5                         | ADC0.10          |

|               |          |                   |                     | CLU2OUT                         | CMP1P.4          |

|               |          |                   |                     | CLU0B.14                        | CMP1N.4          |

|               |          |                   |                     | CLU1A.13                        |                  |

|               |          |                   |                     | CLU2B.13                        |                  |

| 16            | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                         | ADC0.9           |

|               |          |                   |                     | I2C0_SCL                        | CMP1P.3          |

|               |          |                   |                     | CLU0A.14                        | CMP1N.3          |

|               |          |                   |                     | CLU1A.12                        |                  |

|               |          |                   |                     | CLU2B.12                        |                  |

| 17            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                         | CMP1P.2          |

|               |          |                   |                     | I2C0_SDA                        | CMP1N.2          |

|               |          |                   |                     | CLU0B.13                        |                  |

|               |          |                   |                     | CLU1B.11                        |                  |

|               |          |                   |                     | CLU2B.11                        |                  |

|               |          |                   |                     | CLU3A.13                        |                  |

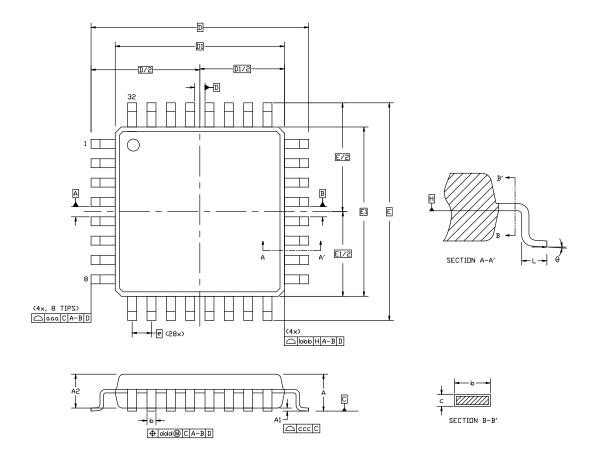

| Dimension                                                                                                   | Min | Тур | Мах |  |  |

|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Note:                                                                                                       |     |     |     |  |  |

| 1. All dimensions shown are in millimeters (mm) unless otherwise noted.                                     |     |     |     |  |  |

| 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.                                                       |     |     |     |  |  |

| 3. This drawing conforms to JEDEC Solid State Outline MO-220.                                               |     |     |     |  |  |

| 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components. |     |     |     |  |  |

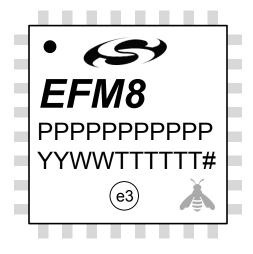

# 8. QFP32 Package Specifications

### 8.1 QFP32 Package Dimensions

Figure 8.1. QFP32 Package Drawing

## Table 8.1. QFP32 Package Dimensions

| Dimension | Min            | Тур  | Мах  |  |

|-----------|----------------|------|------|--|

| A         | _              |      | 1.20 |  |

| A1        | 0.05           | —    | 0.15 |  |

| A2        | 0.95           | 1.00 | 1.05 |  |

| b         | 0.30           | 0.37 | 0.45 |  |

| C         | 0.09           | —    | 0.20 |  |

| D         | 9.00 BSC       |      |      |  |

| D1        | 7.00 BSC       |      |      |  |

| е         | 0.80 BSC       |      |      |  |

| E         | 9.00 BSC       |      |      |  |

| E1        | 7.00 BSC       |      |      |  |

| L         | 0.50 0.60 0.70 |      |      |  |

The package marking consists of:

- PPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

- # The device revision (A, B, etc.).

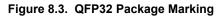

### 9.2 QFN24 PCB Land Pattern

Figure 9.2. QFN24 PCB Land Pattern Drawing

## Table 9.2. QFN24 PCB Land Pattern Dimensions

| Dimension | Min       | Мах |  |

|-----------|-----------|-----|--|

| C1        | 3.00      |     |  |

| C2        | 3.00      |     |  |

| е         | 0.4 REF   |     |  |

| X1        | 0.20      |     |  |

| X2        | 1.80      |     |  |

| Y1        | 0.80      |     |  |

| Y2        | 1.80      |     |  |

| Y3        | 0.4       |     |  |

| f         | 2.50 REF  |     |  |

| С         | 0.25 0.35 |     |  |

| Dimension                                                                                                                                                           | Min                         | Max |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|--|--|

| Note:                                                                                                                                                               |                             |     |  |  |

| 1. All dimensions shown are in millimeters (n                                                                                                                       | nm) unless otherwise noted. |     |  |  |

| 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.                                                                                          |                             |     |  |  |

| 3. This Land Pattern Design is based on the IPC-SM-782 guidelines.                                                                                                  |                             |     |  |  |

| 4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad. |                             |     |  |  |

| 5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.                             |                             |     |  |  |

| 6. The stencil thickness should be 0.125 mm (5 mils).                                                                                                               |                             |     |  |  |

| 7. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.                                                                             |                             |     |  |  |

| 8. A 2 x 1 array of 0.7 mm x 1.6 mm openings on a 0.9 mm pitch should be used for the center pad.                                                                   |                             |     |  |  |

| 9. A No-Clean, Type-3 solder paste is recom                                                                                                                         | mended.                     |     |  |  |

10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

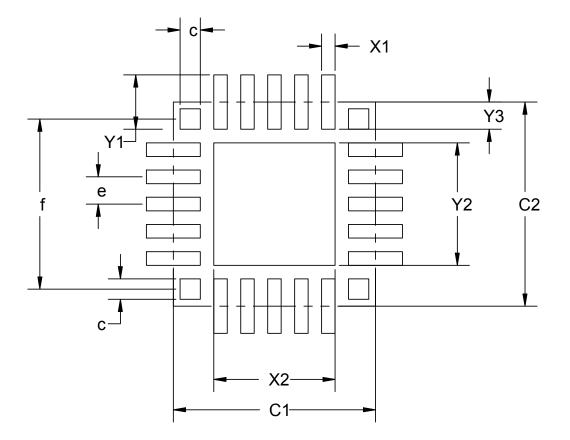

## 9.3 QFN24 Package Marking

Figure 9.3. QFN24 Package Marking

The package marking consists of:

- PPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

- # The device revision (A, B, etc.).

# 10. QSOP24 Package Specifications

### 10.1 QSOP24 Package Dimensions

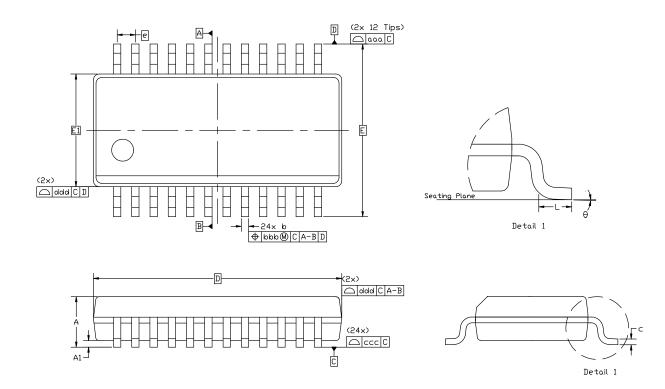

Figure 10.1. QSOP24 Package Drawing

### Table 10.1. QSOP24 Package Dimensions

| Dimension | Min         | Тур | Мах  |  |

|-----------|-------------|-----|------|--|

| A         | _           | —   | 1.75 |  |

| A1        | 0.10        | —   | 0.25 |  |

| b         | 0.20        | —   | 0.30 |  |

| С         | 0.10        | _   | 0.25 |  |

| D         | 8.65 BSC    |     |      |  |

| E         | 6.00 BSC    |     |      |  |

| E1        | 3.90 BSC    |     |      |  |

| e         | 0.635 BSC   |     |      |  |

| L         | 0.40 — 1.27 |     | 1.27 |  |

| theta     | 0°          | —   | 8°   |  |