#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | CIP-51 8051                                                               |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 72MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                               |

| Data Converters            | A/D 12x14b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 24-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 24-QFN (3x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8lb10f16es0-b-qfn24r |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Universal Asynchronous Receiver/Transmitter (UART1)

UART1 is an asynchronous, full duplex serial port offering a variety of data formatting options. A dedicated baud rate generator with a 16-bit timer and selectable prescaler is included, which can generate a wide range of baud rates. A received data FIFO allows UART1 to receive multiple bytes before data is lost and an overflow occurs.

UART1 provides the following features:

- · Asynchronous transmissions and receptions

- Dedicated baud rate generator supports baud rates up to SYSCLK/2 (transmit) or SYSCLK/8 (receive)

- 5, 6, 7, 8, or 9 bit data

- Automatic start and stop generation

- Automatic parity generation and checking

- · Single-byte buffer on transmit and receive

- Auto-baud detection

- · LIN break and sync field detection

- CTS / RTS hardware flow control

### Serial Peripheral Interface (SPI0)

The serial peripheral interface (SPI) module provides access to a flexible, full-duplex synchronous serial bus. The SPI can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select the SPI in slave mode, or to disable master mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a firmware-controlled chip-select output in master mode, or disable to reduce the number of pins required. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

- Supports 3- or 4-wire master or slave modes

- · Supports external clock frequencies up to 12 Mbps in master or slave mode

- · Support for all clock phase and polarity modes

- 8-bit programmable clock rate (master)

- Programmable receive timeout (slave)

- · Two byte FIFO on transmit and receive

- · Can operate in suspend or snooze modes and wake the CPU on reception of a byte

- · Support for multiple masters on the same data lines

#### System Management Bus / I2C (SMB0)

The SMBus I/O interface is a two-wire, bi-directional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus.

The SMBus module includes the following features:

- · Standard (up to 100 kbps) and Fast (400 kbps) transfer speeds

- · Support for master, slave, and multi-master modes

- Hardware synchronization and arbitration for multi-master mode

- · Clock low extending (clock stretching) to interface with faster masters

- · Hardware support for 7-bit slave and general call address recognition

- Firmware support for 10-bit slave address decoding

- · Ability to inhibit all slave states

- Programmable data setup/hold times

- · Transmit and receive FIFOs (one byte) to help increase throughput in faster applications

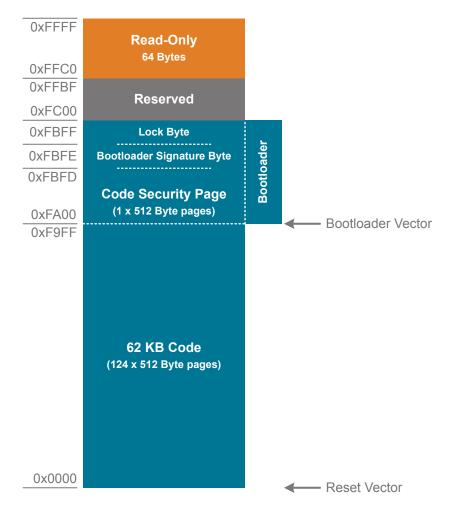

### 3.10 Bootloader

All devices come pre-programmed with a UART0 bootloader or an SMBus bootloader. These bootloaders reside in the code security page, which is the last page of code flash; they can be erased if they are not needed.

The byte before the Lock Byte is the Bootloader Signature Byte. Setting this byte to a value of 0xA5 indicates the presence of the bootloader in the system. Any other value in this location indicates that the bootloader is not present in flash.

When a bootloader is present, the device will jump to the bootloader vector after any reset, allowing the bootloader to run. The bootloader then determines if the device should stay in bootload mode or jump to the reset vector located at 0x0000. When the bootloader is not present, the device will jump to the reset vector of 0x0000 after any reset.

More information about the bootloader protocol and usage can be found in *AN945: EFM8 Factory Bootloader User Guide*. Application notes can be found on the Silicon Labs website (www.silabs.com/8bit-appnotes) or within Simplicity Studio by using the [Application Notes] tile.

Figure 3.2. Flash Memory Map with Bootloader - 62.5 KB Devices

| Table 3.2. | Summary | of Pins fo | or Bootloader | Communication |

|------------|---------|------------|---------------|---------------|

|------------|---------|------------|---------------|---------------|

| Bootloader | Pins for Bootload Communication |

|------------|---------------------------------|

| UART       | TX – P0.4                       |

|            | RX – P0.5                       |

| SMBus      | P0.2 – SDA <sup>1</sup>         |

|            | P0.3 – SCL <sup>1</sup>         |

# 4. Electrical Specifications

## 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the conditions listed in Table 4.1 Recommended Operating Conditions on page 14, unless stated otherwise.

Table 4.1. Recommended Operating Conditions

## 4.1.1 Recommended Operating Conditions

| Parameter                                          | Symbol              | Test Condition | Min | Тур | Мах             | Unit |

|----------------------------------------------------|---------------------|----------------|-----|-----|-----------------|------|

| Operating Supply Voltage on VDD                    | V <sub>DD</sub>     |                | 2.2 | _   | 3.6             | V    |

| Operating Supply Voltage on VIO <sup>2,</sup><br>3 | V <sub>IO</sub>     |                | 2.2 |     | V <sub>DD</sub> | V    |

| System Clock Frequency                             | f <sub>SYSCLK</sub> |                | 0   | —   | 73.5            | MHz  |

| Operating Ambient Temperature                      | T <sub>A</sub>      |                | -40 | —   | 105             | °C   |

| Note:                                              |                     |                |     |     |                 |      |

Note:

1. All voltages with respect to GND

2. In certain package configurations, the VIO and VDD supplies are bonded to the same pin.

3. GPIO levels are undefined whenever VIO is less than 1 V.

## 4.1.2 Power Consumption

| Parameter                                                                                    | Symbol              | Test Condition                                       | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------|-----|------|------|------|

| Digital Core Supply Current                                                                  | 1                   |                                                      | 1   |      |      |      |

| Normal Mode-Full speed with code                                                             | I <sub>DD</sub>     | F <sub>SYSCLK</sub> = 72 MHz (HFOSC1) <sup>2</sup>   | _   | 12.9 | 15   | mA   |

| executing from flash                                                                         |                     | F <sub>SYSCLK</sub> = 24.5 MHz (HFOSC0) <sup>2</sup> | _   | 4.2  | 5    | mA   |

|                                                                                              |                     | F <sub>SYSCLK</sub> = 1.53 MHz (HFOSC0) <sup>2</sup> | _   | 625  | 1050 | μA   |

|                                                                                              |                     | F <sub>SYSCLK</sub> = 80 kHz <sup>3</sup>            | _   | 155  | 575  | μA   |

| dle Mode-Core halted with periph-                                                            | I <sub>DD</sub>     | F <sub>SYSCLK</sub> = 72 MHz (HFOSC1) <sup>2</sup>   | _   | 9.6  | 11.1 | mA   |

| erals running                                                                                |                     | F <sub>SYSCLK</sub> = 24.5 MHz (HFOSC0) <sup>2</sup> | _   | 3.14 | 3.8  | mA   |

|                                                                                              |                     | F <sub>SYSCLK</sub> = 1.53 MHz (HFOSC0) <sup>2</sup> | _   | 520  | 950  | μA   |

|                                                                                              |                     | F <sub>SYSCLK</sub> = 80 kHz <sup>3</sup>            | _   | 135  | 550  | μA   |

| Suspend Mode-Core halted and                                                                 | I <sub>DD</sub>     | LFO Running                                          | _   | 125  | 545  | μA   |

| high frequency clocks stopped,<br>Supply monitor off.                                        |                     | LFO Stopped                                          | _   | 120  | 535  | μA   |

| Snooze Mode-Core halted and                                                                  | I <sub>DD</sub>     | LFO Running                                          | _   | 23   | 430  | μA   |

| nigh frequency clocks stopped.<br>Regulator in low-power state, Sup-<br>oly monitor off.     |                     | LFO Stopped                                          | -   | 19   | 425  | μA   |

| Stop Mode—Core halted and all<br>clocks stopped,Internal LDO On,<br>Supply monitor off.      | I <sub>DD</sub>     |                                                      | _   | 120  | 535  | μA   |

| Shutdown Mode—Core halted and<br>all clocks stopped,Internal LDO<br>Off, Supply monitor off. | IDD                 |                                                      | _   | 0.2  | 2.1  | μA   |

| Analog Peripheral Supply Current                                                             | ts                  |                                                      |     |      |      |      |

| High-Frequency Oscillator 0                                                                  | I <sub>HFOSC0</sub> | Operating at 24.5 MHz,                               | _   | 120  | 135  | μA   |

|                                                                                              |                     | T <sub>A</sub> = 25 °C                               |     |      |      |      |

| High-Frequency Oscillator 1                                                                  | I <sub>HFOSC1</sub> | Operating at 72 MHz,                                 | _   | 1285 | 1340 | μA   |

|                                                                                              |                     | T <sub>A</sub> = 25 °C                               |     |      |      |      |

| _ow-Frequency Oscillator                                                                     | I <sub>LFOSC</sub>  | Operating at 80 kHz,                                 | _   | 3.7  | 6    | μA   |

|                                                                                              |                     | T <sub>A</sub> = 25 °C                               |     |      |      |      |

# Table 4.2. Power Consumption

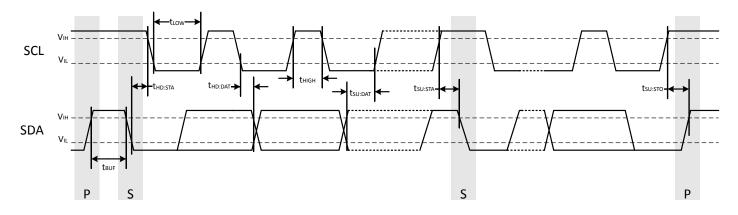

| Parameter                                       | Symbol              | Clocks               |

|-------------------------------------------------|---------------------|----------------------|

| SMBus Operating Frequency                       | f <sub>SMB</sub>    | f <sub>CSO</sub> / 3 |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    | 2 / f <sub>CSO</sub> |

| Hold Time After (Repeated) START Condition      | t <sub>HD:STA</sub> | 1 / f <sub>CSO</sub> |

| Repeated START Condition Setup Time             | t <sub>SU:STA</sub> | 2 / f <sub>CSO</sub> |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub> | 2 / f <sub>CSO</sub> |

| Clock Low Period                                | t <sub>LOW</sub>    | 1 / f <sub>CSO</sub> |

| Clock High Period                               | t <sub>HIGH</sub>   | 2 / f <sub>CSO</sub> |

## Table 4.17. SMBus Peripheral Timing Formulas (Master Mode)

Figure 4.1. SMBus Peripheral Timing Diagram (Master Mode)

### 4.2 Thermal Conditions

### Table 4.18. Thermal Conditions

| Parameter          | Symbol          | Test Condition  | Min | Тур | Max | Unit |  |  |

|--------------------|-----------------|-----------------|-----|-----|-----|------|--|--|

| Thermal Resistance | θ <sub>JA</sub> | QFN24 Packages  | _   | 30  | —   | °C/W |  |  |

|                    |                 | QFN32 Packages  | —   | 26  | _   | °C/W |  |  |

|                    |                 | QFP32 Packages  | —   | 80  | _   | °C/W |  |  |

|                    |                 | QSOP24 Packages | _   | 65  | —   | °C/W |  |  |

| Note:              |                 |                 |     |     |     |      |  |  |

1. Thermal resistance assumes a multi-layer PCB with any exposed pad soldered to a PCB pad.

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 29            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.2           |

|               |          |                   |                     | INT0.4                          | CMP0P.2          |

|               |          |                   |                     | INT1.4                          | CMP0N.2          |

|               |          |                   |                     | UART0_TX                        |                  |

|               |          |                   |                     | CLU0A.10                        |                  |

|               |          |                   |                     | CLU1A.8                         |                  |

|               |          |                   |                     | CLU3B.10                        |                  |

| 30            | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | XTAL2            |

|               |          |                   |                     | EXTCLK                          |                  |

|               |          |                   |                     | INT0.3                          |                  |

|               |          |                   |                     | INT1.3                          |                  |

|               |          |                   |                     | CLU0B.9                         |                  |

|               |          |                   |                     | CLU2B.9                         |                  |

|               |          |                   |                     | CLU3A.9                         |                  |

| 31            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | XTAL1            |

|               |          |                   |                     | INT0.2                          | ADC0.1           |

|               |          |                   |                     | INT1.2                          | CMP0P.1          |

|               |          |                   |                     | CLU0OUT                         | CMP0N.1          |

|               |          |                   |                     | CLU0A.9                         |                  |

|               |          |                   |                     | CLU2B.8                         |                  |

|               |          |                   |                     | CLU3A.8                         |                  |

| 32            | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                         | ADC0.0           |

|               |          |                   |                     | INT0.1                          | CMP0P.0          |

|               |          |                   |                     | INT1.1                          | CMP0N.0          |

|               |          |                   |                     | CLU0B.8                         | AGND             |

|               |          |                   |                     | CLU2A.9                         |                  |

|               |          |                   |                     | CLU3B.9                         |                  |

| Center        | GND      | Ground            |                     |                                 |                  |

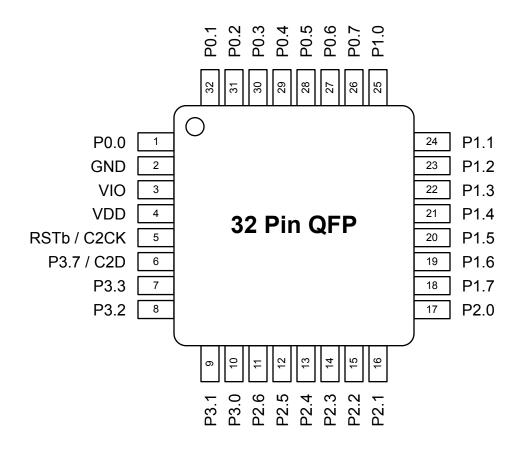

Figure 6.2. EFM8LB1x-QFP32 Pinout

| Table 6.2. | Pin Definitions | for EFM8LB1x-QFP32 |

|------------|-----------------|--------------------|

|------------|-----------------|--------------------|

| Pin<br>Number | Pin Name | Description            | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|------------------------|---------------------|---------------------------------|------------------|

| 1             | P0.0     | Multifunction I/O      | Yes                 | P0MAT.0                         | VREF             |

|               |          |                        |                     | INT0.0                          |                  |

|               |          |                        |                     | INT1.0                          |                  |

|               |          |                        |                     | CLU0A.8                         |                  |

|               |          |                        |                     | CLU2A.8                         |                  |

|               |          |                        |                     | CLU3B.8                         |                  |

| 2             | GND      | Ground                 |                     |                                 |                  |

| 3             | VIO      | I/O Supply Power Input |                     |                                 |                  |

| 4             | VDD      | Supply Power Input     |                     |                                 |                  |

| 5             | RSTb /   | Active-low Reset /     |                     |                                 |                  |

|               | C2CK     | C2 Debug Clock         |                     |                                 |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 18            | P1.7     | Multifunction I/O | Yes                 | P1MAT.7                         | ADC0.13          |

|               |          |                   |                     | CLU0B.15                        | CMP0P.9          |

|               |          |                   |                     | CLU1B.13                        | CMP0N.9          |

|               |          |                   |                     | CLU2A.13                        |                  |

| 19            | P1.6     | Multifunction I/O | Yes                 | P1MAT.6                         | ADC0.12          |

|               |          |                   |                     | CLU0A.15                        |                  |

|               |          |                   |                     | CLU1B.12                        |                  |

|               |          |                   |                     | CLU2A.12                        |                  |

| 20            | P1.5     | Multifunction I/O | Yes                 | P1MAT.5                         | ADC0.11          |

|               |          |                   |                     | CLU0B.14                        |                  |

|               |          |                   |                     | CLU1A.13                        |                  |

|               |          |                   |                     | CLU2B.13                        |                  |

| 21            | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                         | ADC0.10          |

|               |          |                   |                     | CLU0A.14                        |                  |

|               |          |                   |                     | CLU1A.12                        |                  |

|               |          |                   |                     | CLU2B.12                        |                  |

| 22            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                         | ADC0.9           |

|               |          |                   |                     | CLU0B.13                        |                  |

|               |          |                   |                     | CLU1B.11                        |                  |

|               |          |                   |                     | CLU2B.11                        |                  |

|               |          |                   |                     | CLU3A.13                        |                  |

| 23            | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                         | ADC0.8           |

|               |          |                   |                     | CLU0A.13                        | CMP0P.8          |

|               |          |                   |                     | CLU1A.11                        | CMP0N.8          |

|               |          |                   |                     | CLU2B.10                        |                  |

|               |          |                   |                     | CLU3A.12                        |                  |

| 24            | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                         | ADC0.7           |

|               |          |                   |                     | CLU0B.12                        | CMP0P.7          |

|               |          |                   |                     | CLU1B.10                        | CMP0N.7          |

|               |          |                   |                     | CLU2A.11                        |                  |

|               |          |                   |                     | CLU3B.13                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 25            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                         | ADC0.6           |

|               |          |                   |                     | CLU1OUT                         | CMP0P.6          |

|               |          |                   |                     | CLU0A.12                        | CMP0N.6          |

|               |          |                   |                     | CLU1A.10                        | CMP1P.1          |

|               |          |                   |                     | CLU2A.10                        | CMP1N.1          |

|               |          |                   |                     | CLU3B.12                        |                  |

| 26            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                         | ADC0.5           |

|               |          |                   |                     | INT0.7                          | CMP0P.5          |

|               |          |                   |                     | INT1.7                          | CMP0N.5          |

|               |          |                   |                     | CLU0B.11                        | CMP1P.0          |

|               |          |                   |                     | CLU1B.9                         | CMP1N.0          |

|               |          |                   |                     | CLU3A.11                        |                  |

| 27            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                         | ADC0.4           |

|               |          |                   |                     | CNVSTR                          | CMP0P.4          |

|               |          |                   |                     | INT0.6                          | CMP0N.4          |

|               |          |                   |                     | INT1.6                          |                  |

|               |          |                   |                     | CLU0A.11                        |                  |

|               |          |                   |                     | CLU1B.8                         |                  |

|               |          |                   |                     | CLU3A.10                        |                  |

| 28            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                         | ADC0.3           |

|               |          |                   |                     | INT0.5                          | CMP0P.3          |

|               |          |                   |                     | INT1.5                          | CMP0N.3          |

|               |          |                   |                     | UART0_RX                        |                  |

|               |          |                   |                     | CLU0B.10                        |                  |

|               |          |                   |                     | CLU1A.9                         |                  |

|               |          |                   |                     | CLU3B.11                        |                  |

| 29            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.2           |

|               |          |                   |                     | INT0.4                          | CMP0P.2          |

|               |          |                   |                     | INT1.4                          | CMP0N.2          |

|               |          |                   |                     | UART0_TX                        |                  |

|               |          |                   |                     | CLU0A.10                        |                  |

|               |          |                   |                     | CLU1A.8                         |                  |

|               |          |                   |                     | CLU3B.10                        |                  |

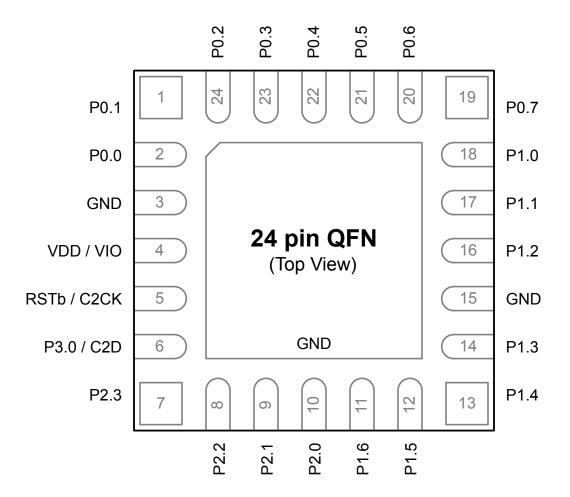

| Table 6.3. | Pin Definitions | for EFM8LB1x-QFN24 |

|------------|-----------------|--------------------|

|------------|-----------------|--------------------|

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 1             | P0.1     | Multifunction I/O | Yes                 | P0MAT.1                         | ADC0.0           |

|               |          |                   |                     | INT0.1                          | CMP0P.0          |

|               |          |                   |                     | INT1.1                          | CMP0N.0          |

|               |          |                   |                     | CLU0B.8                         | AGND             |

|               |          |                   |                     | CLU2A.9                         |                  |

|               |          |                   |                     | CLU3B.9                         |                  |

| Pin<br>Number | Pin Name  | Description         | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|-----------|---------------------|---------------------|---------------------------------|------------------|

| 2             | P0.0      | Multifunction I/O   | Yes                 | P0MAT.0                         | VREF             |

|               |           |                     |                     | INT0.0                          |                  |

|               |           |                     |                     | INT1.0                          |                  |

|               |           |                     |                     | CLU0A.8                         |                  |

|               |           |                     |                     | CLU2A.8                         |                  |

|               |           |                     |                     | CLU3B.8                         |                  |

| 3             | GND       | Ground              |                     |                                 |                  |

| 4             | VDD / VIO | Supply Power Input  |                     |                                 |                  |

| 5             | RSTb /    | Active-low Reset /  |                     |                                 |                  |

|               | C2CK      | C2 Debug Clock      |                     |                                 |                  |

| 6             | P3.0 /    | Multifunction I/O / |                     |                                 |                  |

|               | C2D       | C2 Debug Data       |                     |                                 |                  |

| 7             | P2.3      | Multifunction I/O   | Yes                 | P2MAT.3                         | DAC3             |

|               |           |                     |                     | CLU1B.15                        |                  |

|               |           |                     |                     | CLU2B.15                        |                  |

|               |           |                     |                     | CLU3A.15                        |                  |

| 8             | P2.2      | Multifunction I/O   | Yes                 | P2MAT.2                         | DAC2             |

|               |           |                     |                     | CLU1A.15                        |                  |

|               |           |                     |                     | CLU2B.14                        |                  |

|               |           |                     |                     | CLU3A.14                        |                  |

| 9             | P2.1      | Multifunction I/O   | Yes                 | P2MAT.1                         | DAC1             |

|               |           |                     |                     | CLU1B.14                        |                  |

|               |           |                     |                     | CLU2A.15                        |                  |

|               |           |                     |                     | CLU3B.15                        |                  |

| 10            | P2.0      | Multifunction I/O   | Yes                 | P2MAT.0                         | DAC0             |

|               |           |                     |                     | CLU1A.14                        |                  |

|               |           |                     |                     | CLU2A.14                        |                  |

|               |           |                     |                     | CLU3B.14                        |                  |

| 11            | P1.6      | Multifunction I/O   | Yes                 | P1MAT.6                         | ADC0.11          |

|               |           |                     |                     | CLU3OUT                         | CMP1P.5          |

|               |           |                     |                     | CLU0A.15                        | CMP1N.5          |

|               |           |                     |                     | CLU1B.12                        |                  |

|               |           |                     |                     | CLU2A.12                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 12            | P1.5     | Multifunction I/O | Yes                 | P1MAT.5                         | ADC0.10          |

|               |          |                   |                     | CLU2OUT                         | CMP1P.4          |

|               |          |                   |                     | CLU0B.14                        | CMP1N.4          |

|               |          |                   |                     | CLU1A.13                        |                  |

|               |          |                   |                     | CLU2B.13                        |                  |

| 13            | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                         | ADC0.9           |

|               |          |                   |                     | I2C0_SCL                        | CMP1P.3          |

|               |          |                   |                     | CLU0A.14                        | CMP1N.3          |

|               |          |                   |                     | CLU1A.12                        |                  |

|               |          |                   |                     | CLU2B.12                        |                  |

| 14            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                         | CMP1P.2          |

|               |          |                   |                     | I2C0_SDA                        | CMP1N.2          |

|               |          |                   |                     | CLU0B.13                        |                  |

|               |          |                   |                     | CLU1B.11                        |                  |

|               |          |                   |                     | CLU2B.11                        |                  |

|               |          |                   |                     | CLU3A.13                        |                  |

| 15            | GND      | Ground            |                     |                                 |                  |

| 16            | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                         | ADC0.8           |

|               |          |                   |                     | CLU0A.13                        |                  |

|               |          |                   |                     | CLU1A.11                        |                  |

|               |          |                   |                     | CLU2B.10                        |                  |

|               |          |                   |                     | CLU3A.12                        |                  |

| 17            | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                         | ADC0.7           |

|               |          |                   |                     | CLU0B.12                        |                  |

|               |          |                   |                     | CLU1B.10                        |                  |

|               |          |                   |                     | CLU2A.11                        |                  |

|               |          |                   |                     | CLU3B.13                        |                  |

| 18            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                         | ADC0.6           |

|               |          |                   |                     | CLU0A.12                        |                  |

|               |          |                   |                     | CLU1A.10                        |                  |

|               |          |                   |                     | CLU2A.10                        |                  |

|               |          |                   |                     | CLU3B.12                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 24            | P0.2     | Multifunction I/O | Yes                 | P0MAT.2                         | XTAL1            |

|               |          |                   |                     | INT0.2                          | ADC0.1           |

|               |          |                   |                     | INT1.2                          | CMP0P.1          |

|               |          |                   |                     | CLU0OUT                         | CMP0N.1          |

|               |          |                   |                     | CLU0A.9                         |                  |

|               |          |                   |                     | CLU2B.8                         |                  |

|               |          |                   |                     | CLU3A.8                         |                  |

| Center        | GND      | Ground            |                     |                                 |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 11            | P2.1     | Multifunction I/O | Yes                 | P2MAT.1                         | DAC1             |

|               |          |                   |                     | CLU1B.14                        |                  |

|               |          |                   |                     | CLU2A.15                        |                  |

|               |          |                   |                     | CLU3B.15                        |                  |

| 12            | P2.0     | Multifunction I/O | Yes                 | P2MAT.0                         | DAC0             |

|               |          |                   |                     | CLU1A.14                        |                  |

|               |          |                   |                     | CLU2A.14                        |                  |

|               |          |                   |                     | CLU3B.14                        |                  |

| 13            | P1.7     | Multifunction I/O | Yes                 | P1MAT.7                         | ADC0.12          |

|               |          |                   |                     | CLU0B.15                        | CMP1P.6          |

|               |          |                   |                     | CLU1B.13                        | CMP1N.6          |

|               |          |                   |                     | CLU2A.13                        |                  |

| 14            | P1.6     | Multifunction I/O | Yes                 | P1MAT.6                         | ADC0.11          |

|               |          |                   |                     | CLU3OUT                         | CMP1P.5          |

|               |          |                   |                     | CLU0A.15                        | CMP1N.5          |

|               |          |                   |                     | CLU1B.12                        |                  |

|               |          |                   |                     | CLU2A.12                        |                  |

| 15            | P1.5     | Multifunction I/O | Yes                 | P1MAT.5                         | ADC0.10          |

|               |          |                   |                     | CLU2OUT                         | CMP1P.4          |

|               |          |                   |                     | CLU0B.14                        | CMP1N.4          |

|               |          |                   |                     | CLU1A.13                        |                  |

|               |          |                   |                     | CLU2B.13                        |                  |

| 16            | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                         | ADC0.9           |

|               |          |                   |                     | I2C0_SCL                        | CMP1P.3          |

|               |          |                   |                     | CLU0A.14                        | CMP1N.3          |

|               |          |                   |                     | CLU1A.12                        |                  |

|               |          |                   |                     | CLU2B.12                        |                  |

| 17            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                         | CMP1P.2          |

|               |          |                   |                     | I2C0_SDA                        | CMP1N.2          |

|               |          |                   |                     | CLU0B.13                        |                  |

|               |          |                   |                     | CLU1B.11                        |                  |

|               |          |                   |                     | CLU2B.11                        |                  |

|               |          |                   |                     | CLU3A.13                        |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 24            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                         | ADC0.2           |

|               |          |                   |                     | INT0.4                          | CMP0P.2          |

|               |          |                   |                     | INT1.4                          | CMP0N.2          |

|               |          |                   |                     | UART0_TX                        |                  |

|               |          |                   |                     | CLU0A.10                        |                  |

|               |          |                   |                     | CLU1A.8                         |                  |

|               |          |                   |                     | CLU3B.10                        |                  |

| Dimension                                             | Min                                      | Тур      | Мах           |

|-------------------------------------------------------|------------------------------------------|----------|---------------|

| Note:                                                 |                                          |          |               |

| 1. All dimensions shown                               | are in millimeters (mm) unless otherwise | e noted. |               |

| 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994. |                                          |          |               |

| 3. This drawing conforms                              | to JEDEC Solid State Outline MO-220.     |          |               |

| u u u u u u u u u u u u u u u u u u u                 | flow profile is per the JEDEC/IPC J-ST   |          | dv Components |

The package marking consists of:

- PPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

- # The device revision (A, B, etc.).

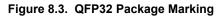

# 9. QFN24 Package Specifications

### 9.1 QFN24 Package Dimensions

Figure 9.1. QFN24 Package Drawing

| Table 9.1. | QFN24 Package Dimensions |

|------------|--------------------------|

|------------|--------------------------|

| Dimension | Min       | Тур      | Мах      |  |  |

|-----------|-----------|----------|----------|--|--|

| A         | 0.8       | 0.85     | 0.9      |  |  |

| A1        | 0.00      | —        | 0.05     |  |  |

| A2        | —         | 0.65     | —        |  |  |

| A3        | 0.203 REF |          |          |  |  |

| b         | 0.15      | 0.2      | 0.25     |  |  |

| b1        | 0.25      | 0.3      | 0.35     |  |  |

| D         | 3.00 BSC  |          |          |  |  |

| E         |           | 3.00 BSC | 3.00 BSC |  |  |

| Dimension | Min  | Тур      | Мах  |

|-----------|------|----------|------|

| е         |      | 0.40 BSC |      |

| e1        |      | 0.45 BSC |      |

| J         | 1.60 | 1.70     | 1.80 |

| К         | 1.60 | 1.70     | 1.80 |

| L         | 0.35 | 0.40     | 0.45 |

| L1        | 0.25 | 0.30     | 0.35 |

| ааа       | _    | 0.10     | —    |

| bbb       | _    | 0.10     | _    |

| ссс       | _    | 0.08     | _    |

| ddd       | _    | 0.1      | _    |

| eee       | _    | 0.1      | —    |

## Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC Solid State Outline MO-248 but includes custom features which are toleranced per supplier designation.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

| Dimension                                                                        | Min                                            | Мах                                            |

|----------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|

| Note:                                                                            |                                                |                                                |

| 1. All dimensions shown are in millimeters (n                                    | nm) unless otherwise noted.                    |                                                |

| 2. Dimensioning and Tolerancing is per the A                                     | ANSI Y14.5M-1994 specification.                |                                                |

| 3. This Land Pattern Design is based on the                                      | IPC-SM-782 guidelines.                         |                                                |

| 4. All metal pads are to be non-solder mask minimum, all the way around the pad. | defined (NSMD). Clearance between the solo     | der mask and the metal pad is to be 60 $\mu m$ |

| 5. A stainless steel, laser-cut and electro-pol                                  | ished stencil with trapezoidal walls should be | used to assure good solder paste release       |

| 6. The stencil thickness should be 0.125 mm                                      | (5 mils).                                      |                                                |

| 7. The ratio of stencil aperture to land pad si                                  | ze should be 1:1 for all perimeter pads.       |                                                |

| 8. A 2 x 1 array of 0.7 mm x 1.6 mm opening                                      | s on a 0.9 mm pitch should be used for the c   | enter pad.                                     |

| 9. A No-Clean, Type-3 solder paste is recom                                      | mended.                                        |                                                |

10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 9.3 QFN24 Package Marking

Figure 9.3. QFN24 Package Marking

The package marking consists of:

- PPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

- # The device revision (A, B, etc.).