Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | CIP-51 8051                                                               |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 72MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SMBus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 29                                                                        |

| Program Memory Size        | 32KB (32K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 2.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                               |

| Data Converters            | A/D 20x14b; D/A 4x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm8lb12f32es0-b-qfn32r |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

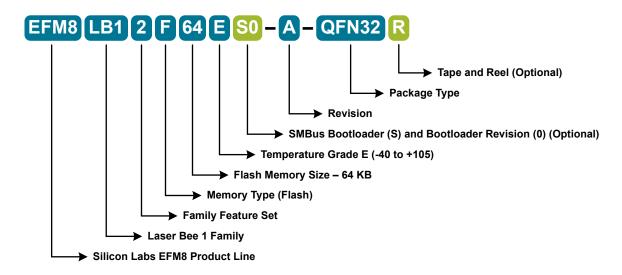

### 2. Ordering Information

Figure 2.1. EFM8LB1 Part Numbering

All EFM8LB1 family members have the following features:

- CIP-51 Core running up to 72 MHz

- Three Internal Oscillators (72 MHz, 24.5 MHz and 80 kHz)

- SMBus

- · I2C Slave

- SPI

- 2 UARTs

- 6-Channel Programmable Counter Array (PWM, Clock Generation, Capture/Compare)

- · Six 16-bit Timers

- · Four Configurable Logic Units

- 14-bit Analog-to-Digital Converter with integrated multiplexer, voltage reference, temperature sensor, channel sequencer, and direct-to-XRAM data transfer

- · Two Analog Comparators

- · 16-bit CRC Unit

- · AEC-Q100 qualified (pending)

In addition to these features, each part number in the EFM8LB1 family has a set of features that vary across the product line. The product selection guide shows the features available on each family member.

Table 2.1. Product Selection Guide

| Ordering Part Number | Flash Memory (kB) | RAM (Bytes) | Digital Port I/Os (Total) | ADC0 Channels | Voltage DACs | Comparator 0 Inputs | Comparator 1 Inputs | Bootloader Type | Pb-free (RoHS Compliant) | Temperature Range | Package |

|----------------------|-------------------|-------------|---------------------------|---------------|--------------|---------------------|---------------------|-----------------|--------------------------|-------------------|---------|

| EFM8LB12F64E-B-QFN32 | 64                | 4352        | 29                        | 20            | 4            | 10                  | 9                   | UART            | Yes                      | -40 to +105 °C    | QFN32   |

| EFM8LB12F64E-B-QFP32 | 64                | 4352        | 28                        | 20            | 4            | 10                  | 9                   | UART            | Yes                      | -40 to +105 °C    | QFP32   |

| EFM8LB12F64E-B-QFN24 | 64                | 4352        | 20                        | 12            | 4            | 6                   | 6                   | UART            | Yes                      | -40 to +105 °C    | QFN24   |

#### I2C Slave (I2CSLAVE0)

The I2C Slave interface is a 2-wire, bidirectional serial bus that is compatible with the I2C Bus Specification 3.0. It is capable of transferring in high-speed mode (HS-mode) at speeds of up to 3.4 Mbps. Firmware can write to the I2C interface, and the I2C interface can autonomously control the serial transfer of data. The interface also supports clock stretching for cases where the core may be temporarily prohibited from transmitting a byte or processing a received byte during an I2C transaction. This module operates only as an I2C slave device.

The I2C module includes the following features:

- Standard (up to 100 kbps), Fast (400 kbps), Fast Plus (1 Mbps), and High-speed (3.4 Mbps) transfer speeds

- · Support for slave mode only

- · Clock low extending (clock stretching) to interface with faster masters

- · Hardware support for 7-bit slave address recognition

- Transmit and receive FIFOs (two byte) to help increase throughput in faster applications

- Hardware support for multiple slave addresses with the option to save the matching address in the receive FIFO

### 16-bit CRC (CRC0)

The cyclic redundancy check (CRC) module performs a CRC using a 16-bit polynomial. CRC0 accepts a stream of 8-bit data and posts the 16-bit result to an internal register. In addition to using the CRC block for data manipulation, hardware can automatically CRC the flash contents of the device.

The CRC module is designed to provide hardware calculations for flash memory verification and communications protocols. The CRC module supports the standard CCITT-16 16-bit polynomial (0x1021), and includes the following features:

- Support for CCITT-16 polynomial

- · Byte-level bit reversal

- · Automatic CRC of flash contents on one or more 256-byte blocks

- Initial seed selection of 0x0000 or 0xFFFF

### Configurable Logic Units (CLU0, CLU1, CLU2, and CLU3)

The Configurable Logic block consists of multiple Configurable Logic Units (CLUs). CLUs are flexible logic functions which may be used for a variety of digital functions, such as replacing system glue logic, aiding in the generation of special waveforms, or synchronizing system event triggers.

- · Four configurable logic units (CLUs), with direct-pin and internal logic connections

- Each unit supports 256 different combinatorial logic functions (AND, OR, XOR, muxing, etc.) and includes a clocked flip-flop for synchronous operations

- · Units may be operated synchronously or asynchronously

- · May be cascaded together to perform more complicated logic functions

- Can operate in conjunction with serial peripherals such as UART and SPI or timing peripherals such as timers and PCA channels

- · Can be used to synchronize and trigger multiple on-chip resources (ADC, DAC, Timers, etc.)

- Asynchronous output may be used to wake from low-power states

#### 3.8 Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- · The core halts program execution.

- Module registers are initialized to their defined reset values unless the bits reset only with a power-on reset.

- · External port pins are forced to a known state.

- · Interrupts and timers are disabled.

All registers are reset to the predefined values noted in the register descriptions unless the bits only reset with a power-on reset. The contents of RAM are unaffected during a reset; any previously stored data is preserved as long as power is not lost. By default, the Port I/O latches are reset to 1 in open-drain mode, with weak pullups enabled during and after the reset. Optionally, firmware may configure the port I/O, DAC outputs, and precision reference to maintain state through system resets other than power-on resets. For Supply Monitor and power-on resets, the RSTb pin is driven low until the device exits the reset state. On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to an internal oscillator. The Watchdog Timer is enabled, and program execution begins at location 0x0000.

Reset sources on the device include the following:

- · Power-on reset

- · External reset pin

- · Comparator reset

- · Software-triggered reset

- · Supply monitor reset (monitors VDD supply)

- · Watchdog timer reset

- · Missing clock detector reset

- · Flash error reset

#### 3.9 Debugging

The EFM8LB1 devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

### 4.1.3 Reset and Supply Monitor

Table 4.3. Reset and Supply Monitor

| Parameter                                                         | Symbol            | Test Condition                                          | Min  | Тур   | Max  | Unit |

|-------------------------------------------------------------------|-------------------|---------------------------------------------------------|------|-------|------|------|

| VDD Supply Monitor Threshold                                      | $V_{VDDM}$        |                                                         | 1.95 | 2.05  | 2.15 | V    |

| Power-On Reset (POR) Threshold                                    | V <sub>POR</sub>  | Rising Voltage on VDD                                   | _    | 1.4   | _    | V    |

|                                                                   |                   | Falling Voltage on VDD                                  | 0.75 | _     | 1.36 | V    |

| VDD Ramp Time                                                     | t <sub>RMP</sub>  | Time to V <sub>DD</sub> > 2.2 V                         | 10   | _     | _    | μs   |

| Reset Delay from POR                                              | t <sub>POR</sub>  | Relative to V <sub>DD</sub> > V <sub>POR</sub>          | 3    | 10    | 31   | ms   |

| Reset Delay from non-POR source                                   | t <sub>RST</sub>  | Time between release of reset source and code execution | _    | 50    | _    | μs   |

| RST Low Time to Generate Reset                                    | t <sub>RSTL</sub> |                                                         | 15   | _     | _    | μs   |

| Missing Clock Detector Response Time (final rising edge to reset) | t <sub>MCD</sub>  | F <sub>SYSCLK</sub> >1 MHz                              | _    | 0.625 | 1.2  | ms   |

| Missing Clock Detector Trigger Frequency                          | F <sub>MCD</sub>  |                                                         | _    | 7.5   | 13.5 | kHz  |

| VDD Supply Monitor Turn-On Time                                   | t <sub>MON</sub>  |                                                         | _    | 2     | _    | μs   |

### 4.1.4 Flash Memory

Table 4.4. Flash Memory

| Parameter                                               | Symbol             | Test Condition                 | Min | Тур  | Max | Units  |

|---------------------------------------------------------|--------------------|--------------------------------|-----|------|-----|--------|

| Write Time <sup>1</sup> , <sup>2</sup>                  | t <sub>WRITE</sub> | One Byte,                      | 19  | 20   | 21  | μs     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| Erase Time <sup>1</sup> , <sup>2</sup>                  | t <sub>ERASE</sub> | One Page,                      | 5.2 | 5.35 | 5.5 | ms     |

|                                                         |                    | F <sub>SYSCLK</sub> = 24.5 MHz |     |      |     |        |

| V <sub>DD</sub> Voltage During Programming <sup>3</sup> | V <sub>PROG</sub>  |                                | 2.2 | _    | 3.6 | V      |

| Endurance (Write/Erase Cycles)                          | N <sub>WE</sub>    |                                | 20k | 100k | _   | Cycles |

| CRC Calculation Time                                    | t <sub>CRC</sub>   | One 256-Byte Block             | _   | 5.5  | _   | μs     |

|                                                         |                    | SYSCLK = 48 MHz                |     |      |     |        |

- 1. Does not include sequencing time before and after the write/erase operation, which may be multiple SYSCLK cycles.

- 2. The internal High-Frequency Oscillator 0 has a programmable output frequency, which is factory programmed to 24.5 MHz. If user firmware adjusts the oscillator speed, it must be between 22 and 25 MHz during any flash write or erase operation. It is recommended to write the HFO0CAL register back to its reset value when writing or erasing flash.

- 3. Flash can be safely programmed at any voltage above the supply monitor threshold (V<sub>VDDM</sub>).

- 4. Data Retention Information is published in the Quarterly Quality and Reliability Report.

# 4.1.5 Power Management Timing

**Table 4.5. Power Management Timing**

| Parameter                 | Symbol               | Test Condition  | Min | Тур | Max | Units   |

|---------------------------|----------------------|-----------------|-----|-----|-----|---------|

| Idle Mode Wake-up Time    | t <sub>IDLEWK</sub>  |                 | 2   | _   | 3   | SYSCLKs |

| Suspend Mode Wake-up Time | t <sub>SUS-</sub>    | SYSCLK = HFOSC0 | _   | 170 | _   | ns      |

|                           | PENDWK               | CLKDIV = 0x00   |     |     |     |         |

| Snooze Mode Wake-up Time  | t <sub>SLEEPWK</sub> | SYSCLK = HFOSC0 | _   | 12  | _   | μs      |

|                           |                      | CLKDIV = 0x00   |     |     |     |         |

# 4.1.6 Internal Oscillators

**Table 4.6. Internal Oscillators**

| Parameter                   | Symbol               | Test Condition                    | Min  | Тур  | Max  | Unit   |

|-----------------------------|----------------------|-----------------------------------|------|------|------|--------|

| High Frequency Oscillator 0 | (24.5 MHz)           |                                   |      |      |      |        |

| Oscillator Frequency        | f <sub>HFOSC0</sub>  | Full Temperature and Supply Range | 24   | 24.5 | 25   | MHz    |

| Power Supply Sensitivity    | PSS <sub>HFOS</sub>  | T <sub>A</sub> = 25 °C            | _    | 0.5  | _    | %/V    |

| Temperature Sensitivity     | TS <sub>HFOSC0</sub> | V <sub>DD</sub> = 3.0 V           | _    | 40   | _    | ppm/°C |

| High Frequency Oscillator 1 | (72 MHz)             |                                   |      |      |      |        |

| Oscillator Frequency        | f <sub>HFOSC1</sub>  | Full Temperature and Supply Range | 70.5 | 72   | 73.5 | MHz    |

| Power Supply Sensitivity    | PSS <sub>HFOS</sub>  | T <sub>A</sub> = 25 °C            | _    | 300  | _    | ppm/V  |

| Temperature Sensitivity     | TS <sub>HFOSC1</sub> | V <sub>DD</sub> = 3.0 V           | _    | 103  | _    | ppm/°C |

| Low Frequency Oscillator (8 | 0 kHz)               |                                   |      | 1    | 1    | 1      |

| Oscillator Frequency        | f <sub>LFOSC</sub>   | Full Temperature and Supply Range | 75   | 80   | 85   | kHz    |

| Power Supply Sensitivity    | PSS <sub>LFOSC</sub> | T <sub>A</sub> = 25 °C            | _    | 0.05 | _    | %/V    |

| Temperature Sensitivity     | TS <sub>LFOSC</sub>  | V <sub>DD</sub> = 3.0 V           | _    | 65   | _    | ppm/°C |

### 4.1.16 SMBus

Table 4.16. SMBus Peripheral Timing Performance (Master Mode)

| Parameter                                       | Symbol               | Test Condition | Min             | Тур | Max              | Unit |

|-------------------------------------------------|----------------------|----------------|-----------------|-----|------------------|------|

| Standard Mode (100 kHz Class)                   |                      |                |                 |     |                  |      |

| I2C Operating Frequency                         | f <sub>I2C</sub>     |                | 0               | _   | 70 <sup>2</sup>  | kHz  |

| SMBus Operating Frequency                       | f <sub>SMB</sub>     |                | 40 <sup>1</sup> | _   | 70 <sup>2</sup>  | kHz  |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>     |                | 9.4             | _   | _                | μs   |

| Hold Time After (Repeated)<br>START Condition   | t <sub>HD:STA</sub>  |                | 4.7             | _   | _                | μs   |

| Repeated START Condition Setup Time             | t <sub>SU:STA</sub>  |                | 9.4             | _   | _                | μs   |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub>  |                | 9.4             | _   | _                | μs   |

| Data Hold Time                                  | t <sub>HD:DAT</sub>  |                | 0               | _   | _                | μs   |

| Data Setup Time                                 | t <sub>SU:DAT</sub>  |                | 4.7             | _   | _                | μs   |

| Detect Clock Low Timeout                        | t <sub>TIMEOUT</sub> |                | 25              | _   | _                | ms   |

| Clock Low Period                                | t <sub>LOW</sub>     |                | 4.7             | _   | _                | μs   |

| Clock High Period                               | t <sub>HIGH</sub>    |                | 9.4             | _   | 50 <sup>3</sup>  | μs   |

| Fast Mode (400 kHz Class)                       |                      |                |                 |     | ı                |      |

| I2C Operating Frequency                         | f <sub>I2C</sub>     |                | 0               | _   | 256 <sup>2</sup> | kHz  |

| SMBus Operating Frequency                       | f <sub>SMB</sub>     |                | 40 <sup>1</sup> | _   | 256 <sup>2</sup> | kHz  |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>     |                | 2.6             | _   | _                | μs   |

| Hold Time After (Repeated)<br>START Condition   | t <sub>HD:STA</sub>  |                | 1.3             | _   | _                | μs   |

| Repeated START Condition Setup Time             | t <sub>SU:STA</sub>  |                | 2.6             | _   | _                | μs   |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub>  |                | 2.6             | _   | _                | μs   |

| Data Hold Time                                  | t <sub>HD:DAT</sub>  |                | 0               | _   | _                | μs   |

| Data Setup Time                                 | t <sub>SU:DAT</sub>  |                | 1.3             | _   | _                | μs   |

| Detect Clock Low Timeout                        | t <sub>TIMEOUT</sub> |                | 25              | _   | _                | ms   |

| Clock Low Period                                | t <sub>LOW</sub>     |                | 1.3             | _   | _                | μs   |

| Clock High Period                               | t <sub>HIGH</sub>    |                | 2.6             | _   | 50 <sup>3</sup>  | μs   |

#### Note

- 1. The minimum SMBus frequency is limited by the maximum Clock High Period requirement of the SMBus specification.

- 2. The maximum I2C and SMBus frequencies are limited by the minimum Clock Low Period requirements of their respective specifications.

- 3. SMBus has a maximum requirement of 50  $\mu$ s for Clock High Period. Operating frequencies lower than 40 kHz will be longer than 50  $\mu$ s. I2C can support periods longer than 50  $\mu$ s.

Table 6.1. Pin Definitions for EFM8LB1x-QFN32

| Pin<br>Number | Pin Name | Description            | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|------------------------|---------------------|------------------------------|------------------|

| 1             | P0.0     | Multifunction I/O      | Yes                 | P0MAT.0                      | VREF             |

|               |          |                        |                     | INT0.0                       |                  |

|               |          |                        |                     | INT1.0                       |                  |

|               |          |                        |                     | CLU0A.8                      |                  |

|               |          |                        |                     | CLU2A.8                      |                  |

|               |          |                        |                     | CLU3B.8                      |                  |

| 2             | VIO      | I/O Supply Power Input |                     |                              |                  |

| 3             | VDD      | Supply Power Input     |                     |                              |                  |

| 4             | RSTb /   | Active-low Reset /     |                     |                              |                  |

|               | C2CK     | C2 Debug Clock         |                     |                              |                  |

| 5             | P3.7 /   | Multifunction I/O /    |                     |                              |                  |

|               | C2D      | C2 Debug Data          |                     |                              |                  |

| 6             | P3.4     | Multifunction I/O      |                     |                              |                  |

| 7             | P3.3     | Multifunction I/O      |                     |                              | DAC3             |

| 8             | P3.2     | Multifunction I/O      |                     |                              | DAC2             |

| 9             | P3.1     | Multifunction I/O      |                     |                              | DAC1             |

| 10            | P3.0     | Multifunction I/O      |                     |                              | DAC0             |

| 11            | P2.6     | Multifunction I/O      |                     |                              | ADC0.19          |

|               |          |                        |                     |                              | CMP1P.8          |

|               |          |                        |                     |                              | CMP1N.8          |

| 12            | P2.5     | Multifunction I/O      |                     | CLU3OUT                      | ADC0.18          |

|               |          |                        |                     |                              | CMP1P.7          |

|               |          |                        |                     |                              | CMP1N.7          |

| 13            | P2.4     | Multifunction I/O      |                     |                              | ADC0.17          |

|               |          |                        |                     |                              | CMP1P.6          |

|               |          |                        |                     |                              | CMP1N.6          |

| 14            | P2.3     | Multifunction I/O      | Yes                 | P2MAT.3                      | ADC0.16          |

|               |          |                        |                     | CLU1B.15                     | CMP1P.5          |

|               |          |                        |                     | CLU2B.15                     | CMP1N.5          |

|               |          |                        |                     | CLU3A.15                     |                  |

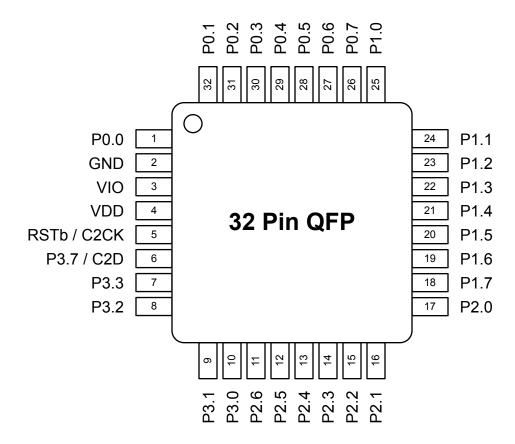

Figure 6.2. EFM8LB1x-QFP32 Pinout

Table 6.2. Pin Definitions for EFM8LB1x-QFP32

| Pin<br>Number | Pin Name | Description            | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|------------------------|---------------------|------------------------------|------------------|

| 1             | P0.0     | Multifunction I/O      | Yes                 | P0MAT.0                      | VREF             |

|               |          |                        |                     | INT0.0                       |                  |

|               |          |                        |                     | INT1.0                       |                  |

|               |          |                        |                     | CLU0A.8                      |                  |

|               |          |                        |                     | CLU2A.8                      |                  |

|               |          |                        |                     | CLU3B.8                      |                  |

| 2             | GND      | Ground                 |                     |                              |                  |

| 3             | VIO      | I/O Supply Power Input |                     |                              |                  |

| 4             | VDD      | Supply Power Input     |                     |                              |                  |

| 5             | RSTb /   | Active-low Reset /     |                     |                              |                  |

|               | C2CK     | C2 Debug Clock         |                     |                              |                  |

| Pin    | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|--------|----------|-------------------|---------------------|------------------------------|------------------|

| Number |          |                   |                     |                              |                  |

| 18     | P1.7     | Multifunction I/O | Yes                 | P1MAT.7                      | ADC0.13          |

|        |          |                   |                     | CLU0B.15                     | CMP0P.9          |

|        |          |                   |                     | CLU1B.13                     | CMP0N.9          |

|        |          |                   |                     | CLU2A.13                     |                  |

| 19     | P1.6     | Multifunction I/O | Yes                 | P1MAT.6                      | ADC0.12          |

|        |          |                   |                     | CLU0A.15                     |                  |

|        |          |                   |                     | CLU1B.12                     |                  |

|        |          |                   |                     | CLU2A.12                     |                  |

| 20     | P1.5     | Multifunction I/O | Yes                 | P1MAT.5                      | ADC0.11          |

|        |          |                   |                     | CLU0B.14                     |                  |

|        |          |                   |                     | CLU1A.13                     |                  |

|        |          |                   |                     | CLU2B.13                     |                  |

| 21     | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                      | ADC0.10          |

|        |          |                   |                     | CLU0A.14                     |                  |

|        |          |                   |                     | CLU1A.12                     |                  |

|        |          |                   |                     | CLU2B.12                     |                  |

| 22     | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                      | ADC0.9           |

|        |          |                   |                     | CLU0B.13                     |                  |

|        |          |                   |                     | CLU1B.11                     |                  |

|        |          |                   |                     | CLU2B.11                     |                  |

|        |          |                   |                     | CLU3A.13                     |                  |

| 23     | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                      | ADC0.8           |

|        |          |                   |                     | CLU0A.13                     | CMP0P.8          |

|        |          |                   |                     | CLU1A.11                     | CMP0N.8          |

|        |          |                   |                     | CLU2B.10                     |                  |

|        |          |                   |                     | CLU3A.12                     |                  |

| 24     | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                      | ADC0.7           |

|        |          |                   |                     | CLU0B.12                     | CMP0P.7          |

|        |          |                   |                     | CLU1B.10                     | CMP0N.7          |

|        |          |                   |                     | CLU2A.11                     |                  |

|        |          |                   |                     | CLU3B.13                     |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 25            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                      | ADC0.6           |

|               |          |                   |                     | CLU1OUT                      | CMP0P.6          |

|               |          |                   |                     | CLU0A.12                     | CMP0N.6          |

|               |          |                   |                     | CLU1A.10                     | CMP1P.1          |

|               |          |                   |                     | CLU2A.10                     | CMP1N.1          |

|               |          |                   |                     | CLU3B.12                     |                  |

| 26            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                      | ADC0.5           |

|               |          |                   |                     | INT0.7                       | CMP0P.5          |

|               |          |                   |                     | INT1.7                       | CMP0N.5          |

|               |          |                   |                     | CLU0B.11                     | CMP1P.0          |

|               |          |                   |                     | CLU1B.9                      | CMP1N.0          |

|               |          |                   |                     | CLU3A.11                     |                  |

| 27            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                      | ADC0.4           |

|               |          |                   |                     | CNVSTR                       | CMP0P.4          |

|               |          |                   |                     | INT0.6                       | CMP0N.4          |

|               |          |                   |                     | INT1.6                       |                  |

|               |          |                   |                     | CLU0A.11                     |                  |

|               |          |                   |                     | CLU1B.8                      |                  |

|               |          |                   |                     | CLU3A.10                     |                  |

| 28            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                      | ADC0.3           |

|               |          |                   |                     | INT0.5                       | CMP0P.3          |

|               |          |                   |                     | INT1.5                       | CMP0N.3          |

|               |          |                   |                     | UART0_RX                     |                  |

|               |          |                   |                     | CLU0B.10                     |                  |

|               |          |                   |                     | CLU1A.9                      |                  |

|               |          |                   |                     | CLU3B.11                     |                  |

| 29            | P0.4     | Multifunction I/O | Yes                 | P0MAT.4                      | ADC0.2           |

|               |          |                   |                     | INT0.4                       | CMP0P.2          |

|               |          |                   |                     | INT1.4                       | CMP0N.2          |

|               |          |                   |                     | UART0_TX                     |                  |

|               |          |                   |                     | CLU0A.10                     |                  |

|               |          |                   |                     | CLU1A.8                      |                  |

|               |          |                   |                     | CLU3B.10                     |                  |

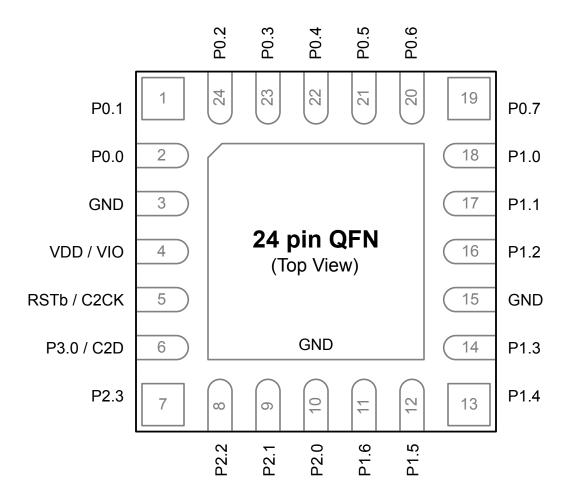

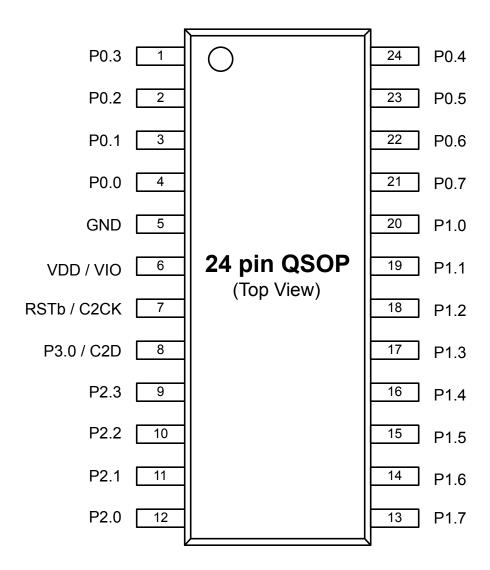

### 6.3 EFM8LB1x-QFN24 Pin Definitions

Figure 6.3. EFM8LB1x-QFN24 Pinout

Table 6.3. Pin Definitions for EFM8LB1x-QFN24

| Pin    | Pin Name | Description       | Crossbar Capability | Additional Digital | Analog Functions |

|--------|----------|-------------------|---------------------|--------------------|------------------|

| Number |          |                   |                     | Functions          |                  |

| 1      | P0.1     | Multifunction I/O | Yes                 | P0MAT.1            | ADC0.0           |

|        |          |                   |                     | INT0.1             | CMP0P.0          |

|        |          |                   |                     | INT1.1             | CMP0N.0          |

|        |          |                   |                     | CLU0B.8            | AGND             |

|        |          |                   |                     | CLU2A.9            |                  |

|        |          |                   |                     | CLU3B.9            |                  |

| Pin<br>Number | Pin Name  | Description         | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|-----------|---------------------|---------------------|------------------------------|------------------|

| 2             | P0.0      | Multifunction I/O   | Yes                 | P0MAT.0                      | VREF             |

|               |           |                     |                     | INT0.0                       |                  |

|               |           |                     |                     | INT1.0                       |                  |

|               |           |                     |                     | CLU0A.8                      |                  |

|               |           |                     |                     | CLU2A.8                      |                  |

|               |           |                     |                     | CLU3B.8                      |                  |

| 3             | GND       | Ground              |                     |                              |                  |

| 4             | VDD / VIO | Supply Power Input  |                     |                              |                  |

| 5             | RSTb /    | Active-low Reset /  |                     |                              |                  |

|               | C2CK      | C2 Debug Clock      |                     |                              |                  |

| 6             | P3.0 /    | Multifunction I/O / |                     |                              |                  |

|               | C2D       | C2 Debug Data       |                     |                              |                  |

| 7             | P2.3      | Multifunction I/O   | Yes                 | P2MAT.3                      | DAC3             |

|               |           |                     |                     | CLU1B.15                     |                  |

|               |           |                     |                     | CLU2B.15                     |                  |

|               |           |                     |                     | CLU3A.15                     |                  |

| 8             | P2.2      | Multifunction I/O   | Yes                 | P2MAT.2                      | DAC2             |

|               |           |                     |                     | CLU1A.15                     |                  |

|               |           |                     |                     | CLU2B.14                     |                  |

|               |           |                     |                     | CLU3A.14                     |                  |

| 9             | P2.1      | Multifunction I/O   | Yes                 | P2MAT.1                      | DAC1             |

|               |           |                     |                     | CLU1B.14                     |                  |

|               |           |                     |                     | CLU2A.15                     |                  |

|               |           |                     |                     | CLU3B.15                     |                  |

| 10            | P2.0      | Multifunction I/O   | Yes                 | P2MAT.0                      | DAC0             |

|               |           |                     |                     | CLU1A.14                     |                  |

|               |           |                     |                     | CLU2A.14                     |                  |

|               |           |                     |                     | CLU3B.14                     |                  |

| 11            | P1.6      | Multifunction I/O   | Yes                 | P1MAT.6                      | ADC0.11          |

|               |           |                     |                     | CLU3OUT                      | CMP1P.5          |

|               |           |                     |                     | CLU0A.15                     | CMP1N.5          |

|               |           |                     |                     | CLU1B.12                     |                  |

|               |           |                     |                     | CLU2A.12                     |                  |

### 6.4 EFM8LB1x-QSOP24 Pin Definitions

Figure 6.4. EFM8LB1x-QSOP24 Pinout

Table 6.4. Pin Definitions for EFM8LB1x-QSOP24

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital<br>Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|---------------------------------|------------------|

| 1             | P0.3     | Multifunction I/O | Yes                 | P0MAT.3                         | XTAL2            |

|               |          |                   |                     | EXTCLK                          |                  |

|               |          |                   |                     | INT0.3                          |                  |

|               |          |                   |                     | INT1.3                          |                  |

|               |          |                   |                     | CLU0B.9                         |                  |

|               |          |                   |                     | CLU2B.9                         |                  |

|               |          |                   |                     | CLU3A.9                         |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 11            | P2.1     | Multifunction I/O | Yes                 | P2MAT.1                      | DAC1             |

|               |          |                   |                     | CLU1B.14                     |                  |

|               |          |                   |                     | CLU2A.15                     |                  |

|               |          |                   |                     | CLU3B.15                     |                  |

| 12            | P2.0     | Multifunction I/O | Yes                 | P2MAT.0                      | DAC0             |

|               |          |                   |                     | CLU1A.14                     |                  |

|               |          |                   |                     | CLU2A.14                     |                  |

|               |          |                   |                     | CLU3B.14                     |                  |

| 13            | P1.7     | Multifunction I/O | Yes                 | P1MAT.7                      | ADC0.12          |

|               |          |                   |                     | CLU0B.15                     | CMP1P.6          |

|               |          |                   |                     | CLU1B.13                     | CMP1N.6          |

|               |          |                   |                     | CLU2A.13                     |                  |

| 14            | P1.6     | Multifunction I/O | Yes                 | P1MAT.6                      | ADC0.11          |

|               |          |                   |                     | CLU3OUT                      | CMP1P.5          |

|               |          |                   |                     | CLU0A.15                     | CMP1N.5          |

|               |          |                   |                     | CLU1B.12                     |                  |

|               |          |                   |                     | CLU2A.12                     |                  |

| 15            | P1.5     | Multifunction I/O | Yes                 | P1MAT.5                      | ADC0.10          |

|               |          |                   |                     | CLU2OUT                      | CMP1P.4          |

|               |          |                   |                     | CLU0B.14                     | CMP1N.4          |

|               |          |                   |                     | CLU1A.13                     |                  |

|               |          |                   |                     | CLU2B.13                     |                  |

| 16            | P1.4     | Multifunction I/O | Yes                 | P1MAT.4                      | ADC0.9           |

|               |          |                   |                     | 12C0_SCL                     | CMP1P.3          |

|               |          |                   |                     | CLU0A.14                     | CMP1N.3          |

|               |          |                   |                     | CLU1A.12                     |                  |

|               |          |                   |                     | CLU2B.12                     |                  |

| 17            | P1.3     | Multifunction I/O | Yes                 | P1MAT.3                      | CMP1P.2          |

|               |          |                   |                     | I2C0_SDA                     | CMP1N.2          |

|               |          |                   |                     | CLU0B.13                     |                  |

|               |          |                   |                     | CLU1B.11                     |                  |

|               |          |                   |                     | CLU2B.11                     |                  |

|               |          |                   |                     | CLU3A.13                     |                  |

| Pin<br>Number | Pin Name | Description       | Crossbar Capability | Additional Digital Functions | Analog Functions |

|---------------|----------|-------------------|---------------------|------------------------------|------------------|

| 18            | P1.2     | Multifunction I/O | Yes                 | P1MAT.2                      | ADC0.8           |

|               |          |                   |                     | CLU0A.13                     |                  |

|               |          |                   |                     | CLU1A.11                     |                  |

|               |          |                   |                     | CLU2B.10                     |                  |

|               |          |                   |                     | CLU3A.12                     |                  |

| 19            | P1.1     | Multifunction I/O | Yes                 | P1MAT.1                      | ADC0.7           |

|               |          |                   |                     | CLU0B.12                     |                  |

|               |          |                   |                     | CLU1B.10                     |                  |

|               |          |                   |                     | CLU2A.11                     |                  |

|               |          |                   |                     | CLU3B.13                     |                  |

| 20            | P1.0     | Multifunction I/O | Yes                 | P1MAT.0                      | ADC0.6           |

|               |          |                   |                     | CLU0A.12                     |                  |

|               |          |                   |                     | CLU1A.10                     |                  |

|               |          |                   |                     | CLU2A.10                     |                  |

|               |          |                   |                     | CLU3B.12                     |                  |

| 21            | P0.7     | Multifunction I/O | Yes                 | P0MAT.7                      | ADC0.5           |

|               |          |                   |                     | INT0.7                       | CMP0P.5          |

|               |          |                   |                     | INT1.7                       | CMP0N.5          |

|               |          |                   |                     | CLU10UT                      | CMP1P.1          |

|               |          |                   |                     | CLU0B.11                     | CMP1N.1          |

|               |          |                   |                     | CLU1B.9                      |                  |

|               |          |                   |                     | CLU3A.11                     |                  |

| 22            | P0.6     | Multifunction I/O | Yes                 | P0MAT.6                      | ADC0.4           |

|               |          |                   |                     | CNVSTR                       | CMP0P.4          |

|               |          |                   |                     | INT0.6                       | CMP0N.4          |

|               |          |                   |                     | INT1.6                       | CMP1P.0          |

|               |          |                   |                     | CLU0A.11                     | CMP1N.0          |

|               |          |                   |                     | CLU1B.8                      |                  |

|               |          |                   |                     | CLU3A.10                     |                  |

| 23            | P0.5     | Multifunction I/O | Yes                 | P0MAT.5                      | ADC0.3           |

|               |          |                   |                     | INT0.5                       | CMP0P.3          |

|               |          |                   |                     | INT1.5                       | CMP0N.3          |

|               |          |                   |                     | UART0_RX                     |                  |

|               |          |                   |                     | CLU0B.10                     |                  |

|               |          |                   |                     | CLU1A.9                      |                  |

|               |          |                   |                     | CLU3B.11                     |                  |

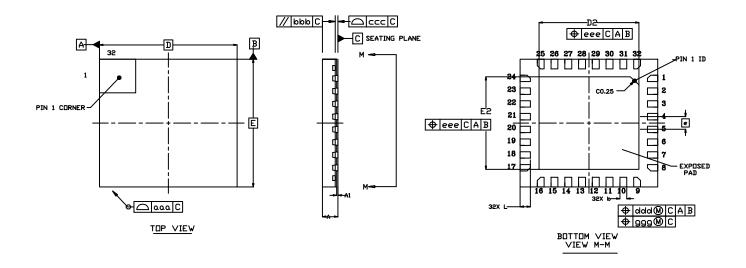

# 7. QFN32 Package Specifications

# 7.1 QFN32 Package Dimensions

Figure 7.1. QFN32 Package Drawing

Table 7.1. QFN32 Package Dimensions

| Dimension | Min       | Тур       | Max  |  |

|-----------|-----------|-----------|------|--|

| A         | 0.45      | 0.50      | 0.55 |  |

| A1        | 0.00      | 0.035     | 0.05 |  |

| b         | 0.15      | 0.20      | 0.25 |  |

| D         |           | 4.00 BSC. |      |  |

| D2        | 2.80      | 2.90      | 3.00 |  |

| е         | 0.40 BSC. |           |      |  |

| Е         |           | 4.00 BSC. |      |  |

| E2        | 2.80      | 2.90      | 3.00 |  |

| L         | 0.20      | 0.30      | 0.40 |  |

| aaa       | _         | _         | 0.10 |  |

| bbb       | _         | _         | 0.10 |  |

| ссс       | _         | _         | 0.08 |  |

| ddd       | _         | _         | 0.10 |  |

| eee       | _         | _         | 0.10 |  |

| 999       | _         | _         | 0.05 |  |

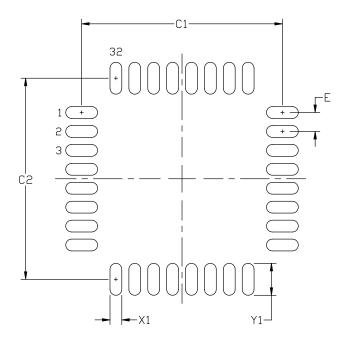

#### 8.2 QFP32 PCB Land Pattern

Figure 8.2. QFP32 PCB Land Pattern Drawing

Table 8.2. QFP32 PCB Land Pattern Dimensions

| Dimension | Min      | Max  |

|-----------|----------|------|

| C1        | 8.40     | 8.50 |

| C2        | 8.40     | 8.50 |

| Е         | 0.80 BSC |      |

| X1        | 0.55     |      |

| Y1        | 1.5      |      |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \mu m$  minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

| Dimension | Min      | Тур  | Max  |  |

|-----------|----------|------|------|--|

| е         | 0.40 BSC |      |      |  |

| e1        | 0.45 BSC |      |      |  |

| J         | 1.60     | 1.70 | 1.80 |  |

| К         | 1.60     | 1.70 | 1.80 |  |

| L         | 0.35     | 0.40 | 0.45 |  |

| L1        | 0.25     | 0.30 | 0.35 |  |

| aaa       | _        | 0.10 | _    |  |

| bbb       | _        | 0.10 | _    |  |

| ccc       | _        | 0.08 | _    |  |

| ddd       | _        | 0.1  | _    |  |

| eee       | _        | 0.1  | _    |  |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC Solid State Outline MO-248 but includes custom features which are toleranced per supplier designation.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Dimension Min Max

#### Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-SM-782 guidelines.

- 4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

- 5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 6. The stencil thickness should be 0.125 mm (5 mils).

- 7. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 8. A 2 x 1 array of 0.7 mm x 1.6 mm openings on a 0.9 mm pitch should be used for the center pad.

- 9. A No-Clean, Type-3 solder paste is recommended.

- 10. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

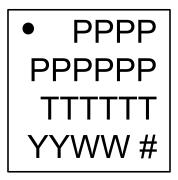

### 9.3 QFN24 Package Marking

Figure 9.3. QFN24 Package Marking

The package marking consists of:

- PPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

- # The device revision (A, B, etc.).

| Dimension | Min | Тур  | Max |

|-----------|-----|------|-----|

| aaa       |     | 0.20 |     |

| bbb       |     | 0.18 |     |

| ccc       |     | 0.10 |     |

| ddd       |     | 0.10 |     |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MO-137, variation AE.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.