Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 160MHz                                                                       |

| Connectivity               | CANbus, CSIO, EBI/EMI, I <sup>2</sup> C, LINbus, SD, SPI, UART/USART, USB    |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 154                                                                          |

| Program Memory Size        | 384КВ (384К × 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 36K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 176-LQFP                                                                     |

| Supplier Device Package    | 176-LQFP (24x24)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e2dh5j0agv2000a |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 12.6 USB Characteristics                                                                                                                              | 164                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 12.7 Low-Voltage Detection Characteristics                                                                                                            | 168                                                                                              |

| 12.7.1 Low-Voltage Detection Reset                                                                                                                    | 168                                                                                              |

| 12.7.2 Interrupt of Low-Voltage Detection                                                                                                             | 168                                                                                              |

| 12.8 MainFlash Memory Write/Erase Characteristics                                                                                                     |                                                                                                  |

| 12.9 VFLASH Memory Write/Erase Characteristics                                                                                                        | 169                                                                                              |

| 12.10 Standby Recovery Time                                                                                                                           | 170                                                                                              |

| 12.10.1 Recovery Cause: Interrupt/WKUP                                                                                                                | 170                                                                                              |

| 12.10.2 Recovery Cause: Reset                                                                                                                         | 172                                                                                              |

|                                                                                                                                                       |                                                                                                  |

| 13. Ordering Information                                                                                                                              | 174                                                                                              |

| 13. Ordering Information<br>14. Package Dimensions                                                                                                    |                                                                                                  |

| •                                                                                                                                                     | 175                                                                                              |

| 14. Package Dimensions                                                                                                                                | . 175<br>. 179                                                                                   |

| 14. Package Dimensions      15. Errata      15.1    Part Numbers Affected      15.2    Qualification Status                                           | <b>175</b><br><b>179</b><br>179<br>179                                                           |

| 14. Package Dimensions      15. Errata      15.1    Part Numbers Affected      15.2    Qualification Status      15.3    Errata Summary               | <b>175</b><br><b>179</b><br>179<br>179<br>179                                                    |

| 14. Package Dimensions      15. Errata      15.1 Part Numbers Affected      15.2 Qualification Status      15.3 Errata Summary      16. Major Changes | <b>175</b><br><b>179</b><br>179<br>179<br>179<br>179<br><b>181</b>                               |

| 14. Package Dimensions      15. Errata      15.1    Part Numbers Affected      15.2    Qualification Status                                           | . <b>175</b><br>. <b>179</b><br>. 179<br>. 179<br>. 179<br>. 179<br>. <b>181</b><br>. <b>182</b> |

|         |                       | n No.                   |         | I/O       | Pin             |               |

|---------|-----------------------|-------------------------|---------|-----------|-----------------|---------------|

| LQFP176 | LQFP120<br>Ex-LQFP120 | LQFP120<br>(S6E2DH5GJA) | FBGA161 | Pin name  | circuit<br>type | state<br>type |

|         |                       |                         |         | P95       |                 |               |

|         |                       |                         |         | AN21      |                 |               |

|         |                       |                         |         | SCK1_1    |                 |               |

| 125     | 87                    | 87                      | D13     | (SCL1_1)  | F               | L             |

|         |                       |                         |         | PNL_PD18  |                 |               |

|         |                       |                         |         | PNL_TSIG6 |                 |               |

|         |                       |                         |         | MAD19_0   |                 |               |

| 100     |                       |                         |         | PCA       |                 |               |

| 126     | —                     | _                       | —       | GE_SDA9   | ĸ               | I             |

|         |                       |                         |         | PCB       |                 |               |

| 127     | _                     | _                       | _       | GE_SDA8   | ĸ               | I             |

|         |                       |                         |         | PCC       |                 |               |

| 128     | _                     | _                       | _       | GE_SDA7   | ĸ               | I             |

| 100     |                       |                         |         | PCD       |                 |               |

| 129     | _                     | _                       | _       | GE_SDA6   | ĸ               | I             |

|         |                       |                         |         | P96       |                 |               |

|         |                       |                         |         | AN22      |                 |               |

| 130     | 88                    | 88                      | C12     | PNL_PD17  | F               | L             |

|         |                       |                         |         | PNL_TSIG5 |                 |               |

|         |                       |                         |         | MRASX_0   |                 |               |

|         |                       |                         |         | P97       |                 |               |

|         |                       |                         |         | AN23      | F               |               |

| 131     | 89                    | 89                      | C13     | PNL_PD16  |                 | L             |

|         |                       |                         |         | MCASX_0   |                 |               |

| 132     | 90                    | 90                      | B13     | VSS       | _               | _             |

| 133     | 91                    | 91                      | A12     | VCC       | _               | _             |

|         |                       |                         |         | PD0       |                 |               |

| 134     | _                     | —                       | _       | GE_SDA5   | К               | I             |

|         |                       |                         |         | PD1       |                 |               |

| 135     | —                     | -                       | _       | GE_SDA4   | ĸ               | I             |

|         |                       |                         |         | PD2       |                 |               |

| 136     | -   -                 | -   -   -               | _       | GE_SDA3   | ĸ               | I             |

|         |                       |                         |         | PD3       |                 | -             |

| 137     | —                     | —                       | -       | GE_SDA2   | ĸ               | I             |

|         |                       |                         |         | PD4       |                 | -             |

| 138     | —                     | —                       | -       | GE_SDA1   | ĸ               | I             |

|         |                       |                         |         | <br>P00   |                 |               |

| 139     | 92                    | 92                      | B12     | TRSTX     | E               | G             |

|         |                       |                         |         | P01       | 1               |               |

| 140     | 93                    | 93                      | A11     | ТСК       | E               | G             |

|         |                       |                         |         | SWCLK     |                 | -             |

|                        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pin No. |                       |                             |         |  |

|------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|-----------------------------|---------|--|

| Module                 | Pin Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LQFP176 | LQFP120<br>Ex-LQFP120 | LQFP120<br>(S6E2DH5GJ<br>A) | FBGA161 |  |

|                        | I2SMCLK0_0  | I <sup>2</sup> S ch.0 external clock pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6       | 2                     | 2                           | C3      |  |

|                        | I2SDO0_0    | I <sup>2</sup> S ch.0 serial transition data output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7       | 3                     | 3                           | C2      |  |

| I <sup>2</sup> S 0     | I2SWS0_0    | I <sup>2</sup> S ch.0 frame synchronization signal pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8       | 4                     | 4                           | D3      |  |

|                        | I2SDI0_0    | I <sup>2</sup> S ch.0 serial received data input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9       | 5                     | 5                           | D2      |  |

|                        | I2SCK0_0    | I <sup>2</sup> S ch.0 bit clock pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10      | 6                     | 6                           | D1      |  |

|                        | I2SMCLK1_0  | S ch.0 external clock pin    6      S ch.0 serial transition data output pin    7      S ch.0 frame synchronization signal pin    8      S ch.0 serial received data input pin    9      S ch.0 bit clock pin    1      S ch.1 serial received data output pin    5      S ch.1 serial transition data output pin    5      S ch.1 serial transition data output pin    5      S ch.1 serial received data input pin    3      PI clock output pin    3      PI clock output pin    3      BI clock output pin    3      BI clock output pin    3      BI chip select output pin    3      BI hardware reset output pin    3 |         | 33                    | 33                          | M3      |  |

|                        | I2SDO1_0    | I <sup>2</sup> S ch.1 serial transition data output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52      | 34                    | 34                          | L4      |  |

| l <sup>2</sup> S 1     | I2SWS1_0    | I <sup>2</sup> S ch.1 frame synchronization signal pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53      | 35                    | 35                          | M4      |  |

|                        | I2SDI1_0    | I <sup>2</sup> S ch.1 serial received data input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54      | 36                    | 36                          | K5      |  |

|                        | I2SCK1_0    | I <sup>2</sup> S ch.1 bit clock pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55      | 37                    | 37                          | L5      |  |

|                        | GE_SPCK     | SPI clock output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34      | 20                    | -                           | J1      |  |

|                        | GE_SPDQ0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35      | 21                    | -                           | K1      |  |

| GDC                    | GE_SPDQ1    | SPI dete input / output nin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38      | 24                    | -                           | J2      |  |

| High-Speed<br>Quad SPI | GE_SPDQ2    | SPI data input / output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | 25                    | -                           | J3      |  |

|                        | GE_SPDQ3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36      | 22                    | -                           | H2      |  |

|                        | GE_SPCSX0   | SPI chip select output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37      | 23                    | -                           | H3      |  |

|                        | GE_HBCK     | HBI clock output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34      | 20                    | -                           | J1      |  |

|                        | GE_HBDQ0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36      | 22                    | -                           | H2      |  |

|                        | GE_HBDQ1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37      | 23                    | -                           | H3      |  |

|                        | GE_HBDQ2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38      | 24                    | -                           | J2      |  |

|                        | GE_HBDQ3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39      | 25                    | -                           | J3      |  |

|                        | GE_HBDQ4    | HBI data input / output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40      | 26                    | -                           | K2      |  |

|                        | GE_HBDQ5    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41      | 27                    | -                           | K3      |  |

| GDC                    | GE_HBDQ6    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42      | 28                    | -                           | L2      |  |

| HyperBus I/F           | GE_HBDQ7    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43      | 29                    | -                           | L3      |  |

|                        | GE_HBCSX0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35      | 21                    | -                           | K1      |  |

| l t                    | GE_HBCSX1   | ны спір select output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12      | 8                     | -                           | E4      |  |

|                        | GE_HBRWDS   | HBI RWDS input / output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33      | 19                    | -                           | G2      |  |

| l t                    | GE_HBRESETX | HBI hardware reset output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25      | 15                    | -                           | F3      |  |

|                        | GE_HBINTX   | HBI interrupt input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26      | 16                    | -                           | F2      |  |

|                        | GE_HBRSTOX  | HBI reset input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27      | 17                    | -                           | F1      |  |

|                        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                       |                             |         |  |

# **S6E2DH Series**

## 7. Handling Devices

#### Power Supply Pins

In products with multiple VCC and VSS pins, respective pins at the same potential are interconnected within the device in order to prevent malfunctions such as latch-up. However, all of these pins should be connected externally to the power supply or ground lines in order to reduce electromagnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with each POWER pins and GND pins of this device at low impedance. It is also advisable that a ceramic capacitor of approximately 0.1 µF be connected as a bypass capacitor between VCC and VSS, between AVCC and AVSS and between AVRH and AVRL near this device.

A malfunction may occur when the power supply voltage fluctuates rapidly even though the fluctuation is within the guaranteed operating range of the VCC power supply voltage. As a rule of voltage stabilization, suppress voltage fluctuation so that the fluctuation in VCC ripple (peak-to-peak value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the standard VCC value, and the transient fluctuation rate does not exceed 0.1 V/µs at a momentary fluctuation such as switching the power supply.

#### **Crystal Oscillator Circuit**

Noise near the X0/X1 and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1, X0A/X1A pins, the crystal oscillator (or ceramic oscillator), and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0/X1 and X0A/X1A pins are surrounded by ground plane as this is expected to produce stable operation.

Evaluate oscillation of your using crystal oscillator by your mount board.

#### Sub Crystal Oscillator

This series sub oscillator circuit is low gain to keep the low current consumption. The crystal oscillator to fill the following conditions is recommended for sub crystal oscillator to stabilize the oscillation.

| Size:             | More than 3.2 mm × 1.5 mm                     |

|-------------------|-----------------------------------------------|

| Load capacitance: | Approximately 6 pF to 7 pF                    |

| -                 | When the Standard setting (CCS/CCB=11001110)  |

| Load capacitance: | Approximately 4 pF to 7 pF                    |

| ·                 | When the low power setting (CCS/CCB=00000100) |

| ■Lead type        |                                               |

| Load capacitance: | Approximately 6 pF to 7 pF                    |

|                   | When the Standard setting (CCS/CCB=11001110)  |

| Load capacitance: | Approximately 4 pF to 7 pF                    |

| •                 | When the low power setting (CCS/CCB=00000100) |

### 12.2 Recommended Operating Conditions

| Parameter           |                             | Symbol           | Conditions | Value  |       | Unit | Remarks                   |  |

|---------------------|-----------------------------|------------------|------------|--------|-------|------|---------------------------|--|

|                     | raiantetet                  |                  |            | Min    | Max   | Onic | Remarks                   |  |

| Doweroupply         | voltaga                     | Vcc              |            | 3.0    | 3.6   | V    | *1                        |  |

| Power supply        | Power supply voltage        |                  | -          | 2.7 *5 | 3.6   | V    | *2                        |  |

| Power supply        | Power supply voltage (VBAT) |                  | -          | 1.65   | 3.6   | V    |                           |  |

| Analog power        | supply voltage              | AV <sub>CC</sub> | -          | 2.7    | 3.6   | V    | AVcc = Vcc                |  |

| Analog referen      |                             | AVRH             | -          | *4     | AVcc  | V    |                           |  |

| Analog relefer      | Analog reference voltage    |                  | -          | AVss   | AVss  | V    |                           |  |

| Smoothing capacitor |                             | Cs               | -          | 1      | 10    | μF   | for built-in regulator *6 |  |

| Operating           | Junction temperature        | TJ               | -          | -40    | + 125 | °C   |                           |  |

| temperature         | Ambient temperature         | TA               | -          | -40    | *3    | °C   |                           |  |

\*1: When using the GDC part .

When P81/UDP0 and P80/UDM0 pins are used as USB (UDP0, UDM0).

\*2: When P81/UDP0 and P80/UDM0 pins are used as GPIO (P81, P80).

\*3: The maximum temperature of the ambient temperature (T<sub>A</sub>) can guarantee a range that does not exceed the junction temperature (T<sub>J</sub>).

The calculation formula of the ambient temperature (T<sub>A</sub>) is shown below.

$$\begin{split} T_A(Max) &= T_J(Max) - Pd(Max) \times \theta_{JA} \\ Pd: & \text{Power dissipation (W)} \\ \theta_{JA}: & \text{Package thermal resistance (°C/W)} \\ Pd (Max) &= V_{CC} \times I_{CC} (Max) + \Sigma (I_{OL} \times V_{OL}) + \Sigma ((V_{CC} - V_{OH}) \times (-I_{OH})) \\ I_{OL}: & L \text{ level output current} \\ I_{OH}: & H \text{ level output current} \\ V_{OL}: & L \text{ level output voltage} \end{split}$$

- V<sub>OH</sub>: H level output voltage

- \*4: The minimum value of Analog reference voltage depends on the value of compare clock cycle (t<sub>CCK</sub>). See 14.5 12-bit A/D Converter for the details.

- \*5: In between less than the minimum power supply voltage and low voltage reset/interrupt detection voltage or more, instruction execution and low voltage detection function by built-in High-speed CR(including Main PLL is used) or built-in Low-speed CR is possible to operate only.

- \*6: See "C pin" in "7. Handling Devices" for the connection of the smoothing capacitor.

### **12.4 AC Characteristics**

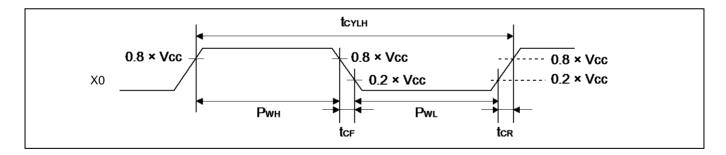

### 12.4.1 Main Clock Input Characteristics

| () | Vcc  | = | 2.7V  | to | 3.6V,  | Vss  | = | 0V    | ) |

|----|------|---|-------|----|--------|------|---|-------|---|

|    | • 00 |   | 2.1 V | .0 | 0.0 •, | v 33 |   | U V . | , |

| Parameter                                   | Symbol                               | Pin  | Conditions              | Value |     | Unit | Remarks                                 |

|---------------------------------------------|--------------------------------------|------|-------------------------|-------|-----|------|-----------------------------------------|

| Farameter                                   | Symbol                               | Name | Conditions              | Min   | Max | Unit | Remarks                                 |

|                                             | _                                    |      | -                       | 4     | 20  | MHz  | When crystal oscillator is<br>connected |

| Input frequency                             | fсн                                  |      | -                       | 4     | 20  | MHz  | When using external clock               |

| Input clock cycle                           | tсуLн                                |      | -                       | 50    | 250 | ns   | When using external clock               |

| Input clock pulse width                     | -                                    |      | Рwн/tcy∟н,<br>Рw∟/tcy∟н | 45    | 55  | %    | When using external clock               |

| Input clock rising time<br>and falling time | t <sub>CF</sub> ,<br>t <sub>CR</sub> |      | -                       | -     | 5   | ns   | When using external clock               |

|                                             | f <sub>CM</sub>                      | -    | -                       | -     | 160 | MHz  | Master clock                            |

| Internal operating alcol/*1                 | fcc                                  | -    | -                       | -     | 160 | MHz  | Base clock (HCLK/FCLK)                  |

| Internal operating clock*1<br>frequency     | f <sub>CP0</sub>                     | -    | -                       | -     | 80  | MHz  | APB0 bus clock*2                        |

|                                             | f <sub>CP1</sub>                     |      | -                       | -     | 160 | MHz  | APB1 bus clock*2                        |

|                                             | f <sub>CP2</sub>                     | -    | -                       | -     | 80  | MHz  | APB2 bus clock*2                        |

|                                             | tcycc                                | -    | -                       | 5     | -   | ns   | Base clock (HCLK/FCLK)                  |

| Internal operating clock*1                  | t <sub>CYCP0</sub>                   | -    | -                       | 10    | -   | ns   | APB0 bus clock*2                        |

| cycle time                                  | t <sub>CYCP1</sub>                   | -    | -                       | 5     | -   | ns   | APB1 bus clock*2                        |

|                                             | t <sub>CYCP2</sub>                   | -    | -                       | 10    | -   | ns   | APB2 bus clock*2                        |

\*1: For more information about each internal operating clock, see Chapter 2-1: Clock in FM4 Family Peripheral Manual Main part (002-04856).

\*2: For about each APB bus which each peripheral is connected to, see Block Diagram in this data sheet.

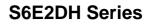

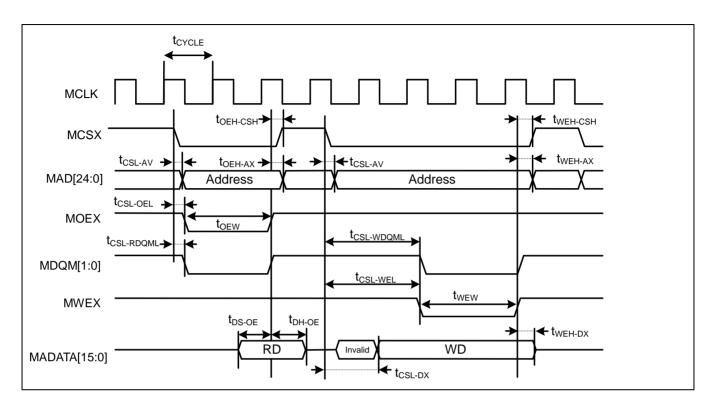

### Separate Bus Access Synchronous SRAM Mode

(V<sub>CC</sub> = 2.7V to 3.6V,  $V_{SS}$  = 0V)

| Parameter                                     | Symbol            | Pin Name              | Conditions | Va     | lue     | Unit | Remarks |

|-----------------------------------------------|-------------------|-----------------------|------------|--------|---------|------|---------|

| Farameter                                     | -                 |                       | Conditions | Min    | Max     | Unit | Remarks |

| Address delay time                            | tav               | MCLK,<br>MAD[24:0]    | -          | 1      | 9       | ns   |         |

| MCSX delay time                               | tcs∟              | MCLK,                 | -          | 1      | 9       | ns   |         |

| MCSX delay lime                               | tсsн              | MCSX                  | -          | 1      | 9       | ns   |         |

|                                               | t <sub>REL</sub>  | MCLK,                 | -          | 1      | 9       | ns   |         |

| MOEX delay time                               | tren              | MOEX                  | -          | 1      | 9       | ns   |         |

| Data set up<br>→MCLK ↑ time                   | t <sub>DS</sub>   | MCLK,<br>MADATA[15:0] | -          | 19     | -       | ns   |         |

| MCLK $\uparrow \rightarrow$<br>Data hold time | tdн               | MCLK,<br>MADATA[15:0] | -          | 0      | -       | ns   |         |

|                                               | twel              | MCLK,                 | -          | 1      | 9       | ns   |         |

| MWEX delay time                               | t <sub>WEH</sub>  | MWEX                  | -          | 1      | 9       | ns   |         |

| MDQM[1:0]                                     | t <sub>DQML</sub> | MCLK,                 | -          | 1      | 9       | ns   |         |

| delay time                                    | tdqmh             | MDQM[1:0]             | -          | 1      | 9       | ns   |         |

| MCLK ↑ →<br>Data output time                  | tods              | MCLK,<br>MADATA[15:0] | -          | MCLK+1 | MCLK+18 | ns   |         |

| MCLK ↑ →<br>Data hold time                    | top               | MCLK,<br>MADATA[15:0] | -          | 1      | 18      | ns   |         |

#### Note:

- When the external load capacitance  $C_L = 30 \, pF$

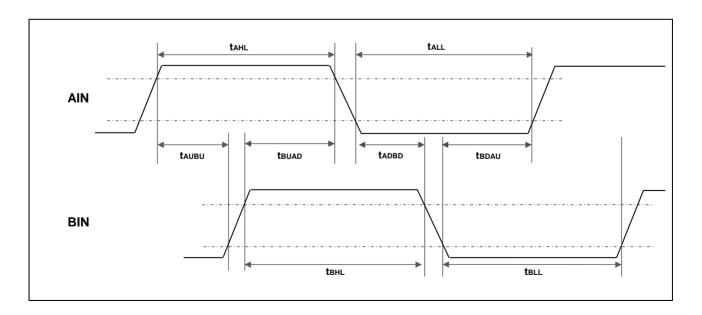

### 12.4.14 Quadrature Position/Revolution Counter Timing

(V<sub>CC</sub> = 2.7V to 3.6V, V<sub>SS</sub> = 0V)

| _                          |                   |             | Va        | lue |      |

|----------------------------|-------------------|-------------|-----------|-----|------|

| Parameter                  | Symbol            | Conditions  | Min       | Max | Unit |

| AIN pin H width            | t <sub>AHL</sub>  | -           |           |     |      |

| AIN pin L width            | t <sub>ALL</sub>  | -           |           |     |      |

| BIN pin H width            | t <sub>BHL</sub>  | -           |           |     |      |

| BIN pin L width            | t <sub>BLL</sub>  | -           |           |     |      |

| BIN rising time from       | 4                 | PC_Mode2 or |           |     |      |

| AIN pin H level            | taubu             | PC_Mode3    |           |     |      |

| AIN falling time from      | <b>t</b> BUAD     | PC_Mode2 or |           |     |      |

| BIN pin H level            | IBUAD             | PC_Mode3    |           |     |      |

| BIN falling time from      | t                 | PC_Mode2 or |           |     |      |

| AIN pin L level            | t <sub>ADBD</sub> | PC_Mode3    |           |     |      |

| AIN rising time from       | t <sub>BDAU</sub> | PC_Mode2 or |           |     |      |

| BIN pin L level            | IBDAU             | PC_Mode3    |           |     |      |

| AIN rising time from       | t <sub>ΒUAU</sub> | PC_Mode2 or |           |     |      |

| BIN pin H level            | IBUAU             | PC_Mode3    | - 2tcycp* | _   | ns   |

| BIN falling time from      | t <sub>AUBD</sub> | PC_Mode2 or | ZICYCP    | -   | 115  |

| AIN pin H level            | LAUBD             | PC_Mode3    |           |     |      |

| AIN falling time from      | <b>t</b> BDAD     | PC_Mode2 or |           |     |      |

| BIN pin L level            | IBDAD             | PC_Mode3    |           |     |      |

| BIN rising time from       | t <sub>ADBU</sub> | PC_Mode2 or |           |     |      |

| AIN pin L level            | LADBO             | PC_Mode3    |           |     |      |

| ZIN pin H width            | t <sub>ZHL</sub>  | QCR:CGSC=0  |           |     |      |

| ZIN pin L width            | tzLL              | QCR:CGSC=0  |           |     |      |

| AIN/BIN rising and falling |                   |             |           |     |      |

| time from determined ZIN   | tzabe             | QCR:CGSC=1  |           |     |      |

| level                      |                   |             |           |     |      |

| Determined ZIN level from  |                   |             |           |     |      |

| AIN/BIN rising and falling | tABEZ             | QCR:CGSC=1  |           |     |      |

| time                       |                   |             |           |     |      |

\*: t<sub>CYCP</sub> indicates the APB bus clock cycle time except when in Stop mode, in timer mode. About the APB bus number which Quadrature Position/Revolution Counter is connected to, see 8. Block Diagram in this data sheet.

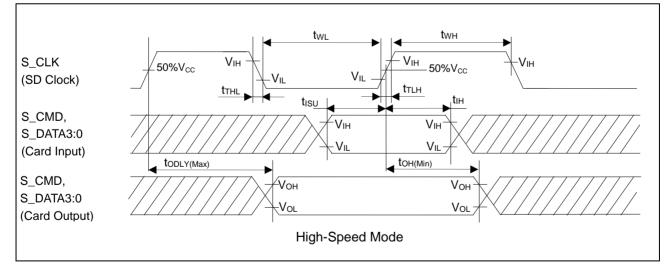

### **High-Speed Mode**

■Clock CLK (All values are referred to V<sub>IH</sub> and V<sub>IL</sub>)

### (V<sub>CC</sub> = 2.7V to 3.6V, V<sub>SS</sub> = 0V)

| Parameter                             | Symbol           | Din Namo | Pin Name Conditions       |     | Value |         |  |

|---------------------------------------|------------------|----------|---------------------------|-----|-------|---------|--|

| Farailleter                           | Symbol           |          | Conditions                | Min | Max   | Remarks |  |

| Clock frequency Data<br>Transfer Mode | f <sub>PP</sub>  | S_CLK    |                           | 0   | 50    | MHz     |  |

| Clock low time                        | t <sub>WL</sub>  | S_CLK    | C <sub>CARD</sub> ≤ 10 pF | 7   | -     | ns      |  |

| Clock high time                       | twн              | S_CLK    | (1 card)                  | 7   | -     | ns      |  |

| Clock rising time                     | tтьн             | S_CLK    |                           | -   | 3     | ns      |  |

| Clock falling time                    | t <sub>THL</sub> | S_CLK    |                           | -   | 3     | ns      |  |

### Card Inputs CMD, DAT (referenced to Clock CLK)

| Parameter        | Symbol          | Pin Name            | Conditions                | Va  | Remarks |           |

|------------------|-----------------|---------------------|---------------------------|-----|---------|-----------|

| Falameter        | Symbol          |                     | Conditions                | Min | Max     | Relliarks |

| Input setup time | tisu            | S_CMD,<br>S_DATA3:0 | C <sub>CARD</sub> ≤ 10 pF | 6   | -       | ns        |

| Input hold time  | t <sub>IH</sub> | S_CMD,<br>S_DATA3:0 | (1 card)                  | 2   | -       | ns        |

#### Card Outputs CMD, DAT (referenced to Clock CLK)

| Parameter                                      | Symbol | Pin Name            | Conditions                         | Va  | Remarks |         |

|------------------------------------------------|--------|---------------------|------------------------------------|-----|---------|---------|

| Falalletei                                     | Symbol |                     | Conditions                         | Min | Max     | Remarks |

| Output Delay time during<br>Data Transfer Mode | todly  | S_CMD,<br>S_DATA3:0 | C∟ ≤ 40 pF<br>(1 card)             | 0   | 14      | ns      |

| Output Hold time                               | tон    | S_CMD,<br>S_DATA3:0 | C <sub>L</sub> ≥ 15 pF<br>(1 card) | 2.5 | -       | ns      |

| Total System capacitance for<br>each line*     | CL     | -                   | 1 card                             | -   | 40      | pF      |

\*: In order to satisfy severe timing, host shall drive only one card.

#### Notes:

- The Card Input corresponds to the Host Output and the Card Output corresponds to the Host Input because this model is the Host.

- Please refer to: SD card interface Chapter 15 in FM4 Family Peripheral Manual Main part (002-04856) for Clock frequency (f<sub>PP</sub>).

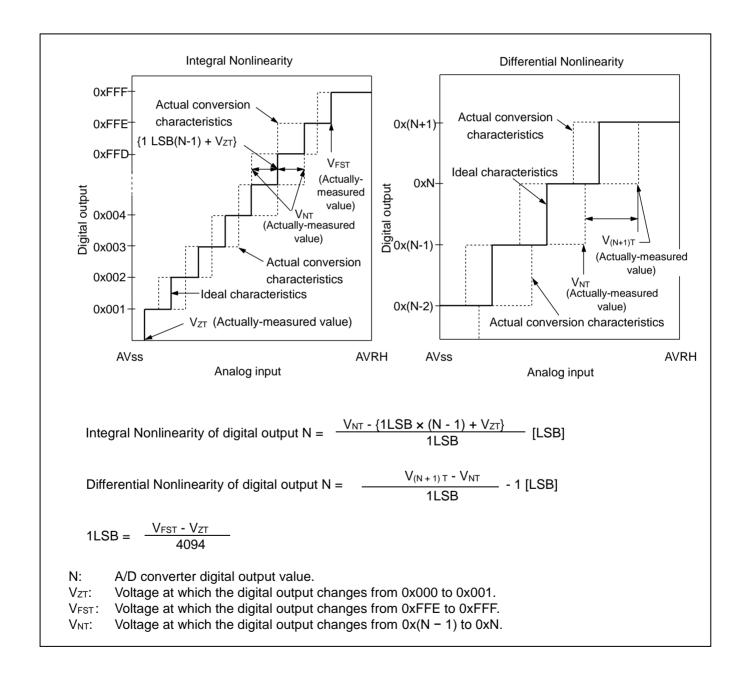

### 12.5 12-bit A/D Converter

#### **Electrical Characteristics for the A/D Converter**

| ( | Vcc = | AVcc  | = | 2.7V  | to | 3.6V.  | Vss =  | AVss   | = | AVRI      | = | 0V) |

|---|-------|-------|---|-------|----|--------|--------|--------|---|-----------|---|-----|

|   | VUC - | 11000 | _ | Z./ V | ιU | 0.0 v, | v 33 - | 110 33 | _ | / \/   \_ | _ | Uv, |

| Demonster                                     | remeter Symbol Pin Value |      |                   |             | 11       | Dementer |                                      |

|-----------------------------------------------|--------------------------|------|-------------------|-------------|----------|----------|--------------------------------------|

| Parameter                                     | Symbol                   | Name | Min               | Тур         | Max      | Unit     | Remarks                              |

| Resolution                                    | -                        | -    | -                 | -           | 12       | bit      |                                      |

| Integral Nonlinearity                         | -                        | -    | -                 | -           | ± 4.5    | LSB      |                                      |

| Differential Nonlinearity                     | -                        | -    | -                 | -           | ± 2.5    | LSB      | AVRH=2.7 V to                        |

| Zero transition voltage                       | Vzt                      | ANxx | -                 | ±2          | ±7       | LSB      | 3.6 V                                |

| Full-scale transition voltage                 | VFST                     | ANxx | -                 | AVRH ±<br>2 | AVRH ± 7 | LSB      | Offset calibration when used         |

| Total error                                   | -                        | -    | -                 | ± 3         | ± 8      | LSB      |                                      |

| Conversion time                               | -                        | -    | 1.0 <sup>*1</sup> | -           | -        | μs       |                                      |

| Sampling time *2                              | ts                       | -    | 0.3               | -           | 10       | μs       |                                      |

| Compare clock cycle*3                         | tсск                     | -    | 50                | -           | 1000     | ns       |                                      |

| State transition time to operation permission | ts⊤⊤                     | -    | -                 | -           | 1.0      | μs       |                                      |

| Power supply current                          | -                        | AVcc | -                 | 0.30        | 0.45     | mA       | A/D 1unit<br>operation               |

| (analog + digital)                            |                          |      | -                 | 0.1         | 9.5      | μA       | When A/D stop                        |

| Reference power<br>supply current(AVRH)       | -                        | AVRH | -                 | 0.66        | 1.18     | mA       | A/D 1unit<br>operation<br>AVRH=3.3 V |

|                                               |                          |      | -                 | 0.2         | 3.2      | μA       | When A/D stop                        |

| Analog input capacity                         | CAIN                     | -    | -                 | -           | 12.05    | pF       |                                      |

| Analog input resistance                       | RAIN                     | -    | -                 | -           | 1.8      | kΩ       |                                      |

| Interchannel disparity                        | -                        | -    | -                 | -           | 4        | LSB      |                                      |

| Analog port input leak current                | -                        | ANxx | -                 | -           | 5        | μA       |                                      |

| Anglenianut It                                |                          |      | AVss              | -           | AVRH     | V        |                                      |

| Analog input voltage                          | -                        | ANxx | AVss              | -           | AVcc     | V        |                                      |

| Defense veltere                               | -                        | AVRH | 2.7               | -           | AVcc     | V        | t <sub>сск</sub> ≥ 50 ns             |

| Reference voltage                             | -                        | AVRL | AV <sub>SS</sub>  | -           | AVss     | V        |                                      |

\*1: The conversion time is the value of sampling time  $(t_S)$  + compare time  $(t_C)$ .

Ensure that it satisfies the value of sampling time (ts) and compare clock cycle (tcck).

For setting of sampling time and compare clock cycle, see Chapter 1-1: A/D Converter in FM4 Family Peripheral Manual Analog Macro Part (002-04860). The register setting of the A/D converter is reflected by the APB bus clock timing. For more information about the APB bus signal to which the A/D converter is connected, see 10. Block Diagram in this data sheet.

The sampling clock and compare clock are set at base clock (HCLK).

\*2: A necessary sampling time changes by external impedance. Ensure that it set the sampling time to satisfy (Equation 1).

\*3: The compare time (tc) is the value of (Equation 2).

### Definition of 12-bit A/D Converter Terms

| ■Resolution:                | Analog variation that is recognized by an A/D converter.                                                                                                                                                                                            |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integral Nonlinearity:      | Deviation of the line between the zero-transition point (0b00000000000 $\leftarrow \rightarrow$ 0b0000000001) and the full-scale transition point (0b1111111110 $\leftarrow \rightarrow$ 0b11111111111) from the actual conversion characteristics. |

| ■Differential Nonlinearity: | Deviation from the ideal value of the input voltage that is required to change the output code by 1 LSB.                                                                                                                                            |

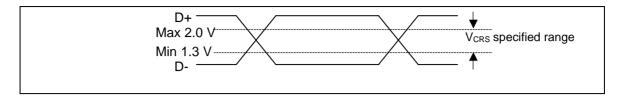

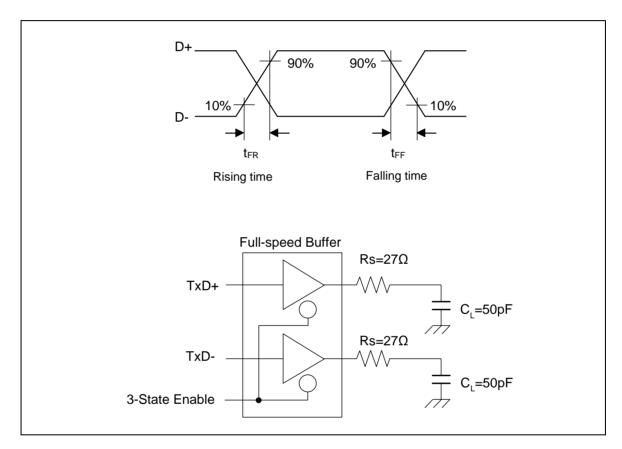

\*5: They indicate Rising time (tFR) and Falling time (tFF) of the Full-speed differential data signal. They are defined by the time between 10 % and 90 % of the output signal voltage. For Full-speed buffer, tFR/tFF ratio is regulated as within ± 10 % to minimize RFI emission.

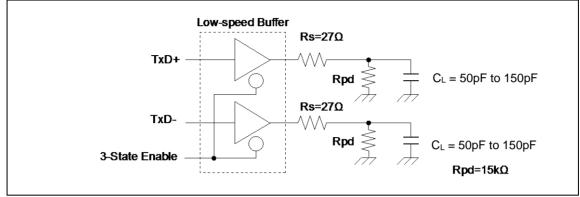

#### ■Low-speed load (Upstream port load) - Reference 1

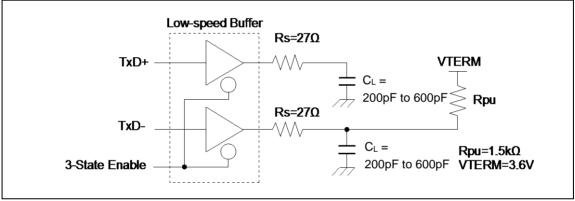

### Low-speed load (Downstream port load) - Reference 2

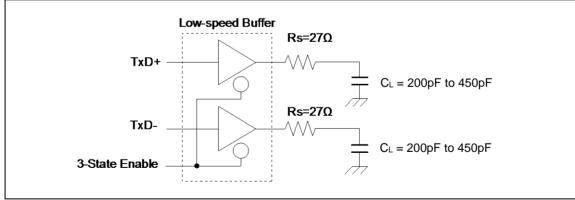

### ■Low-speed load (Compliance load)

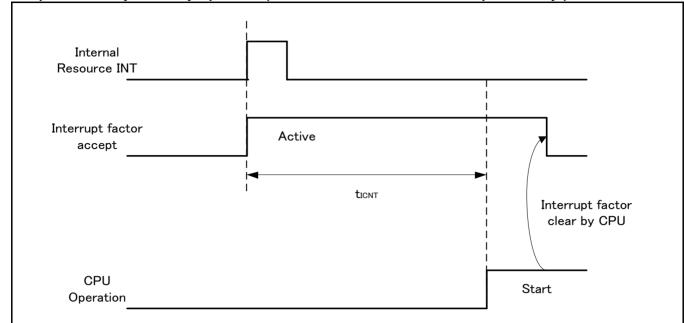

#### Example of Standby Recovery Operation (when in Internal Resource Interrupt Recovery\*)

\*: Depending on the standby mode, interrupt from the internal resource is not included in the recovery cause.

#### Notes:

- The return factor is different in each Low-Power consumption modes.

See Chapter 6: The return factor from each low power consumption modes in "FM4 Family Peripheral Manual Main Part (002-04856).

- When interrupt recoveries, the operation mode that CPU recoveries depends on the state before the Low-Power consumption mode transition. See Chapter 6: Low Power Consumption Mode" in "FM4 Family Peripheral Manual Main part (002-04856).

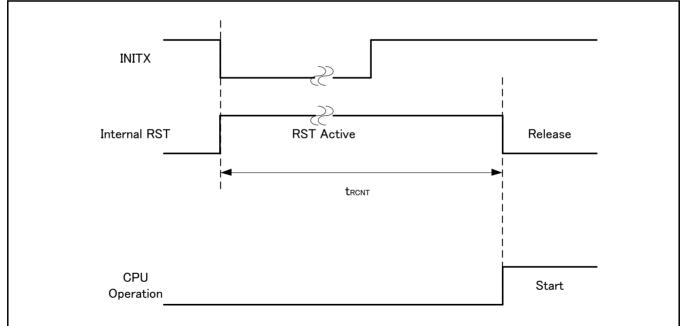

#### 12.10.2 Recovery Cause: Reset

The time from reset release to the program operation start is shown.

### **Recovery Count Time**

$(V_{CC} = 2.7V \text{ to } 3.6V, V_{SS} = 0V)$

| Bananatan                                                     | Cumphiel      | Va  | lue  | 11   | Demonster             |

|---------------------------------------------------------------|---------------|-----|------|------|-----------------------|

| Parameter                                                     | Symbol        | Тур | Max* | Unit | Remarks               |

| Sleep mode                                                    |               | 155 | 266  | μs   |                       |

| High-speed CR Timer mode<br>Main Timer mode<br>PLL Timer mode |               | 155 | 266  | μs   |                       |

| Low-speed CR timer mode                                       |               | 315 | 567  | μs   |                       |

| Sub timer mode                                                | <b>t</b> ront | 315 | 567  | μs   |                       |

| RTC mode<br>Stop mode                                         | -             | 315 | 567  | μs   |                       |

| Deep standby RTC mode                                         |               | 336 | 667  | μs   | without RAM retention |

| Deep standby Stop mode                                        |               | 336 | 667  | μs   | with RAM retention    |

\*: The maximum value depends on the built-in CR accuracy.

### Example of Standby Recovery Operation (when in INITX Recovery)

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |