Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                |

| Core Processor             | ARM® Cortex®-M4                                                                       |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 48MHz                                                                                 |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, MMC/SD, QSPI, SCI, SPI, SSI, UART/USART, USB       |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 36                                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | 8K x 8                                                                                |

| RAM Size                   | 32K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                           |

| Data Converters            | A/D 14x14b; D/A 3x8b, 3x12b                                                           |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 48-LQFP                                                                               |

| Supplier Device Package    | 48-LFQFP (7x7)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs3a6783a01cfl-aa0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

S3A6 Datasheet 1. Overview

Table 1.3 System (1 of 2)

| Feature                                               | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating modes                                       | Two operating modes:  • Single-chip mode  • SCI/USB boot mode.  See section 3, Operating Modes in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Resets                                                | 14 resets:  RES pin reset  Power-on reset  VBATT-selected voltage power-on reset  Independent watchdog timer reset  Watchdog timer reset  Voltage monitor 0 reset  Voltage monitor 1 reset  Voltage monitor 2 reset  SRAM parity error reset  SRAM ECC error reset  Bus master MPU error reset  Bus slave MPU error reset  CPU stack pointer error reset  Software reset.  See section 5, Resets in User's Manual.                                                                                                                                                                                                               |

| Low Voltage Detection (LVD)                           | Low Voltage Detection (LVD) function monitors the voltage level input to the VCC pin, and the detection level can be selected using a software program. See section 7, Low Voltage Detection (LVD) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Clocks                                                | <ul> <li>Main clock oscillator (MOSC)</li> <li>Sub-clock oscillator (SOSC)</li> <li>High-speed on-chip oscillator (HOCO)</li> <li>Middle-speed on-chip oscillator (MOCO)</li> <li>Low-speed on-chip oscillator (LOCO)</li> <li>PLL frequency synthesizer</li> <li>IWDT-dedicated on-chip oscillator</li> <li>Clock out support.</li> <li>See section 8, Clock Generation Circuit in User's Manual.</li> </ul>                                                                                                                                                                                                                    |

| Clock Frequency Accuracy<br>Measurement Circuit (CAC) | The Clock Frequency Accuracy Measurement Circuit (CAC) counts pulses of the clock to be measured (measurement target clock) within the time generated by the clock to be used as a measurement reference (measurement reference clock), and determines the accuracy depending on whether the number of pulses is within the allowable range.  When measurement is complete or the number of pulses within the time generated by the measurement reference clock is not within the allowable range, an interrupt request is generated.  See section 9, Clock Frequency Accuracy Measurement Circuit (CAC) in User's Manual.       |

| Interrupt Controller Unit (ICU)                       | The Interrupt Controller Unit (ICU) controls which event signals are linked to the NVIC/DTC module and DMAC module. The ICU also controls NMI interrupts. See section 13, Interrupt Controller Unit (ICU) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Key Interrupt Function (KINT)                         | A key interrupt can be generated by setting the Key Return Mode Register (KRM) and inputting a rising or falling edge to the key interrupt input pins. See section 20, Key Interrupt Function (KINT) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                           |

| Low power modes                                       | Power consumption can be reduced in multiple ways, such as by setting clock dividers, stopping modules, selecting power control mode in normal operation, and transitioning to low power modes. See section 10, Low Power Modes in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                |

| Battery backup function                               | A battery backup function is provided for partial powering by a battery. The battery powered area includes RTC, SOSC, LOCO, wakeup control, backup memory, VBATT_R low voltage detection, and switches between VCC and VBATT.  During normal operation, the battery powered area is powered by the main power supply, which is the VCC pin. When a VCC voltage drop is detected, the power source is switched to the dedicated battery backup power pin, the VBATT pin.  When the voltage rises again, the power source is switched from the VBATT pin to the VCC pin. See section 11, Battery Backup Function in User's Manual. |

| Register write protection                             | The register write protection function protects important registers from being overwritten because of software errors. See section 12, Register Write Protection in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

S3A6 Datasheet 1. Overview

# Table 1.10 Data processing

| Feature                                  | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Cyclic Redundancy Check (CRC) calculator | The Cyclic Redundancy Check (CRC) calculator generates CRC codes to detect errors in the data. The bit order of CRC calculation results can be switched for LSB-first or MSB-first communication. Additionally, various CRC generation polynomials are available. The snoop function allows monitoring reads from and writes to specific addresses. This function is useful in applications that require CRC code to be generated automatically in certain events, such as monitoring writes to the serial transmit buffer and reads from the serial receive buffer. See section 32, Cyclic Redundancy Check (CRC) Calculator in User's Manual. |  |  |  |  |  |

| Data Operation Circuit (DOC)             | The Data Operation Circuit (DOC) compares, adds, and subtracts 16-bit data. See section 42, Data Operation Circuit (DOC) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

# Table 1.11 Security

| Feature                       | Functional description                                                                                                                |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Secure Crypto Engine 5 (SCE5) | Security algorithm Symmetric algorithm: AES. Other support features TRNG (True Random Number Generator) Hash-value generation: GHASH. |

S3A6 Datasheet 1. Overview

Table 1.14 Pin functions (3 of 4)

| Function               | Signal                                                        | I/O    | Description                                                                                                                                                                                                     |

|------------------------|---------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USBFS                  | VSS_USB                                                       | Input  | Ground pin                                                                                                                                                                                                      |

|                        | VCC_USB_LDO                                                   | Input  | Power supply pin for USB LDO regulator                                                                                                                                                                          |

|                        | VCC_USB                                                       | I/O    | Input: USB transceiver power supply pin. Output: USB LDO regulator output pin. This pin should be connected to an external capacitor.                                                                           |

|                        | USB_DP                                                        | I/O    | D+ I/O pin of the USB on-chip transceiver. This pin should be connected to the D+ pin of the USB bus.                                                                                                           |

|                        | USB_DM                                                        | I/O    | D- I/O pin of the USB on-chip transceiver. This pin should be connected to the D- pin of the USB bus.                                                                                                           |

|                        | USB_VBUS                                                      | Input  | USB cable connection monitor pin. This pin should be connected to VBUS of the USB bus. The VBUS pin status (connected or disconnected) can be detected when the USB module is operating as a device controller. |

|                        | USB_EXICEN                                                    | Output | Low power control signal for external power supply (OTG) chip                                                                                                                                                   |

|                        | USB_VBUSEN                                                    | Output | VBUS (5 V) supply enable signal for external power supply chip                                                                                                                                                  |

|                        | USB_OVRCURA,<br>USB_OVRCURB                                   | Input  | Connect the external overcurrent detection signals to these pins. Connect the VBUS comparator signals to these pins when the OTG power supply chip is connected.                                                |

|                        | USB_ID                                                        | Input  | Connect the MicroAB connector ID input signal to this pin during operation in OTG mode                                                                                                                          |

| Analog power<br>supply | AVCC0                                                         | Input  | Analog voltage supply pin                                                                                                                                                                                       |

|                        | AVSS0                                                         | Input  | Analog voltage supply ground pin                                                                                                                                                                                |

|                        | VREFH0                                                        | Input  | Analog reference voltage supply pin                                                                                                                                                                             |

|                        | VREFL0                                                        | Input  | Reference power supply ground pin                                                                                                                                                                               |

|                        | VREFH                                                         | Input  | Analog reference voltage supply pin for D/A converter                                                                                                                                                           |

|                        | VREFL                                                         | Input  | Analog reference ground pin for D/A converter                                                                                                                                                                   |

| ADC14                  | AN000 to AN014,<br>AN016 to AN025                             | Input  | Input pins for the analog signals to be processed by the A/D converter                                                                                                                                          |

|                        | ADTRG0                                                        | Input  | Input pins for the external trigger signals that start the A/D conversion, active-low                                                                                                                           |

| DAC12                  | DA0                                                           | Output | Output pins for the analog signals to be processed by the D/A converter                                                                                                                                         |

| Comparator output      | VCOUT                                                         | Output | Comparator output pin                                                                                                                                                                                           |

| ACMPLP                 | CMPREF0,<br>CMPREF1                                           | Input  | Reference voltage input pin                                                                                                                                                                                     |

|                        | CMPIN0, CMPIN1                                                | Input  | Analog voltage input pins                                                                                                                                                                                       |

| OPAMP                  | AMP0+ to AMP3+                                                | Input  | Analog voltage input pins                                                                                                                                                                                       |

|                        | AMP0- to AMP3-                                                | Input  | Analog voltage input pins                                                                                                                                                                                       |

|                        | AMP00 to AMP30                                                | Output | Analog voltage output pins                                                                                                                                                                                      |

| CTSU                   | TS00 to TS13,<br>TS17 to TS22,<br>TS27 to TS31,<br>TS34, TS35 | Input  | Capacitive touch detection pins (touch pins)                                                                                                                                                                    |

|                        | TSCAP                                                         | -      | Secondary power supply pin for the touch driver                                                                                                                                                                 |

Table 2.6 I/O  $I_{OH}$ ,  $I_{OL}$  (2 of 2) Conditions: VCC = AVCC0 = VCC\_USB = VCC\_USB\_LCO = 1.6 to 5.5 V

| Parameter                  |                                                                                                                                  | Symbol                               | Min                    | Тур | Max | Unit  |    |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------|-----|-----|-------|----|

| Permissible output current | Ports P212, P213                                                                                                                 | -                                    | I <sub>OH</sub>        | -   | -   | -4.0  | mA |

| Max value per pin)         |                                                                                                                                  |                                      | I <sub>OL</sub>        | -   | -   | 4.0   | mA |

|                            | Port P408                                                                                                                        | Low drive*1                          | I <sub>OH</sub>        | -   | -   | -4.0  | mA |

|                            |                                                                                                                                  |                                      | I <sub>OL</sub>        | -   | -   | 4.0   | mA |

|                            |                                                                                                                                  | Middle drive for IIC                 | I <sub>OH</sub>        | -   | -   | -8.0  | mA |

|                            |                                                                                                                                  | Fast-mode*4<br>VCC = 2.7 to 5.5 V    | I <sub>OL</sub>        | -   | -   | 8.0   | mA |

|                            |                                                                                                                                  | Middle drive*2                       | I <sub>OH</sub>        | -   | -   | -20.0 | mA |

|                            |                                                                                                                                  | VCC = 3.0 to 5.5 V                   | I <sub>OL</sub>        | -   | -   | 20.0  | mA |

|                            | Port P409                                                                                                                        | Low drive*1                          | I <sub>OH</sub>        | -   | -   | -4.0  | mA |

|                            |                                                                                                                                  |                                      | I <sub>OL</sub>        | -   | -   | 4.0   | mA |

|                            |                                                                                                                                  | Middle drive*2                       | I <sub>OH</sub>        | -   | -   | -8.0  | mA |

|                            |                                                                                                                                  | VCC = 2.7 to 3.0 V                   | I <sub>OL</sub>        | -   | -   | 8.0   | mA |

|                            |                                                                                                                                  | Middle drive*2<br>VCC = 3.0 to 5.5 V | I <sub>OH</sub>        | -   | -   | -20.0 | mA |

|                            |                                                                                                                                  |                                      | l <sub>OL</sub>        | -   | -   | 20.0  | mA |

|                            | Ports P100 to P115,<br>P201 to P204, P300 to P307,<br>P500 to P503, P600 to P603,<br>P608 to P610, P808, P809<br>(total 41 pins) | Low drive*1                          | I <sub>OH</sub>        | -   | -   | -4.0  | mA |

|                            |                                                                                                                                  |                                      | I <sub>OL</sub>        | -   | -   | 4.0   | mA |

|                            |                                                                                                                                  | Middle drive*2                       | I <sub>OH</sub>        | -   | -   | -4.0  | mA |

|                            |                                                                                                                                  |                                      | I <sub>OL</sub>        | -   | -   | 8.0   | mA |

|                            | Ports P914, P915                                                                                                                 | -                                    | I <sub>OH</sub>        | -   | -   | -4.0  | mA |

|                            |                                                                                                                                  |                                      | I <sub>OL</sub>        | -   | -   | 4.0   | mA |

|                            | Other output pin*3                                                                                                               | Low drive*1                          | I <sub>OH</sub>        | -   | -   | -4.0  | mA |

|                            |                                                                                                                                  |                                      | I <sub>OL</sub>        | -   | -   | 4.0   | mA |

|                            |                                                                                                                                  | Middle drive*2                       | I <sub>OH</sub>        | -   | -   | -8.0  | mA |

|                            |                                                                                                                                  |                                      | I <sub>OL</sub>        | -   | -   | 8.0   | mA |

| Permissible output current | Total of ports P000 to P008, P01                                                                                                 | 0 to P015                            | ΣI <sub>OH (max)</sub> | -   | -   | -30   | mA |

| max value total pins)      |                                                                                                                                  |                                      | ΣI <sub>OL (max)</sub> | -   | -   | 30    | mA |

|                            | Ports P914, P915                                                                                                                 |                                      | ΣI <sub>OH (max)</sub> | -   | -   | -2.0  | mA |

|                            |                                                                                                                                  |                                      | ΣI <sub>OL (min)</sub> | -   | -   | 2.0   | mA |

|                            | Total of all output pin*5                                                                                                        |                                      | ΣI <sub>OH (max)</sub> | -   | -   | -60   | mA |

|                            |                                                                                                                                  |                                      | ΣI <sub>OL (max)</sub> | -   | -   | 60    | mA |

Caution: To protect the reliability of the MCU, the output current values should not exceed the values in this table. The average output current indicates the average value of current measured during 100  $\mu s$ .

- Note 1. This is the value when low driving ability is selected with the Port Drive Capability bit in PmnPFS register.

- Note 2. This is the value when middle driving ability is selected with the Port Drive Capability bit in PmnPFS register.

- Except for ports P200, P214, P215, which are input ports. Note 3.

- Note 4. This is the value when middle driving ability for IIC Fast-mode is selected with the Port Drive Capability bit in PmnPFS register.

- Note 5. For details on the permissible output current used with CTSU, see section 2.11, CTSU Characteristics.

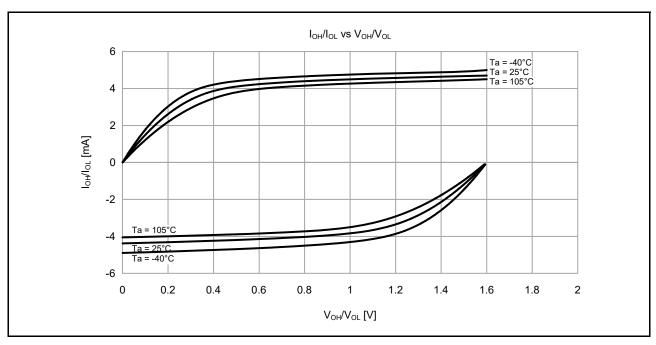

Figure 2.8  $V_{OH}/V_{OL}$  and  $I_{OH}/I_{OL}$  temperature characteristics at VCC = 1.6 V when middle drive output is selected (reference data)

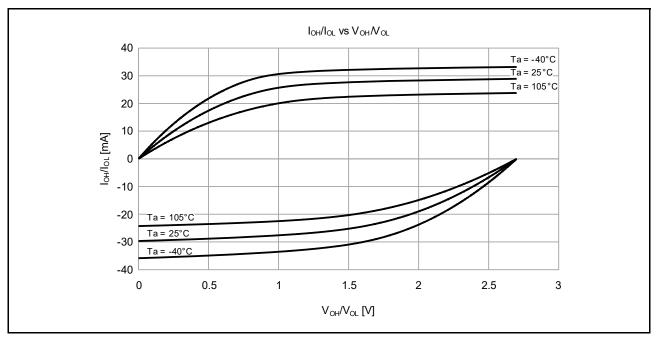

Figure 2.9  $V_{OH}/V_{OL}$  and  $I_{OH}/I_{OL}$  temperature characteristics at VCC = 2.7 V when middle drive output is selected (reference data)

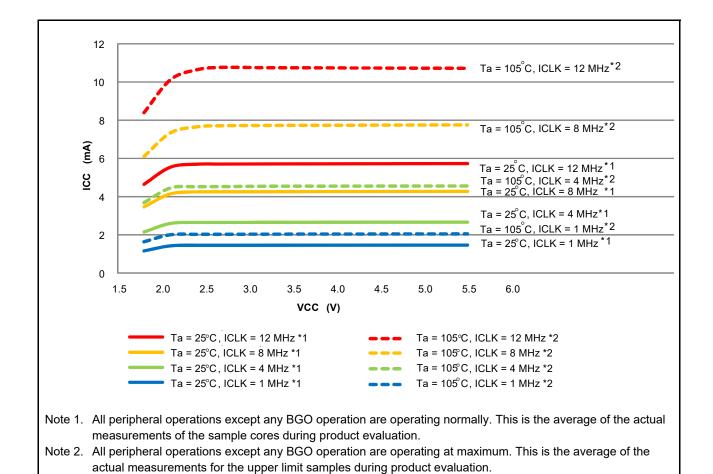

Figure 2.18 Voltage dependency in middle-speed operating mode (reference data)

# 2.2.10 VCC Rise and Fall Gradient and Ripple Frequency

Table 2.15 Rise and fall gradient characteristics

Conditions: VCC = AVCC0 = 0 to 5.5 V

| Parameter                    |                                              | Symbol | Min  | Тур | Max | Unit | Test conditions |

|------------------------------|----------------------------------------------|--------|------|-----|-----|------|-----------------|

| Power-on VCC rising gradient | 1 (                                          |        | 0.02 | -   | 2   | ms/V | -               |

|                              | Voltage monitor 0 reset enabled at startup*1 |        | 0.02 | -   | -   |      |                 |

|                              | SCI/USB boot mode*2                          |        | 0.02 | -   | 2   |      |                 |

Note 1. When OFS1.LVDAS = 0.

Note 2. At boot mode, the reset from voltage monitor 0 is disabled regardless of the value of OFS1.LVDAS bit.

## Table 2.16 Rising and falling gradient and ripple frequency characteristics

Conditions: VCC = AVCC0 = VCC USB = 1.6 to 5.5 V

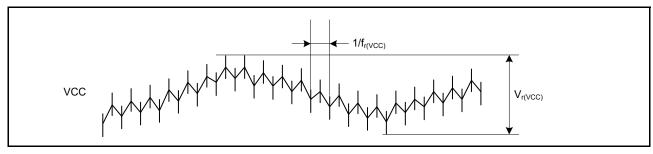

The ripple voltage must meet the allowable ripple frequency  $f_{r(VCC)}$  within the range between the VCC upper limit (5.5 V) and lower limit (1.6 V).

When VCC change exceeds VCC ±10%, the allowable voltage change rising/falling gradient dt/dVCC must be met.

| Parameter                                            | Symbol               | Min | Тур | Max | Unit | Test conditions                               |

|------------------------------------------------------|----------------------|-----|-----|-----|------|-----------------------------------------------|

| Allowable ripple frequency                           | f <sub>r (VCC)</sub> | -   | -   | 10  | kHz  | Figure 2.24 $V_{r (VCC)} \le VCC \times 0.2$  |

|                                                      |                      | -   | -   | 1   | MHz  | Figure 2.24 $V_{r (VCC)} \le VCC \times 0.08$ |

|                                                      |                      | -   | -   | 10  | MHz  | Figure 2.24 $V_{r (VCC)} \le VCC \times 0.06$ |

| Allowable voltage change rising and falling gradient | dt/dVCC              | 1.0 | -   | -   | ms/V | When VCC change exceeds VCC ±10%              |

Figure 2.24 Ripple waveform

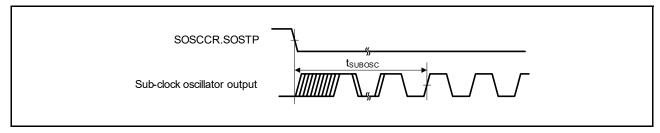

Figure 2.30 Sub-clock oscillation start timing

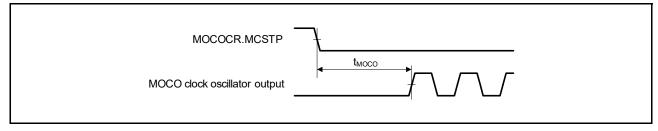

Figure 2.31 MOCO clock oscillation start timing

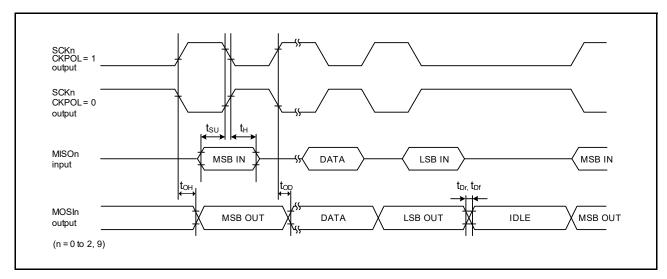

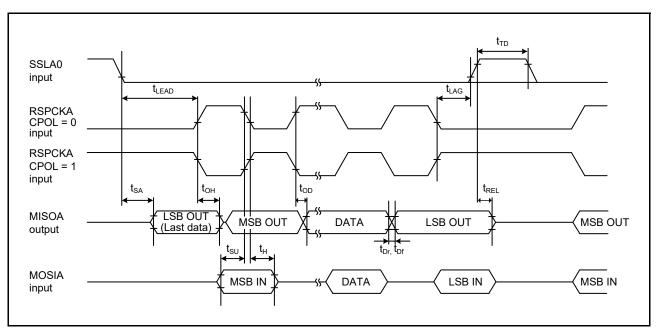

Figure 2.48 SCI simple SPI mode timing for master when CKPH = 0

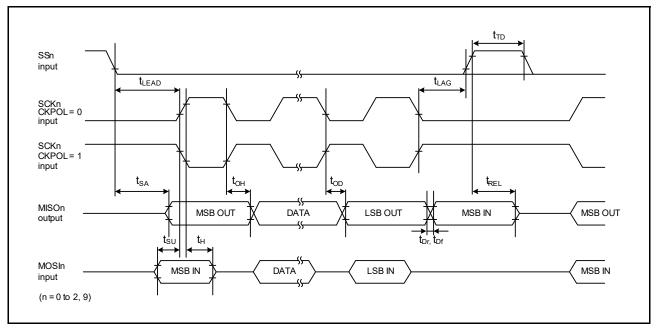

Figure 2.49 SCI simple SPI mode timing for slave when CKPH = 1

Figure 2.58 SPI timing for slave when CPHA = 1

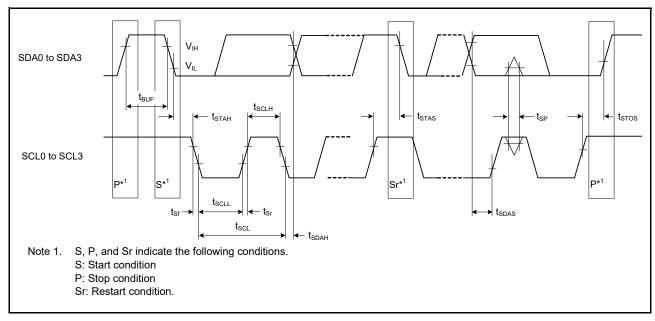

# 2.3.10 IIC Timing

Table 2.37 IIC timing (1 of 2) Conditions: VCC = 2.7 to 5.5 V

| Parameter           |                                                                    |                   | Min*1                                                        | Max                         | Unit | Test conditions |

|---------------------|--------------------------------------------------------------------|-------------------|--------------------------------------------------------------|-----------------------------|------|-----------------|

| IIC (standard mode, | SCL input cycle time                                               | t <sub>SCL</sub>  | 6 (12) × t <sub>IICcyc</sub> + 1300                          | -                           | ns   | Figure 2.59     |

| SMBus)              | SCL input high pulse width                                         | t <sub>SCLH</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   | -               |

|                     | SCL input low pulse width                                          | t <sub>SCLL</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                 |

|                     | SCL, SDA input rise time                                           | t <sub>Sr</sub>   | -                                                            | 1,000                       | ns   |                 |

|                     | SCL, SDA input fall time                                           | t <sub>Sf</sub>   | -                                                            | 300                         | ns   |                 |

|                     | SCL, SDA input spike pulse removal time                            | t <sub>SP</sub>   | 0                                                            | 1 (4) × t <sub>IICcyc</sub> | ns   | -               |

|                     | SDA input bus free time<br>(When wakeup function is disabled)      | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   | -               |

|                     | SDA input bus free time<br>(When wakeup function is enabled)       | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> +<br>4 × t <sub>Pcyc</sub> + 300 | -                           | ns   |                 |

|                     | START condition input hold time (When wakeup function is disabled) | t <sub>STAH</sub> | t <sub>IICcyc</sub> + 300                                    | -                           | ns   |                 |

|                     | START condition input hold time (When wakeup function is enabled)  | t <sub>STAH</sub> | 1 (5) × t <sub>IICcyc</sub> +<br>t <sub>Pcyc</sub> + 300     | -                           | ns   |                 |

|                     | Repeated START condition input setup time                          | t <sub>STAS</sub> | 1,000                                                        | -                           | ns   |                 |

|                     | STOP condition input setup time                                    | t <sub>STOS</sub> | 1,000                                                        | -                           | ns   | 1               |

|                     | Data input setup time                                              | t <sub>SDAS</sub> | t <sub>IICcyc</sub> + 50                                     | -                           | ns   |                 |

|                     | Data input hold time                                               | t <sub>SDAH</sub> | 0                                                            | -                           | ns   |                 |

|                     | SCL, SDA capacitive load                                           | C <sub>b</sub>    | -                                                            | 400                         | pF   |                 |

Table 2.37 IIC timing (2 of 2) Conditions: VCC = 2.7 to 5.5 V

| Parameter          |                                                                    | Symbol            | Min*1                                                        | Max                         | Unit | Test conditions                             |

|--------------------|--------------------------------------------------------------------|-------------------|--------------------------------------------------------------|-----------------------------|------|---------------------------------------------|

| IIC<br>(Fast mode) | SCL input cycle time                                               | t <sub>SCL</sub>  | 6 (12) × t <sub>IICcyc</sub> + 600                           | -                           | ns   | Figure 2.59<br>For all ports                |

|                    | SCL input high pulse width                                         | t <sub>SCLH</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   | except P408,<br>use<br>PmnPFS.DSC           |

|                    | SCL input low pulse width                                          | t <sub>SCLL</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   | R of middle drive.                          |

|                    | SCL, SDA input rise time                                           | t <sub>Sr</sub>   | -                                                            | 300                         | ns   | For port P408,<br>use                       |

|                    | SCL, SDA input fall time                                           | t <sub>Sf</sub>   | -                                                            | 300                         | ns   | PmnPFS.DSC                                  |

|                    | SCL, SDA input spike pulse removal time                            | t <sub>SP</sub>   | 0                                                            | 1 (4) × t <sub>IICcyc</sub> | ns   | R1/DSCR of<br>middle drive<br>for IIC fast- |

|                    | SDA input bus free time<br>(When wakeup function is disabled)      | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   | mode.                                       |

|                    | SDA input bus free time<br>(When wakeup function is enabled)       | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> +<br>4 × t <sub>Pcyc</sub> + 300 | -                           | ns   |                                             |

|                    | START condition input hold time (When wakeup function is disabled) | t <sub>STAH</sub> | t <sub>IICcyc</sub> + 300                                    | -                           | ns   |                                             |

|                    | START condition input hold time (When wakeup function is enabled)  | t <sub>STAH</sub> | 1(5) × t <sub>IICcyc</sub> +<br>t <sub>Pcyc</sub> + 300      | -                           | ns   |                                             |

|                    | Repeated START condition input setup time                          | t <sub>STAS</sub> | 300                                                          | -                           | ns   |                                             |

|                    | STOP condition input setup time                                    | t <sub>STOS</sub> | 300                                                          | -                           | ns   | ]                                           |

|                    | Data input setup time                                              | t <sub>SDAS</sub> | t <sub>IICcyc</sub> + 50                                     | -                           | ns   | ]                                           |

|                    | Data input hold time                                               | t <sub>SDAH</sub> | 0                                                            | -                           | ns   | ]                                           |

|                    | SCL, SDA capacitive load                                           | C <sub>b</sub>    | -                                                            | 400                         | pF   |                                             |

Note: t<sub>IICcyc</sub>: IIC internal reference clock (IICφ) cycle, t<sub>Pcyc</sub>: PCLKB cycle

Note 1. The value in parentheses apply when ICMR3.NF[1:0] is set to 11b while the digital filter is enabled with ICFER.NFE set to 1.

Figure 2.59 IIC bus interface input/output timing

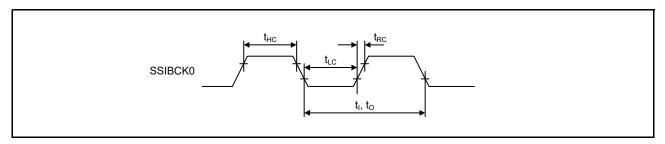

# 2.3.11 SSIE Timing

**Table 2.38 SSIE timing** Conditions: VCC = 1.6 to 5.5 V

| Parameter                     |                                              |                | Symbol             | Min | Max | Unit | Test conditions             |

|-------------------------------|----------------------------------------------|----------------|--------------------|-----|-----|------|-----------------------------|

| SSIE                          | AUDIO_CLK input                              | 2.7 V or above | t <sub>AUDIO</sub> | -   | 25  | MHz  | -                           |

|                               | frequency                                    | 1.6 V or above |                    | -   | 4   |      |                             |

|                               | Output clock period                          | •              | t <sub>O</sub>     | 250 | -   | ns   | Figure 2.60                 |

|                               | Input clock period                           |                | t <sub>l</sub>     | 250 | -   | ns   | 1                           |

|                               | Clock high pulse                             | 1.8 V or above | t <sub>HC</sub>    | 100 | -   | ns   |                             |

|                               | width                                        | 1.6 V or above |                    | 200 | -   |      | _                           |

|                               | Clock low pulse                              | 1.8 V or above | t <sub>LC</sub>    | 100 | -   | ns   |                             |

|                               | width                                        | 1.6 V or above |                    | 200 | -   |      |                             |

|                               | Clock rise time                              | 1              | t <sub>RC</sub>    | -   | 25  | ns   |                             |

|                               | Data delay                                   | 2.7 V or above | t <sub>DTR</sub>   | -   | 65  | ns   | Figure 2.61,<br>Figure 2.62 |

|                               |                                              | 1.8 V or above |                    | -   | 105 |      |                             |

|                               |                                              | 1.6 V or above |                    | -   | 140 |      |                             |

|                               | Set-up time                                  | 2.7 V or above | t <sub>SR</sub>    | 65  | -   | ns   |                             |

|                               |                                              | 1.8 V or above |                    | 90  | -   |      |                             |

|                               |                                              | 1.6 V or above |                    | 140 | -   |      |                             |

| SSI <sup>*</sup> dela<br>SSII | Hold time                                    | Hold time      |                    | 40  | -   | ns   | 1                           |

|                               | SSITXD0 output                               | 1.8 V or above | T <sub>DTRW</sub>  | -   | 105 | ns   | Figure 2.63                 |

|                               | delay from<br>SSILRCK0/SSIFS0<br>change time | 1.6 V or above |                    | -   | 140 |      |                             |

Figure 2.60 SSIE clock input/output timing

Table 2.43 A/D conversion characteristics (2) in high-speed A/D conversion mode (2 of 2)

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VREFH0 = 2.7 to 5.5 V Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter                                             |                                                   | Min      | Тур      | Max   | Unit | Test conditions                                                       |

|-------------------------------------------------------|---------------------------------------------------|----------|----------|-------|------|-----------------------------------------------------------------------|

| 14-bit mode                                           |                                                   | <u>.</u> | <u> </u> | 1     | •    |                                                                       |

| Resolution                                            |                                                   | -        | -        | 14    | Bit  | -                                                                     |

| Conversion time*1<br>(Operation at<br>PCLKC = 48 MHz) | Permissible signal source impedance Max. = 0.3 kΩ | 1.06     | -        | -     | μѕ   | High-precision channel ADCSR.ADHSC = 0 ADSSTRn.SST[7:0] = 0Dh         |

|                                                       |                                                   | 1.63     | -        | -     | μѕ   | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                          |                                                   | -        | ±2.0     | ±18   | LSB  | High-precision channel                                                |

|                                                       |                                                   |          |          | ±24.0 | LSB  | Other than above                                                      |

| Full-scale error                                      |                                                   | -        | ±3.0     | ±18   | LSB  | High-precision channel                                                |

|                                                       |                                                   |          |          | ±24.0 | LSB  | Other than above                                                      |

| Quantization error                                    |                                                   | -        | ±0.5     | -     | LSB  | -                                                                     |

| Absolute accuracy                                     | Absolute accuracy                                 |          | ±5.0     | ±20   | LSB  | High-precision channel                                                |

|                                                       |                                                   |          |          | ±32.0 | LSB  | Other than above                                                      |

| DNL differential nonlinearity error                   |                                                   | -        | ±4.0     | -     | LSB  | -                                                                     |

| INL integral nonlinear                                | ity error                                         | -        | ±4.0     | ±12.0 | LSB  | -                                                                     |

Note: The characteristics apply when no pin functions other than 14-bit A/D converter input are used. Absolute accuracy does not include quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. The number of sampling states is indicated for the test conditions.

Note 2. Except for I/O input capacitance ( $C_{in}$ ), see section 2.2.4, I/O  $V_{OH}$ ,  $V_{OL}$ , and Other Characteristics.

Table 2.44 A/D conversion characteristics (3) in high-speed A/D conversion mode (1 of 2)

Conditions: VCC = AVCC0 = 2.4 to 5.5 V, VREFH0 = 2.4 to 5.5 V Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter                     |                                                   |    | Min  | Тур   | Max                  | Unit | Test conditions                                                       |  |

|-------------------------------|---------------------------------------------------|----|------|-------|----------------------|------|-----------------------------------------------------------------------|--|

| Frequency                     |                                                   |    | 1    | -     | 32                   | MHz  | -                                                                     |  |

| Analog input capacitance*2 Cs |                                                   | s  | -    | -     | 8 (reference data)   | pF   | High-precision channel                                                |  |

|                               |                                                   |    | -    | -     | 9 (reference data)   | pF   | Normal-precision channel                                              |  |

| Analog input resistand        | ce R                                              | ls | -    | -     | 2.5 (reference data) | kΩ   | High-precision channel                                                |  |

|                               |                                                   |    | -    | -     | 6.7 (reference data) | kΩ   | Normal-precision channel                                              |  |

| Analog input voltage r        | Analog input voltage range Ain                    |    | 0    | -     | VREFH0               | V    | -                                                                     |  |

| 12-bit mode                   | •                                                 |    | •    | •     | •                    |      | •                                                                     |  |

| Resolution                    |                                                   |    | -    | -     | 12                   | Bit  | -                                                                     |  |

| (Operation at                 | Permissible signal source impedance Max. = 1.3 kΩ |    | 1.41 | -     | -                    | μs   | High-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 0Dh   |  |

|                               |                                                   |    | 2.25 | -     | -                    | μs   | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |  |

| Offset error                  |                                                   |    | -    | ±0.5  | ±4.5                 | LSB  | High-precision channel                                                |  |

|                               |                                                   |    |      |       | ±6.0                 | LSB  | Other than above                                                      |  |

| Full-scale error              |                                                   |    | -    | ±0.75 | ±4.5                 | LSB  | High-precision channel                                                |  |

|                               |                                                   |    |      |       | ±6.0                 | LSB  | Other than above                                                      |  |

| Quantization error            |                                                   |    | -    | ±0.5  | -                    | LSB  | -                                                                     |  |

| Absolute accuracy             |                                                   |    | -    | ±1.25 | ±5.0                 | LSB  | High-precision channel                                                |  |

|                               |                                                   |    |      |       | ±8.0                 | LSB  | Other than above                                                      |  |

Table 2.48 A/D conversion characteristics (7) in low power A/D conversion mode (2 of 2) Conditions: VCC = AVCC0 = 1.6 to 5.5 V (AVCC0 = VCC when VCC < 2.0 V), VREFH0 = 1.6 to 5.5 V

Reference voltage range applied to the VREFH0 and VREFL0.

| Parameter                                            |                                          | Min   | Тур   | Max   | Unit | Test conditions                                                       |

|------------------------------------------------------|------------------------------------------|-------|-------|-------|------|-----------------------------------------------------------------------|

| Conversion time*1<br>(Operation at<br>PCLKC = 4 MHz) | Permissible signal source impedance Max. | 13.5  | -     | -     | μs   | High-precision channel<br>ADCSR.ADHSC = 1<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                      | = 9.9 kΩ                                 | 20.25 | -     | -     | μs   | Normal-precision channel<br>ADCSR.ADHSC = 1<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                         |                                          | -     | ±1.0  | ±7.5  | LSB  | High-precision channel                                                |

|                                                      |                                          |       |       | ±10.0 | LSB  | Other than above                                                      |

| Full-scale error                                     |                                          | -     | ±1.5  | ±7.5  | LSB  | High-precision channel                                                |

|                                                      |                                          |       |       | ±10.0 | LSB  | Other than above                                                      |

| Quantization error                                   |                                          | -     | ±0.5  | -     | LSB  | -                                                                     |

| Absolute accuracy                                    |                                          | -     | ±3.0  | ±8.0  | LSB  | High-precision channel                                                |

|                                                      |                                          |       |       | ±12.0 | LSB  | Other than above                                                      |

| DNL differential nor                                 | ONL differential nonlinearity error      |       | ±1.0  | -     | LSB  | -                                                                     |

| INL integral nonlinearity error                      |                                          | -     | ±1.0  | ±3.0  | LSB  | -                                                                     |

| 14-bit mode                                          |                                          | •     | •     | •     |      | -                                                                     |

| Resolution                                           |                                          | -     | -     | 14    | Bit  | -                                                                     |

| Conversion time*1<br>(Operation at<br>PCLKC = 4 MHz) | Permissible signal source impedance Max. | 15.0  | -     | -     | μs   | High-precision channel<br>ADCSR.ADHSC = 1<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                      | = 9.9 kΩ                                 | 21.75 | -     | -     | μs   | Normal-precision channel<br>ADCSR.ADHSC = 1<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                         | -                                        |       | ±4.0  | ±30.0 | LSB  | High-precision channel                                                |

|                                                      |                                          |       |       | ±40.0 | LSB  | Other than above                                                      |

| Full-scale error                                     |                                          | -     | ±6.0  | ±30.0 | LSB  | High-precision channel                                                |

|                                                      |                                          |       |       | ±40.0 | LSB  | Other than above                                                      |

| Quantization error                                   |                                          | -     | ±0.5  | -     | LSB  | -                                                                     |

| Absolute accuracy                                    |                                          | -     | ±12.0 | ±32.0 | LSB  | High-precision channel                                                |

|                                                      |                                          |       |       | ±48.0 | LSB  | Other than above                                                      |

| DNL differential nor                                 | linearity error                          | -     | ±4.0  | -     | LSB  | -                                                                     |

| INL integral nonline                                 | arity error                              | -     | ±4.0  | ±12.0 | LSB  | -                                                                     |

Note: The characteristics apply when no pin functions other than 14-bit A/D converter input are used. Absolute accuracy does not include quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. The number of sampling states is indicated for the test conditions.

Note 2. Except for I/O input capacitance ( $C_{in}$ ), see section 2.2.4, I/O  $V_{OH}$ ,  $V_{OL}$ , and Other Characteristics.

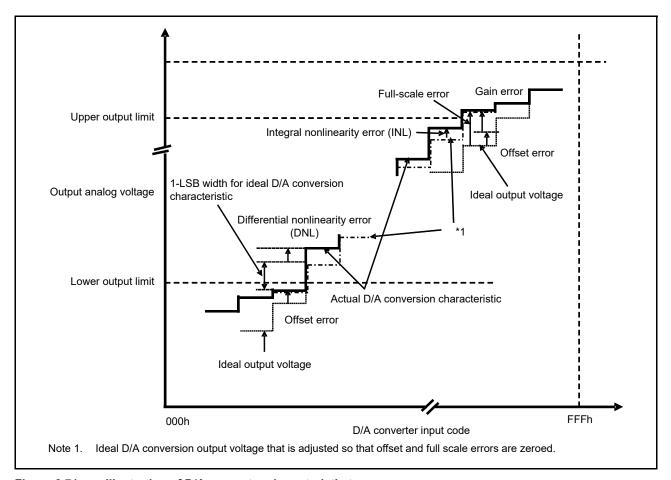

Figure 2.71 Illustration of D/A converter characteristic terms

# Integral nonlinearity error (INL)

Integral nonlinearity error is the maximum deviation between the ideal output voltage based on the ideal conversion characteristic when the measured offset and full-scale errors are zeroed, and the actual output voltage.

### Differential nonlinearity error (DNL)

Differential nonlinearity error is the difference between 1-LSB voltage width based on the ideal D/A conversion characteristics and the width of the actual output voltage.

### Offset error

Offset error is the difference between the highest actual output voltage that falls below the lower output limit and the ideal output voltage based on the input code.

#### Full-scale error

Full-scale error is the difference between the lowest actual output voltage that exceeds the upper output limit and the ideal output voltage based on the input code.

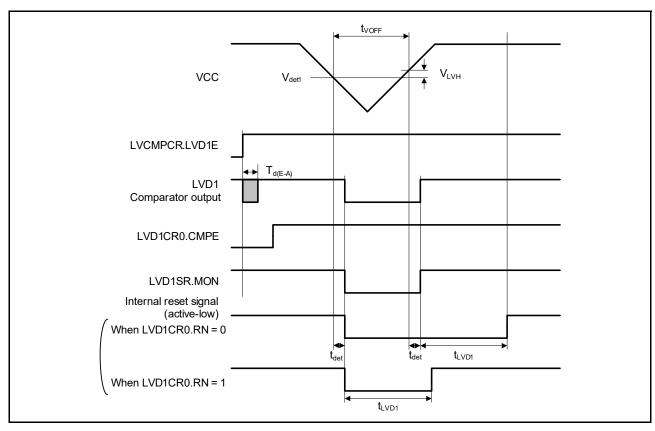

Figure 2.76 Voltage detection circuit timing (V<sub>det1</sub>)

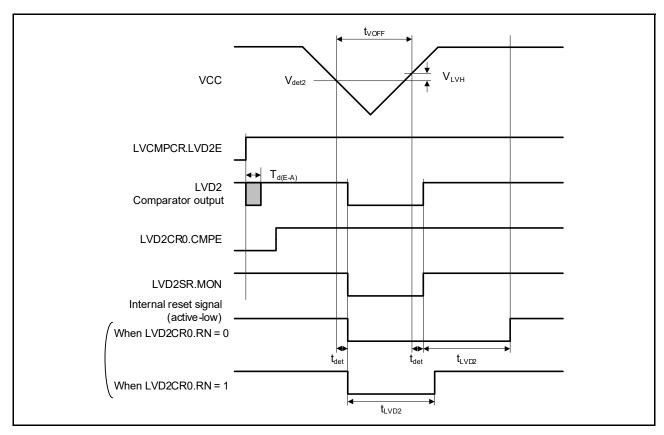

Figure 2.77 Voltage detection circuit timing (V<sub>det2</sub>)

# 2.12 Segment LCD Controller Characteristics

## 2.12.1 Resistance Division Method

[Static Display Mode]

Table 2.61 Resistance division method LCD characteristics (1)

Conditions: VL4 ≤ VCC ≤ 5.5 V

| Parameter         | Symbol   | Min | Тур | Max | Unit | Test conditions |

|-------------------|----------|-----|-----|-----|------|-----------------|

| LCD drive voltage | $V_{L4}$ | 2.0 | -   | VCC | V    | -               |

[1/2 Bias Method, 1/4 Bias Method]

## Table 2.62 Resistance division method LCD characteristics (2)

Conditions: VL4 ≤ VCC ≤ 5.5 V

| Parameter         | Symbol   | Min | Тур | Max | Unit | Test conditions |

|-------------------|----------|-----|-----|-----|------|-----------------|

| LCD drive voltage | $V_{L4}$ | 2.7 | -   | VCC | V    | -               |

[1/3 Bias Method]

#### Table 2.63 Resistance division method LCD characteristics (3)

Conditions: VL4 ≤ VCC ≤ 5.5 V

| Parameter         | Symbol   | Min | Тур | Max | Unit | Test conditions |

|-------------------|----------|-----|-----|-----|------|-----------------|

| LCD drive voltage | $V_{L4}$ | 2.5 | -   | VCC | V    | -               |

# 2.12.2 Internal Voltage Boosting Method

[1/3 Bias Method]

Table 2.64 Internal voltage boosting method LCD characteristics

Conditions: VCC = 1.8 V to 5.5 V

| Parameter                            | Symbol            | Conditions                |            | Min                        | Тур                 | Max                 | Unit | Test conditions |

|--------------------------------------|-------------------|---------------------------|------------|----------------------------|---------------------|---------------------|------|-----------------|

| LCD output voltage                   | V <sub>L1</sub>   | C1 to C4*1 = 0.47 µF      | VLCD = 04h | 0.90                       | 1.0                 | 1.08                | V    | -               |

| variation range                      |                   |                           | VLCD = 05h | 0.95                       | 1.05                | 1.13                | V    | -               |

|                                      |                   |                           | VLCD = 06h | 1.00                       | 1.10                | 1.18                | V    | -               |

|                                      |                   |                           | VLCD = 07h | 1.05                       | 1.15                | 1.23                | V    | -               |

|                                      |                   |                           | VLCD = 08h | 1.10                       | 1.20                | 1.28                | V    | -               |

|                                      |                   |                           | VLCD = 09h | 1.15                       | 1.25                | 1.33                | V    | -               |

|                                      |                   |                           | VLCD = 0Ah | 1.20                       | 1.30                | 1.38                | V    | -               |

|                                      |                   |                           | VLCD = 0Bh | 1.25                       | 1.35                | 1.43                | V    | -               |

|                                      |                   |                           | VLCD = 0Ch | 1.30                       | 1.40                | 1.48                | V    | -               |

|                                      |                   |                           | VLCD = 0Dh | 1.35                       | 1.45                | 1.53                | V    | -               |

|                                      |                   |                           | VLCD = 0Eh | 1.40                       | 1.50                | 1.58                | V    | -               |

|                                      |                   |                           | VLCD = 0Fh | 1.45                       | 1.55                | 1.63                | V    | -               |

|                                      |                   |                           | VLCD = 10h | 1.50                       | 1.60                | 1.68                | V    | -               |

|                                      |                   |                           | VLCD = 11h | 1.55                       | 1.65                | 1.73                | V    | -               |

|                                      |                   |                           | VLCD = 12h | 1.60                       | 1.70                | 1.78                | V    | -               |

|                                      |                   |                           | VLCD = 13h | 1.65                       | 1.75                | 1.83                | V    | -               |

| Doubler output voltage               | $V_{L2}$          | C1 to C4*1 = 0.47 $\mu$ F |            | 2 × V <sub>L1</sub> - 0.1  | 2 × V <sub>L1</sub> | 2 × V <sub>L1</sub> | V    | -               |

| Tripler output voltage               | $V_{L4}$          | C1 to C4*1 = 0.47 µF      |            | 3 × V <sub>L1</sub> - 0.15 | 3 × V <sub>L1</sub> | 3 × V <sub>L1</sub> | V    | -               |

| Reference voltage setup time*2       | t <sub>VL1S</sub> |                           |            | 5                          | -                   | -                   | ms   | Figure 2.81     |

| LCD output voltage variation range*3 | t <sub>VLWT</sub> | C1 to C4*1 = 0.47 µF      |            | 500                        | •                   | -                   | ms   |                 |

Note 1. This is a capacitor that is connected between voltage pins used to drive the LCD.

Table 2.74 Data flash characteristics (3)

Middle-speed operating mode

Conditions: VCC = 1.8 to 5.5 V,  $T_a = -40$  to +85°C

|                               |           |                    |     | FCLK = 4 MHz |      |     | FCLK = 8 MHz |      |      |  |

|-------------------------------|-----------|--------------------|-----|--------------|------|-----|--------------|------|------|--|

| Parameter                     |           | Symbol             | Min | Тур          | Max  | Min | Тур          | Max  | Unit |  |

| Programming time              | 1-byte    | t <sub>DP1</sub>   | -   | 94.7         | 886  | -   | 89.3         | 849  | μs   |  |

| Erasure time                  | 1-KB      | t <sub>DE1K</sub>  | -   | 9.59         | 299  | -   | 8.29         | 273  | ms   |  |

| Blank check time              | 1-byte    | t <sub>DBC1</sub>  | -   | -            | 56.2 | -   | -            | 52.5 | μs   |  |

|                               | 1-KB      | t <sub>DBC1K</sub> | -   | -            | 2.17 | -   | -            | 1.51 | ms   |  |

| Suspended time during erasing |           | t <sub>DSED</sub>  | -   | -            | 23.0 | -   | -            | 21.7 | μs   |  |

| Data flash STOP recov         | very time | t <sub>DSTOP</sub> | 720 | -            | -    | 720 | -            | -    | ns   |  |

Note: Does not include the time until each operation of the flash memory is started after instructions are executed by software.

Note: The lower-limit frequency of FCLK is 1 MHz during programming or erasing the flash memory. When using FCLK at below

4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note: The frequency accuracy of FCLK must be ±3.5%. Confirm the frequency accuracy of the clock source.

# 2.16 Boundary Scan

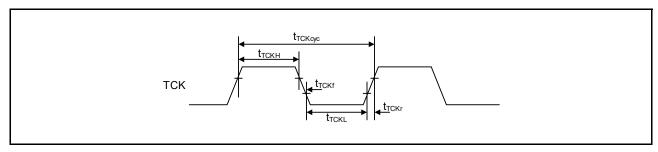

Table 2.75 Boundary scan

Conditions: VCC = AVCC0 = 2.4 to 5.5 V

| Parameter                             | Symbol              | Min                | Тур | Max | Unit | Test conditions |

|---------------------------------------|---------------------|--------------------|-----|-----|------|-----------------|

| TCK clock cycle time                  | t <sub>TCKcyc</sub> | 100                | -   | -   | ns   | Figure 2.82     |

| TCK clock high pulse width            | t <sub>TCKH</sub>   | 45                 | -   | -   | ns   |                 |

| TCK clock low pulse width             | t <sub>TCKL</sub>   | 45                 | -   | -   | ns   |                 |

| TCK clock rise time                   | t <sub>TCKr</sub>   | -                  | -   | 5   | ns   |                 |

| TCK clock fall time                   | t <sub>TCKf</sub>   | -                  | -   | 5   | ns   |                 |

| TMS setup time                        | t <sub>TMSS</sub>   | 20                 | -   | -   | ns   | Figure 2.83     |

| TMS hold time                         | t <sub>TMSH</sub>   | 20                 | -   | -   | ns   |                 |

| TDI setup time                        | t <sub>TDIS</sub>   | 20                 | -   | -   | ns   |                 |

| TDI hold time                         | t <sub>TDIH</sub>   | 20                 | -   | -   | ns   |                 |

| TDO data delay                        | t <sub>TDOD</sub>   | -                  | -   | 70  | ns   | 1               |

| Boundary Scan circuit start up time*1 | t <sub>BSSTUP</sub> | t <sub>RESWP</sub> | -   | -   | -    | Figure 2.84     |

Note 1. Boundary scan does not function until power-on-reset becomes negative.

Figure 2.82 Boundary scan TCK timing

S3A6 Microcontroller Group Datasheet

Publication Date: Rev.1.10 Jun 25, 2018

Published by: Renesas Electronics Corporation

#### **General Precautions**

#### 1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

#### 2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

#### 3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

#### 4. Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

#### 5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

#### 6. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

#### 7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

## 8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.