# E·XF Renesas Electronics America Inc - UPD78F0555MA-FAA-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | I <sup>2</sup> C, LINbus, UART/USART                                                 |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 9                                                                                    |

| Program Memory Size        | 4KB (4K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 384 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 4x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 16-SSOP (0.173", 4.40mm Width)                                                       |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0555ma-faa-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

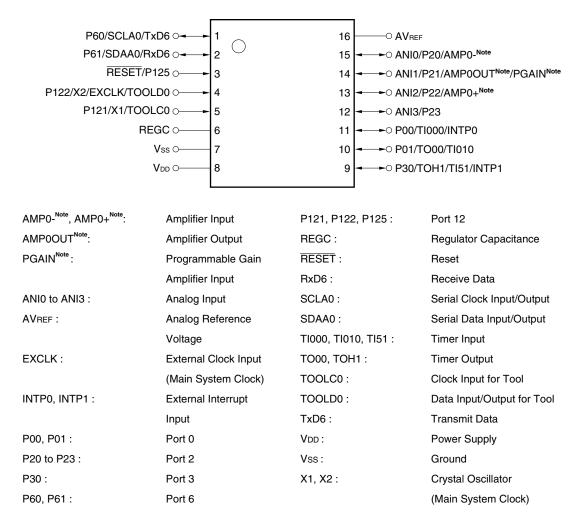

# 1.3 Pin Configuration (Top View)

# 1.3.1 78K0/KY2-L

• 16-pin plastic SSOP (5.72 mm (225))

Note µPD78F0555, 78F0556, 78F0557 (products with operational amplifier) only

- Cautions 1. Vss functions alternately as the ground potential of the A/D converter. Be sure to connect Vss to a stabilized GND (= 0 V).

- 2. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- 3. ANI0/P20/AMP0-, ANI1/P21/AMP0OUT/PGAIN, ANI2/P22/AMP0+, and ANI3/P23 are set in the analog input mode after release of reset.

- 4. RESET/P125 immediately after release of reset is set in the external reset input.

<R>

Figure 2-1. Pin I/O Circuit List (4/4)

| Function Name | I/O   | Function                                                                                                                                                                                                                                                                | After Reset  | Alternate Function                                      |

|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------|

| P00           | I/O   | Port 0.                                                                                                                                                                                                                                                                 | Input port   | TI000/INTP0                                             |

| P01           |       | 2-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                                                                                                       |              | TO00/TI010                                              |

| P20           | I/O   | Port 2.                                                                                                                                                                                                                                                                 | Analog input | ANI0/AMP0- <sup>Note</sup>                              |

| P21           |       | 4-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                                                                                                                        |              | ANI1/AMP0OUT <sup>Note</sup> /<br>PGAIN <sup>Note</sup> |

| P22           |       |                                                                                                                                                                                                                                                                         |              | ANI2/AMP0+ <sup>Note</sup>                              |

| P23           |       |                                                                                                                                                                                                                                                                         |              | ANI3                                                    |

| P30           | I/O   | Port 3.<br>1-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                                                                                            | Input port   | TOH1/TI51/INTP1                                         |

| P60           | I/O   | Port 6.<br>2-bit I/O port.                                                                                                                                                                                                                                              | Input port   | SCLA0/TxD6                                              |

| P61           |       | Input/output can be specified in 1-bit units.<br>Input can be set to SMBus input buffer in 1-bit units.<br>Output can be set to N-ch open-drain output (V <sub>DD</sub><br>tolerance).<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting. |              | SDAA0/RxD6                                              |

| P121          | Input | Port 12.                                                                                                                                                                                                                                                                | Input port   | X1/TOOLC0                                               |

| P122          |       | 3-bit input-only port.                                                                                                                                                                                                                                                  |              | X2/EXCLK/TOOLD0                                         |

| P125          |       | For only P125, use of an on-chip pull-up resistor can be specified by a software setting.                                                                                                                                                                               | Reset input  | RESET                                                   |

| Table 4-2. | <b>Port Functions</b> | (78K0/KY2-L) |

|------------|-----------------------|--------------|

|------------|-----------------------|--------------|

Note µPD78F0555, 78F0556, and 78F0557 (products with operational amplifier) only

#### Figure 4-48. Format of A/D Port Configuration Register 0, 1 (ADPC0, ADPC1) (2/2)

### (e) 78K0/KB2-L

| Address: FF                           | E2EH After      | reset: 00H                             | R/W                  |                  |                |                  |        |             |

|---------------------------------------|-----------------|----------------------------------------|----------------------|------------------|----------------|------------------|--------|-------------|

| Symbol                                | 7               | 6                                      | 5                    | 4                | 3              | 2                | 1      | 0           |

| ADPC0                                 | 0               | 0                                      | 0                    | 0                | ADPCS3         | ADPCS2           | ADPCS1 | ADPCS0      |

|                                       |                 |                                        |                      |                  |                |                  |        |             |

| Address: FF                           | F2FH After      | reset: 07H                             | R/W                  |                  |                |                  |        |             |

| Symbol                                | 7               | 6                                      | 5                    | 4                | 3              | 2                | 1      | 0           |

| ADPC1                                 | 0               | 0                                      | 0                    | 0                | 0              | ADPCS10          | ADPCS9 | ADPCS8      |

|                                       | 2-L (40-pin p   | -                                      |                      |                  |                |                  |        |             |

| Address: FF                           |                 | reset: 00H                             | R/W                  |                  |                |                  |        |             |

| Symbol                                | 7               | 6                                      | 5                    | 4                | 3              | 2                | 1      | 0           |

| ADPC0                                 | 0               | ADPCS6                                 | ADPCS5               | ADPCS4           | ADPCS3         | ADPCS2           | ADPCS1 | ADPCS0      |

| Address: FF<br>Symbol                 | F2FH After<br>7 | reset: 07H<br>6                        | R/W<br>5             | 4                | 3              | 2                | 1      | 0           |

| ADPC1                                 | 0               | 0                                      | 0                    | 0                | 0              | ADPCS10          | ADPCS9 | ADPCS8      |

| (g) 78K0/KC2<br>Address: FF<br>Symbol |                 | n <b>d 48-pin p</b><br>reset: 00H<br>6 | roducts)<br>R/W<br>5 | 4                | 3              | 2                | 1      | 0           |

| ADPC0                                 | ,<br>ADPCS7     | ADPCS6                                 | ADPCS5               | 4<br>ADPCS4      | ADPCS3         | ADPCS2           | ADPCS1 | 0<br>ADPCS0 |

| Address: FF<br>Symbol                 |                 | reset: 07H                             | R/W<br>5             | 4                | 3              | 2                | 1      | 0           |

| ADPC1                                 | 0               | 0                                      | 0                    | 4<br>0           | 0              | ADPCS10          | ADPCS9 | ADPCS8      |

| ADPUT                                 | 0               | 0                                      | 0                    | 0                | 0              | ADPCSTU          | ADPC59 | ADPC56      |

|                                       | ADPCSn          |                                        | Di                   | nital I/O ar and |                | tion (n Oto t    |        |             |

|                                       |                 | Angles I/O                             | Dię                  | ynai i/O or ana  | alog I/O selec | tion (n = 0 to 1 | 10)    |             |

|                                       | 0               | Analog I/O                             |                      |                  |                |                  |        |             |

|                                       | 1               | Digital I/O                            |                      |                  |                |                  |        |             |

- Cautions 1. Set the pin set to analog input to the input mode by using port mode register 1, 2, and 7 (PM1, PM2, and PM7).

- 2. If data is written to ADPC0 and ADPC1, a wait cycle is generated. Do not write data to ADPC0 and ADPC1 when the peripheral hardware clock is stopped. For details, refer to CHAPTER 31 CAUTIONS FOR WAIT.

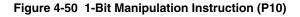

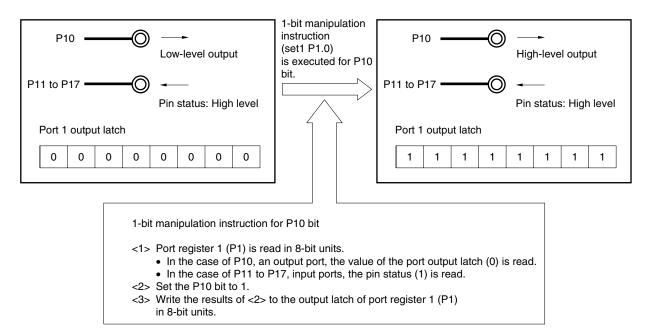

# 4.6 Cautions on 1-Bit Manipulation Instruction for Port Register n (Pn)

When a 1-bit manipulation instruction is executed on a port that provides both input and output functions, the output latch value of an input port that is not subject to manipulation may be written in addition to the targeted bit.

Therefore, it is recommended to rewrite the output latch when switching a port from input mode to output mode.

- <Example> When P10 is an output port, P11 to P17 are input ports (all pin statuses are high level), and the port latch value of port 1 is 00H, if the output of output port P10 is changed from low level to high level via a 1-bit manipulation instruction, the output latch value of port 1 is FFH.

- Explanation: The targets of writing to and reading from the Pn register of a port whose PMnm bit is 1 are the output latch and pin status, respectively.

- A 1-bit manipulation instruction is executed in the following order in the 78K0/Kx2-L microcontrollers.

- <1> The Pn register is read in 8-bit units.

- <2> The targeted one bit is manipulated.

- <3> The Pn register is written in 8-bit units.

In step <1>, the output latch value (0) of P10, which is an output port, is read, while the pin statuses of P11 to P17, which are input ports, are read. If the pin statuses of P11 to P17 are high level at this time, the read value is FEH.

The value is changed to FFH by the manipulation in <2>.

FFH is written to the output latch by the manipulation in <3>.

Remark The following instructions are 1-bit manipulation instructions.

• MOV1, AND1, OR1, XOR1, SET1, CLR1, NOT1

<2> Setting the high-speed system clock as the main system clock (MCM register) When XSEL and MCM0 are set to 1, the high-speed system clock is supplied as the main system clock and peripheral hardware clock.

| XSEL | MCM0 | Selection of Main System Clock and Clock Supplied to Peripheral Hardware |                               |  |  |  |

|------|------|--------------------------------------------------------------------------|-------------------------------|--|--|--|

|      |      | Main System Clock (fxp) Peripheral Hardware Clock (fprs)                 |                               |  |  |  |

| 1    | 1    | High-speed system clock (fxH)                                            | High-speed system clock (fxH) |  |  |  |

Caution If the high-speed system clock is selected as the main system clock, a clock other than the high-speed system clock cannot be set as the peripheral hardware clock.

<3> Setting the main system clock as the CPU clock and selecting the division ratio (PCC register) When CSS is cleared to 0, the main system clock is supplied to the CPU. To select the CPU clock division ratio, use PCC0, PCC1, and PCC2.

| CSS | PCC2             | PCC1 | PCC0 | CPU Clock (fcpu) Selection |

|-----|------------------|------|------|----------------------------|

| 0   | 0                | 0    | 0    | fxp                        |

|     | 0                | 0    | 1    | fxp/2 (default)            |

|     | 0                | 1    | 0    | fxp/2 <sup>2</sup>         |

|     | 0                | 1    | 1    | fxp/2 <sup>3</sup>         |

|     | 1                | 0    | 0    | fxp/2 <sup>4</sup>         |

|     | Other than above |      |      | Setting prohibited         |

#### (4) Example of setting procedure when stopping the high-speed system clock

The high-speed system clock can be stopped in the following two ways.

- Executing the STOP instruction and stopping the X1 oscillation (disabling clock input if the external clock is used)

- Setting MSTOP to 1 and stopping the X1 oscillation (disabling clock input if the external clock is used)

#### (a) To execute a STOP instruction

<1> Setting to stop peripheral hardware

Stop peripheral hardware that cannot be used in the STOP mode (for peripheral hardware that cannot be used in STOP mode, refer to **CHAPTER 19 STANDBY FUNCTION**).

- <2> Setting the X1 clock oscillation stabilization time after standby release When the CPU is operating on the X1 clock, set the value of the OSTS register before the STOP instruction is executed.

- <3> Executing the STOP instruction When the STOP instruction is executed, the system is placed in the STOP mode and X1 oscillation is stopped (the input of the external clock is disabled).

|         | Item                                | 78K0/KY2-L<br>(µPD78F055x)            |                                       | 78K0/KA2-L<br>(µPD78F056x) |                                                                           | 78K0/KB2-L<br>(μPD78F057x)            | 78K0/KC2-L<br>(μPD78F058x)            |

|---------|-------------------------------------|---------------------------------------|---------------------------------------|----------------------------|---------------------------------------------------------------------------|---------------------------------------|---------------------------------------|

| <r></r> |                                     | 16 Pins                               | 20 Pins                               | 25 Pins                    | 32 Pins                                                                   | 30 Pins                               | 40, 44, 48 Pins                       |

|         | 16-bit<br>timer/event<br>counter 00 | $\checkmark$                          | $\checkmark$                          | $\checkmark$               | $\checkmark$                                                              | $\checkmark$                          | $\checkmark$                          |

|         | Timer I/O pin                       | input: 1, output: 1<br>or<br>input: 2 | input: 1, output: 1<br>or<br>input: 2 | input: 1,<br>output: none  | input: 1<br>or<br>output 1<br>or<br>input: 2<br>or<br>input: 1, output: 1 | input: 1, output: 1<br>or<br>input: 2 | input: 1, output: 1<br>or<br>input: 2 |

# CHAPTER 6 16-BIT TIMER/EVENT COUNTER 00

#### **Remark** $\sqrt{:}$ Mounted, -: Not mounted

#### 6.1 Functions of 16-Bit Timer/Event Counter 00

16-bit timer/event counter 00 is mounted onto all 78K0/Kx2-L microcontroller products. 16-bit timer/event counter 00 has the following functions.

#### (1) Interval timer

16-bit timer/event counter 00 generates an interrupt request at the preset time interval.

#### (2) Square-wave output

16-bit timer/event counter 00 can output a square wave with any selected frequency.

#### (3) External event counter

16-bit timer/event counter 00 can measure the number of pulses of an externally input signal.

#### (4) One-shot pulse output

16-bit timer event counter 00 can output a one-shot pulse whose output pulse width can be set freely.

#### (5) PPG output

16-bit timer/event counter 00 can output a rectangular wave whose frequency and output pulse width can be set freely.

#### (6) Pulse width measurement

16-bit timer/event counter 00 can measure the pulse width of an externally input signal.

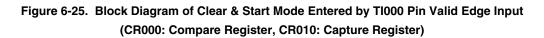

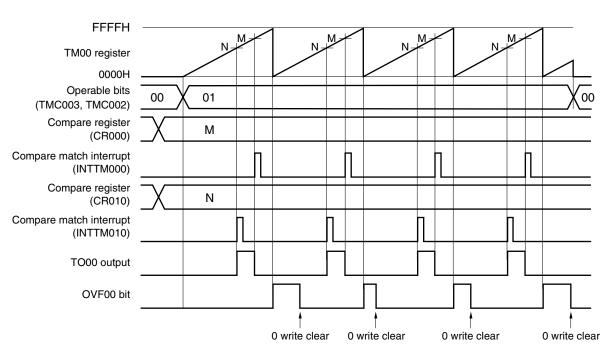

# (2) Operation in clear & start mode entered by TI000 pin valid edge input (CR000: compare register, CR010: capture register)

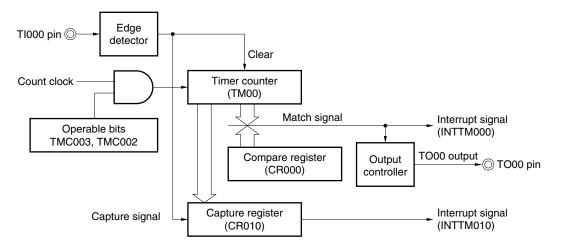

# Figure 6-26. Timing Example of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Compare Register, CR010: Capture Register) (1/2)

(a) TOC00 = 13H, PRM00 = 10H, CRC00 = 04H, TMC00 = 08H, CR000 = 0001H

This is an application example where the TO00 output level is inverted when the count value has been captured & cleared.

The count value is captured to CR010 and TM00 is cleared (to 0000H) when the valid edge of the Tl000 pin is detected. When the count value of TM00 is 0001H, a compare match interrupt signal (INTTM000) is generated, and the TO00 output level is inverted.

# Figure 6-34. Timing Example of Free-Running Timer Mode (CR000: Compare Register, CR010: Compare Register)

• TOC00 = 13H, PRM00 = 00H, CRC00 = 00H, TMC00 = 04H

This is an application example where two compare registers are used in the free-running timer mode. The TO00 output level is reversed each time the count value of TM00 matches the set value of CR000 or CR010. When the count value matches the register value, the INTTM000 or INTTM010 signal is generated.

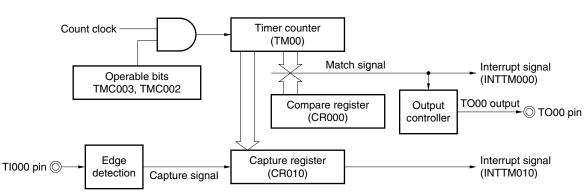

# (2) Free-running timer mode operation

(CR000: compare register, CR010: capture register)

# Figure 6-35. Block Diagram of Free-Running Timer Mode (CR000: Compare Register, CR010: Capture Register)

#### Figure 7-10. Format of 8-Bit Timer Mode Control Register 51 (TMC51) (2/2)

#### (b) 78K0/KB2-L, 78K0/KC2-L

0

Count operation start

| Address: FF | 43H After | reset: 00H    | R/W <sup>Note</sup>                                             |   |       |       |        |       |

|-------------|-----------|---------------|-----------------------------------------------------------------|---|-------|-------|--------|-------|

| Symbol      | <7>       | 6             | 5                                                               | 4 | <3>   | <2>   | 1      | <0>   |

| TMC51       | TCE51     | TMC516        | 0                                                               | 0 | LVS51 | LVR51 | TMC511 | TOE51 |

|             |           |               |                                                                 |   |       |       |        |       |

|             | TCE51     |               | TM51 count operation control                                    |   |       |       |        |       |

|             | 0         | After clearin | After clearing to 0, count operation disabled (counter stopped) |   |       |       |        |       |

| TMC516 | TM51 operating mode selection                                       |

|--------|---------------------------------------------------------------------|

| 0      | Mode in which clear & start occurs on a match between TM51 and CR51 |

| 1      | PWM (free-running) mode                                             |

| LVS51 | LVR51 | Timer output F/F status setting                                |

|-------|-------|----------------------------------------------------------------|

| 0     | 0     | No change                                                      |

| 0     | 1     | Timer output F/F clear (0) (default value of TO51 output: low) |

| 1     | 0     | Timer output F/F set (1) (default value of TO51 output: high)  |

| 1     | 1     | Setting prohibited                                             |

| TMC511 | In other modes (TMC516 = 0)  | In PWM mode (TMC516 = 1) |

|--------|------------------------------|--------------------------|

|        | Timer F/F control            | Active level selection   |

| 0      | Inversion operation disabled | Active-high              |

| 1      | Inversion operation enabled  | Active-low               |

| TOE51 | Timer output control                       |

|-------|--------------------------------------------|

| 0     | Output disabled (TO51 output is low level) |

| 1     | Output enabled                             |

Note Bits 2 and 3 are write-only.

# Cautions 1. The settings of LVS51 and LVR51 are valid in other than PWM mode.

- 2. Perform <1> to <4> below in the following order, not at the same time.

- <1> Set TMC511, TMC516: Operation mode setting

- <2> Set TOE51 to enable output: To enable out

- Timer output enable

- <3> Set LVS51, LVR51 (refer to Caution 1): Timer F/F setting <4> Set TCE51

- 3. When TCE51 = 1, setting the other bits of TMC51 is prohibited.

- 4. The actual TO51/TI51/P33/INTP4 pin output is determined depending on PM33 and P33 besides TO51 output.

**Remarks 1.** In PWM mode, PWM output is made inactive by clearing TCE51 to 0.

- 2. If LVS51 and LVR51 are read, the value is 0.

- **3.** The values of the TMC516, LVS51, LVR51, TMC511, and TOE51 bits are reflected at the TO51 output regardless of the value of TCE51.

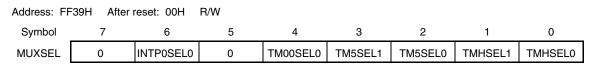

## <R>(3) Port alternate switch control register (MUXSEL) (78K0/KA2-L (25-pin) only)

MUXSEL of 78K0/KA2-L (25-pin products) assigns TOH1, TI51, TI000, and INTP0 pins. By default, INTP0 and TI000 are assigned to P00, while TI51 and TOH1 have no assignment setting.

This register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears MUXSEL to 00H.

#### Figure 7-11. Format of Port Alternate Switch Control Register (MUXSEL)

| TM5SEL1 | TM5SEL0 | 8-bit timer 51 input (TI51) pin function assignment   |

|---------|---------|-------------------------------------------------------|

| 0       | 0       | No TI51 function assignment.                          |

| 0       | 1       | Assign TI51 to the P34 pin as the alternate function. |

| 1       | 0       | Assign TI51 to the P00 pin as the alternate function. |

| 1       | 1       | Setting prohibited                                    |

#### <R>(4) Port mode registers 0, 1, 3 (PM0, PM1, PM3)

These registers set port 0, 1, and 3 input/output in 1-bit units. PM0, PM1, and PM3 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

• 78K0/KY2-L, 78K0/KA2-L (20-pin products)

When using the P30/TI51/TOH1/INTP1 pin for timer input, set PM30 to 1. The output latches of P30 at this time may be 0 or 1.

• 78K0/KA2-L (25-pin products)

When using the P34/TI51/TOH1/INTP4 pin for timer input, set PM34 to 1. The output latches of P34 at this time may be 0 or 1.

When using the P00/TI51/TOH1/INTP0/TI000 pin for timer input, set PM00 to 1. The output latches of P00 at this time may be 0 or 1.

• 78K0/KB2-L, 78K0/KC2-L

When using the P17/TO50/TI50 and P33/TO51/TI51/INTP4 pins for timer output, clear PM17 and PM33 and the output latches of P17 and P33 to 0.

When using the P17/TO50/TI50 and P33/TO51/TI51/INTP4 pins for timer input, set PM17 and PM33 to 1. The output latches of P17 and P33 at this time may be 0 or 1.

The peripheral functions used in the LIN communication operation are shown below.

<Peripheral functions used>

- External interrupt (INTP0); wakeup signal detection

Use: Detects the wakeup signal edges and detects start of communication.

- 16-bit timer/event counter 00 (TI000); baud rate error detection

- Use: Detects the baud rate error (measures the TI000 input edge interval in the capture mode) by detecting the sync field (SF) length and divides it by the number of bits.

- Serial interface UART6

# 14.2 Configuration of Serial Interface UART6

Serial interface UART6 includes the following hardware.

| Item                     | Configuration                                                                                                                              |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Registers                | Receive buffer register 6 (RXB6)<br>Receive shift register 6 (RXS6)                                                                        |

|                          | Transmit buffer register 6 (TXB6)<br>Transmit shift register 6 (TXS6)                                                                      |

| Construct we adjust a we |                                                                                                                                            |

| Control registers        | Asynchronous serial interface operation mode register 6 (ASIM6)<br>Asynchronous serial interface reception error status register 6 (ASIS6) |

|                          | Asynchronous serial interface transmission status register 6 (ASIF6)                                                                       |

|                          | Clock selection register 6 (CKSR6)                                                                                                         |

|                          | Baud rate generator control register 6 (BRGC6)                                                                                             |

|                          | Asynchronous serial interface control register 6 (ASICL6)                                                                                  |

|                          | Input switch control register (ISC)                                                                                                        |

|                          | Port mode register 1 (PM1), port mode register 6 (PM6) <sup>Note 1</sup>                                                                   |

|                          | Port register 1 (P1), port register 6 (P6) <sup>Note 1</sup>                                                                               |

|                          | Port output mode register 6 (POM6) Note 2                                                                                                  |

# Table 14-1. Configuration of Serial Interface UART6

Notes 1. 78K0/KY2-L, 78K0/KA2-L: Port mode register 6 (PM6), port register 6 (P6) 78K0/KB2-L, 78K0/KC2-L: Port mode register 1 (PM1), port register 1 (P1)

2. In the 78K0/KY2-L and 78K0/KA2-L, this register is used when using serial interface UART6.

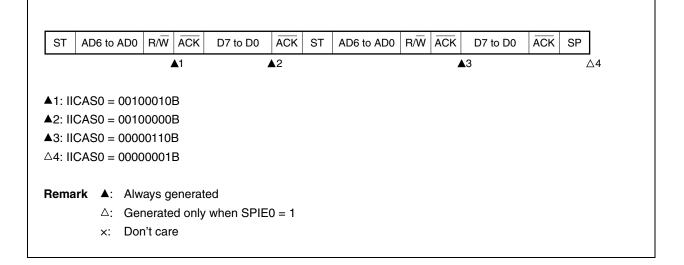

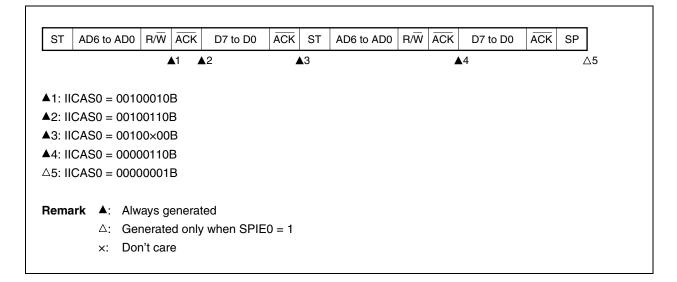

#### (d) Start ~ Code ~ Data ~ Start ~ Address ~ Data ~ Stop

#### (i) When WTIM0 = 0 (after restart, does not match address (= not extension code))

#### (ii) When WTIM0 = 1 (after restart, does not match address (= not extension code))

# 16.2 Configuration of Serial Interfaces CSI10 and CSI11

Serial interfaces CSI10 and CSI11 include the following hardware.

| Table 16-1. Configuration of Serial Interfaces CSI10 and CSI11 |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

| Item              | Configuration                                                                                                                                                                                      |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Controller        | Transmit controller<br>Clock start/stop controller & clock phase controller                                                                                                                        |  |

| Registers         | Transmit buffer register 1n (SOTB1n)<br>Serial I/O shift register 1n (SIO1n)                                                                                                                       |  |

| Control registers | Serial operation mode register 1n (CSIM1n)<br>Serial clock selection register 1n (CSIC1n)<br>Port alternate switch control register (MUXSEL)<br>Port mode register x (PMx)<br>Port register x (Px) |  |

Remark78K0/KA2-L (25 pins, 32 pins):n = 1, x = 0, 378K0/KB2-L:n = 0, x = 178K0/KC2-L:n = 0, 1, x = 1, 4, 6, 12

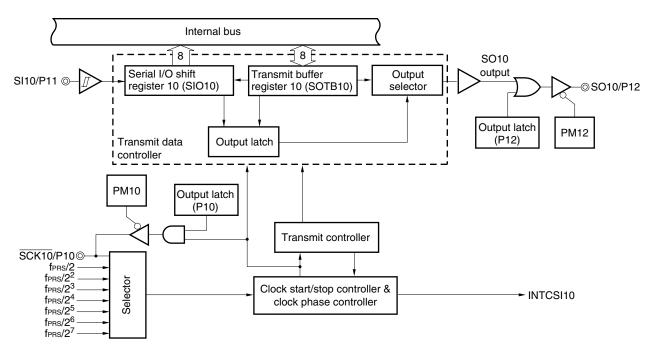

#### Figure 16-1. Block Diagram of Serial Interface CSI10 (78K0/KB2-L and 78K0/KC2-L)

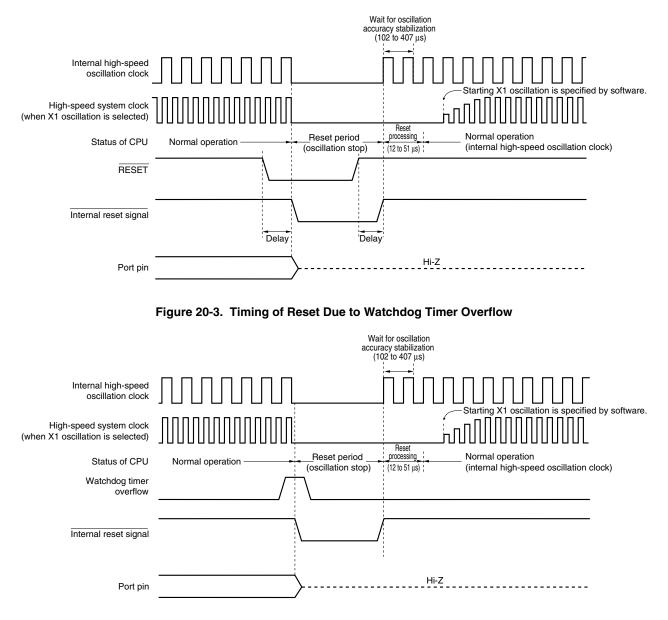

Figure 20-2. Timing of Reset by RESET Input

Caution A watchdog timer internal reset resets the watchdog timer.

|                      | Hardware                                                                      | Status After Reset<br>Acknowledgment <sup>Note 1</sup> |

|----------------------|-------------------------------------------------------------------------------|--------------------------------------------------------|

| Reset function       | Reset control flag register (RESF)                                            | 00H <sup>Note 2</sup>                                  |

| Low-voltage detector | Low-voltage detection register (LVIM)                                         | 00H <sup>Note 2</sup>                                  |

|                      | Low-voltage detection level selection register (LVIS)                         | 00H <sup>Note 2</sup>                                  |

| Interrupt            | Request flag registers 0L, 0H, 1L, 1H (IF0L, IF0H, IF1L, IF1H)                | 00H                                                    |

|                      | Mask flag registers 0L, 0H, 1L, 1H (MK0L, MK0H, MK1L, MK1H)                   | FFH                                                    |

|                      | Priority specification flag registers 0L, 0H, 1L, 1H (PR0L, PR0H, PR1L, PR1H) | FFH                                                    |

|                      | External interrupt rising edge enable registers 0, 1 (EGPCTL0, EGPCTL1)       | 00H                                                    |

|                      | External interrupt falling edge enable registers 0, 1 (EGNCTL0, EGNCTL1)      | 00H                                                    |

| Regulator            | Regulator mode control register (RMC)                                         | 00H                                                    |

| Table 20-2. | . Hardware Statuses | s After Reset Acknowle | dgment (4/4) |

|-------------|---------------------|------------------------|--------------|

|-------------|---------------------|------------------------|--------------|

**Notes 1.** During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware statuses become undefined. All other hardware statuses remain unchanged after reset.

2. These values vary depending on the reset source.

<R>

|          | Reset Source | RESET Input   | Reset by POC  | Reset by WDT  | Reset by LVI                      | Reset by LVI              |

|----------|--------------|---------------|---------------|---------------|-----------------------------------|---------------------------|

| Register |              |               |               |               | (Except Reset                     | Default Start<br>Function |

|          |              |               |               |               | by LVI Default<br>Start Function) | FUNCTION                  |

| RESF     | WDTRF flag   | Cleared (0)   | Cleared (0)   | Set (1)       | Held                              | Cleared (0)               |

|          | LVIRF flag   |               |               | Held          | Set (1)                           |                           |

| LVIM     |              | Cleared (00H) | Cleared (00H) | Cleared (00H) | Held                              | Cleared (00H)             |

| LVIS     |              |               |               |               |                                   |                           |

Remark The special function registers (SFRs) mounted depend on the product. Refer to 3.2.3 Special function registers (SFRs).

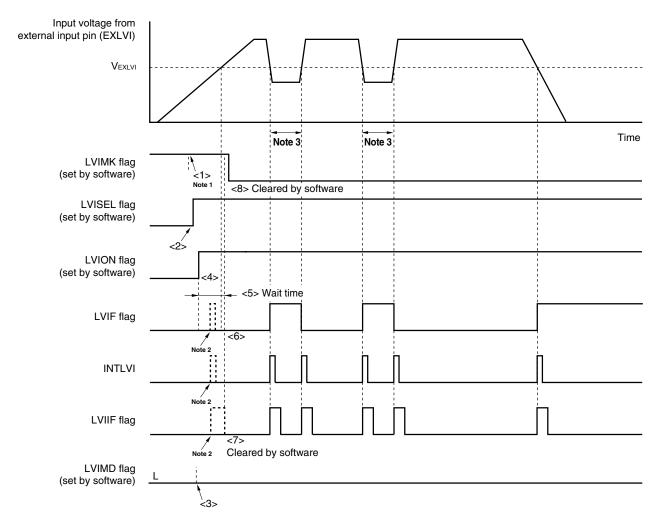

# Figure 22-10. Timing of Low-Voltage Detector Interrupt Signal Generation (Bit: LVISEL = 1)

- Notes 1. The LVIMK flag is set to "1" by reset signal generation.

- 2. The interrupt request signal (INTLVI) is generated and the LVIF and LVIIF flags may be set (1).

- If LVI operation is disabled when the input voltage of external input pin (EXLVI) is less than or equal to the detection voltage (VEXLVI), an interrupt request signal (INTLVI) is generated and LVIIF may be set to 1.

- Remark <1> to <8> in Figure 22-10 above correspond to <1> to <8> in the description of "When starting operation" in 22.4.2 (2) When detecting level of input voltage from external input pin (EXLVI).

#### Table 25-9. Processing Time for Each Command When PG-FP5 Is Used (Reference) (2/3)

(1) 78K0/KY2-L, 78K0/KA2-L (2/2)

#### (c) Products with internal ROMs of the 16 KB: μPD78F0552, 78F0557, 78F0562, 78F0567

| Command of PG-FP5 | Port: UART-Internal-OSC (Internal high-speed oscillation clock (fii: 8 MHz (typ.)),<br>Speed: 500,000 bps |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------|--|--|

|                   |                                                                                                           |  |  |

| Signature         | 0.5 s (typ.)                                                                                              |  |  |

| Blankcheck        | 0.5 s (typ.)                                                                                              |  |  |

| Erase             | 1 s (typ.)                                                                                                |  |  |

| Program           | 2.5 s (typ.)                                                                                              |  |  |

| Verify            | 1.5 s (typ.)                                                                                              |  |  |

| E.P.V             | 2.5 s (typ.)                                                                                              |  |  |

| Checksum          | 1 s (typ.)                                                                                                |  |  |

| Security          | 0.5 s (typ.)                                                                                              |  |  |

# (2) 78K0/KB2-L, 78K0/KC2-L (1/2)

#### (a) Products with internal ROMs of the 8 KB: $\mu$ PD78F0571, 78F0576, 78F0581, 78F0586

| Command of PG-FP5 | Port: UART-Internal-OSC (Internal high-speed oscillation clock (f⊮: 8 MHz (typ.)),<br>Speed: 500,000 bps |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------|--|--|

|                   |                                                                                                          |  |  |

| Signature         | 0.5 s (typ.)                                                                                             |  |  |

| Blankcheck        | 1 s (typ.)                                                                                               |  |  |

| Erase             | 1 s (typ.)                                                                                               |  |  |

| Program           | 1.5 s (typ.)                                                                                             |  |  |

| Verify            | 1 s (typ.)                                                                                               |  |  |

| E.P.V             | 1.5 s (typ.)                                                                                             |  |  |

| Checksum          | 1 s (typ.)                                                                                               |  |  |

| Security          | 1 s (typ.)                                                                                               |  |  |

# Caution When executing boot swapping, do not use the E.P.V. command with the dedicated flash memory programmer.

| Address        | On-Chip Debug Security ID |

|----------------|---------------------------|

| 0085H to 008EH | Any ID code of 10 bytes   |

| 1085H to 108EH |                           |

#### Table 26-1. On-Chip Debug Security ID

### 26.3 Securing of User Resources

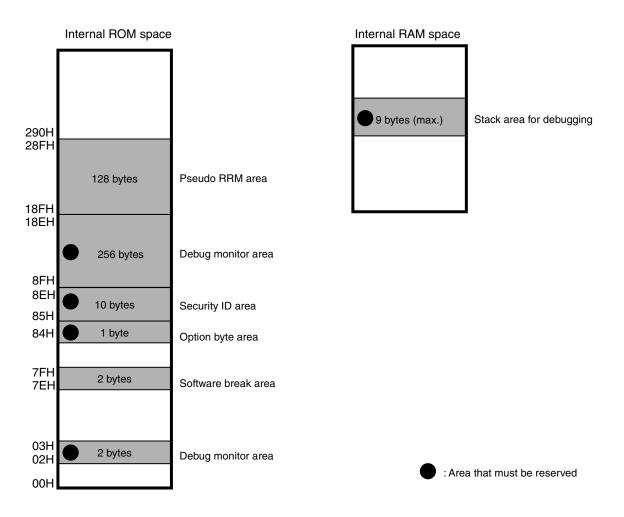

QB-MINI2 uses the user memory spaces (shaded portions in Figure 26-2) to implement communication with the target device, or each debug functions. The areas marked with a dot (•) are always used for debugging, and other areas are used for each debug function used.

These areas can be secured by using user programs or the linker option.

For details on the securing of these areas, refer to the QB-MINI2 On-Chip Debug Emulator with Programming Function User's Manual (U18371E).

|            |                                                                                             | (4/4)          |

|------------|---------------------------------------------------------------------------------------------|----------------|

| Page       | Description                                                                                 | Classification |

| CHAPTER 25 | FLASH MEMORY                                                                                |                |

| p.712      | Change of Remark in 25.8 Flash Memory Programming by Self Programming                       | (e)            |

| CHAPTER 26 | ON-CHIP DEBUG FUNCTION                                                                      |                |

| p.718      | Addition of Caution 2 in 26.1 Connecting QB-MINI2 to 78K0/Kx2-L Microcontrollers            | (c)            |

| p.720      | Addition of Figure 26-1. Connection Example of QB-MINI2 and 78K0/Ix2 Microcontrollers (2/3) | (c)            |

**Remark** "Classification" in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note, (d): Addition/change of package, part number, or management division, (e): Addition/change of related documents