# E. Renesas Electronics America Inc - UPD78F0561MC-CAA-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | I²C, LINbus, UART/USART                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 13                                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 512 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 6x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 20-LSSOP (0.240", 6.10mm Width)                                                      |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0561mc-caa-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

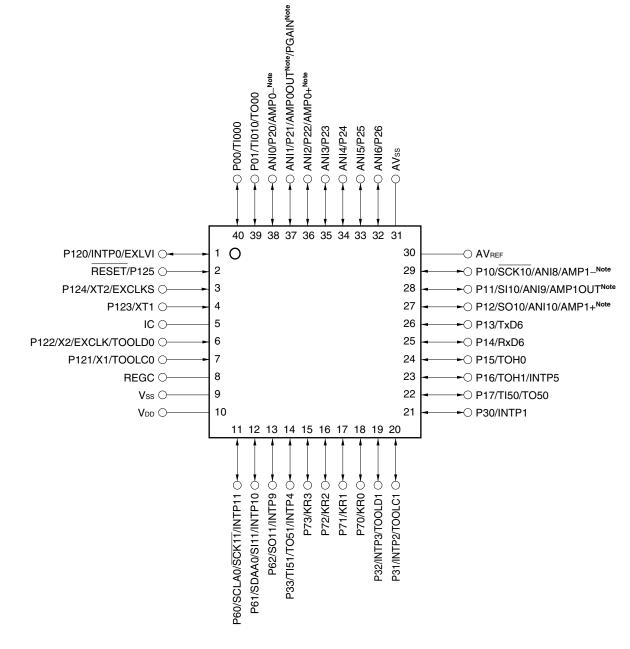

#### 1.3.4 78K0/KC2-L

#### <R> (1) 40-pin plastic WQFN (6x6) (1/2)

Note μPD78F0586, 78F0587, 78F0588 (products with operational amplifier) only

Cautions 1. Leave the IC (Internally Connected) pin open.

- 2. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- 3. ANI0/P20/AMP0-, ANI1/P21/AMP0OUT/PGAIN, ANI2/P22/AMP0+, and ANI3/P23 to ANI6/P26 are set in the analog input mode, P10/ANI8/AMP1-/SCK10, P11/ANI9/AMP1OUT/SI10, and P12/ANI10/AMP1+/SO10 are set in the digital input mode after release of reset.

- 4. RESET/P125 immediately after release of reset is set in the external reset input.

- 5. Set P40, P41, and P63 to output mode (PM40 = PM41 = PM63 = 0) by using software after release of reset.

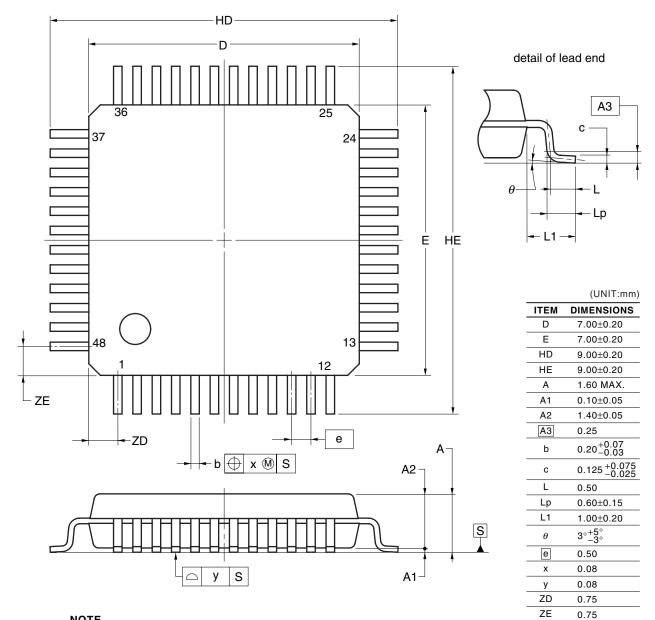

### (3) 48-pin plastic LQFP (fine pitch) (7x7) (2/2)

| AMP0- <sup>Note</sup> , AMP0+ <sup>Note</sup> , |                          | REGC :                     | Regulator Capacitance      |

|-------------------------------------------------|--------------------------|----------------------------|----------------------------|

| AMP1- <sup>Note</sup> , AMP1+ <sup>Note</sup> : | Amplifier Input          | RESET :                    | Reset                      |

| AMP0OUT <sup>Note</sup> ,                       | Amplifier Output         | RTC1HZ :                   | Real-time Counter          |

| AMP1OUT <sup>Note</sup> :                       |                          |                            | Correction Clock (1 Hz)    |

| PGAIN <sup>Note</sup> :                         | Programmable Gain        |                            | Output                     |

|                                                 | Amplifier Input          | RTCCL :                    | Real-time Counter          |

| ANIO-ANI10 :                                    | Analog Input             |                            | Clock (32 kHz Original     |

| AVREF :                                         | Analog Reference         |                            | Oscillation) Output        |

|                                                 | Voltage                  | RTCDIV :                   | Real-time Counter          |

| AVss:                                           | Analog Ground            |                            | Clock (32 kHz Divided      |

| EXCLK :                                         | External Clock Input     |                            | Frequency) Output          |

|                                                 | (Main System Clock)      | RxD6 :                     | Receive Data               |

| EXCLKS :                                        | External Clock Input     | SCLA0, SCK10, SCK11 :      | Serial Clock Input/Output  |

|                                                 | (Subsystem Clock)        | SDAA0 :                    | Serial Data Input/Output   |

| EXLVI :                                         | External potential Input | SI10, SI11 :               | Serial Data Input          |

|                                                 | for Low-voltage detector | SO10, SO11 :               | Serial Data Output         |

| IC :                                            | Internally Connected     | SSI11 :                    | Serial Interface Chip      |

| INTP0 to INTP11 :                               | External Interrupt       |                            | Select Input               |

|                                                 | Input                    | TI000, TI010, TI50, TI51 : | Timer Input                |

| KR0 to KR5 :                                    | Key Return               | TO00, TO50, TO51,          |                            |

| P00 to P02 :                                    | Port 0                   | TOH0, TOH1 :               | Timer Output               |

| P10 to P17 :                                    | Port 1                   | TOOLC0, TOOLC1 :           | Clock Input for Tool       |

| P20 to P27 :                                    | Port 2                   | TOOLD0, TOOLD1 :           | Data Input/Output for Tool |

| P30 to P33 :                                    | Port 3                   | TxD6 :                     | Transmit Data              |

| P40 to P42 :                                    | Port 4                   | VDD:                       | Power Supply               |

| P60 to P63 :                                    | Port 6                   | Vss:                       | Ground                     |

| P70 to P75 :                                    | Port 7                   | X1, X2 :                   | Crystal Oscillator         |

| P120 to P125 :                                  | Port 12                  |                            | (Main System Clock)        |

| PCL :                                           | Programmble Clock        | XT1, XT2 :                 | Crystal Oscillator         |

|                                                 | Output                   |                            | (Subsystem Clock)          |

|                                                 |                          |                            |                            |

Note  $\mu$ PD78F0586, 78F0587, 78F0588 (products with operational amplifier) only

#### 2.2.8 P120 to P125 (port 12)

P120 functions as an I/O port. P121 to P125 function as an Input port. These pins also function as pins for external interrupt request input, potential input for external low-voltage detection, connecting resonator for main system clock, external clock input for main system clock, external clock input for subsystem clock, external clock external clock input for flash memory programmer/on-chip debugger.

Set bit 5 (RSTM) of the reset pin mode register (RSTMASK) to 1 when using P125/RESET as an input port, and clear RSTM to 0 when using P125/RESET as an external reset input.

<R> Furthermore, the timer input and external interrupt request input can be assigned to P121 of the 78K0/KA2-L (25-pin products) and P121 and P125 of the 78K0/KA2-L (32-pin products) by setting the port alternate switch control register (MUXSEL). The data output of the serial interface can be assigned to P120 of the 78K0/KC2-L (44-pin and 48-pin products) by setting the port alternate switch control register (MUXSEL).

| <r></r> | 78K0/KY2-L<br>(μPD78F055x)   |                                                                                           | 78K0/KA2-L<br>(µPD78F056x) |                                                                                           | 78K0/KB2-L<br>(μPD78F057x)   | 78K0/<br>(µPD78                 | KC2-L<br>3F058x)                |                    |                    |

|---------|------------------------------|-------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------|------------------------------|---------------------------------|---------------------------------|--------------------|--------------------|

|         | 16 Pins                      | 20 Pins                                                                                   | 25 Pins                    | 32 Pins                                                                                   | 30 Pins                      | 40 Pins                         | 44, 48 Pins                     |                    |                    |

|         | _                            | _                                                                                         | _                          | _                                                                                         | P120/EXLVI/<br>INTP0         | P120/EXLVI/<br>INTP0            | P120/EXLVI/<br>INTP0(/SO11)     |                    |                    |

|         | P121/X1/<br>TOOLC0           | LC0 TOOLC0 TOOLC0<br>(/TI000)<br>(/INTP0)<br>2/X2/ P122/X2/ P122/X2/<br>LK/ EXCLK/ EXCLK/ |                            | TOOLC0         TOOLC0         TOOLC0           (/TI000)         (/TI000)         (/TI000) |                              | 0 TOOLC0 TOO<br>(/TI000)        |                                 | P121/X1/<br>TOOLC0 | P121/X1/<br>TOOLC0 |

|         | P122/X2/<br>EXCLK/<br>TOOLD0 |                                                                                           |                            | P122/X2/<br>EXCLK/<br>TOOLD0                                                              | P122/X2/<br>EXCLK/<br>TOOLD0 | P122/X2/<br>EXCLK/<br>TOOLD0    | P122/X2/<br>EXCLK/<br>TOOLD0    |                    |                    |

|         | _                            |                                                                                           |                            |                                                                                           |                              | P123/XT1<br>P124/XT2/<br>EXCLKS | P123/XT1<br>P124/XT2/<br>EXCLKS |                    |                    |

|         | P125/RESET                   | 25/RESET P125/RESET P125/RESET                                                            |                            | P125/RESET<br>(/TI000)<br>(/INTP0)                                                        | P125/RESET                   | P125/RESET                      | P125/RESET                      |                    |                    |

**Remark** Functions in parentheses () can be assigned by setting the port alternate switch control register (MUXSEL).

The following operation modes can be specified in 1-bit units.

#### (1) Port mode

P120 to P125 function as an I/O port. P120 to P125 can be set to input or output port using port mode register 12 (PM12). Only for P120 and P125, use of an on-chip pull-up resistor can be specified by pull-up resistor option register 12 (PU12).

#### (2) Control mode

P120 to P125 function as pins for external interrupt request input, potential input for external low-voltage detection, connecting resonator for main system clock, connecting resonator for subsystem clock, external clock input for main system clock, external clock input for subsystem clock, external reset input, and clock input and data I/O for flash memory programmer/on-chip debugger.

#### Figure 4-48. Format of A/D Port Configuration Register 0, 1 (ADPC0, ADPC1) (2/2)

#### (e) 78K0/KB2-L

| Address: FF                           | E2EH After                      | reset: 00H                             | R/W                  |                  |                |                  |        |             |  |  |  |

|---------------------------------------|---------------------------------|----------------------------------------|----------------------|------------------|----------------|------------------|--------|-------------|--|--|--|

| Symbol                                | 7                               | 6                                      | 5                    | 4                | 3              | 2                | 1      | 0           |  |  |  |

| ADPC0                                 | 0                               | 0                                      | 0                    | 0                | ADPCS3         | ADPCS2           | ADPCS1 | ADPCS0      |  |  |  |

|                                       |                                 |                                        |                      |                  |                |                  |        |             |  |  |  |

| Address: FF                           | F2FH After                      | reset: 07H                             | R/W                  |                  |                |                  |        |             |  |  |  |

| Symbol                                | 7                               | 6                                      | 5                    | 4                | 3              | 2                | 1      | 0           |  |  |  |

| ADPC1                                 | 0                               | 0                                      | 0                    | 0                | 0              | ADPCS10          | ADPCS9 | ADPCS8      |  |  |  |

|                                       | f) 78K0/KC2-L (40-pin products) |                                        |                      |                  |                |                  |        |             |  |  |  |

| Address: FF                           |                                 | reset: 00H                             | R/W                  |                  |                |                  |        |             |  |  |  |

| Symbol                                | 7                               | 6                                      | 5                    | 4                | 3              | 2                | 1      | 0           |  |  |  |

| ADPC0                                 | 0                               | ADPCS6                                 | ADPCS5               | ADPCS4           | ADPCS3         | ADPCS2           | ADPCS1 | ADPCS0      |  |  |  |

| Address: FF<br>Symbol                 | F2FH After<br>7                 | reset: 07H<br>6                        | R/W<br>5             | 4                | 3              | 2                | 1      | 0           |  |  |  |

| ADPC1                                 | 0                               | 0                                      | 0                    | 0                | 0              | ADPCS10          | ADPCS9 | ADPCS8      |  |  |  |

| (g) 78K0/KC2<br>Address: FF<br>Symbol |                                 | n <b>d 48-pin p</b><br>reset: 00H<br>6 | roducts)<br>R/W<br>5 | 4                | 3              | 2                | 1      | 0           |  |  |  |

| ADPC0                                 | ,<br>ADPCS7                     | ADPCS6                                 | ADPCS5               | 4<br>ADPCS4      | ADPCS3         | ADPCS2           | ADPCS1 | 0<br>ADPCS0 |  |  |  |

| Address: FF<br>Symbol                 |                                 | reset: 07H                             | R/W<br>5             | 4                | 3              | 2                | 1      | 0           |  |  |  |

| ADPC1                                 | 0                               | 0                                      | 0                    | 4<br>0           | 0              | ADPCS10          | ADPCS9 | ADPCS8      |  |  |  |

| ADPUT                                 | 0                               | 0                                      | 0                    | 0                | 0              | ADPCSTU          | ADPC59 | ADPC56      |  |  |  |

|                                       | ADPCSn                          |                                        | Di                   | nital I/O ar and |                | tion (n Oto t    |        |             |  |  |  |

|                                       |                                 | Angles I/O                             | Dię                  | ynai i/O or ana  | alog I/O selec | tion (n = 0 to 1 | 10)    |             |  |  |  |

|                                       | 0                               | Analog I/O                             |                      |                  |                |                  |        |             |  |  |  |

|                                       | 1                               | Digital I/O                            |                      |                  |                |                  |        |             |  |  |  |

- Cautions 1. Set the pin set to analog input to the input mode by using port mode register 1, 2, and 7 (PM1, PM2, and PM7).

- 2. If data is written to ADPC0 and ADPC1, a wait cycle is generated. Do not write data to ADPC0 and ADPC1 when the peripheral hardware clock is stopped. For details, refer to CHAPTER 31 CAUTIONS FOR WAIT.

# Table 4-15. Settings of Port Mode Register and Output Latch When Using Alternate Function (78K0/KA2-L (20-pin products)) (2/2)

| Pin Name | Alternate Function      |       | PM×× | P×× |

|----------|-------------------------|-------|------|-----|

|          | Function Name           | I/O   |      |     |

| P121     | X1 <sup>Note 1</sup>    | -     | ×    | ×   |

|          | TOOLCO                  | Input | ×    | ×   |

| P122     | X2 <sup>Note 1</sup>    | -     | ×    | ×   |

|          | EXCLK <sup>Note 1</sup> | Input | ×    | ×   |

|          | TOOLD0                  | I/O   | ×    | ×   |

| P125     | RESET Note 2            | Input | ×    | ×   |

- Notes 1. When using the P121 and P122 pins to connect a resonator for the main system clock (X1, X2) or to input an external clock for the main system clock (EXCLK), the X1 oscillation mode or external clock input mode must be set by using OSCCTL register (for details, refer to 5.3 (1) Clock operation mode select register (OSCCTL)). The reset value of OSCCTL is 00H (both P121 and P122 are input port pins).

- 2. Clear RSTM bit (bit 5 of RSTMASK register) to 0 when using P125 as an external reset input (RESET).

**Remark** ×: Don't care

PM××: Port mode register

P×x: Port output latch

<R>

| Pin Name                     | Alternate Function        | ı      | MUXSEL                                            | PM×× | P×× |

|------------------------------|---------------------------|--------|---------------------------------------------------|------|-----|

|                              | Function Name             | I/O    |                                                   |      |     |

| P60                          | SCLA0 Notes 1, 2          | I/O    | -                                                 | 0    | 1   |

|                              | TxD6 <sup>Note 3</sup>    | Output | -                                                 | 0    | 1   |

| P61                          | SDAA0 Notes 1,2           | I/O    | -                                                 | 0    | 1   |

|                              | RxD6                      | Input  | -                                                 | 1    | ×   |

| P70 to P72 <sup>Note 4</sup> | ANI8 to ANI10 Notes 4,5   | Input  | -                                                 | 1    | ×   |

| P121                         | X1 <sup>Note 6</sup>      | -      | -                                                 | ×    | ×   |

|                              | TOOLC0                    | Input  | -                                                 | ×    | ×   |

|                              | (TI000)                   | Input  | TM00SEL1 <sup>Note 4</sup> ,                      | ×    | ×   |

|                              |                           |        | TM00SEL0 = 0, 1                                   |      |     |

|                              | (INTPO)                   | Input  | INTPOSEL1 <sup>Note 4</sup> ,<br>INTPOSEL0 = 0, 1 | ×    | ×   |

| P122                         | X2 <sup>Note 6</sup>      | -      | -                                                 | ×    | ×   |

|                              | EXCLK <sup>Note 6</sup>   | Input  | _                                                 | ×    | ×   |

|                              | TOOLD0                    | I/O    | -                                                 | ×    | ×   |

| P125                         | RESET <sup>Note 7</sup>   | Input  | _                                                 | ×    | ×   |

|                              | (TI000) <sup>Note 4</sup> | Input  | TM00SEL1,                                         | ×    | ×   |

|                              |                           |        | TM00SEL0 = 1, 0                                   |      |     |

|                              | (INTP0) Note 4            | Input  | INTP0SEL1,                                        | ×    | ×   |

|                              |                           |        | INTP0SEL0 = 1, 0                                  |      |     |

## Table 4-16. Settings of Port Mode Register and Output Latch When Using Alternate Function (78K0/KA2-L (25-pin and 32-pin products)) (2/2)

**Notes 1.** During I<sup>2</sup>C communication, set SCLA0 and SDAA0 to N-ch open drain output (V<sub>DD</sub> tolerance) mode by using POM6 register (refer to **4.3 (5) Port output mode register 6 (POM6)**).

- 2. When using an input compliant with the SMBus specifications in I<sup>2</sup>C communication, select the SMBus input buffer by using PIM6 register (refer to 4.3 (4) Port input mode register 6 (PIM6)).

- 3. During UART communication, set TxD6 to normal output (CMOS output) mode by using POM6 register (refer to 4.3 (5) Port output mode register 6 (POM6)).

- 4. 32-pin products only

- The pin function can be selected by using ADPC1 register, PM7 register, and ADS register. Refer to Table

4-13 of 4.2.7 Port 7.

- 6. When using the P121 and P122 pins to connect a resonator for the main system clock (X1, X2) or to input an external clock for the main system clock (EXCLK), the X1 oscillation mode or external clock input mode must be set by using OSCCTL register (for details, refer to 5.3 (1) Clock operation mode select register (OSCCTL)). The reset value of OSCCTL is 00H (both P121 and P122 are input port pins).

- 7. Clear RSTM bit (bit 5 of RSTMASK register) to 0 when using P125 as an external reset input (RESET).

- Remarks 1. ×: Don't care

- PM××: Port mode register

- Pxx: Port output latch

- 2. Functions in parentheses ( ) can be assigned by setting MUXSEL register.

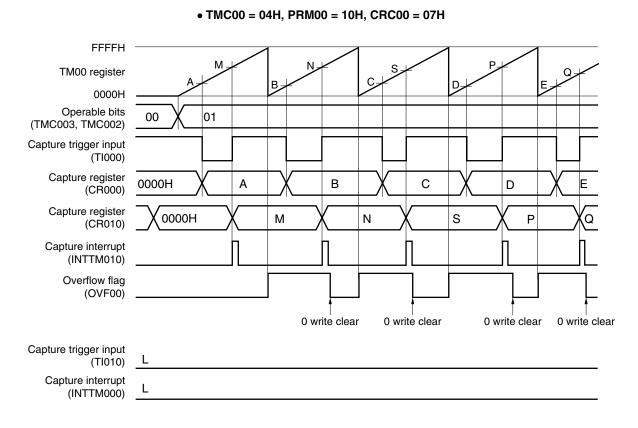

#### (2) Measuring the pulse width by using one input signal of the TI000 pin (free-running timer mode)

Set the free-running timer mode (TMC003 and TMC002 = 01). The count value of TM00 is captured to CR000 in the phase reverse to the valid edge detected on the Tl000 pin. When the valid edge of the Tl000 pin is detected, the count value of TM00 is captured to CR010.

By this measurement method, values are stored in separate capture registers when a width from one edge to another is measured. Therefore, the capture values do not have to be saved. By subtracting the value of one capture register from that of another, a high-level width, low-level width, and cycle are calculated.

If an overflow occurs, the value becomes negative if one captured value is simply subtracted from another and, therefore, a borrow occurs (bit 0 (CY) of the program status word (PSW) is set to 1). If this happens, ignore CY and take the calculated value as the pulse width. In addition, clear bit 0 (OVF00) of 16-bit timer mode control register 00 (TMC00) to 0.

### Figure 6-50. Timing Example of Pulse Width Measurement (2)

#### 7.4.3 Square-wave output operation

A square wave with any selected frequency is output at intervals determined by the value preset to 8-bit timer compare register 5n (CR5n).

The TO5n pin output status is inverted at intervals determined by the count value preset to CR5n by setting bit 0 (TOE5n) of 8-bit timer mode control register 5n (TMC5n) to 1. This enables a square wave with any selected frequency to be output (duty = 50%).

Remark Square-wave output is operable only in the 78K0/KB2-L and 78K0/KC2-L.

#### Setting

- <1> Set each register.

- Clear the port output latch (P17 or P33)<sup>Note</sup> and port mode register (PM17 or PM33)<sup>Note</sup> to 0.

- TCL5n: Select the count clock.

- CR5n: Compare value

- TMC5n: Stop the count operation, select the mode in which clear & start occurs on a match of TM5n and CR5n.

| LVS5n | LVR5n | Timer Output F/F Status Setting                                      |

|-------|-------|----------------------------------------------------------------------|

| 0     | 1     | Timer output F/F clear (0) (default value of TO5n output: low level) |

| 1     | 0     | Timer output F/F set (1) (default value of TO5n output: high level)  |

Timer output enabled

(TMC5n = 00001011B or 00000111B)

- <2> After TCE5n = 1 is set, the count operation starts.

- <3> The timer output F/F is inverted by a match of TM5n and CR5n. After INTTM5n is generated, TM5n is cleared to 00H.

- <4> After these settings, the timer output F/F is inverted at the same interval and a square wave is output from TO5n. The frequency is as follows.

- Frequency = 1/2t (N + 1) (N: 00H to FFH)

- Note 8-bit timer/event counter 50: P17, PM17 8-bit timer/event counter 51: P33, PM33

#### Caution Do not write other values to CR5n during operation.

Remarks 1. For how to enable the INTTM5n signal interrupt, refer to CHAPTER 17 INTERRUPT FUNCTIONS.

2. 78K0/KB2-L, 78K0/KC2-L: n = 0, 1

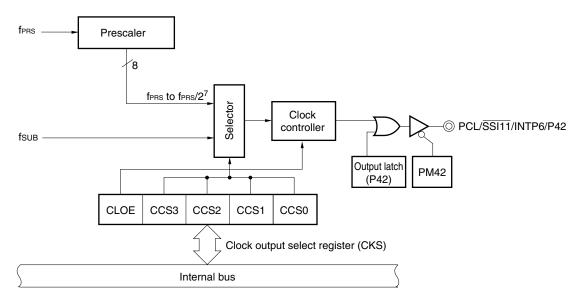

### CHAPTER 11 CLOCK OUTPUT CONTROLLER

| Item                    | 78K0/KY2-L<br>(μPD78F055x) | 78K0/KA2-L<br>(μθD78F056x) | 78K0/KB2-L<br>(μPD78F057x) |             | KC2-L<br>F058x) |

|-------------------------|----------------------------|----------------------------|----------------------------|-------------|-----------------|

|                         | 16 Pins                    | 20, 25, 32 Pins            | 30 Pins                    | 40, 44 Pins | 48 Pins         |

| Clock output controller |                            |                            | _                          |             | $\checkmark$    |

**Remark**  $\sqrt{:}$  Mounted, -: Not mounted

#### 11.1 Functions of Clock Output Controller

The clock output controller is intended for carrier output during remote controlled transmission and clock output for supply to peripheral ICs. The clock selected with the clock output selection register (CKS) is output.

Figure 11-1 shows the block diagram of clock output controller.

#### 11.2 Configuration of Clock Output Controller

The clock output controller includes the following hardware.

| Table 11-1. | Configuration | of Clock | Output Controller |

|-------------|---------------|----------|-------------------|

|-------------|---------------|----------|-------------------|

| Item              | Configuration                                                       |

|-------------------|---------------------------------------------------------------------|

| Control registers | Clock output selection register (CKS)<br>Port mode register 4 (PM4) |

|                   | Port register 4 (P4)                                                |

|     |        |                   |      |       | (1                                | ) 4.0 V ≤ A               | $V_{REF} \le 5.5 V$ |                  |                 |                           |

|-----|--------|-------------------|------|-------|-----------------------------------|---------------------------|---------------------|------------------|-----------------|---------------------------|

| A/C | Conver | ter Mod<br>(ADM0) | •    | ter 0 | Mode                              | Conversion Time Selection |                     |                  |                 | Conversion<br>Clock (fad) |

| FR2 | FR1    | FR0               | LV1  | LV0   |                                   |                           | fprs = 4 MHz        | fprs = 8 MHz     | fprs = 10 MHz   |                           |

| 0   | 0      | 0                 | 0    | 0     | Standard                          | 264/fprs                  | 66.0 μs             | 33.0 <i>µ</i> s  | 26.4 <i>μ</i> s | fprs/12                   |

| 0   | 0      | 1                 |      |       |                                   | 176/fprs                  | 44.0 μs             | 22.0 <i>µ</i> s  | 17.6 <i>μ</i> s | fprs/8                    |

| 0   | 1      | 0                 |      |       |                                   | 132/fprs                  | 33.0 <i>µ</i> s     | 16.5 <i>μ</i> s  | 13.2 <i>μ</i> s | fprs/6                    |

| 0   | 1      | 1                 |      |       |                                   | 88/fprs                   | 22.0 µs             | 11.0 <i>μ</i> s  | 8.8 <i>µ</i> s  | f <sub>PRS</sub> /4       |

| 1   | 0      | 0                 |      |       |                                   | 66/fprs                   | 16.5 <i>μ</i> s     | 8.25 <i>µ</i> s  | 6.6 <i>μ</i> s  | fprs/3                    |

| 1   | 0      | 1                 |      |       |                                   | 44/f <sub>PRS</sub>       | 11.0 <i>μ</i> s     | Setting prohibi  | ted             | fprs/2                    |

| 1   | 1      | 0                 |      |       |                                   | 33/fprs                   | 8.25 <i>μ</i> s     | Setting prohibi  | ted             | fprs/1.5                  |

| 1   | 1      | 1                 |      |       |                                   | 22/fprs                   | Setting prohibi     | ited             |                 | fprs                      |

| 1   | 0      | 1                 | 1    | 1     | High-speed 2                      | 44/f <sub>PRS</sub>       | 11.0 <i>μ</i> s     | 5.5 <i>μ</i> s   | 4.4 <i>μ</i> s  | fprs/2                    |

| 1   | 1      | 1                 |      |       | 22/fprs 5.5 µs Setting prohibited |                           | ted                 | fprs             |                 |                           |

| 1   | 0      | 0                 | 1    | 0     | High-speed 1                      | 66/fprs                   | 16.5 <i>μ</i> s     | 8.25 <i>μ</i> s  | 6.6 <i>μ</i> s  | fprs/3                    |

| 1   | 1      | 0                 |      |       |                                   | 33/fprs                   | 8.25 <i>µ</i> s     | 4.125 <i>μ</i> s | 3.3 <i>µ</i> s  | fprs/1.5                  |

|     | Othe   | er than a         | bove |       | Setting prohibit                  | ted                       |                     |                  |                 |                           |

### Table 12-2. A/D Conversion Time Selection (1/3)

- Cautions 1. When rewriting FR2 to FR0, LV1, and LV0 to other than the same data, stop A/D conversion once (ADCS = 0) beforehand.

- 2. The above conversion time does not include clock frequency errors. Select conversion time, taking clock frequency errors into consideration.

Remark fPRs: Peripheral hardware clock frequency

| <r></r>                          | Fiç         | gure 12-12. | Format of I  | Port Mode I   | Register 7 (I | PM7) (78K0    | /KA2-L (32-    | pin product | s))  |

|----------------------------------|-------------|-------------|--------------|---------------|---------------|---------------|----------------|-------------|------|

|                                  | Address: FF | 27H After   | reset: FFH   | R/W           |               |               |                |             |      |

|                                  | Symbol      | 7           | 6            | 5             | 4             | 3             | 2              | 1           | 0    |

|                                  | PM7         | 1           | 1            | 1             | 1             | 1             | PM72           | PM71        | PM70 |

|                                  |             |             |              |               |               |               |                |             |      |

|                                  |             | PM7n        |              |               | P7n pin I/O r | node selectio | n (n = 0 to 2) |             |      |

| 0 Output mode (output buffer on) |             |             |              |               |               |               |                |             |      |

|                                  |             | 1           | Input mode ( | output buffer | off)          |               |                |             |      |

#### at of Dout Mode Deviator 7 (DM7) (79K0/KA9 L (29 min ما ب مه م ۱ 10.10 E -

#### Figure 13-4. Format of A/D Port Configuration Register 0 (ADPC0)

### (a) 78K0/KY2-L

|            | Address: Ff                                                                                                               | E2EH After                                                                                 | reset: 00H                                                                     | R/W                                                         |                                 |                                      |                                      |                                      |                            |

|------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|----------------------------|

|            | Symbol                                                                                                                    | 7                                                                                          | 6                                                                              | 5                                                           | 4                               | 3                                    | 2                                    | 1                                    | 0                          |

|            | ADPC0                                                                                                                     | 0                                                                                          | 0                                                                              | 0                                                           | 0                               | ADPCS3                               | ADPCS2                               | ADPCS1                               | ADPCS0                     |

| (b)        | 78K0/KA2-L (                                                                                                              | 20-pin prod                                                                                | ucts)                                                                          |                                                             |                                 |                                      |                                      |                                      |                            |

|            | Address: FF                                                                                                               | E2EH After                                                                                 | reset: 00H                                                                     | R/W                                                         |                                 |                                      |                                      |                                      |                            |

|            | Symbol                                                                                                                    | 7                                                                                          | 6                                                                              | 5                                                           | 4                               | 3                                    | 2                                    | 1                                    | 0                          |

|            | ADPC0                                                                                                                     | 0                                                                                          | 0                                                                              | ADPCS5                                                      | ADPCS4                          | ADPCS3                               | ADPCS2                               | ADPCS1                               | ADPCS0                     |

| (c)        | 78K0/KA2-L (                                                                                                              | 25-pin prod                                                                                | ucts)                                                                          |                                                             |                                 |                                      |                                      |                                      |                            |

|            | Address: FF                                                                                                               | E2EH After                                                                                 | reset: 00H                                                                     | R/W                                                         |                                 |                                      |                                      |                                      |                            |

|            | Symbol                                                                                                                    | 7                                                                                          | 6                                                                              | 5                                                           | 4                               | 3                                    | 2                                    | 1                                    | 0                          |

|            | ADPC0                                                                                                                     | 0                                                                                          | ADPCS6                                                                         | ADPCS5                                                      | ADPCS4                          | ADPCS3                               | ADPCS2                               | ADPCS1                               | ADPCS0                     |

| (d)        | 78K0/KA2-L (                                                                                                              | 32-pin prod                                                                                | ucts)                                                                          |                                                             |                                 |                                      |                                      |                                      |                            |

|            | Address: FF                                                                                                               | E2EH After                                                                                 | reset: 00H                                                                     | R/W                                                         |                                 |                                      |                                      |                                      |                            |

|            | Symbol                                                                                                                    | 7                                                                                          | 6                                                                              | 5                                                           | 4                               | 3                                    | 2                                    | 1                                    | 0                          |

|            | ADPC0                                                                                                                     | ADPCS7                                                                                     | ADPCS6                                                                         | ADPCS5                                                      | ADPCS4                          | ADPCS3                               | ADPCS2                               | ADPCS1                               | ADPCS0                     |

|            |                                                                                                                           |                                                                                            |                                                                                |                                                             |                                 |                                      |                                      |                                      |                            |

| (e)        | 78K0/KB2-L                                                                                                                |                                                                                            |                                                                                |                                                             |                                 |                                      |                                      |                                      |                            |

| (e)        | Address: FF                                                                                                               |                                                                                            | reset: 00H                                                                     | R/W                                                         |                                 |                                      |                                      |                                      |                            |

| (e)        | Address: FF<br>Symbol                                                                                                     | 7                                                                                          | 6                                                                              | 5                                                           | 4                               | 3                                    | 2                                    | 1                                    | 0                          |

| (e)        | Address: FF                                                                                                               |                                                                                            |                                                                                |                                                             | 4                               | 3<br>ADPCS3                          | 2<br>ADPCS2                          | 1<br>ADPCS1                          | 0<br>ADPCS0                |

| (e)<br>(f) | Address: FF<br>Symbol                                                                                                     | 7                                                                                          | 6<br>0                                                                         | 5                                                           |                                 |                                      |                                      |                                      |                            |

|            | Address: Ff<br>Symbol<br>ADPC0                                                                                            | 7<br>0<br>40-pin prod                                                                      | 6<br>0                                                                         | 5                                                           |                                 |                                      |                                      |                                      |                            |

|            | Address: FF<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: FF<br>Symbol                                                   | 7<br>0<br>40-pin prod                                                                      | 6<br>0<br>ucts)<br>reset: 00H<br>6                                             | 5<br>0<br>R/W<br>5                                          | 0                               | ADPCS3                               |                                      | ADPCS1                               | ADPCS0<br>0                |

|            | Address: FF<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: FF                                                             | 7<br>0<br><b>40-pin prod</b><br>=2EH After                                                 | 6<br>0<br>ucts)<br>reset: 00H                                                  | 5<br>0<br>R/W                                               | 0                               | ADPCS3                               | ADPCS2                               | ADPCS1                               | ADPCS0                     |

| (f)        | Address: FF<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: FF<br>Symbol                                                   | 7<br>0<br><b>40-pin prod</b><br>=2EH After<br>7<br>0                                       | 6<br>0<br>ucts)<br>reset: 00H<br>6<br>ADPCS6                                   | 5<br>0<br>R/W<br>5<br>ADPCS5                                | 0                               | ADPCS3                               | ADPCS2<br>2                          | ADPCS1                               | ADPCS0<br>0                |

| (f)        | Address: FF<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: FF<br>Symbol<br>ADPC0                                          | 7<br>0<br><b>40-pin prod</b><br>=2EH After<br>7<br>0<br><b>44-pin and</b> 4                | 6<br>0<br>ucts)<br>reset: 00H<br>6<br>ADPCS6                                   | 5<br>0<br>R/W<br>5<br>ADPCS5                                | 0                               | ADPCS3                               | ADPCS2<br>2                          | ADPCS1                               | ADPCS0<br>0                |

| (f)        | Address: Ff<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: Ff<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: Ff<br>Symbol | 7<br>0<br>40-pin prod<br>=2EH After<br>7<br>0<br>44-pin and 4<br>=2EH After<br>7           | 6<br>0<br>ucts)<br>reset: 00H<br>6<br>ADPCS6<br>48-pin prod<br>reset: 00H<br>6 | 5<br>0<br>R/W<br>5<br>ADPCS5<br>ucts)<br>R/W<br>5           | 0<br>4<br>ADPCS4                | ADPCS3<br>3<br>ADPCS3<br>3           | ADPCS2<br>2<br>ADPCS2<br>2           | ADPCS1<br>1<br>ADPCS1                | ADPCS0<br>0<br>ADPCS0<br>0 |

| (f)        | Address: FF<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: FF<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: FF           | 7<br>0<br>40-pin prod<br>=2EH After<br>7<br>0<br>44-pin and 4                              | 6<br>0<br>ucts)<br>reset: 00H<br>6<br>ADPCS6<br>48-pin prod                    | 5<br>0<br>R/W<br>5<br>ADPCS5<br>ucts)<br>R/W                | 0<br>4<br>ADPCS4                | ADPCS3<br>3<br>ADPCS3                | ADPCS2<br>2<br>ADPCS2                | ADPCS1<br>1<br>ADPCS1                | 0<br>ADPCS0                |

| (f)        | Address: Ff<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: Ff<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: Ff<br>Symbol | 7<br>0<br>40-pin prod<br>=2EH After<br>7<br>0<br>44-pin and 4<br>=2EH After<br>7<br>ADPCS7 | 6<br>0<br>ucts)<br>reset: 00H<br>6<br>ADPCS6<br>48-pin prod<br>reset: 00H<br>6 | 5<br>0<br>R/W<br>5<br>ADPCS5<br>ucts)<br>R/W<br>5<br>ADPCS5 | 0<br>4<br>ADPCS4<br>4<br>ADPCS4 | ADPCS3<br>3<br>ADPCS3<br>3<br>ADPCS3 | ADPCS2<br>2<br>ADPCS2<br>2<br>ADPCS2 | 1<br>ADPCS1<br>ADPCS1<br>1<br>ADPCS1 | ADPCS0<br>0<br>ADPCS0<br>0 |

| (f)        | Address: Ff<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: Ff<br>Symbol<br>ADPC0<br>78K0/KC2-L (<br>Address: Ff<br>Symbol | 7<br>0<br>40-pin prod<br>=2EH After<br>7<br>0<br>44-pin and 4<br>=2EH After<br>7           | 6<br>0<br>ucts)<br>reset: 00H<br>6<br>ADPCS6<br>48-pin prod<br>reset: 00H<br>6 | 5<br>0<br>R/W<br>5<br>ADPCS5<br>ucts)<br>R/W<br>5<br>ADPCS5 | 0<br>4<br>ADPCS4<br>4<br>ADPCS4 | ADPCS3<br>3<br>ADPCS3<br>3           | ADPCS2<br>2<br>ADPCS2<br>2<br>ADPCS2 | 1<br>ADPCS1<br>ADPCS1<br>1<br>ADPCS1 | ADPCS0<br>0<br>ADPCS0<br>0 |

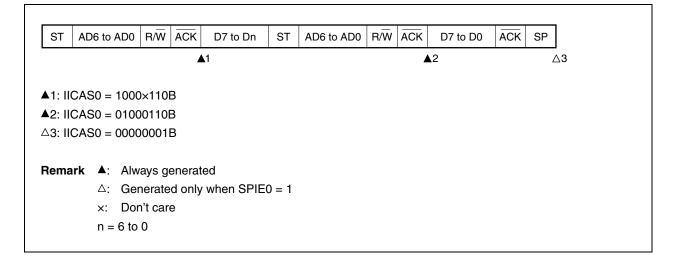

#### (ii) When WTIM0 = 1

| <b></b>        |                     | _       |          |              | 11  |          | 11  |    | ٦  |

|----------------|---------------------|---------|----------|--------------|-----|----------|-----|----|----|

| ST             | AD6 to AD0          | R/W     | ACK      | D7 to D0     | ACK | D7 to D0 | ACK | SP |    |

|                |                     |         | ▲1       |              |     | 2        |     | Δ  | ∆3 |

|                |                     |         |          |              |     |          |     |    |    |

| <b>▲</b> 1: II | CAS0 = 1000         | 1110B   | 3        |              |     |          |     |    |    |

| <b>▲</b> 2: II | CAS0 = 0100         | 0100E   | 3        |              |     |          |     |    |    |

| ∆3: II         | CAS0 = 0000         | 0001E   | 3        |              |     |          |     |    |    |

|                |                     |         |          |              |     |          |     |    |    |

| Rema           | r <b>k ≜</b> : Alwa | ays ge  | enerate  | d            |     |          |     |    |    |

|                | ∆: Ger              | nerated | d only v | vhen SPIE0 = | 1   |          |     |    |    |

|                |                     |         |          |              |     |          |     |    |    |

#### (d) When loss occurs due to restart condition during data transfer

#### (i) Not extension code (Example: unmatches with SVA0)

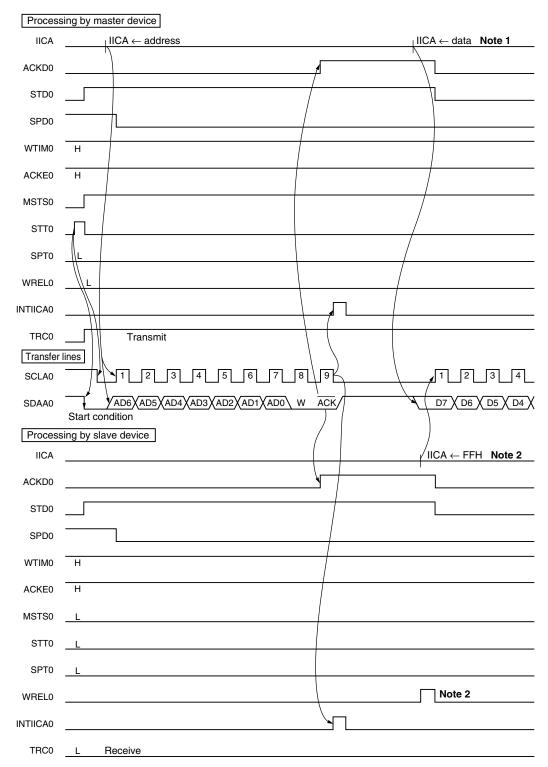

## Figure 15-33. Example of Master to Slave Communication (When 9-Clock Wait Is Selected for Both Master and Slave) (1/3)

#### (1) Start condition ~ address

Notes 1. Write data to IICA, not setting WREL0, in order to cancel a wait state during master transmission.2. To cancel slave wait, write "FFH" to IICA or set WREL0.

RENESAS

### 17.3 Registers Controlling Interrupt Functions

The following 6 types of registers are used to control the interrupt functions.

- Interrupt request flag registers (IF0L, IF0H, IF1L, IF1H)

- Interrupt mask flag registers (MK0L, MK0H, MK1L, MK1H)

- Priority specification flag registers (PR0L, PR0H, PR1L, PR1H)

- External interrupt rising edge enable registers (EGPCTL0, EGPCTL1)

- External interrupt falling edge enable registers (EGNCTL0, EGNCTL1)

- Program status word (PSW)

Table 17-2 shows a list of interrupt request flags, interrupt mask flags, and priority specification flags corresponding to interrupt request sources.

| < | R> |

|---|----|

|   |    |

#### Table 17-2. Flags Corresponding to Interrupt Request Sources (1/2)

| KY           | К            | A            | KB           | KC2-L        |              | Interrupt    | Interrupt Request Flag |         | Interrupt Ma | ask Flag | Priority Specification Flag |         |          |

|--------------|--------------|--------------|--------------|--------------|--------------|--------------|------------------------|---------|--------------|----------|-----------------------------|---------|----------|

| 2-L          | 2-           | ٠L           | 2-L          |              |              |              | Source                 |         | Register     |          | Register                    |         | Register |

| 16           | 20           | 25,          | 30           | 40           | 44           | 48           |                        |         |              |          |                             |         |          |

| pins         | pins         | 32           | pins         | pins         | pins         | pins         |                        |         |              |          |                             |         |          |

|              |              | pins         |              |              |              |              |                        |         |              |          |                             |         |          |

| $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | INTLVI                 | LVIIF   | IFOL         | LVIMK    | MKOL                        | LVIPR   | PROL     |

| $\checkmark$ | INTP0                  | PIF0    |              | PMK0     |                             | PPR0    |          |

| $\checkmark$ |              | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP1                  | PIF1    |              | PMK1     |                             | PPR1    |          |

| -            |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP2                  | PIF2    |              | PMK2     |                             | PPR2    |          |

| -            |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP3                  | PIF3    |              | PMK3     |                             | PPR3    |          |

| -            | -            | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | INTP4                  | PIF4    |              | PMK4     |                             | PPR4    |          |

| -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTP5                  | PIF5    |              | PMK5     |                             | PPR5    |          |

| $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTSRE6                | SREIF6  |              | SREMK6   |                             | SREPR6  |          |

| $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTSR6                 | SRIF6   | IF0H         | SRMK6    | мкон                        | SRPR6   | PR0H     |

| $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTST6                 | STIF6   |              | STMK6    |                             | STPR6   |          |

| -            | -            | -            |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | INTCSI10               | CSIIF10 |              | CSIMK10  |                             | CSIPR10 |          |

| -            | -            |              | -            | _            | -            | -            | INTCSI11               | CSIIF11 |              | CSIMK11  |                             | CSIPR11 |          |

| $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | INTTMH1                | TMIFH1  |              | TMMKH1   |                             | TMPRH1  |          |

| -            | -            | -            | $\checkmark$ |              |              |              | INTTMH0                | TMIFH0  |              | ТММКН0   |                             | TMPRH0  |          |

| -            | -            | -            | $\checkmark$ |              | $\checkmark$ |              | INTTM50                | TMIF50  |              | TMMK50   |                             | TMPR50  |          |

| $\checkmark$ |              |              |              |              | $\checkmark$ | $\checkmark$ | INTTM000               | TMIF000 | ]            | TMMK000  | ]                           | TMPR000 |          |

| $\checkmark$ |              |              | $\checkmark$ |              | $\checkmark$ |              | INTTM010               | TMIF010 |              | TMMK010  |                             | TMPR010 |          |

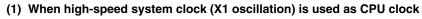

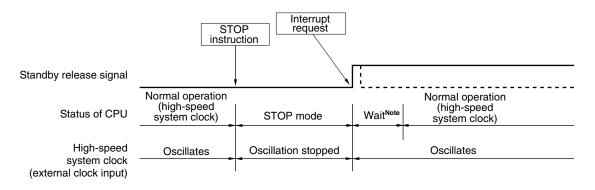

#### Interrupt request Wait STOP instruction (set by OSTS) Standby release signal Normal operation Normal operation Oscillation stabilization wait (high-speed (high-speed Status of CPU system clock) STOP mode (HALT mode status) system clock) High-speed Oscillates Oscillation stopped Oscillates system clock (X1 oscillation) Oscillation stabilization time (set by OSTS)

#### Figure 19-6. STOP Mode Release by Interrupt Request Generation (1/2)

(2) When high-speed system clock (external clock input) is used as CPU clock

**Note** The wait time is as follows:

- When vectored interrupt servicing is carried out: 17 or 18 clocks

- When vectored interrupt servicing is not carried out: 11 or 12 clocks

- **Remark** The broken lines indicate the case when the interrupt request that has released the standby mode is acknowledged.

#### 25.8 Flash Memory Programming by Self Programming

The 78K0/Kx2-L microcontrollers support a self programming function that can be used to rewrite the flash memory via a user program. Because this function allows a user application to rewrite the flash memory by using the 78K0/Kx2-L microcontroller self programming library, it can be used to upgrade the program in the field.

If an interrupt occurs during self programming, self programming can be temporarily stopped and interrupt servicing can be executed. If an unmasked interrupt request is generated in the EI state, the request branches directly from the self programming library to the interrupt routine. After the self programming mode is later restored, self programming can be resumed. However, the interrupt response time is different from that of the normal operation mode.

- Cautions 1. The self programming function cannot be used when the CPU operates with the subsystem clock.

- 2. To prohibit an interrupt during self programming, in the same way as in the normal operation mode, execute the self programming library in the state where the IE flag is cleared (0) by the DI instruction. To enable an interrupt, clear (0) the interrupt mask flag to accept in the state where the IE flag is set (1) by the El instruction, and then execute the self programming library.

- 3. Make sure that the regulator output voltage mode is fixed when executing self programming or EEPROM emulation.

- 4. The power supply voltage range in which the flash memory can be rewritten in normal power mode is  $V_{DD} \ge 2.5$  V. Note that program area can be rewritten by using the self programming library in normal power mode.

- 5. Observe the following points when rewriting the flash memory in low power consumption mode:

- Data area can be rewritten in low power consumption mode, but program area cannot.

Data area: Flash memory area handled as data

Program area: Flash memory area handled as the program

- The flash memory cannot be rewritten in low power consumption mode if the power supply voltage is 2.0 V or lower.

- Flash memory that is erased and written in low power consumption mode cannot be accessed in normal power mode. To use this data in normal power mode, switch to low power consumption mode and transfer the flash memory contents to RAM.

- Blocks cannot be overwritten by using the self programming library. Be sure to erase a block first before rewriting data to it.

- A wait time of 2 ms is required before executing self programming after switching from normal power mode to low power consumption mode.

- <R> Remark For details of the self programming function and the self programming library, refer to "78K0 Microcontrollers User's Manual Self Programming Library Type 01 (U18274E)" and "78K0 Microcontrollers Self Programming Library Type 01 Ver. 3.10 Operating Precautions (notification document) (ZUD-CD-09-0122)".

For details of the EEPROM emulation library, refer to "78K0 Microcontrollers User's Manual EEPROM Emulation Library Type 01 (U18275E)" and "78K0 Microcontrollers EEPROM Emulation Library Type 01 Ver.2.10 Operating Precautions (notification document) (ZUD-CD-09-0165)".

• µPD78F0581GA-GAM-AX, 78F0582GA-GAM-AX, 78F0583GA-GAM-AX, 78F0586GA-GAM-AX, 78F0587GA-GAM-AX, 78F0588GA-GAM-AX

### 48-PIN PLASTIC LQFP (FINE PITCH) (7x7)

#### NOTE

Each lead centerline is located within 0.08 mm of its true position at maximum material condition.

P48GA-50-GAM

|             | _                                                                                                                                                                                                                                                | (3/                                    |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|

| Edition     | Description                                                                                                                                                                                                                                      | Chapter                                |  |  |

| 2nd Edition | Modification of Table 12-3 Setting Functions of P10/ANI8/AMP1-, P12/ANI10/AMP1+<br>Pins                                                                                                                                                          | CHAPTER 12 A/D<br>CONVERTER            |  |  |

|             | Modification of Table 12-5 Setting Functions of P20/ANI0/AMP0-, P22/ANI2/AMP0+<br>Pins                                                                                                                                                           |                                        |  |  |

|             | Deletion of Caution 2 in 12.4.1 Basic operations of A/D converter                                                                                                                                                                                |                                        |  |  |

|             | Modification of description of setting methods and deletion of <b>Caution 2</b> in <b>12.4.3</b> (1) A/D conversion operation                                                                                                                    |                                        |  |  |

|             | Modification of Figure 13-1 Block Diagram of Operational Amplifier                                                                                                                                                                               | CHAPTER 13                             |  |  |

|             | Addition of <b>Remark</b> to <b>Figure 13-2</b> Format of Operational Amplifier 0 Control Register (AMP0M) (Products with Operational Amplifier Only)                                                                                            | OPERATIONAL<br>AMPLIFIERS              |  |  |

|             | Modification of Figure 13-4 Format of A/D Port Configuration Register 0 (ADPC0)                                                                                                                                                                  |                                        |  |  |

|             | Modification of Figure 13-5 Format of A/D Port Configuration Register 1 (ADPC1)<br>(78K0/KB2-L and 78K0/KC2-L Only)                                                                                                                              |                                        |  |  |

|             | Modification of Table 13-2 Setting Functions of P10/ANI8/AMP1-, P12/ANI10/AMP1+<br>Pins                                                                                                                                                          |                                        |  |  |

|             | Modification of Table 13-4 Setting Functions of P20/ANI0/AMP0-, P22/ANI2/AMP0+<br>Pins                                                                                                                                                           |                                        |  |  |

|             | Modification of Remark in Figure 14-4 Block Diagram of Serial Interface UART6                                                                                                                                                                    | CHAPTER 14                             |  |  |

|             | Addition of Note 3 to Figure 14-8 Format of Clock Selection Register 6 (CKSR6)                                                                                                                                                                   | SERIAL INTERFACE                       |  |  |

|             | Modification of description in 14.3 (8) Port mode register 1 (PM1), port mode register 6 (PM6)                                                                                                                                                   | UART6                                  |  |  |

|             | Modification of (1) 78K0/KY2-L and 78K0/KA2-L in Table 14-2 Relationship Between<br>Register Settings and Pins                                                                                                                                   |                                        |  |  |

|             | Addition of 15.4.2 Setting transfer clock by using IICWL and IICWH registers                                                                                                                                                                     | CHAPTER 15<br>SERIAL INTERFACE<br>IICA |  |  |

|             | Modification of the mounted situation in the 78K0/KB2-L and 78K0/KC2-L                                                                                                                                                                           | CHAPTER 16                             |  |  |

|             | Modification of description in 16.3 (4) Port mode registers 1, 4, 6, 12 (PM1, PM4, PM6, PM12)                                                                                                                                                    | SERIAL INTERFACES<br>CSI10 AND CSI11   |  |  |

|             | Modification of and addition of Notes 3 and 4 to Table 16-3 SO1n Output Status                                                                                                                                                                   | 1                                      |  |  |

|             | Modification of maskable interrupts (internal) in the 78K0/KB2-L and 78K0/KC2-L                                                                                                                                                                  | CHAPTER 17                             |  |  |

|             | Modification of Table 17-1 Interrupt Source List (1/2)                                                                                                                                                                                           | INTERRUPT                              |  |  |

|             | Modification of Table 17-2 Flags Corresponding to Interrupt Request Sources (1/2)                                                                                                                                                                | FUNCTIONS                              |  |  |

|             | Modification of Caution in Figure 17-4 Format of Interrupt Request Flag Registers<br>(IF0L, IF0H, IF1L, IF1H) (78K0/KB2-L) to Figure 17-6 Format of Interrupt Request Flag<br>Registers (IF0L, IF0H, IF1L, IF1H) (48-pin products of 78K0/KC2-L) |                                        |  |  |

|             | Modification of Caution in Figure 17-9 Format of Interrupt Mask Flag Registers (MK0L,<br>MK0H, MK1L, MK1H) (78K0/KB2-L) to Figure 17-11 Format of Interrupt Mask Flag<br>Registers (MK0L, MK0H, MK1L, MK1H) (48-pin products of 78K0/KC2-L)      |                                        |  |  |

**Remark** "Classification" in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note, (d):

Addition/change of package, part number, or management division, (e): Addition/change of related documents

| Edition     | Description                                                                                                                                                                                                                                                                                                                                          | Chapter                                                 |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| 3rd Edition | Modification of Related Documents                                                                                                                                                                                                                                                                                                                    | INTRODUCTION                                            |  |

|             | Modification of description in 1.1 Features                                                                                                                                                                                                                                                                                                          | CHAPTER 1                                               |  |

|             | Modification of Caution 1 in 1.3.3 78K0/KB2-L and 1.3.4 78K0/KC2-L                                                                                                                                                                                                                                                                                   | OUTLINE                                                 |  |

|             | Modification of Caution 1 in 1.4.3 78K0/KB2-L and 1.4.4 78K0/KC2-L                                                                                                                                                                                                                                                                                   |                                                         |  |

|             | Modification of description in 1.5 Outline of Functions                                                                                                                                                                                                                                                                                              |                                                         |  |

|             | Modification of Table 3-6 Special Function Register List: 78K0/KY2-L to Table 3-9 Special Function Register List: 78K0/KC2-L                                                                                                                                                                                                                         | CHAPTER 3 CPU<br>ARCHITECTURE                           |  |

|             | Modification of Table 4-10 Setting Functions of P21/ANI1/AMP0OUT/PGAIN Pin                                                                                                                                                                                                                                                                           | CHAPTER 4 PORT                                          |  |

|             | Addition of description to 4.3 (5) Port output mode register 6 (POM6)                                                                                                                                                                                                                                                                                | FUNCTIONS                                               |  |

|             | Addition of Caution 5 to Table 4-12 Settings of Port Mode Register and Output Latch<br>When Using Alternate Function (78K0/KY2-L) (1/2)                                                                                                                                                                                                              |                                                         |  |

|             | Addition of Caution 5 to Table 4-13 Settings of Port Mode Register and Output Latch<br>When Using Alternate Function (78K0/KA2-L) (1/2)                                                                                                                                                                                                              |                                                         |  |