# E. Renesas Electronics America Inc - UPD78F0565MC-CAA-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

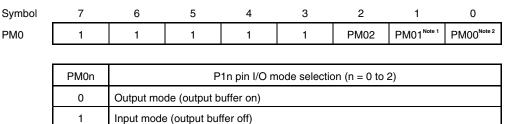

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | I²C, LINbus, UART/USART                                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 13                                                                                   |

| Program Memory Size        | 4KB (4K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 384 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 6x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

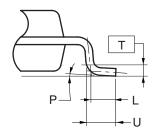

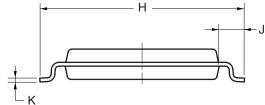

| Package / Case             | 20-LSSOP (0.240", 6.10mm Width)                                                      |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0565mc-caa-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address           | Symbol   | Bit No. R/W Number of Bits<br>Manipulated<br>Simultaneously |                          |      |      |      |               |               |               | ed    | After<br>Reset | Reference<br>page |              |        |                  |

|-------------------|----------|-------------------------------------------------------------|--------------------------|------|------|------|---------------|---------------|---------------|-------|----------------|-------------------|--------------|--------|------------------|

|                   |          | 7                                                           | 6                        | 5    | 4    | 3    | 2             | 1             | 0             |       | 1              | 8                 | 16           |        | ш                |

| FF00H             | P0       | 0                                                           | 0                        | 0    | 0    | 0    | 0             | P01           | P00           | R/W   | $\checkmark$   | $\checkmark$      | -            | 00H    | 172              |

| FF01H             | -        | -                                                           | -                        | -    | -    | -    | -             | -             | -             | -     | -              | -                 | -            | -      | -                |

| FF02H             | P2       | 0                                                           | 0                        | P25  | P24  | P23  | P22           | P21           | P20           | R/W   | $\checkmark$   | $\checkmark$      | _            | 00H    | 172              |

| FF03H             | P3       | 0                                                           | 0                        | 0    | 0    | 0    | P32           | P31           | P30           | R/W   | $\checkmark$   | $\checkmark$      | -            | 00H    | 172              |

| FF04H             | -        | -                                                           | _                        | _    | _    | -    | _             | -             | _             | -     | -              | _                 | _            | -      | _                |

| FF05H             | -        | -                                                           | -                        | -    | -    | -    | -             | -             | -             | -     | -              | -                 | -            | -      | -                |

| FF06H             | P6       | 0                                                           | 0                        | 0    | 0    | 0    | 0             | P61           | P60           | R/W   | $\checkmark$   | $\checkmark$      | -            | 00H    | 172              |

| FF07H             | -        | -                                                           | _                        | _    | _    | -    | _             | -             | _             | -     | -              | _                 | _            | -      | -                |

| FF08H             | AD ADCRL | 1                                                           | -                        | I    | I    | 1    | _             | _             | -             | R     | I              | $\checkmark$      | _            | 00H    | 411              |

| FF09H             | CR       | 0                                                           | 0                        | 0    | 0    | 0    | 0             | _             | -             | R     | -              | _                 | $\checkmark$ | 0000H  | 410              |

| FF0AH             | RXB6     | 1                                                           | -                        | -    | -    | -    | -             | -             | -             | R     | -              | $\checkmark$      | _            | FFH    | 452              |

| <b>FF0BH</b>      | TXB6     | I                                                           | -                        | I    | -    | I    | -             | _             | -             | R/W   | I              | $\checkmark$      | -            | FFH    | 453              |

| FF0CH             | P12      | 0                                                           | 0                        | P125 | 0    | 0    | P122          | P121          | 0             | R     | $\checkmark$   | $\checkmark$      | _            | 00H    | 172              |

| FF0DH             | ADCRH    | _                                                           | -                        | _    | -    | -    | -             | _             | -             | R     | -              | $\checkmark$      | _            | 00H    | 411              |

| FF0EH             | ADS      | 0                                                           | <adoas><br/>Note</adoas> | 0    | 0    | 0    | <ads2></ads2> | <ads1></ads1> | <ads0></ads0> | R/W   | $\checkmark$   | $\checkmark$      | _            | 00H    | 412, 439         |

| <b>FF0FH</b>      | -        | _                                                           |                          | _    | _    | -    | _             | _             | _             | _     | _              | _                 | _            | -      | _                |

| FF10H             | ТМОО     | _                                                           | -                        | _    | -    | -    | -             | _             | -             | R     | _              | _                 |              | 0000H  | 243              |

| FF11H             | TIVIOU   | -                                                           | -                        | -    | -    | -    | _             | _             | -             | n     | _              |                   | v            | 00000  | 243              |

| FF12H             | CR000    | _                                                           | _                        | -    | -    | 1    | _             | _             | _             | R/W   | _              | _                 |              | 0000H  | 244              |

| FF13H             | 011000   | _                                                           | _                        | -    | -    | 1    | _             | _             | _             | 10/00 |                |                   | Ŷ            | 000011 | 244              |

| FF14H             | CR010    | _                                                           | _                        | _    | -    | -    | _             | _             | _             | R/W   | _              | _                 |              | 0000H  | 244              |

| FF15H             | 011010   | -                                                           | -                        | -    | -    | -    | -             | -             | -             | 10,00 |                |                   | `            | 000011 | 211              |

| FF16H to<br>FF19H | -        | -                                                           | -                        | -    | -    | -    | -             | -             | -             | -     | -              | -                 | -            | -      | -                |

| FF1AH             | CMP01    | _                                                           | _                        | -    | -    | 1    | _             | _             | _             | R/W   | -              | $\checkmark$      | _            | 00H    | 338              |

| FF1BH             | CMP11    | -                                                           | -                        | -    | -    | -    | -             | _             | -             | R/W   | -              | $\checkmark$      | -            | 00H    | 338              |

| FF1CH to<br>FF1EH | -        | -                                                           | -                        | _    | -    | _    | -             | -             | -             | -     | -              | -                 | _            | -      | _                |

| FF1FH             | TM51     | -                                                           | -                        | -    | -    | -    | -             | -             | -             | R     | -              | $\checkmark$      | _            | 00H    | 317              |

| FF20H             | PM0      | 1                                                           | 1                        | 1    | 1    | 1    | 1             | PM01          | PM00          | R/W   | $\checkmark$   | $\checkmark$      | _            | FFH    | 167, 256         |

| FF21H             | -        | -                                                           | -                        | -    | -    | -    | -             | -             | -             | -     | -              | _                 | _            | -      | -                |

| FF22H             | PM2      | 1                                                           | 1                        | PM25 | PM24 | PM23 | PM22          | PM21          | PM20          | R/W   | V              | V                 | -            | FFH    | 167, 415,<br>440 |

| FF23H             | PM3      | 1                                                           | 1                        | 1    | 1    | 1    | PM32          | PM31          | PM30          | R/W   | $\checkmark$   | V                 | -            | FFH    | 167, 324,<br>345 |

| FF24H             | -        | _                                                           | _                        | -    | _    | -    | _             | _             | _             |       | _              | _                 | _            | _      | -                |

| FF25H             | -        | -                                                           | -                        | -    | -    | -    | -             | -             | _             |       | -              | _                 | -            | -      | -                |

Table 3-7. Special Function Register List: 78K0/KA2-L (20-pin products) (1/4)

**Note** This bit is incorporated only in products with operational amplifier.

**Remark** For a bit name enclosed in angle brackets (<>), the bit name is defined as a reserved word in the RA78K0, and is defined as an sfr variable using the #pragma sfr directive in the CC78K0.

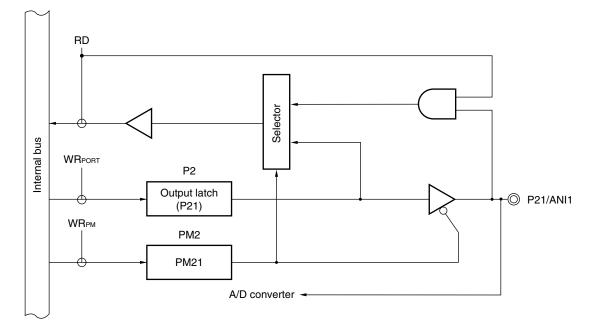

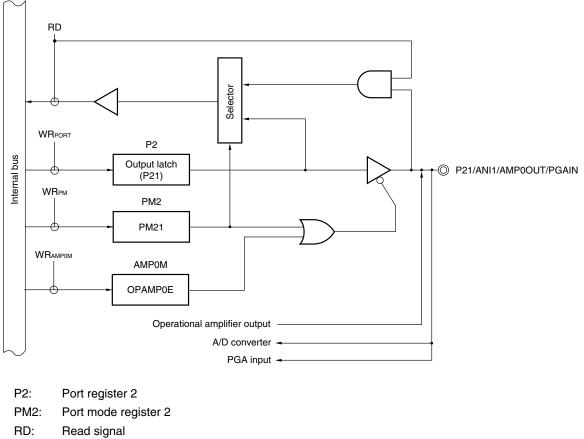

Figure 4-12. Block Diagram of P21

## (1) Products without operational amplifier

## <R>(2) Products with operational amplifier

WR××: Write signal

Remark PGA: Programmable Gain Amplifier

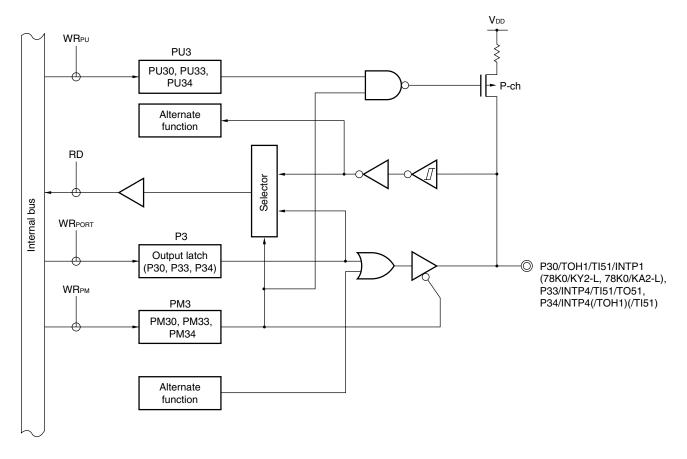

## Figure 4-15. Block Diagram of P30 (78K0/KY2-L, 78K0/KA2-L), P33, P34

- P3: Port register 3

- PU3: Pull-up resistor option register 3

- PM3: Port mode register 3

- RD: Read signal

- WR××: Write signal

<R>

## (5) Port output mode register 6 (POM6)

This register sets the output mode of P60 to P63 in 1-bit units. During  $I^2C$  communication, set POM60 and POM61 to 1.

In the 78K0/KY2-L and 78K0/KA2-L, clear POM60 to 0 when using the P60/TxD6/SCLA0 pin as the data output of serial interface UART6.

This register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Figure 4-46. Format of Port Output Mode Register 6 (POM6)

Address: FF2AH After reset: 00H R/W

Symbol 7 6 5 3 2 1 0 4 POM63<sup>Note</sup> POM62<sup>Note</sup> POM6 0 0 0 0 POM61 POM60

| POM6n | P6n pin output mode selection $(n = 0 \text{ to } 3)$ |

|-------|-------------------------------------------------------|

| 0     | Normal output (CMOS output) mode                      |

| 1     | N-ch open drain output (VDD tolerance) mode           |

#### Note 78K0/KC2-L only

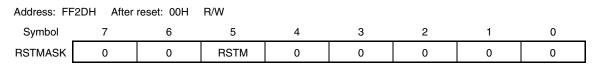

#### (6) Reset pin mode register (RSTMASK)

This register sets the pin function of  $\overrightarrow{\mathsf{RESET}}/\mathsf{P125}$  (external reset input/input-dedicated port). This register can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

#### Figure 4-47. Format of Reset Pin Mode Register (RSTMASK)

| RSTM | RESET/P125 pin function selection     |

|------|---------------------------------------|

| 0    | Using as external reset input (RESET) |

| 1    | Using as input-dedicated port (P125)  |

#### (3) Example of setting procedure when stopping the internal high-speed oscillation clock

- The internal high-speed oscillation clock can be stopped in the following two ways.

- Executing the STOP instruction to set the STOP mode

- Setting RSTOP to 1 and stopping the internal high-speed oscillation clock

#### (a) To execute a STOP instruction

<1> Setting of peripheral hardware

Stop peripheral hardware that cannot be used in the STOP mode (for peripheral hardware that cannot be used in STOP mode, refer to **CHAPTER 19 STANDBY FUNCTION**).

<2> Setting the X1 clock oscillation stabilization time after standby release

When the CPU is operating on the X1 clock, set the value of the OSTS register before the STOP instruction is executed. To operate the CPU immediately after the STOP mode has been released, set MCM0 to 0, switch the CPU clock to the internal high-speed oscillation clock, and check that RSTS is 1.

<3> Executing the STOP instruction When the STOP instruction is executed, the system is placed in the STOP mode and internal high-speed oscillation clock is stopped.

#### (b) To stop internal high-speed oscillation clock by setting RSTOP to 1

<1> Confirming the CPU clock status (PCC and MCM registers)

Confirm with CLS and MCS that the CPU is operating on a clock other than the internal high-speed oscillation clock.

When CLS = 0 and MCS = 0, the internal high-speed oscillation clock is supplied to the CPU, so change the CPU clock to a clock other than the internal high-speed oscillation clock.

#### • 78K0/KY2-L, 78K0/KA2-L, and 78K0/KB2-L

| MCS | CPU Clock Status                      |  |  |  |  |  |  |

|-----|---------------------------------------|--|--|--|--|--|--|

| 0   | Internal high-speed oscillation clock |  |  |  |  |  |  |

| 1   | High-speed system clock               |  |  |  |  |  |  |

#### • 78K0/KC2-L

| CLS | MCS | CPU Clock Status                      |  |  |  |  |  |  |

|-----|-----|---------------------------------------|--|--|--|--|--|--|

| 0   | 0   | Internal high-speed oscillation clock |  |  |  |  |  |  |

| 0   | 1   | High-speed system clock               |  |  |  |  |  |  |

| 1   | ×   | Subsystem clock                       |  |  |  |  |  |  |

<2> Stopping the internal high-speed oscillation clock (RCM register) When RSTOP is set to 1, internal high-speed oscillation clock is stopped.

Caution Be sure to confirm that MCS = 1 or CLS = 1 when setting RSTOP to 1. In addition, stop peripheral hardware that is operating on the internal high-speed oscillation clock.

## Figure 6-39. Example of Register Settings in Free-Running Timer Mode (2/2)

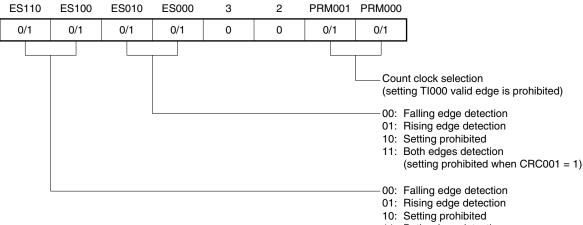

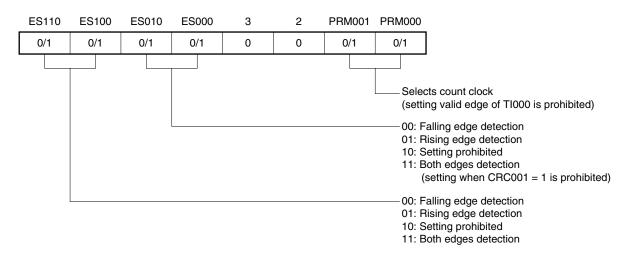

## (d) Prescaler mode register 00 (PRM00)

11: Both edges detection

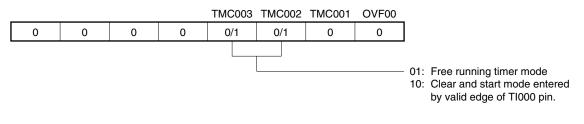

#### (e) 16-bit timer counter 00 (TM00)

By reading TM00, the count value can be read.

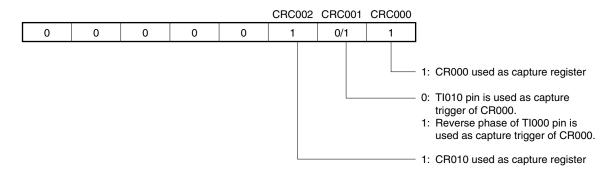

#### (f) 16-bit capture/compare register 000 (CR000)

When this register is used as a compare register and when its value matches the count value of TM00, an interrupt signal (INTTM000) is generated. The count value of TM00 is not cleared.

To use this register as a capture register, select either the TI000 or TI010 pin input as a capture trigger. When the valid edge of the capture trigger is detected, the count value of TM00 is stored in CR000.

#### (g) 16-bit capture/compare register 010 (CR010)

When this register is used as a compare register and when its value matches the count value of TM00, an interrupt signal (INTTM010) is generated. The count value of TM00 is not cleared.

When this register is used as a capture register, the TI000 pin input is used as a capture trigger. When the valid edge of the capture trigger is detected, the count value of TM00 is stored in CR010.

## Figure 6-52. Example of Register Settings for Pulse Width Measurement (1/2)

#### (a) 16-bit timer mode control register 00 (TMC00)

#### (b) Capture/compare control register 00 (CRC00)

#### (c) 16-bit timer output control register 00 (TOC00)

| _ |   | OSPT00 | OSPE00 | TOC004 | LVS00 | LVR00 | TOC001 | TOE00 |

|---|---|--------|--------|--------|-------|-------|--------|-------|

|   | 0 | 0      | 0      | 0      | 0     | 0     | 0      | 0     |

#### (d) Prescaler mode register 00 (PRM00)

| Symbol    | <7>          | 6                                                                     | 5                                                                    | 4              | <3>            | <2>                    | 1           | <0>   |  |  |  |  |  |  |  |

|-----------|--------------|-----------------------------------------------------------------------|----------------------------------------------------------------------|----------------|----------------|------------------------|-------------|-------|--|--|--|--|--|--|--|

| TMC50     | TCE50        | TMC506                                                                | 0                                                                    | 0              | LVS50          | LVR50                  | TMC501      | TOE50 |  |  |  |  |  |  |  |

|           | TCE50        |                                                                       |                                                                      | TMEO           | ount operation | apatral                |             |       |  |  |  |  |  |  |  |

|           |              | After startin                                                         |                                                                      |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | 0            |                                                                       | -                                                                    | operation disa | bled (counter  | stopped)               |             |       |  |  |  |  |  |  |  |

|           | 1            | Count opera                                                           | Count operation start                                                |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | TMC506       |                                                                       | TM50 operating mode selection                                        |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | 0            | Mode in whi                                                           | Mode in which clear & start occurs on a match between TM50 and CR50  |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | 1            | PWM (free-                                                            | PWM (free-running) mode                                              |                |                |                        |             |       |  |  |  |  |  |  |  |

|           |              | T                                                                     |                                                                      |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | LVS50        | LVR50                                                                 | VR50 Timer output F/F status setting                                 |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | 0            | 0                                                                     | No change                                                            |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | 0            | 1                                                                     | Timer output F/F clear (0) (default value of TO50 output: low level) |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | 1            | 0 Timer output F/F set (1) (default value of TO50 output: high level) |                                                                      |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | 1            | 1                                                                     | 1 Setting prohibited                                                 |                |                |                        |             |       |  |  |  |  |  |  |  |

|           | TMC501       | In of                                                                 | her modes (T                                                         | MC506 = 0)     |                | In PWM m               | ode (TMC506 | = 1)  |  |  |  |  |  |  |  |

|           |              |                                                                       | Timer F/F c                                                          | ontrol         |                | Active level selection |             |       |  |  |  |  |  |  |  |

|           | 0            | Inversion op                                                          | eration disab                                                        | led            | Active         | Active-high            |             |       |  |  |  |  |  |  |  |

|           | 1            | Inversion op                                                          | eration enabl                                                        | ed             | Active         | Active-low             |             |       |  |  |  |  |  |  |  |

|           | TOFFO        |                                                                       |                                                                      | T:-            |                |                        |             |       |  |  |  |  |  |  |  |

|           | TOE50<br>0   | Output disa                                                           | alad (TOE0 or                                                        |                | ner output cor | itroi                  |             |       |  |  |  |  |  |  |  |

|           | 1            |                                                                       | bled (TO50 ou                                                        |                | /ei)           |                        |             |       |  |  |  |  |  |  |  |

|           | 1            | Output enat                                                           | Jieu                                                                 |                |                |                        |             |       |  |  |  |  |  |  |  |

| te Bits 2 | and 3 are w  | rite-only                                                             |                                                                      |                |                |                        |             |       |  |  |  |  |  |  |  |

| Dito 2    |              | nto only.                                                             |                                                                      |                |                |                        |             |       |  |  |  |  |  |  |  |

| utions 1. | . The settin | gs of LVS5                                                            | 0 and LVR5                                                           | 0 are valid    | n other that   | n PWM moo              | le.         |       |  |  |  |  |  |  |  |

|           |              |                                                                       |                                                                      |                |                |                        |             |       |  |  |  |  |  |  |  |

#### Figure 7-9. Format of 8-Bit Timer Mode Control Register 50 (TMC50) (78K0/KB2-L, 78K0/KC2-L Only)

- <2> Set TOE50 to enable output:

- Timer output enable

- <3> Set LVS50, LVR50 (refer to Caution 1): Timer F/F setting <4> Set TCE50

- 3. When TCE50 = 1, setting the other bits of TMC50 is prohibited.

- 4. The actual TO50/TI50/P17 pin output is determined depending on PM17 and P17 besides TO50 output.

Remarks 1. In PWM mode, PWM output is made inactive by clearing TCE50 to 0.

- 2. If LVS50 and LVR50 are read, the value is 0.

- 3. The values of the TMC506, LVS50, LVR50, TMC501, and TOE50 bits are reflected at the TO50 output regardless of the value of TCE50.

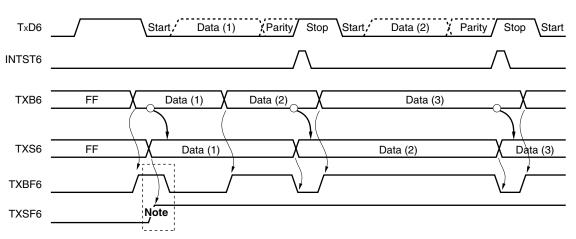

Figure 14-19 shows the timing of starting continuous transmission, and Figure 14-20 shows the timing of ending continuous transmission.

Figure 14-19. Timing of Starting Continuous Transmission

**Note** When ASIF6 is read, there is a period in which TXBF6 and TXSF6 = 1, 1. Therefore, judge whether writing is enabled using only the TXBF6 bit.

**Remark** TxD6: TxD6 pin (output)

INTST6: Interrupt request signal

- TXB6: Transmit buffer register 6

- TXS6: Transmit shift register 6

- ASIF6: Asynchronous serial interface transmission status register 6

- TXBF6: Bit 1 of ASIF6

- TXSF6: Bit 0 of ASIF6

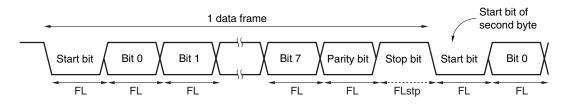

#### (5) Data frame length during continuous transmission

When data is continuously transmitted, the data frame length from a stop bit to the next start bit is extended by two clocks of base clock from the normal value. However, the result of communication is not affected because the timing is initialized on the reception side when the start bit is detected.

#### Figure 14-28. Data Frame Length During Continuous Transmission

Where the 1-bit data length is FL, the stop bit length is FLstp, and base clock frequency is fxclk6, the following expression is satisfied.

FLstp = FL + 2/fxclk6

Therefore, the data frame length during continuous transmission is:

Data frame length =  $11 \times FL + 2/f_{XCLK6}$

| l                                                                                                | <7>                                                                                                                                                                                                         | <6>                                                                                                                                                                                                                                              | <5>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <4>                                                                                                                                             | <3>                                                                                                                                                 | <2>                                                                                                                                                                                                                      | <1>                                                                                                                           | <0>                                                 | _                |  |  |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|--|--|--|--|

| .0                                                                                               | IICE0                                                                                                                                                                                                       | LREL0                                                                                                                                                                                                                                            | WREL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SPIE0                                                                                                                                           | WTIM0                                                                                                                                               | ACKE0                                                                                                                                                                                                                    | STT0                                                                                                                          | SPT0                                                |                  |  |  |  |  |

| Γ                                                                                                | IICE0                                                                                                                                                                                                       |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 | l <sup>2</sup> C op                                                                                                                                 | eration enabl                                                                                                                                                                                                            | e                                                                                                                             |                                                     |                  |  |  |  |  |

|                                                                                                  | 0                                                                                                                                                                                                           | Stop operat                                                                                                                                                                                                                                      | tion. Reset th                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ne IICA statu                                                                                                                                   | us register 0                                                                                                                                       | (IICAS0) <sup>Note 1</sup> .                                                                                                                                                                                             | Stop intern                                                                                                                   | al operation.                                       |                  |  |  |  |  |

|                                                                                                  | 1                                                                                                                                                                                                           | Enable ope                                                                                                                                                                                                                                       | ration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |                                                                                                                                                     |                                                                                                                                                                                                                          |                                                                                                                               |                                                     |                  |  |  |  |  |

| E                                                                                                | Be sure to                                                                                                                                                                                                  | set this bit (1                                                                                                                                                                                                                                  | ) while the SC                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CLA0 and SI                                                                                                                                     | DLA0 lines a                                                                                                                                        | re at high lev                                                                                                                                                                                                           | el.                                                                                                                           |                                                     |                  |  |  |  |  |

| (                                                                                                | Condition for clearing (IICE0 = 0) Condition for setting (IICE0 = 1)                                                                                                                                        |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |                                                                                                                                                     |                                                                                                                                                                                                                          |                                                                                                                               |                                                     |                  |  |  |  |  |

|                                                                                                  | <ul><li>Cleared b</li><li>Reset</li></ul>                                                                                                                                                                   | by instruction                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 | •                                                                                                                                                   | Set by instru                                                                                                                                                                                                            | ction                                                                                                                         |                                                     |                  |  |  |  |  |

|                                                                                                  | LREL0 <sup>Note s 2,3</sup>                                                                                                                                                                                 |                                                                                                                                                                                                                                                  | Exit from communications                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |                                                                                                                                                     |                                                                                                                                                                                                                          |                                                                                                                               |                                                     |                  |  |  |  |  |

|                                                                                                  | 0                                                                                                                                                                                                           | Normal ope                                                                                                                                                                                                                                       | eration                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |                                                                                                                                                     |                                                                                                                                                                                                                          |                                                                                                                               |                                                     |                  |  |  |  |  |

|                                                                                                  |                                                                                                                                                                                                             | Its uses inc<br>The SCLAC                                                                                                                                                                                                                        | This exits from the current communications and sets standby mode. This setting is automatically cleared<br>to 0 after being executed.<br>Its uses include cases in which a locally irrelevant extension code has been received.<br>The SCLA0 and SDAA0 lines are set to high impedance.<br>The following flags of IICA control register 0 (IICACTL0) and IICA status register 0 (IICAS0) are cleared<br>to 0.<br>• STT0 • SPT0 • MSTS0 • EXC0 • COI0 • TRC0 • ACKD0 • STD0 |                                                                                                                                                 |                                                                                                                                                     |                                                                                                                                                                                                                          |                                                                                                                               |                                                     |                  |  |  |  |  |

|                                                                                                  | The standl conditions                                                                                                                                                                                       | by mode follo                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |                                                                                                                                                     |                                                                                                                                                                                                                          |                                                                                                                               |                                                     | mmunications en  |  |  |  |  |

| •                                                                                                | conditions<br>• After a st<br>• An addre                                                                                                                                                                    | by mode follo<br>are met.<br>op condition i                                                                                                                                                                                                      | owing exit fro<br>is detected, re<br>extension cod                                                                                                                                                                                                                                                                                                                                                                                                                         | om commun<br>estart is in m                                                                                                                     | nications rem<br>naster mode.<br>occurs after                                                                                                       | nains in effec                                                                                                                                                                                                           | et until the f                                                                                                                | ollowing cor                                        | mmunications en  |  |  |  |  |

|                                                                                                  | conditions<br>• After a st<br>• An addre<br>Condition f                                                                                                                                                     | by mode follo<br>are met.<br>op condition i<br>ss match or e<br>or clearing (L                                                                                                                                                                   | owing exit fro<br>is detected, re<br>extension cod                                                                                                                                                                                                                                                                                                                                                                                                                         | om commun<br>estart is in m<br>e reception                                                                                                      | aster mode.<br>occurs after                                                                                                                         | nains in effect                                                                                                                                                                                                          | et until the f<br>dition.<br>etting (LREL                                                                                     | ollowing cor                                        | mmunications en  |  |  |  |  |

| ()<br>()<br>()                                                                                   | conditions<br>• After a st<br>• An addre<br>Condition f<br>• Automation                                                                                                                                     | by mode follo<br>are met.<br>op condition i<br>ss match or e<br>or clearing (L<br>cally cleared                                                                                                                                                  | owing exit fro<br>is detected, re<br>extension cod<br>REL0 = 0)                                                                                                                                                                                                                                                                                                                                                                                                            | om commun<br>estart is in m<br>e reception                                                                                                      | aster mode.<br>occurs after<br>C                                                                                                                    | the start condition for s                                                                                                                                                                                                | et until the f<br>dition.<br>etting (LREL                                                                                     | ollowing cor                                        | nmunications en  |  |  |  |  |

| ()<br>()<br>()                                                                                   | conditions<br>• After a st<br>• An addre<br>Condition f<br>• Automati<br>• Reset                                                                                                                            | by mode follo<br>are met.<br>op condition i<br>ss match or e<br>or clearing (L<br>cally cleared                                                                                                                                                  | owing exit fro<br>is detected, re<br>extension cod<br>REL0 = 0)<br>after executio                                                                                                                                                                                                                                                                                                                                                                                          | om commun<br>estart is in m<br>e reception                                                                                                      | aster mode.<br>occurs after<br>C                                                                                                                    | the start cond<br>condition for s<br>Set by instru                                                                                                                                                                       | et until the f<br>dition.<br>etting (LREL                                                                                     | ollowing cor                                        | mmunications en  |  |  |  |  |

| ()<br>()<br>()                                                                                   | conditions<br>• After a st<br>• An addre<br>Condition f<br>• Automati<br>• Reset<br>WREL0 <sup>Ndes2.3</sup>                                                                                                | by mode follo<br>are met.<br>op condition i<br>ss match or e<br>for clearing (L<br>cally cleared                                                                                                                                                 | owing exit fro<br>is detected, re<br>extension cod<br>REL0 = 0)<br>after executio                                                                                                                                                                                                                                                                                                                                                                                          | om commun<br>estart is in m<br>e reception<br>on                                                                                                | aster mode.<br>occurs after<br>C<br>•<br>Wait                                                                                                       | the start condition for s<br>Set by instru-                                                                                                                                                                              | at until the f<br>dition.<br>etting (LREL<br>ction                                                                            | ollowing cor                                        | nmunications en  |  |  |  |  |

| (<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>, | conditions<br>• After a st<br>• An addre<br>Condition f<br>• Automati<br>• Reset<br>WREL0 <sup>Notes23</sup><br>0<br>1<br>When WRF                                                                          | by mode follo<br>are met.<br>op condition is<br>ss match or e<br>for clearing (L<br>cally cleared<br>Do not can<br>Cancel wait<br>EL0 is set (wa                                                                                                 | owing exit fro<br>is detected, re<br>extension cod<br>REL0 = 0)<br>after execution<br>cel wait<br>t. This setting                                                                                                                                                                                                                                                                                                                                                          | om commun<br>estart is in m<br>e reception<br>on<br>g is automat<br>during the w                                                                | ications rem<br>haster mode.<br>occurs after<br>C<br>C<br>•<br>Wait<br>ically cleared<br>ait period at                                              | the start condition for s<br>Set by instru-<br>cancellation<br>d after wait is<br>the ninth cloo                                                                                                                         | at until the f<br>dition.<br>etting (LREL<br>ction                                                                            | ollowing cor<br>_0 = 1)                             | ion status (TRC0 |  |  |  |  |

|                                                                                                  | conditions<br>• After a st<br>• An addre<br>Condition f<br>• Automation<br>• Reset<br>WREL0 <sup>Notes2.3</sup><br>0<br>1<br>When WRH<br>1), the SD/                                                        | by mode follo<br>are met.<br>op condition is<br>ss match or e<br>for clearing (L<br>cally cleared<br>Do not can<br>Cancel wait<br>EL0 is set (wa                                                                                                 | owing exit fro<br>is detected, re<br>extension cod<br>.REL0 = 0)<br>after execution<br>cel wait<br>t. This setting<br>ait canceled) of<br>s into the high                                                                                                                                                                                                                                                                                                                  | om commun<br>estart is in m<br>e reception<br>on<br>g is automat<br>during the w                                                                | ications rem<br>haster mode.<br>occurs after<br>C<br>C<br>•<br>•<br>Wait<br>ically cleared<br>ait period at<br>state (TRCC                          | the start condition for s<br>Set by instru-<br>cancellation<br>d after wait is<br>the ninth cloo                                                                                                                         | t until the f<br>dition.<br>etting (LREL<br>ction<br>canceled.<br>ck pulse in th                                              | ollowing cor<br>_0 = 1)<br>ne transmiss             |                  |  |  |  |  |

|                                                                                                  | conditions<br>• After a st<br>• An addre<br>Condition f<br>• Automati<br>• Reset<br>WREL0 <sup>Notes2,3</sup><br>0<br>1<br>When WRF<br>1), the SD/<br>Condition f                                           | by mode follo<br>are met.<br>op condition is<br>ss match or e<br>for clearing (L<br>cally cleared<br>Do not can<br>Cancel wait<br>EL0 is set (wat<br>AA0 line goes<br>or clearing (V                                                             | owing exit fro<br>is detected, re<br>extension cod<br>.REL0 = 0)<br>after execution<br>cel wait<br>t. This setting<br>ait canceled) of<br>s into the high                                                                                                                                                                                                                                                                                                                  | om commun<br>estart is in m<br>e reception<br>on<br>g is automat<br>during the w<br>impedance                                                   | ications rem<br>haster mode.<br>occurs after<br>C<br>C<br>•<br>•<br>Wait<br>ically cleared<br>ait period at<br>state (TRCC                          | the start condition for s<br>Set by instru-<br>concellation<br>d after wait is<br>the ninth cloo<br>0 = 0).                                                                                                              | t until the f<br>dition.<br>etting (LREL<br>ction<br>canceled.<br>ck pulse in th<br>etting (WRE                               | ollowing cor<br>_0 = 1)<br>ne transmiss             |                  |  |  |  |  |

|                                                                                                  | conditions<br>• After a st<br>• An addre<br>Condition f<br>• Automati<br>• Reset<br>WREL0 <sup>Nutes23</sup><br>0<br>1<br>When WRI<br>1), the SD/<br>Condition f<br>• Automati<br>• Reset<br>Notes 1.       | by mode follo<br>are met.<br>op condition is<br>ss match or e<br>for clearing (L<br>cally cleared<br>Do not can<br>Cancel wai<br>EL0 is set (wa<br>AA0 line goes<br>for clearing (V<br>cally cleared<br>The IICAS<br>bits of the                 | owing exit fro<br>is detected, re<br>extension cod<br>REL0 = 0)<br>after execution<br>cel wait<br>t. This setting<br>ait canceled) of<br>s into the high<br>VREL0 = 0)<br>after execution<br>0 register, t<br>IICACTL1 re                                                                                                                                                                                                                                                  | om commun<br>estart is in m<br>e reception<br>on<br>g is automat<br>during the w<br>impedance<br>on<br>he STCF a<br>egister are                 | ications rem<br>haster mode.<br>occurs after<br>C<br>C<br>Vait<br>ically cleared<br>rait period at<br>state (TRCC<br>C<br>C<br>and IICBSN<br>reset. | the start condition for s<br>Set by instru-<br>cancellation<br>d after wait is<br>the ninth cloo<br>0 = 0.<br>Sondition for s<br>Set by instru-                                                                          | t until the f<br>dition.<br>etting (LREL<br>ction<br>canceled.<br>ck pulse in th<br>etting (WRE<br>ction<br>e IICAF0 re       | ollowing cor<br>_0 = 1)<br>he transmiss<br>iL0 = 1) |                  |  |  |  |  |

|                                                                                                  | conditions<br>• After a st<br>• An addre<br>Condition f<br>• Automati<br>• Reset<br>WREL0 <sup>Notes23</sup><br>0<br>1<br>When WRH<br>1), the SD/<br>Condition f<br>• Automati<br>• Reset<br>Notes 1.<br>2. | by mode follo<br>are met.<br>op condition is<br>ss match or e<br>for clearing (L<br>cally cleared<br>Do not cand<br>Cancel wait<br>EL0 is set (wat<br>AA0 line goes<br>for clearing (V<br>cally cleared<br>The IICAS<br>bits of the line signals | owing exit fro<br>is detected, re<br>extension cod<br>REL0 = 0)<br>after execution<br>cel wait<br>t. This setting<br>ait canceled) of<br>s into the high<br>VREL0 = 0)<br>after execution<br>0 register, t                                                                                                                                                                                                                                                                 | pm commun<br>estart is in m<br>e reception<br>on<br>g is automat<br>during the w<br>impedance<br>on<br>he STCF a<br>egister are<br>its are inva | ically cleared<br>attack (TRCC)<br>and IICBS)<br>reset.                                                                                             | the start condition for s<br>Set by instru-<br>condition for s<br>Set by instru-<br>cancellation<br>d after wait is<br>the ninth cloo<br>0 = 0).<br>Condition for s<br>Set by instru-<br>f bits of the<br>e IICE0 bit is | t until the f<br>dition.<br>etting (LREL<br>ction<br>canceled.<br>ck pulse in th<br>etting (WRE<br>ction<br>IICAF0 re<br>s 0. | ollowing cor<br>_0 = 1)<br>he transmiss<br>iL0 = 1) | ion status (TRC0 |  |  |  |  |

## Figure 15-5. Format of IICA Control Register 0 (IICACTL0) (1/4)

Caution If the operation of  $I^2C$  is enabled (IICE0 = 1) when the SCLA0 line is high level, the SDAA0 line is low level, and the digital filter is turned on (DFC0 of the IICACTL1 register = 1), a start condition will be inadvertently detected immediately. In this case, set (1) the LREL0 bit by using a 1-bit memory manipulation instruction immediately after enabling operation of  $I^2C$ (IICE0 = 1).

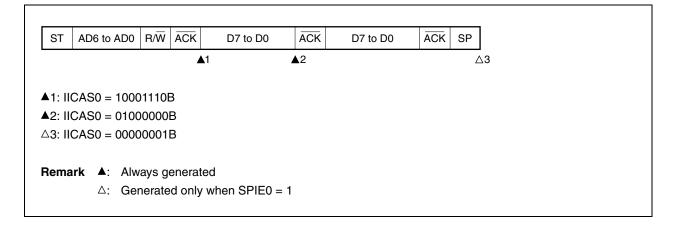

#### (b) When arbitration loss occurs during transmission of extension code

| ST AD                                        | 6 to AD0                                  | R/W                           | ACK                              | D7 to D0          | ACK | D7 to D0 | ACK | SP |

|----------------------------------------------|-------------------------------------------|-------------------------------|----------------------------------|-------------------|-----|----------|-----|----|

|                                              |                                           |                               | 1                                |                   |     |          |     |    |

| ▲1: IICAS<br>Sets LRE<br>△2: IICAS<br>Remark | L0 = 1 by<br>0 = 0000<br>▲: Alw<br>△: Ger | v softwa<br>00001E<br>vays ge | are<br>3<br>enerated<br>d only w | l<br>/hen SPIE0 = | 1   |          |     |    |

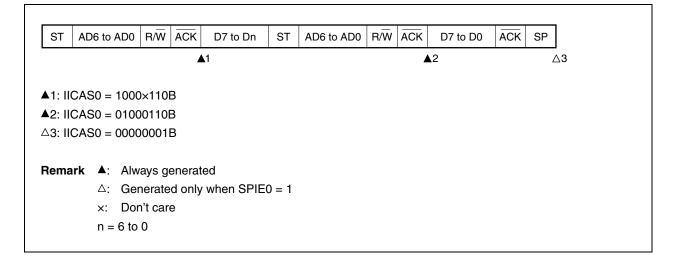

## (c) When arbitration loss occurs during transmission of data

#### (i) When WTIM0 = 0

#### (ii) When WTIM0 = 1

| <b></b>         |                      | _       |          |              | 11  |          | 11  |    | ٦  |

|-----------------|----------------------|---------|----------|--------------|-----|----------|-----|----|----|

| ST              | AD6 to AD0           | R/W     | ACK      | D7 to D0     | ACK | D7 to D0 | ACK | SP |    |

|                 |                      |         | ▲1       |              |     | 2        |     | Δ  | ∆3 |

|                 |                      |         |          |              |     |          |     |    |    |

| <b>▲</b> 1: II  | CAS0 = 1000          | 1110B   | }        |              |     |          |     |    |    |

| <b>▲</b> 2: II  | CAS0 = 0100          | 0100E   | 3        |              |     |          |     |    |    |

| ∆ <b>3</b> : II | CAS0 = 0000          | 0001E   | 3        |              |     |          |     |    |    |

|                 |                      |         |          |              |     |          |     |    |    |

| Rema            | n <b>rk ≜</b> : Alwa | ays ge  | enerated | b            |     |          |     |    |    |

|                 | ∆: Ger               | nerated | d only v | when SPIE0 = | 1   |          |     |    |    |

|                 |                      |         |          |              |     |          |     |    |    |

#### (d) When loss occurs due to restart condition during data transfer

#### (i) Not extension code (Example: unmatches with SVA0)

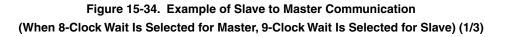

#### (1) Start condition ~ address

Notes 1. To cancel master wait, write "FFH" to IICA or set WREL0.

2. Write data to IICA, not setting WREL0, in order to cancel a wait state during slave transmission.

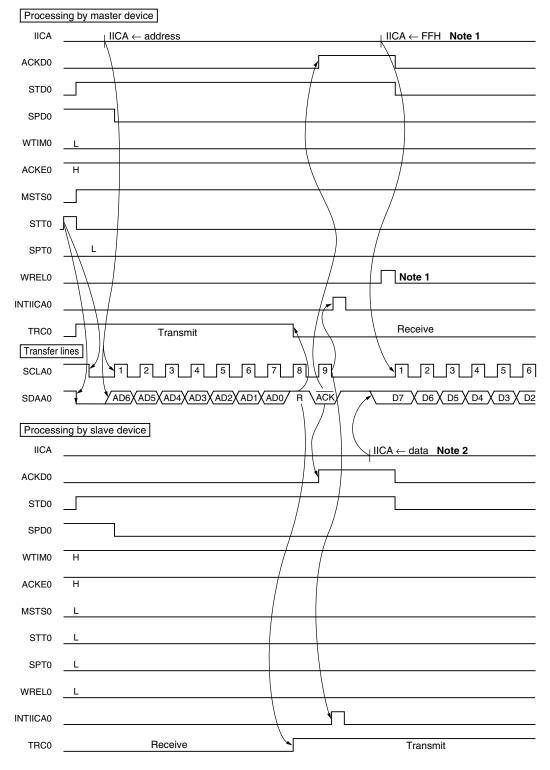

PM0, PM1, PM3, PM4, PM6, and PM12 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets these registers to FFH.

#### <R>

#### Figure 16-9. Format of Port Mode Register 0 (PM0)

Address: FF20H After reset: FFH R/W

#### Notes 1. 32-pin products only

- **2.** 25-pin products only

- **Remark** The figure shown above presents the format of port mode register 1 of the 78K0/KB2-L and 78K0/KA2-L (25, 32-pin products).

#### Figure 16-10. Format of Port Mode Register 1 (PM1)

| Address: | FF21H A | fter reset: FI | H R/W |      |      |      |      |      |

|----------|---------|----------------|-------|------|------|------|------|------|

| Symbol   | 7       | 6              | 5     | 4    | 3    | 2    | 1    | 0    |

| PM1      | PM17    | PM16           | PM15  | PM14 | PM13 | PM12 | PM11 | PM10 |

|          |         |                |       |      |      |      |      |      |

|   | PM1n | P1n pin I/O mode selection (n = 0 to 7) |  |  |  |  |  |

|---|------|-----------------------------------------|--|--|--|--|--|

|   | 0    | Output mode (output buffer on)          |  |  |  |  |  |

| 1 | 1    | Input mode (output buffer off)          |  |  |  |  |  |

**Remark** The figure shown above presents the format of port mode register 1 of the 78K0/KB2-L and 78K0/KC2-L.

#### <R>

#### Figure 16-11. Format of Port Mode Register 3 (PM3)

Address: FF23H After reset: FFH R/W Symbol 6 5 2 0 7 4 3 1 РМ3 PM37 PM36 PM35 PM34 PM33 PM32 PM31 PM30

| PM3n | P3n pin I/O mode selection (n = 0 to 7) |  |  |  |  |

|------|-----------------------------------------|--|--|--|--|

| 0    | Output mode (output buffer on)          |  |  |  |  |

| 1    | Input mode (output buffer off)          |  |  |  |  |

**Remark** The figure shown above presents the format of port mode register 1 of the 78K0/KB2-L and 78K0/KA2-L (25, 32-pin products).

# <R>

# Figure 17-6. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H) (40-pin products of 78K0/KC2-L)

| Address: FF | E0H After r                                                | eset: 00H R/ | W             |                |               |         |         |         |

|-------------|------------------------------------------------------------|--------------|---------------|----------------|---------------|---------|---------|---------|

| Symbol      | <7>                                                        | <6>          | <5>           | <4>            | <3>           | <2>     | <1>     | <0>     |

| IF0L        | SREIF6                                                     | PIF5         | PIF4          | PIF3           | PIF2          | PIF1    | PIF0    | LVIIF   |

|             |                                                            |              |               |                |               |         |         |         |

| Address: FF | EIH Atter r                                                | eset: 00H I  | R/W           |                |               |         |         |         |

| Symbol      | <7>                                                        | <6>          | <5>           | <4>            | <3>           | <2>     | <1>     | <0>     |

| IF0H        | TMIF010                                                    | TMIF000      | TMIF50        | TMIFH0         | TMIFH1        | CSIIF10 | STIF6   | SRIF6   |

|             |                                                            |              |               |                |               |         |         |         |

| Address: FF | E2H After r                                                | eset: 00H I  | R/W           |                |               |         |         |         |

| Symbol      | 7                                                          | 6            | <5>           | <4>            | <3>           | <2>     | 1       | <0>     |

| IF1L        | 0                                                          | 0            | RTCIF         | KRIF           | TMIF51        | RTCIIF  | 0       | ADIF    |

|             |                                                            |              |               |                |               |         |         |         |

| Address: FF | E3H After r                                                | eset: 00H I  | R/W           |                |               |         |         |         |

| Symbol      | 7                                                          | 6            | 5             | <4>            | <3>           | <2>     | <1>     | <0>     |

| IF1H        | 0                                                          | 0            | 0             | PIF11          | PIF10         | PIF9    | CSIIF11 | IICAIF0 |

|             |                                                            | -            |               |                |               |         |         |         |

|             | XXIFX                                                      |              |               | Inte           | rrupt request | flag    |         |         |

|             | 0                                                          | No interrupt | request signa | l is generated |               |         |         |         |

|             | 1 Interrupt request is generated, interrupt request status |              |               |                |               |         |         |         |

Caution Be sure to clear bits 1, 6, and 7 of IF1L, and bits 5 to 7 of IF1H to 0.

# 27.2 Operation List

| Instruction | Mnemonic | Onerende       | Bytes | Clocks |        | Operation                       | ľ | Flag  |