# E. Renesas Electronics America Inc - UPD78F0571MC-CAB-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                  |

|----------------------------|--------------------------------------------------------------------------------------|

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 21                                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 512 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 7x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 30-LSSOP (0.240", 6.10mm Width)                                                      |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0571mc-cab-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address           | Symbol   |   |                          |      | Bit  | No.  |               |               |               | R/W   | R/W Number of Bits<br>Manipulated<br>Simultaneously |              | After<br>Reset | Reference<br>page |                  |

|-------------------|----------|---|--------------------------|------|------|------|---------------|---------------|---------------|-------|-----------------------------------------------------|--------------|----------------|-------------------|------------------|

|                   |          | 7 | 6                        | 5    | 4    | 3    | 2             | 1             | 0             |       | 1                                                   | 8            | 16             |                   | ш                |

| FF00H             | P0       | 0 | 0                        | 0    | 0    | 0    | 0             | P01           | P00           | R/W   | $\checkmark$                                        | $\checkmark$ | -              | 00H               | 172              |

| FF01H             | -        | - | -                        | -    | -    | -    | -             | -             | -             | -     | -                                                   | -            | -              | -                 | -                |

| FF02H             | P2       | 0 | 0                        | P25  | P24  | P23  | P22           | P21           | P20           | R/W   | $\checkmark$                                        | $\checkmark$ | _              | 00H               | 172              |

| FF03H             | P3       | 0 | 0                        | 0    | 0    | 0    | P32           | P31           | P30           | R/W   | $\checkmark$                                        | $\checkmark$ | -              | 00H               | 172              |

| FF04H             | -        | - | _                        | _    | _    | -    | _             | -             | _             | -     | -                                                   | _            | _              | -                 | _                |

| FF05H             | -        | - | -                        | -    | -    | -    | -             | -             | -             | -     | -                                                   | -            | -              | -                 | -                |

| FF06H             | P6       | 0 | 0                        | 0    | 0    | 0    | 0             | P61           | P60           | R/W   | $\checkmark$                                        | $\checkmark$ | -              | 00H               | 172              |

| FF07H             | -        | - | _                        | _    | _    | -    | _             | -             | _             | -     | -                                                   | _            | _              | -                 | -                |

| FF08H             | AD ADCRL | 1 | -                        | I    | I    | 1    | _             | _             | -             | R     | I                                                   | $\checkmark$ | _              | 00H               | 411              |

| FF09H             | CR       | 0 | 0                        | 0    | 0    | 0    | 0             | _             | -             | R     | -                                                   | _            | $\checkmark$   | 0000H             | 410              |

| FF0AH             | RXB6     | 1 | -                        | -    | -    | -    | -             | -             | -             | R     | -                                                   | $\checkmark$ | _              | FFH               | 452              |

| <b>FF0BH</b>      | TXB6     | I | -                        | I    | -    | I    | -             | _             | _             | R/W   | I                                                   | $\checkmark$ | -              | FFH               | 453              |

| FF0CH             | P12      | 0 | 0                        | P125 | 0    | 0    | P122          | P121          | 0             | R     | $\checkmark$                                        | $\checkmark$ | _              | 00H               | 172              |

| FF0DH             | ADCRH    | - | -                        | _    | -    | -    | -             | _             | -             | R     | -                                                   | $\checkmark$ | _              | 00H               | 411              |

| FF0EH             | ADS      | 0 | <adoas><br/>Note</adoas> | 0    | 0    | 0    | <ads2></ads2> | <ads1></ads1> | <ads0></ads0> | R/W   | $\checkmark$                                        | $\checkmark$ | _              | 00H               | 412, 439         |

| <b>FF0FH</b>      | -        | _ |                          | _    | _    | -    | _             | _             | _             | _     | _                                                   | _            | _              | -                 | _                |

| FF10H             | ТМОО     | - | -                        | _    | -    | -    | -             | _             | -             | R     | _                                                   | _            |                | 0000H             | 243              |

| FF11H             | TIVIOU   | - | -                        | -    | -    | -    | _             | _             | -             | n     | _                                                   |              | v              | 00000             | 243              |

| FF12H             | CR000    | _ | _                        | -    | -    | 1    | _             | _             | _             | R/W   | _                                                   | _            |                | 0000H             | 244              |

| FF13H             | 011000   | _ | _                        | -    | -    | 1    | _             | _             | _             | 10/00 |                                                     |              | Ŷ              | 000011            | 244              |

| FF14H             | CR010    | _ | _                        | _    | -    | -    | _             | _             | _             | R/W   | _                                                   | _            |                | 0000H             | 244              |

| FF15H             | 011010   | - | -                        | -    | -    | -    | -             | -             | -             | 10,00 |                                                     |              | `              | 000011            | 211              |

| FF16H to<br>FF19H | -        | - | -                        | -    | -    | -    | -             | -             | -             | -     | -                                                   | -            | -              | -                 | -                |

| FF1AH             | CMP01    | _ | _                        | -    | -    | 1    | _             | _             | _             | R/W   | -                                                   | $\checkmark$ | _              | 00H               | 338              |

| FF1BH             | CMP11    | - | -                        | -    | -    | -    | -             | _             | -             | R/W   | -                                                   | $\checkmark$ | -              | 00H               | 338              |

| FF1CH to<br>FF1EH | -        | - | -                        | _    | -    | _    | -             | -             | -             | -     | -                                                   | -            | _              | -                 | _                |

| FF1FH             | TM51     | - | -                        | -    | -    | -    | -             | -             | -             | R     | -                                                   | $\checkmark$ | _              | 00H               | 317              |

| FF20H             | PM0      | 1 | 1                        | 1    | 1    | 1    | 1             | PM01          | PM00          | R/W   | $\checkmark$                                        | $\checkmark$ | _              | FFH               | 167, 256         |

| FF21H             | -        | - | -                        | -    | -    | -    | -             | -             | -             | -     | -                                                   | _            | _              | -                 | -                |

| FF22H             | PM2      | 1 | 1                        | PM25 | PM24 | PM23 | PM22          | PM21          | PM20          | R/W   | V                                                   | V            | -              | FFH               | 167, 415,<br>440 |

| FF23H             | PM3      | 1 | 1                        | 1    | 1    | 1    | PM32          | PM31          | PM30          | R/W   | $\checkmark$                                        | V            | -              | FFH               | 167, 324,<br>345 |

| FF24H             | -        | _ | _                        | -    | _    | -    | _             | _             | _             |       | _                                                   | _            | _              | _                 | -                |

| FF25H             | -        | - | -                        | -    | -    | -    | -             | -             | _             |       | -                                                   | _            | -              | -                 | -                |

Table 3-7. Special Function Register List: 78K0/KA2-L (20-pin products) (1/4)

**Note** This bit is incorporated only in products with operational amplifier.

**Remark** For a bit name enclosed in angle brackets (<>), the bit name is defined as a reserved word in the RA78K0, and is defined as an sfr variable using the #pragma sfr directive in the CC78K0.

# 4.2.4 Port 3

<R>

| ۲> | 78K0/KY2-L<br>(µPD78F055x) |                         | 78K0/KA2-L<br>(μPD78F056x)      |                      | 78K0/KB2-L<br>(μPD78F057x) |                         | 78K0/KC2-L<br>(µPD78F058x) |                         |

|----|----------------------------|-------------------------|---------------------------------|----------------------|----------------------------|-------------------------|----------------------------|-------------------------|

|    | 16 Pins                    | 20 Pins                 | 25 Pins                         | 32 Pins              | 30 Pins                    | 40 Pins                 | 44 Pins                    | 48 Pins                 |

|    | P30/TOH1/<br>TI51/INTP1    | P30/TOH1/<br>TI51/INTP1 | -                               | -                    | P30/INTP1                  | P30/INTP1               | P30/INTP1                  | P30/INTP1               |

|    | _                          | P31/INTP2/<br>TOOLC1    | P31/INTP2/<br>TOOLC1            | P31/INTP2/<br>TOOLC1 | P31/INTP2/<br>TOOLC1       | P31/INTP2/<br>TOOLC1    | P31/INTP2/<br>TOOLC1       | P31/INTP2/<br>TOOLC1    |

|    | _                          | P32/INTP3/<br>TOOLD1    | P32/INTP3/<br>TOOLD1            | P32/INTP3/<br>TOOLD1 | P32/INTP3/<br>TOOLD1       | P32/INTP3/<br>TOOLD1    | P32/INTP3/<br>TOOLD1       | P32/INTP3/<br>TOOLD1    |

|    | _                          | _                       | P33                             | P33                  | P33/TI51/<br>TO51/INTP4    | P33/TI51/<br>TO51/INTP4 | P33/TI51/<br>TO51/INTP4    | P33/TI51/<br>TO51/INTP4 |

|    | _                          | _                       | P34/INTP4<br>(/TOH1)<br>(/TI51) | P34/INTP4<br>(/TOH1) | _                          | _                       | _                          | -                       |

|    | _                          | _                       | P35/SCK11                       | P35/SCK11            | _                          | -                       | -                          | _                       |

|    | _                          | _                       | P36/SI11                        | P36/SI11             | -                          | _                       | _                          | -                       |

|    | _                          | _                       | P37/SO11                        | P37/SO11             | -                          | -                       | -                          | _                       |

Port 3 is an I/O port with an output latch. Port 3 can be set to the input mode or output mode in 1-bit units using port mode register 3 (PM3). When the P30 to P37 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 3 (PU3).

This port can also be used for external interrupt request input, timer I/O, clock input and data I/O for flash memory programmer/on-chip debugger, and clock I/O and data I/O for serial interface.

The timer I/O can be assigned to P34 of the 78K0/KA2-L (25-pin and 32-pin products) by setting the port alternate switch control register (MUXSEL).

Reset signal generation sets port 3 to input mode.

Figures 4-15 to 4-18 show block diagrams of port 3.

Remark For how to connect a flash memory programmer using TOOLC1/P31, TOOLD1/P32, refer to CHAPTER 25 FLASH MEMORY. For how to connect TOOLC1/P31, TOOLD1/P32 and an on-chip debug emulator, refer to CHAPTER 26 ON-CHIP DEBUG FUNCTION.

# (9) Peripheral enable register 0 (PER0)<sup>Note</sup>

<R> This register controls the clock supplied to peripheral functions other than the real-time counter. By stopping the clock supplied to such peripheral functions, the power consumption can be reduced. PER0 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

Note 78K0/KC2-L only

#### Figure 5-12. Format of Peripheral Enable Register 0 (PER0)

Address: FF25H After reset: 00H R/W

<R>

| Symbol | <7>   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|-------|---|---|---|---|---|---|---|

| PER0   | RTCEN | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| RTCEN | Control of real-time counter (RTC) input clock supply |

|-------|-------------------------------------------------------|

| 0     | Sub HALT low power consumption mode                   |

| 1     | Sub HALT normal mode <sup>Note</sup>                  |

**Note** To output the subsystem clock by using the PCL function while in the subsystem clock HALT mode, set RTCEN to 1.

Caution Be sure to clear bits 0 to 6 of PER0 to "0".

# (3) Example of setting procedure when using the subsystem clock as the CPU clock

<1> Setting subsystem clock oscillation<sup>Note</sup>

# (Refer to 5.6.3 (1) Example of setting procedure when oscillating the XT1 clock and (2) Example of setting procedure when using the external subsystem clock.)

Note The setting of <1> is not necessary when while the subsystem clock is operating.

# <2> Switching the CPU clock (PCC register)

When CSS is set to 1, the subsystem clock is supplied to the CPU.

| CSS | PCC2 | PCC1         | PCC0 | CPU Clock (fcPu) Selection |

|-----|------|--------------|------|----------------------------|

| 1   | 0    | 0            | 0    | fsuв                       |

|     | 0    | 0            | 1    |                            |

|     | 0    | 1            | 0    |                            |

|     | 0    | 1            | 1    |                            |

|     | 1    | 0            | 0    |                            |

|     | Ot   | her than abo | ve   | Setting prohibited         |

# (4) Example of setting procedure when stopping the subsystem clock

<1> Confirming the CPU clock status (PCC and MCM registers)

Confirm with CLS and MCS that the CPU is operating on a clock other than the subsystem clock.

When CLS = 1, the subsystem clock is supplied to the CPU, so change the CPU clock to a clock other than the subsystem clock.

| CLS | MCS | CPU Clock Status                      |  |  |  |  |

|-----|-----|---------------------------------------|--|--|--|--|

| 0   | 0   | Internal high-speed oscillation clock |  |  |  |  |

| 0   | 1   | High-speed system clock               |  |  |  |  |

| 1   | ×   | Subsystem clock                       |  |  |  |  |

<2> Stopping the subsystem clock (OSCCTL register) When OSCSELS is cleared to 0, XT1 oscillation is stopped (the input of the external clock is disabled).

# Cautions 1. Be sure to confirm that CLS = 0 when clearing OSCSELS to 0. In addition, stop the watch timer if it is operating on the subsystem clock.

2. The subsystem clock oscillation cannot be stopped using the STOP instruction.

01: Rising edge detection10: Setting prohibited11: Both edges detection

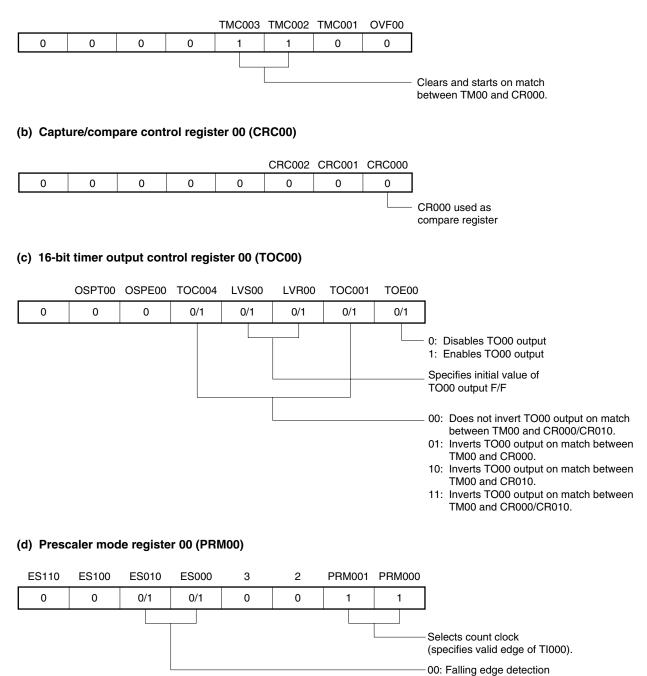

# Figure 6-21. Example of Register Settings in External Event Counter Mode (1/2)

### (a) 16-bit timer mode control register 00 (TMC00)

# Figure 6-21. Example of Register Settings in External Event Counter Mode (2/2)

# (e) 16-bit timer counter 00 (TM00)

By reading TM00, the count value can be read.

# (f) 16-bit capture/compare register 000 (CR000)

If M is set to CR000, the interrupt signal (INTTM000) is generated when the number of external events reaches (M + 1).

Setting CR000 to 0000H is prohibited.

# (g) 16-bit capture/compare register 010 (CR010)

Usually, CR010 is not used in the external event counter mode. However, a compare match interrupt (INTTM010) is generated when the set value of CR010 matches the value of TM00. Therefore, mask the interrupt request by using the interrupt mask flag (TMMK010).

# Figure 10-10. Format of Day Count Register (DAY)

| Address: FFB | 6H After res | set: 01H R/V | V     |       |      |      |      |      |

|--------------|--------------|--------------|-------|-------|------|------|------|------|

| Symbol       | 7            | 6            | 5     | 4     | 3    | 2    | 1    | 0    |

| DAY          | 0            | 0            | DAY20 | DAY10 | DAY8 | DAY4 | DAY2 | DAY1 |

# (10) Week count register (WEEK)

The WEEK register is an 8-bit register that takes a value of 0 to 6 (decimal) and indicates the count value of weekdays.

It counts up in synchronization with the day counter.

When data is written to this register, it is written to a buffer and then to the counter up to 2 clocks (32.768 kHz) later. Set a decimal value of 00 to 06 to this register in BCD code. If a value outside this range is set, the register value returns to the normal value after 1 period.

WEEK can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

#### Figure 10-11. Format of Week Count Register (WEEK)

| Address: FFB | S5H After res | set: 00H R/W | / |   |   |       |       |       |

|--------------|---------------|--------------|---|---|---|-------|-------|-------|

| Symbol       | 7             | 6            | 5 | 4 | 3 | 2     | 1     | 0     |

| WEEK         | 0             | 0            | 0 | 0 | 0 | WEEK4 | WEEK2 | WEEK1 |

Caution Values corresponding to the month count register and day count register are not automatically stored to the week count register.

Set the week count register as follows, after reset release.

| Day       | WEEK |

|-----------|------|

| Sunday    | 00H  |

| Monday    | 01H  |

| Tuesday   | 02H  |

| Wednesday | 03H  |

| Thursday  | 04H  |

| Friday    | 05H  |

| Saturday  | 06H  |

<R>

| ADPC0 Register          | PM2 Register | OPAMP0E<br>bit | PGAEN bit | ADS Register                        | P21/ANI1/AMP0OUT/PGAIN Pin                                                                        |

|-------------------------|--------------|----------------|-----------|-------------------------------------|---------------------------------------------------------------------------------------------------|

| Analog I/O<br>selection | Input mode   | 0              | 0         | Selects ANI1.                       | Analog input (to be converted into digital signals)                                               |

|                         |              |                |           | Does not select ANI1.               | Analog input (not to be converted into digital signals)                                           |

|                         |              | 0              | 1         | Selects PGAOUT.                     | PGA input (PGA output is converted into digital signals)                                          |

|                         |              |                |           | Selects ANI1.                       | PGA input (to be converted into digital signals)                                                  |

|                         |              |                |           | Does not select<br>PGAOUT and ANI1. | PGA input (not to be converted into digital signals)                                              |

|                         |              | 1              | 0         | Selects ANI1.                       | Operational amplifier 0 output (to be converted into digital signals)                             |

|                         |              |                |           | Does not select ANI1.               | Operational amplifier 0 output (not to be converted into digital signals)                         |

|                         |              | 1              | 1         | Selects PGAOUT.                     | Operational amplifier 0 output and PGA<br>input (PGA output is converted into digital<br>signals) |

|                         |              |                |           | Selects ANI1.                       | Operational amplifier 0 output (to be converted into digital signals)                             |

|                         |              |                |           | Does not select<br>PGAOUT and ANI1. | Operational amplifier 0 output (not to be converted into digital signals)                         |

|                         | Output mode  | -              | _         | -                                   | Setting prohibited                                                                                |

| Digital I/O             | Input mode   | 0              |           | Selects ANI1.                       | Setting prohibited                                                                                |

| selection               |              |                |           | Does not select ANI1.               | Digital input                                                                                     |

|                         |              | 1              |           | _                                   | Setting prohibited                                                                                |

|                         | Output mode  | 0              | _         | Selects ANI1.                       | Setting prohibited                                                                                |

|                         |              |                |           | Does not select ANI1.               | Digital output                                                                                    |

|                         |              | 1              | -         | -                                   | Setting prohibited                                                                                |

# Table 12-6. Setting Functions of P21/ANI1/AMP0OUT/PGAIN Pin

# Table 12-7. Setting Functions of P23/ANI3 to P27/ANI7 Pins

|        | ADPC0 Registe          | er PM2 Register     | ADS Register( $n = 3$ to 7)  | P23/ANI3 to P27/ANI7 Pins                               |  |  |  |  |  |

|--------|------------------------|---------------------|------------------------------|---------------------------------------------------------|--|--|--|--|--|

|        | Analog input selection | Input mode          | Selects ANIn.                | Analog input (to be converted into digital signals)     |  |  |  |  |  |

|        |                        |                     | Does not select ANIn.        | Analog input (not to be converted into digital signals) |  |  |  |  |  |

|        |                        | Output mode         | _                            | Setting prohibited                                      |  |  |  |  |  |

|        | Digital I/O            | Input mode          | Selects ANIn.                | Setting prohibited                                      |  |  |  |  |  |

|        | selection              |                     | Does not select ANIn.        | Digital input                                           |  |  |  |  |  |

|        |                        | Output mode         | Selects ANIn.                | Setting prohibited                                      |  |  |  |  |  |

|        |                        |                     | Does not select ANIn.        | Digital output                                          |  |  |  |  |  |

| Remark | ADPC0:                 | A/D port configura  | ation register 0             |                                                         |  |  |  |  |  |

|        | PM2:                   | Port mode registe   | t mode register 2            |                                                         |  |  |  |  |  |

|        | OPAMP0E:               | Bit 7 of operationa | al amplifier 0 control regis | ter (AMP0M)                                             |  |  |  |  |  |

PGAEN: Bit 6 of AMP0M

ADS: Analog input channel specification register

### (2) Asynchronous serial interface reception error status register 6 (ASIS6)

This register indicates an error status on completion of reception by serial interface UART6. It includes three error flag bits (PE6, FE6, OVE6).

This register is read-only by an 8-bit memory manipulation instruction.

Reset signal generation, or clearing bit 7 (POWER6) or bit 5 (RXE6) of ASIM6 to 0 clears this register to 00H. 00H is read when this register is read. If a reception error occurs, read ASIS6 and then read receive buffer register 6 (RXB6) to clear the error flag.

# Figure 14-6. Format of Asynchronous Serial Interface Reception Error Status Register 6 (ASIS6)

#### Address: FF53H After reset: 00H R

| Symbol | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0    |

|--------|---|---|---|---|---|-----|-----|------|

| ASIS6  | 0 | 0 | 0 | 0 | 0 | PE6 | FE6 | OVE6 |

| PE6 | Status flag indicating parity error                                                     |

|-----|-----------------------------------------------------------------------------------------|

| 0   | If POWER6 = 0 or RXE6 = 0, or if ASIS6 register is read                                 |

| 1   | If the parity of transmit data does not match the parity bit on completion of reception |

| FE6 | Status flag indicating framing error                       |

|-----|------------------------------------------------------------|

| 0   | If POWER6 = 0 or RXE6 = 0, or if ASIS6 register is read    |

| 1   | If the stop bit is not detected on completion of reception |

| OVE6 | Status flag indicating overrun error                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------|

| 0    | If POWER6 = 0 or RXE6 = 0, or if ASIS6 register is read                                                            |

| 1    | If receive data is set to the RXB6 register and the next reception operation is completed before the data is read. |

Cautions 1. The operation of the PE6 bit differs depending on the set values of the PS61 and PS60 bits of asynchronous serial interface operation mode register 6 (ASIM6).

- 2. For the stop bit of the receive data, only the first stop bit is checked regardless of the number of stop bits.

- 3. If an overrun error occurs, the next receive data is not written to receive buffer register 6 (RXB6) but discarded.

- 4. If data is read from ASIS6, a wait cycle is generated. Do not read data from ASIS6 when the peripheral hardware clock (fPRs) is stopped. For details, refer to CHAPTER 31 CAUTIONS FOR WAIT.

# (b) Parity types and operation

The parity bit is used to detect a bit error in communication data. Usually, the same type of parity bit is used on both the transmission and reception sides. With even parity and odd parity, a 1-bit (odd number) error can be detected. With zero parity and no parity, an error cannot be detected.

#### Caution Fix the PS61 and PS60 bits to 0 when the device is used in LIN communication operation.

# (i) Even parity

Transmission

Transmit data, including the parity bit, is controlled so that the number of bits that are "1" is even. The value of the parity bit is as follows.

If transmit data has an odd number of bits that are "1": 1 If transmit data has an even number of bits that are "1": 0

Reception

The number of bits that are "1" in the receive data, including the parity bit, is counted. If it is odd, a parity error occurs.

# (ii) Odd parity

Transmission

Unlike even parity, transmit data, including the parity bit, is controlled so that the number of bits that are "1" is odd.

If transmit data has an odd number of bits that are "1": 0 If transmit data has an even number of bits that are "1": 1

• Reception

The number of bits that are "1" in the receive data, including the parity bit, is counted. If it is even, a parity error occurs.

# (iii) 0 parity

The parity bit is cleared to 0 when data is transmitted, regardless of the transmit data.

The parity bit is not detected when the data is received. Therefore, a parity error does not occur regardless of whether the parity bit is "0" or "1".

#### (iv) No parity

No parity bit is appended to the transmit data.

Reception is performed assuming that there is no parity bit when data is received. Because there is no parity bit, a parity error does not occur.

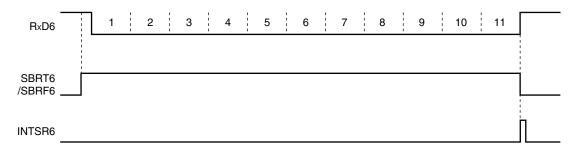

# (i) SBF reception

When the device is used in LIN communication operation, the SBF (Synchronous Break Field) reception control function is used for reception. For the reception operation of LIN, refer to **Figure 14-2** LIN Reception **Operation**.

Reception is enabled when bit 7 (POWER6) of asynchronous serial interface operation mode register 6 (ASIM6) is set to 1 and then bit 5 (RXE6) of ASIM6 is set to 1. SBF reception is enabled when bit 6 (SBRT6) of asynchronous serial interface control register 6 (ASICL6) is set to 1. In the SBF reception enabled status, the RxD6 pin is sampled and the start bit is detected in the same manner as the normal reception enable status.

When the start bit has been detected, reception is started, and serial data is sequentially stored in the receive shift register 6 (RXS6) at the set baud rate. When the stop bit is received and if the width of SBF is 11 bits or more, a reception completion interrupt request (INTSR6) is generated as normal processing. At this time, the SBRF6 and SBRT6 bits are automatically cleared, and SBF reception ends. Detection of errors, such as OVE6, PE6, and FE6 (bits 0 to 2 of asynchronous serial interface reception error status register 6 (ASIS6)) is suppressed, and error detection processing of UART communication is not performed. In addition, data transfer between receive shift register 6 (RXS6) and receive buffer register 6 (RXB6) is not performed, and the reset value of FFH is retained. If the width of SBF is 10 bits or less, an interrupt does not occur as error processing after the stop bit has been received, and the SBF reception mode is restored. In this case, the SBRF6 and SBRT6 bits are not cleared.

#### Figure 14-25. SBF Reception

#### 1. Normal SBF reception (stop bit is detected with a width of more than 10.5 bits)

#### 2. SBF reception error (stop bit is detected with a width of 10.5 bits or less)

Remark

RxD6:

RxD6 pin (input)

SBRT6:

Bit 6 of asynchronous serial interface control register 6 (ASICL6)

SBRF6:

Bit 7 of ASICL6

INTSR6:

Reception completion interrupt request

#### Figure 15-4. Format of Slave Address Register 0 (SVA0)

| Address: | FFA6H | After reset: | 00H R/V | V |   |   |   |                   |

|----------|-------|--------------|---------|---|---|---|---|-------------------|

| Symbol   | 7     | 6            | 5       | 4 | 3 | 2 | 1 | 0                 |

| SVA0     |       |              |         |   |   |   |   | 0 <sup>Note</sup> |

#### Note Bit 0 is fixed to 0.

# (3) SO latch

The SO latch is used to retain the SDAA0 pin's output level.

#### (4) Wakeup controller

This circuit generates an interrupt request (INTIICA0) when the address received by this register matches the address value set to the slave address register 0 (SVA0) or when an extension code is received.

#### (5) Serial clock counter

This counter counts the serial clocks that are output or input during transmit/receive operations and is used to verify that 8-bit data was transmitted or received.

#### (6) Interrupt request signal generator

This circuit controls the generation of interrupt request signals (INTIICA0).

An I<sup>2</sup>C interrupt request is generated by the following two triggers.

- Falling edge of eighth or ninth clock of the serial clock (set by WTIM0 bit)

- Interrupt request generated when a stop condition is detected (set by SPIE0 bit)

Remark WTIM0 bit: Bit 3 of IICA control register 0 (IICACTL0) SPIE0 bit: Bit 4 of IICA control register 0 (IICACTL0)

#### (7) Serial clock controller

In master mode, this circuit generates the clock output via the SCLA0 pin from a sampling clock.

#### (8) Serial clock wait controller

This circuit controls the wait timing.

(9) ACK generator, stop condition detector, start condition detector, and ACK detector These circuits generate and detect each status.

#### (10) Data hold time correction circuit

This circuit generates the hold time for data corresponding to the falling edge of the serial clock.

#### (11) Start condition generator

This circuit generates a start condition when the STT0 bit is set to 1. However, in the communication reservation disabled status (IICRSV bit = 1), when the bus is not released (IICBSY bit = 1), start condition requests are ignored and the STCF bit is set to 1.

# (12) Stop condition generator

This circuit generates a stop condition when the SPT0 bit is set to 1.

# Figure 17-22. Format of Priority Specification Flag Registers (PR0L, PR0H, PR1L, PR1H) (48-pin products of 78K0/KC2-L)

| Address: FFE | E8H After re | eset: FFH F    | R/W    |        |                  |         |         |         |

|--------------|--------------|----------------|--------|--------|------------------|---------|---------|---------|

| Symbol       | <7>          | <6>            | <5>    | <4>    | <3>              | <2>     | <1>     | <0>     |

| PR0L         | SREPR6       | PPR5           | PPR4   | PPR3   | PPR2             | PPR1    | PPR0    | LVIPR   |

| -            |              |                |        |        |                  |         |         |         |

| Address: FFE | E9H After re | eset: FFH F    | R/W    |        |                  |         |         |         |

| Symbol       | <7>          | <6>            | <5>    | <4>    | <3>              | <2>     | <1>     | <0>     |

| PR0H         | TMPR010      | TMPR000        | TMPR50 | TMPRH0 | TMPRH1           | CSIPR10 | STPR6   | SRPR6   |

| -            |              |                |        |        |                  |         |         |         |

| Address: FFE | EAH After r  | eset: FFH I    | R/W    |        |                  |         |         |         |

| Symbol       | <7>          | <6>            | <5>    | <4>    | <3>              | <2>     | <1>     | <0>     |

| PR1L         | PPR8         | PPR7           | RTCPR  | KRPR   | TMPR51           | RTCIPR  | PPR6    | ADPR    |

|              |              |                |        |        |                  |         |         |         |

| Address: FFE | EBH After r  | eset: FFH I    | R/W    |        |                  |         |         |         |

| Symbol       | 7            | 6              | 5      | <4>    | <3>              | <2>     | <1>     | <0>     |

| PR1H         | 1            | 1              | 1      | PPR11  | PPR10            | PPR9    | CSIPR11 | IICAPR0 |

| -            |              |                |        |        |                  |         |         |         |

|              | XXPRX        |                |        | Prio   | rity level selec | otion   |         |         |

|              | 0            | High priority  | level  |        |                  |         |         |         |

|              | 1            | Low priority I | level  |        |                  |         |         |         |

#### Caution Be sure to set bits 5 to 7 of PR1H to 1.

(4) External interrupt rising edge enable registers (EGPCTL0, EGPCTL1), external interrupt falling edge enable registers (EGNCTL0, EGNCTL1)

These registers specify the valid edge for INTPn.

EGPCTL0, EGPCTL1, EGNCTL0, and EGNCTL1 are set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears these registers to 00H.

|         | Remark | n = 0, 1:            | 78K0/KY2-L                        |

|---------|--------|----------------------|-----------------------------------|

|         |        | n = 0 to 3:          | 20-pin products of 78K0/KA2-L     |

| <r></r> |        | n = 0, 2 to 5:       | 25, 32-pin products of 78K0/KA2-L |

|         |        | n = 0 to 5, 10, 11:  | 78K0/KB2-L                        |

| <r></r> |        | n = 0 to 5, 9 to 11: | 40-pin products of 78K0/KC2-L     |

|         |        | n = 0 to 5, 8 to 11: | 44-pin products of 78K0/KC2-L     |

|         |        | n = 0 to 11:         | 48-pin products of 78K0/KC2-L     |

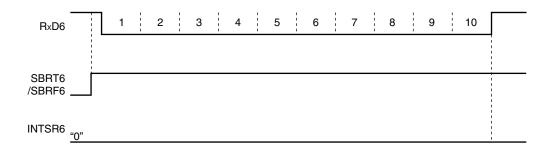

#### Figure 17-25. Interrupt Request Acknowledgment Processing Algorithm

××IF: Interrupt request flag

××MK: Interrupt mask flag

××PR: Priority specification flag

IE: Flag that controls acknowledgment of maskable interrupt request (1 = Enable, 0 = Disable)

ISP: Flag that indicates the priority level of the interrupt currently being serviced (0 = high-priority interrupt servicing, 1 = No interrupt request acknowledged, or low-priority interrupt servicing)

|                                | Hardware                                                      | Status After Reset<br>Acknowledgment <sup>Note 1</sup> |

|--------------------------------|---------------------------------------------------------------|--------------------------------------------------------|

| Clock operation mode sele      | ct register (OSCCTL)                                          | 00H                                                    |

| Processor clock control reg    | jister (PCC)                                                  | 01H                                                    |

| Internal oscillation mode re   | 80H                                                           |                                                        |

| Main OSC control register      | 80H                                                           |                                                        |

| Main clock mode register (I    | MCM)                                                          | 00H                                                    |

| Oscillation stabilization time | e counter status register (OSTC)                              | 00H                                                    |

| Oscillation stabilization time | e select register (OSTS)                                      | 05H                                                    |

| Peripheral enable register     | 0 (PER0)                                                      | 00H                                                    |

| 16-bit timer/event counter     | Timer counter 00 (TM00)                                       | 0000H                                                  |

| 00                             | Capture/compare registers 000, 010 (CR000, CR010)             | 0000H                                                  |

|                                | Mode control register 00 (TMC00)                              | 00H                                                    |

|                                | Prescaler mode register 00 (PRM00)                            | 00H                                                    |

|                                | Capture/compare control register 00 (CRC00)                   | 00H                                                    |

|                                | Timer output control register 00 (TOC00)                      | 00H                                                    |

| 8-bit timer/event counters     | Timer counters 50, 51 (TM50, TM51)                            | 00H                                                    |

| 50, 51                         | Compare registers 50, 51 (CR50, CR51)                         | 00H                                                    |

|                                | Timer clock selection registers 50, 51 (TCL50, TCL51)         | 00H                                                    |

|                                | Mode control registers 50, 51 (TMC50, TMC51)                  | 00H                                                    |

| 8-bit timers H0, H1            | Compare registers 00, 10, 01, 11 (CMP00, CMP10, CMP01, CMP11) | 00H                                                    |

|                                | Mode registers (TMHMD0, TMHMD1)                               | 00H                                                    |

|                                | Carrier control register 1 (TMCYC1) <sup>Note 2</sup>         | 00H                                                    |

| Real-time counter              | Sub-count register (RSUBC)                                    | 0000H                                                  |

|                                | Second count register (SEC)                                   | 00H                                                    |

|                                | Minute count register (MIN)                                   | 00H                                                    |

|                                | Hour count register (HOUR)                                    | 12H                                                    |

|                                | Week count register (WEEK)                                    | 00H                                                    |

|                                | Day count register (DAY)                                      | 01H                                                    |

|                                | Month count register (MONTH)                                  | 01H                                                    |

|                                | Year count register (YEAR)                                    | 00H                                                    |

|                                | Watch error correction register (SUBCUD)                      | 00H                                                    |

|                                | Alarm minute register (ALARMWM)                               | 00H                                                    |

|                                | Alarm hour register (ALARMWH)                                 | 12H                                                    |

|                                | Alarm week register (ALARMWW)                                 | 00H                                                    |

|                                | Control register 0 (RTCC0)                                    | 00H                                                    |

|                                | Control register 1 (RTCC1)                                    | 00H                                                    |

|                                | Control register 2 (RTCC2)                                    | 00H                                                    |

Table 20-2. Hardware Statuses After Reset Acknowledgment (2/4)

- **Notes 1.** During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware statuses become undefined. All other hardware statuses remain unchanged after reset.

- 2. 8-bit timer H1 only.

- Remark The special function registers (SFRs) mounted depend on the product. Refer to 3.2.3 Special function registers (SFRs).

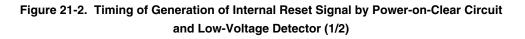

#### (1) When LVI is OFF upon power application (option byte: LVISTART = 0)

- Notes 1. The operation guaranteed range is  $1.8 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$ . To make the state at lower than 1.8 V reset state when the supply voltage falls, use the reset function of the low-voltage detector, or input the low level to the RESET pin.

- If the rate at which the voltage rises to 1.8 V after power application is slower than 0.5 V/ms (MIN.), input a low level to the RESET pin before the voltage reaches to 1.8 V.

- **3.** The internal voltage stabilization wait time includes the oscillation accuracy stabilization time of the internal high-speed oscillation clock.

- 4. The internal high-speed oscillation clock, high-speed system clock or subsystem clock can be selected as the CPU clock. To use the X1 clock, use the OSTC register to confirm the lapse of the oscillation stabilization time. To use the XT1 clock, use the timer function for confirmation of the lapse of the stabilization time.

# Caution Set the low-voltage detector by software after the reset status is released (refer to CHAPTER 22 LOW-VOLTAGE DETECTOR).

- Remark VLVI: LVI detection voltage

- VPOR: POC power supply rise detection voltage

- VPDR: POC power supply fall detection voltage

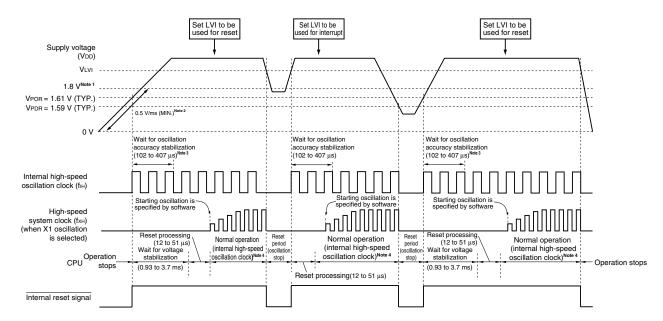

# Figure 21-3. Example of Software Processing After Reset Release (2/2)

Checking reset source

# 25.4 Connection of Pins on Board

To write the flash memory on-board, connectors that connect the dedicated flash memory programmer must be provided on the target system. First provide a function that selects the normal operation mode or flash memory programming mode on the board.

When the flash memory programming mode is set, all the pins not used for programming the flash memory are in the same status as immediately after reset. Therefore, if the external device does not recognize the state immediately after reset, the pins must be handled as described below.

# 25.4.1 TOOL pins

The pins used for communication in flash memory programming mode are shown in the table below.

| Pin Name       | Connection of Pins                                                                                                                              |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| TOOLC0, TOOLC1 | Connect this pin directly to the dedicated flash memory programmer or pull it down by connecting it to Vss via a resistor (10 k $\Omega$ )      |

| TOOLD0, TOOLD1 | Connect this pin directly to the dedicated flash memory programmer or pull it up by connecting it to VDD via a resistor (3 k to 10 k $\Omega$ ) |

Table 25-3. Pins Used for Communication in Flash Memory Programming Mode

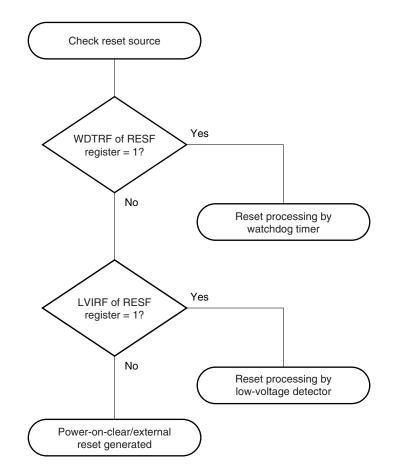

To connect the dedicated flash memory programmer to the pins of a serial interface that is connected to another device on the board, care must be exercised so that signals do not collide or that the other device does not malfunction.

#### (1) Signal collision

If the dedicated flash memory programmer is connected to the TOOL pin that is connected to another device, signal collision takes place. To avoid this collision, either isolate the connection with the other device, or make the other device go into a high-impedance state.

# Figure 25-3. Signal Collision (TOOL Pin)

In the flash memory programming mode, the signal of the other device collides with the signal of the dedicated flash programmer. Therefore, isolate the signal of the other device.

# Caution The pins mounted depend on the product. Refer to Caution 2 at the beginning of this chapter.

| Parameter                     | Symbol | (                           | Conditions                                                                            | Ratings     | Unit |

|-------------------------------|--------|-----------------------------|---------------------------------------------------------------------------------------|-------------|------|

| Output current, high          | Іон1   | Per pin                     | P00 to P02, P10 to P17,<br>P30 to P33, P40 to P42,<br>P60 to P63, P70 to P75,<br>P120 | -10         | mA   |

|                               |        | Total of all pins<br>–80 mA | P00 to P02, P40 to P42,<br>P120                                                       | -25         | mA   |

|                               |        |                             | P10 to P17, P30 to P33,<br>P60 to P63, P70 to P75                                     | -55         | mA   |

|                               | Іон2   | Per pin                     | P20 to P27                                                                            | -0.5        | mA   |

|                               |        | Total of all pins           |                                                                                       | -2          | mA   |

| Output current, low           | IOL1   | Per pin                     | P00 to P02, P10 to P17,<br>P30 to P33, P40 to P42,<br>P60 to P63, P70 to P75,<br>P120 | 30          | mA   |

|                               |        | Total of all pins<br>200 mA | P00 to P02, P40 to P42,<br>P120                                                       | 60          | mA   |

|                               |        |                             | P10 to P17, P30 to P33,<br>P60 to P63, P70 to P75                                     | 140         | mA   |

|                               | IOL2   | Per pin                     | P20 to P27                                                                            | 1           | mA   |

|                               |        | Total of all pins           |                                                                                       | 5           | mA   |

| Operating ambient temperature | TA     |                             |                                                                                       | -40 to +85  | °C   |

| Storage temperature           | Tstg   |                             |                                                                                       | -65 to +150 | °C   |

# Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (78K0/KY2-L, 78K0/KA2-L (20 pins), 78K0/KB2-L, 78K0/KC2-L) (2/2)

- Cautions 1. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- 2. The value of the current that can be run per pin must satisfy the value of the current per pin and the total value of the currents of all pins.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.

(E (O)

| Edition     | Description                                                                                                                                                                                                                                                     | Chapter                                                               |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|

| 2nd Edition | Modification of Caution in Figure 17-14 Format of Priority Specification Flag Registers<br>(PR0L, PR0H, PR1L, PR1H) (78K0/KB2-L) to Figure 17-16 Format of Priority<br>Specification Flag Registers (PR0L, PR0H, PR1L, PR1H) (48-pin products of<br>78K0/KC2-L) | CHAPTER 28<br>ELECTRICAL<br>SPECIFICATIONS<br>(TARGET VALUES)         |  |

|             | Addition of reset current (IDDrst)                                                                                                                                                                                                                              |                                                                       |  |

|             | (1) A/D Converter in Analog Characteristics                                                                                                                                                                                                                     |                                                                       |  |

|             | Modification of conversion time (tconv) in <1> ANI0 to ANI7                                                                                                                                                                                                     |                                                                       |  |

|             | Addition of <2> ANI8 to ANI10 (78K0/KB2-L and 78K0/KC2-L only)                                                                                                                                                                                                  |                                                                       |  |

|             | (3) Operational amplifier 0 in Analog Characteristics                                                                                                                                                                                                           |                                                                       |  |

|             | Modification of VDD range                                                                                                                                                                                                                                       |                                                                       |  |

|             | Addition of phase margin and large-amplitude voltage gain (AVOPO)                                                                                                                                                                                               |                                                                       |  |

|             | Modification of gain-bandwidth product (GBWoPo)                                                                                                                                                                                                                 |                                                                       |  |

|             | (4) Operational amplifier 1 in Analog Characteristics                                                                                                                                                                                                           |                                                                       |  |

|             | Addition of phase margin and large-amplitude voltage gain (AVoP1)                                                                                                                                                                                               |                                                                       |  |

|             | Modification of gain-bandwidth product (GBWoP1)                                                                                                                                                                                                                 |                                                                       |  |

|             | (7) LVI in Analog Characteristics                                                                                                                                                                                                                               |                                                                       |  |

|             | • Addition of supply voltage level (VLVI14) and supply voltage when power supply voltage is turned on (VDDLVI)                                                                                                                                                  |                                                                       |  |

|             | Flash Memory Programming Characteristics                                                                                                                                                                                                                        |                                                                       |  |

|             | <ul> <li>Modification of VDD range</li> <li>Modification of system clock frequency (fcLK)</li> <li>Modification of Number of rewrites per chip (Cerwr)</li> <li>Addition of Note 1</li> </ul>                                                                   |                                                                       |  |

|             | Modification of 29.1 78K0/KY2-L                                                                                                                                                                                                                                 | CHAPTER 29                                                            |  |

|             |                                                                                                                                                                                                                                                                 | PACKAGE<br>DRAWINGS                                                   |  |

|             | Addition of preliminary                                                                                                                                                                                                                                         | CHAPTER 30<br>RECOMMENDED<br>SOLDERING<br>CONDITIONS<br>(PRELIMINARY) |  |

|             | Modification of URL of download site for development tools                                                                                                                                                                                                      | APPENDIX A<br>DEVELOPMENT<br>TOOLS                                    |  |

|             | Addition of chapter                                                                                                                                                                                                                                             | APPENDIX B<br>REGISTER INDEX                                          |  |

|             | Addition of chapter                                                                                                                                                                                                                                             | APPENDIX C<br>REVISION HISTORY                                        |  |

**Remark** "Classification" in the above table classifies revisions as follows.

(a): Error correction, (b): Addition/change of specifications, (c): Addition/change of description or note, (d): Addition/change of package, part number, or management division, (e): Addition/change of related documents