# E. Renesas Electronics America Inc - UPD78F0581GA-GAM-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 37                                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 512 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 11x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 48-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0581ga-gam-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# (2) 25-pin plastic FLGA (3x3) (2/2)

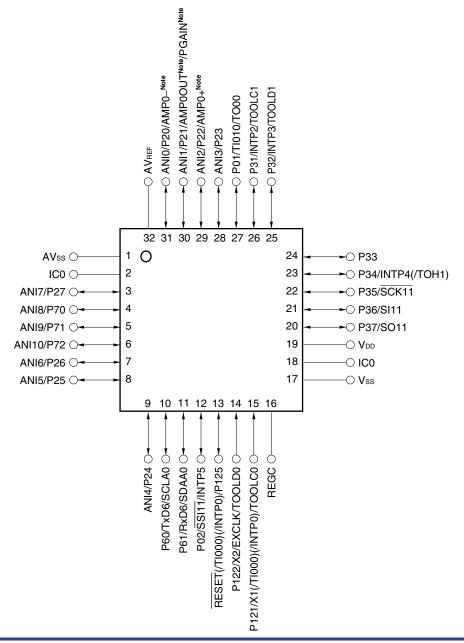

Note µPD78F0565, 78F0566, 78F0567 (products with operational amplifier) only

- Cautions 1. Vss functions alternately as the ground potential of the A/D converter. Be sure to connect Vss to a stabilized GND (= 0 V).

- 2. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- 3. ANI0/P20/AMP0-, ANI1/P21/AMP0OUT/PGAIN, ANI2/P22/AMP0+, and ANI3/P23 to ANI6/P26 are set in the analog input mode after release of reset.

- 4. RESET/P125 immediately after release of reset is set in the external reset input.

- 5. Set P30 and P01 to output mode (PM30 = PM01 = 0) by using software after release of reset.

- **Remark** Functions in parentheses () in the figure above can be assigned by setting the port alternate switch control register (MUXSEL).

### <R> (3) 32-pin plastic WQFN (5x5) (1/2)

RENESAS

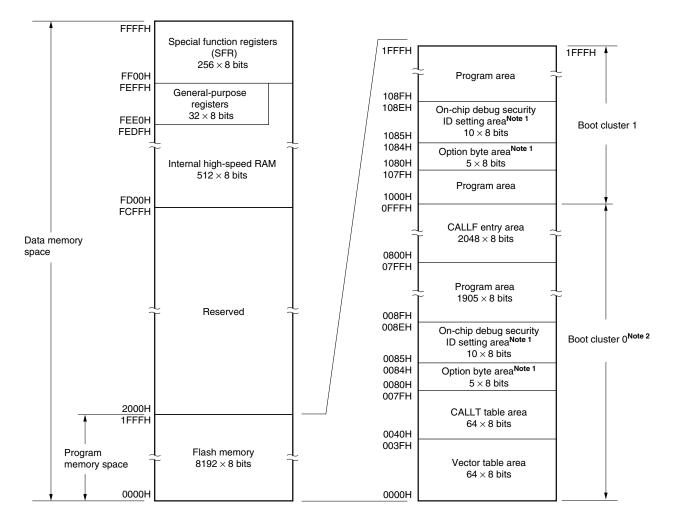

### Figure 3-2. Memory Map (µPD78F0551, 78F0556, 78F0561, 78F0566, 78F0571, 78F0576, 78F0581, 78F0586)

Notes 1. When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used: Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (refer to 25.6 Security Settings).

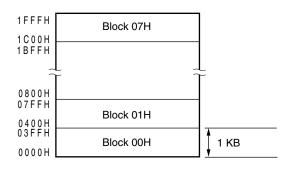

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, refer to **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

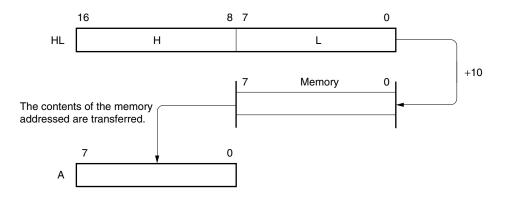

# 3.4.7 Based addressing

### [Function]

8-bit immediate data is added as offset data to the contents of the base register, that is, the HL register pair in the register bank specified by the register bank select flag (RBS0 and RBS1), and the sum is used to address the memory. Addition is performed by expanding the offset data as a positive number to 16 bits. A carry from the 16th bit is ignored.

This addressing can be carried out for all of the memory spaces.

# [Operand format]

| Identifier | Description |

|------------|-------------|

| -          | [HL + byte] |

### [Description example]

MOV A, [HL + 10H]; when setting byte to 10H

| Operation code | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 |

|----------------|---|---|---|---|---|---|---|---|

|                |   | • |   | • | • |   |   | • |

|                | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

|                |   |   |   |   |   |   |   |   |

# [Illustration]

| Function Name         | I/O   | Function                                                                                                                                                             | After Reset | Alternate Function                       |

|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------|

| P60                   | I/O   | Port 6.<br>4-bit I/O port.                                                                                                                                           | Input port  | SCLA0/SCK11/<br>INTP11                   |

| P61                   |       | Input/output can be specified in 1-bit units.                                                                                                                        |             | SDAA0/SI11/INTP10                        |

| P62                   |       | Input of P60 and P61 can be set to SMBus input buffer in 1-bit units.                                                                                                |             | SO11/INTP9                               |

| P63 <sup>Note 2</sup> |       | Output of P60 to P63 can be set to N-ch open-drain output (V <sub>DD</sub> tolerance).<br>Use of an on-chip pull-up resistor can be specified by a software setting. |             | INTP8 <sup>Note 2</sup>                  |

| P70                   | I/O   | Port 7.                                                                                                                                                              | Input port  | KR0                                      |

| P71                   |       | 6-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                    |             | KR1                                      |

| P72                   |       |                                                                                                                                                                      |             | KR2                                      |

| P73                   |       |                                                                                                                                                                      |             | KR3                                      |

| P74 <sup>Note 1</sup> |       |                                                                                                                                                                      |             | KR4 <sup>Note 1</sup>                    |

| P75 <sup>Note 1</sup> |       |                                                                                                                                                                      |             | KR5 <sup>Note 1</sup>                    |

| P120                  | I/O   | Port 12.<br>1-bit I/O port and 5-bit input port.                                                                                                                     | Input port  | EXLVI/INTP0<br>(/SO11) <sup>Note 2</sup> |

| P121                  | Input | For only P120 and P125, use of an on-chip pull-up resistor can be specified by a software setting.                                                                   |             | X1/TOOLC0                                |

| P122                  |       | can be speaned by a soliware setting.                                                                                                                                |             | X2/EXCLK/TOOLD0                          |

| P123                  |       |                                                                                                                                                                      |             | XT1                                      |

| P124                  |       |                                                                                                                                                                      |             | XT2/EXCLKS                               |

| P125                  |       |                                                                                                                                                                      | Reset input | RESET                                    |

| Table 4-6. | Port Functions | (78K0/KC2-L) (2/2) |

|------------|----------------|--------------------|

|------------|----------------|--------------------|

Notes 1. 48-pin products only

**2.** 44-pin and 48-pin products only

**Remark** Functions in parentheses () can be assigned by setting the port alternate switch control register (MUXSEL).

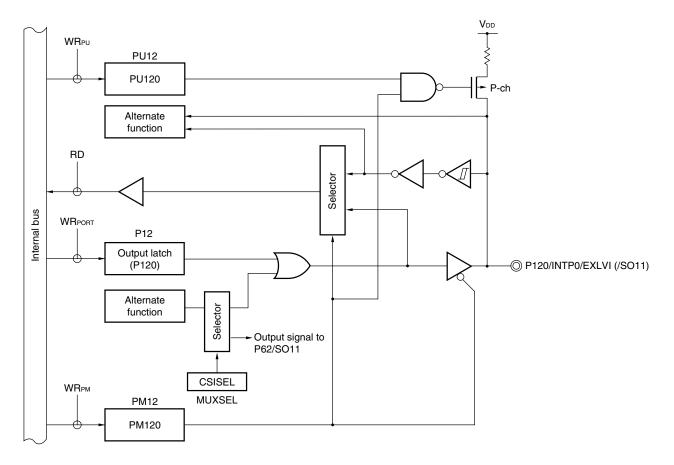

Figure 4-27. Block Diagram of P120 (2/2)

# (2) 78K0/KC2-L

- P12: Port register 12

- PU12: Pull-up resistor option register 12

- PM12: Port mode register 12

- MUXSEL: Port alternate switch control register

- RD: Read signal

- WR××: Write signal

- Caution 3. The XT1 oscillator is a circuit with low amplification in order to achieve low-power consumption. Note the following points when designing the circuit.

- Pins and circuit boards include parasitic capacitance. Therefore, perform oscillation evaluation using a circuit board to be actually used and confirm that there are no problems.

- Use the recommended resonator, which will be described in CHAPTER 28 ELECTRICAL SPECIFICATIONS after it is evaluated, when using the XT1 oscillator in the ultra-low power consumption oscillation (RSWOSC = 1).

- Make the wiring between the XT1 and XT2 pins and the resonators as short as possible, and minimize the parasitic capacitance and wiring resistance. Note this particularly when the ultra-low power consumption oscillation (RSWOSC = 1) is selected.

- Configure the circuit of the circuit board, using material with little wiring resistance.

- Place a ground pattern that has the same potential as Vss as much as possible near the XT1 oscillator.

- Be sure that the signal lines between the XT1 and XT2 pins, and the resonators do not cross with the other signal lines. Do not route the wiring near a signal line through which a high fluctuating current flows.

- The impedance between the XT1 and XT2 pins may drop and oscillation may be disturbed due to moisture absorption of the circuit board in a high-humidity environment or dew condensation on the board. When using the circuit board in such an environment, take measures to damp-proof the circuit board, such as by coating.

- When coating the circuit board, use material that does not cause capacitance or leakage between the XT1 and XT2 pins.

### (2) Processor clock control register (PCC)

This register is used to select the CPU clock, the division ratio, and operation mode for subsystem clock. PCC is set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets PCC to 01H.

### Figure 5-5. Format of Processor Clock Control Register (PCC) (78K0/KY2-L, 78K0/KA2-L, 78K0/KB2-L)

| Address: FF | FBH After | reset: 01H    | R/W  |                    |        |                  |        |      |

|-------------|-----------|---------------|------|--------------------|--------|------------------|--------|------|

| Symbol      | 7         | 6             | 5    | 4                  | 3      | 2                | 1      | 0    |

| PCC         | 0         | 0             | 0    | 0                  | 0      | PCC2             | PCC1   | PCC0 |

|             |           |               |      | 1                  |        |                  |        |      |

|             | PCC2      | PCC1          | PCC0 |                    | CPU o  | clock (fcpu) sel | ection |      |

|             | 0         | 0             | 0    | fxp                |        |                  |        |      |

|             | 0         | 0             | 1    | fxp/2 (default     | :)     |                  |        |      |

|             | 0         | 1             | 0    | fxp/2 <sup>2</sup> |        |                  |        |      |

|             | 0         | 1             | 1    | fxp/2 <sup>3</sup> |        |                  |        |      |

|             | 1         | 0             | 0    | fxp/2 <sup>4</sup> |        |                  |        |      |

|             | 0         | ther than abo | ve   | Setting prohi      | ibited |                  |        |      |

### Cautions 1. Be sure to clear bits 3 to 7 to 0.

2. The peripheral hardware clock (fPRs) is not divided when the division ratio of the PCC is set.

Remark fxp: Main system clock oscillation frequency

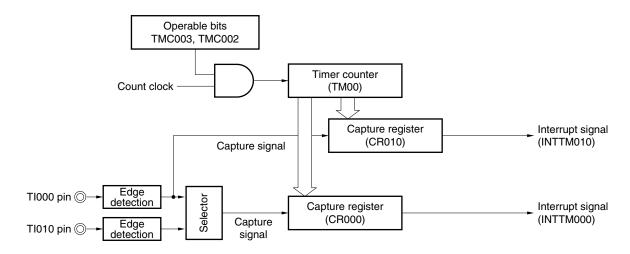

- Cautions 1. The valid edge of TI010 and timer output (TO00) cannot be used for the P01 pin at the same time. Select either of the functions.

- 2. If clearing of bits 3 and 2 (TMC003 and TMC002) of 16-bit timer mode control register 00 (TMC00) to 00 and input of the capture trigger conflict, then the captured data is undefined.

- 3. To change the mode from the capture mode to the comparison mode, first clear the TMC003 and TMC002 bits to 00, and then change the setting.

A value that has been once captured remains stored in CR000 unless the device is reset. If the mode has been changed to the comparison mode, be sure to set a comparison value.

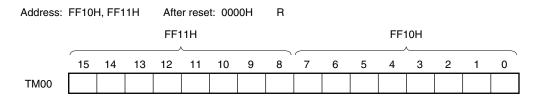

# (1) 16-bit timer counter 00 (TM00)

TM00 is a 16-bit read-only register that counts count pulses. The counter is incremented in synchronization with the rising edge of the count clock.

# Figure 6-2. Format of 16-Bit Timer Counter 00 (TM00)

The count value of TM00 can be read by reading TM00 when the value of bits 3 and 2 (TMC003 and TMC002) of 16bit timer mode control register 00 (TMC00) is other than 00. The value of TM00 is 0000H if it is read when TMC003 and TMC002 = 00.

The count value is reset to 0000H in the following cases.

- At reset signal generation

- If TMC003 and TMC002 are cleared to 00

- If the valid edge of the TI000 pin is input in the mode in which the clear & start occurs when inputting the valid edge to the TI000 pin

- If TM00 and CR000 match in the mode in which the clear & start occurs when TM00 and CR000 match

- OSPT00 is set to 1 in one-shot pulse output mode or the valid edge is input to the TI000 pin

# Caution Even if TM00 is read, the value is not captured by CR010.

# (3) 16-bit timer output control register 00 (TOC00)

TOC00 is an 8-bit register that controls the TO00 output.

TOC00 can be rewritten while only OSPT00 is operating (when TMC003 and TMC002 = other than 00). Rewriting the other bits is prohibited during operation.

However, TOC004 can be rewritten during timer operation as a means to rewrite CR010 (refer to **6.5.1 Rewriting CR010 during TM00 operation**).

TOC00 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears TOC00 to 00H.

# Caution Be sure to set TOC00 using the following procedure.

<1> Set TOC004 and TOC001 to 1.

<2> Set only TOE00 to 1.

<3> Set either of LVS00 or LVR00 to 1.

# (3) Free-running timer mode operation

(CR000: capture register, CR010: capture register)

# Figure 6-37. Block Diagram of Free-Running Timer Mode (CR000: Capture Register, CR010: Capture Register)

**Remark** If both CR000 and CR010 are used as capture registers in the free-running timer mode, the TO00 output level is not inverted.

However, it can be inverted each time the valid edge of the TI000 pin is detected if bit 1 (TMC001) of 16-bit timer mode control register 00 (TMC00) is set to 1.

# (4) Real-time counter control register 2 (RTCC2)

The RTCC2 register is an 8-bit register that is used to control the interval interrupt function and the RTCDIV pin. RTCC2 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

### Figure 10-5. Format of Real-Time Counter Control Register 2 (RTCC2)

| Address: FF6 | FH After res | et: 00H R/W |        |   |   |      |      |      |

|--------------|--------------|-------------|--------|---|---|------|------|------|

| Symbol       | <7>          | <6>         | <5>    | 4 | 3 | 2    | 1    | 0    |

| RTCC2        | RINTE        | RCLOE2      | RCKDIV | 0 | 0 | ICT2 | ICT1 | ICT0 |

| RINTE | ICT2 | ICT1 | ICT0 | Interval interrupt (INTRTCI) selection |

|-------|------|------|------|----------------------------------------|

| 0     | ×    | ×    | ×    | Interval interrupt is not generated.   |

| 1     | 0    | 0    | 0    | 2 <sup>°</sup> /fsuв (1.953125 ms)     |

| 1     | 0    | 0    | 1    | 2 <sup>7</sup> /fsub (3.90625 ms)      |

| 1     | 0    | 1    | 0    | 2 <sup>8</sup> /fsuв (7.8125 ms)       |

| 1     | 0    | 1    | 1    | 2 <sup>9</sup> /fsuв (15.625 ms)       |

| 1     | 1    | 0    | 0    | 2 <sup>10</sup> /fsuв (31.25 ms)       |

| 1     | 1    | 0    | 1    | 2 <sup>11</sup> /fsuв (62.5 ms)        |

| 1     | 1    | 1    | ×    | 2 <sup>12</sup> /fsub (125 ms)         |

| RCLOE2<br>Notes 1, 2 | RTCDIV pin output control         |

|----------------------|-----------------------------------|

| 0                    | Output of RTCDIV pin is disabled. |

| 1                    | Output of RTCDIV pin is enabled.  |

| RCKDIV <sup>Note 1</sup> | Selection of RTCDIV pin output frequency  |

|--------------------------|-------------------------------------------|

| 0                        | RTCDIV pin outputs 512 Hz (1.95 ms).      |

| 1                        | RTCDIV pin outputs 16.384 kHz (0.061 ms). |

Notes 1. 78K0/KC2-L (44-pin and 48-pin products) only

2. RCLOE0 and RCLOE2 must not be enabled at the same time.

Cautions 1. Change ICT2, ICT1, and ICT0 when RINTE = 0.

2. When the output from RTCDIV pin is stopped, the output continues after a maximum of two clocks of fsuB and enters the low level. While 512 Hz is output, and when the output is stopped immediately after entering the high level, a pulse of at least one clock width of fsuB may be generated.

Remark fsub: Subsystem clock oscillation frequency

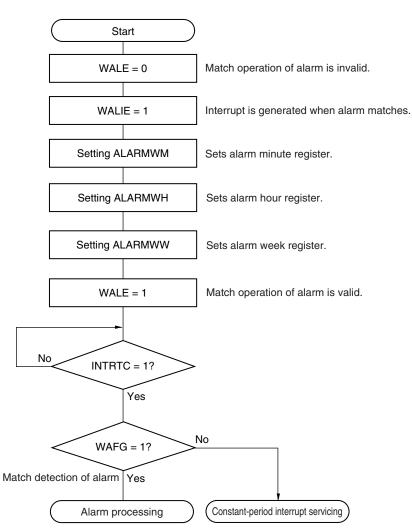

### 10.4.4 Setting alarm of real-time counter

Set time of alarm after setting 0 to WALE first.

### Figure 10-23. Alarm Setting Procedure

Remarks 1. ALARMWM, ALARMWH, and ALARMWW may be written in any sequence.

Fixed-cycle interrupts and alarm match interrupts use the same interrupt source (INTRTC). When using

these two types of interrupts at the same time, which interrupt occurred can be judged by checking the

fixed-cycle interrupt status flag (RIFG) and the alarm detection status flag (WAFG) upon INTRTC

occurrence.

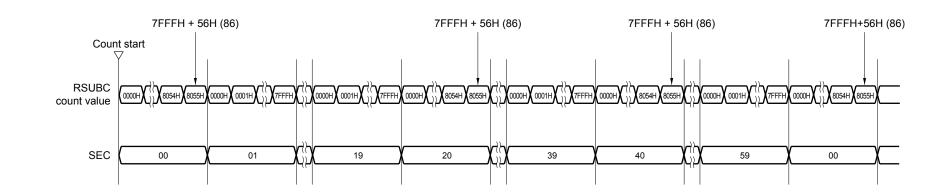

### Correction example <1>

Example of correcting from 32772.3 Hz to 32768 Hz (32772.3 Hz - 131.2 ppm)

### [Measuring the oscillation frequency]

The oscillation frequency<sup>Note</sup> of each product is measured by outputting about 32 kHz from the RTCCL pin or outputting about 1 Hz from the RTC1HZ pin when the watch error correction register is set to its initial value (00H).

Note Refer to 10.4.5 1 Hz output of real-time counter for the setting procedure of outputting about 1 Hz from the RTC1HZ pin, and 10.4.6 32.768 kHz output of real-time counter for the setting procedure of outputting about 32 kHz from the RTCCL pin.

[Calculating the correction value]

(When the output frequency from the RTCCL pin is 32772.3 Hz)

If the target frequency is assumed to be 32768 Hz (32772.3 Hz - 131.2 ppm), the correction range for -131.2 ppm is -63.1 ppm or less, so assume DEV to be 0.

The expression for calculating the correction value when DEV is 0 is applied.

Correction value = Number of correction counts in 1 minute ÷ 3

| = (Oscillation frequency $\div$ Target frequency – 1) $\times$ 32768 $\times$ 60 $\div$ | 3 |

|-----------------------------------------------------------------------------------------|---|

| $= (32772.3 \div 32768 - 1) \times 32768 \times 60 \div 3$                              |   |

| = 86                                                                                    |   |

[Calculating the values to be set to (F6 to F0)]

(When the correction value is 86)

If the correction value is 0 or more (when delaying), assume F6 to be 0. Calculate (F5, F4, F3, F2, F1, F0) from the correction value.

| { (F5, F4, F3, F2, F1, F0) $-$ 1} $	imes$ 2 | = 86                 |

|---------------------------------------------|----------------------|

| (F5, F4, F3, F2, F1, F0)                    | = 44                 |

| (F5, F4, F3, F2, F1, F0)                    | = (1, 0, 1, 1, 0, 0) |

Consequently, when correcting from 32772.3 Hz to 32768 Hz (32772.3 Hz – 131.2 ppm), setting the correction register such that DEV is 0 and the correction value is 86 (bits 6 to 0 of SUBCUD: 0101100) results in 32768 Hz (0 ppm).

Figure 10-27 shows the operation when (DEV, F6, F5, F4, F3, F2, F1, F0) is (0, 0, 1, 0, 1, 1, 0, 0).

# Figure 10-27. Operation when (DEV, F6, F5, F4, F3, F2, F1, F0) = (0, 0, 1, 0, 1, 1, 0, 0)

78K0/Kx2-L

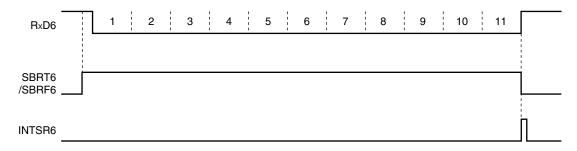

### (i) SBF reception

When the device is used in LIN communication operation, the SBF (Synchronous Break Field) reception control function is used for reception. For the reception operation of LIN, refer to **Figure 14-2** LIN Reception **Operation**.

Reception is enabled when bit 7 (POWER6) of asynchronous serial interface operation mode register 6 (ASIM6) is set to 1 and then bit 5 (RXE6) of ASIM6 is set to 1. SBF reception is enabled when bit 6 (SBRT6) of asynchronous serial interface control register 6 (ASICL6) is set to 1. In the SBF reception enabled status, the RxD6 pin is sampled and the start bit is detected in the same manner as the normal reception enable status.

When the start bit has been detected, reception is started, and serial data is sequentially stored in the receive shift register 6 (RXS6) at the set baud rate. When the stop bit is received and if the width of SBF is 11 bits or more, a reception completion interrupt request (INTSR6) is generated as normal processing. At this time, the SBRF6 and SBRT6 bits are automatically cleared, and SBF reception ends. Detection of errors, such as OVE6, PE6, and FE6 (bits 0 to 2 of asynchronous serial interface reception error status register 6 (ASIS6)) is suppressed, and error detection processing of UART communication is not performed. In addition, data transfer between receive shift register 6 (RXS6) and receive buffer register 6 (RXB6) is not performed, and the reset value of FFH is retained. If the width of SBF is 10 bits or less, an interrupt does not occur as error processing after the stop bit has been received, and the SBF reception mode is restored. In this case, the SBRF6 and SBRT6 bits are not cleared.

### Figure 14-25. SBF Reception

### 1. Normal SBF reception (stop bit is detected with a width of more than 10.5 bits)

### 2. SBF reception error (stop bit is detected with a width of 10.5 bits or less)

Remark

RxD6:

RxD6 pin (input)

SBRT6:

Bit 6 of asynchronous serial interface control register 6 (ASICL6)

SBRF6:

Bit 7 of ASICL6

INTSR6:

Reception completion interrupt request

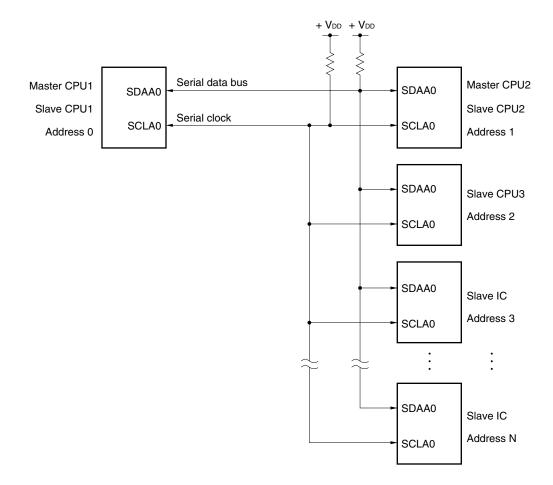

Figure 15-2 shows a serial bus configuration example.

# Figure 15-2. Serial Bus Configuration Example Using I<sup>2</sup>C Bus

| CLD0                                                                                                           | Detection of SCLA0 pin level (valid only when IICE0 = 1) |                                     |  |  |  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------|--|--|--|

| 0                                                                                                              | The SCLA0 pin was detected at low level.                 |                                     |  |  |  |

| 1                                                                                                              | The SCLA0 pin was detected at high level.                |                                     |  |  |  |

| Condition for clearing (CLD0 = 0)                                                                              |                                                          | Condition for setting (CLD0 = 1)    |  |  |  |

| <ul> <li>When the SCLA0 pin is at low level</li> <li>When IICE0 = 0 (operation stop)</li> <li>Reset</li> </ul> |                                                          | When the SCLA0 pin is at high level |  |  |  |

# Figure 15-8. Format of IICA Control Register 1 (IICACTL1) (2/2)

| DAD0                                                                                                           | Detection of SDAA0 pin level (valid only when IICE0 = 1) |                                     |  |  |  |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------|--|--|--|

| 0                                                                                                              | The SDAA0 pin was detected at low level.                 |                                     |  |  |  |

| 1                                                                                                              | The SDAA0 pin was detected at high level.                |                                     |  |  |  |

| Condition for clearing (DAD0 = 0)                                                                              |                                                          | Condition for setting (DAD0 = 1)    |  |  |  |

| <ul> <li>When the SDAA0 pin is at low level</li> <li>When IICE0 = 0 (operation stop)</li> <li>Reset</li> </ul> |                                                          | When the SDAA0 pin is at high level |  |  |  |

| SMC0 | Operation mode switching   |  |  |

|------|----------------------------|--|--|

| 0    | Operates in standard mode. |  |  |

| 1    | Operates in fast mode.     |  |  |

| DFC0                                                                                                                                                                                                                        | Digital filter operation control |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|

| 0                                                                                                                                                                                                                           | Digital filter off.              |  |  |  |  |  |

| 1                                                                                                                                                                                                                           | Digital filter on.               |  |  |  |  |  |

| Digital filter can be used only in fast mode.<br>In fast mode, the transfer clock does not vary, regardless of the DFC0 bit being set (1) or cleared (0).<br>The digital filter is used for noise elimination in fast mode. |                                  |  |  |  |  |  |

Remark IICE0: Bit 7 of IICA control register 0 (IICACTL0)

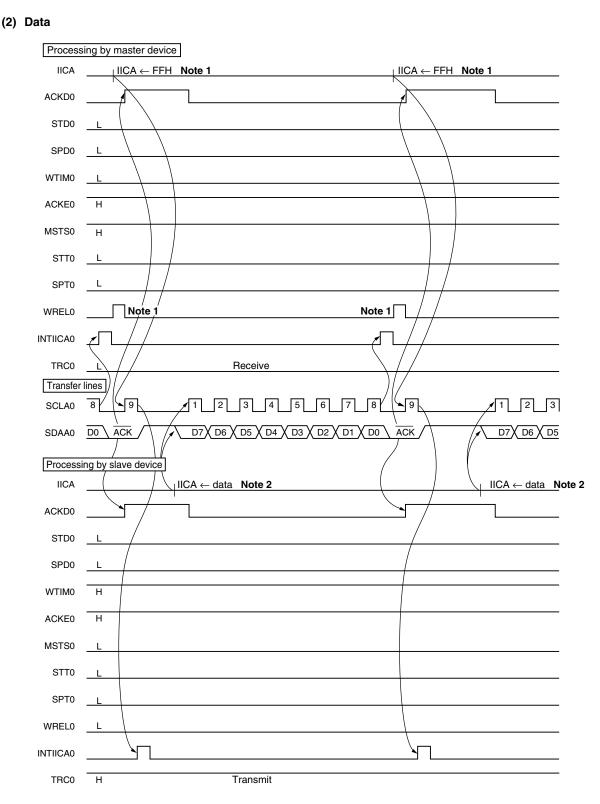

# Figure 15-34. Example of Slave to Master Communication (When 8-Clock Wait Is Selected for Master, 9-Clock Wait Is Selected for Slave) (2/3)

Notes 1. To cancel master wait, write "FFH" to IICA or set WREL0.

2. Write data to IICA, not setting WREL0, in order to cancel a wait state during slave transmission.

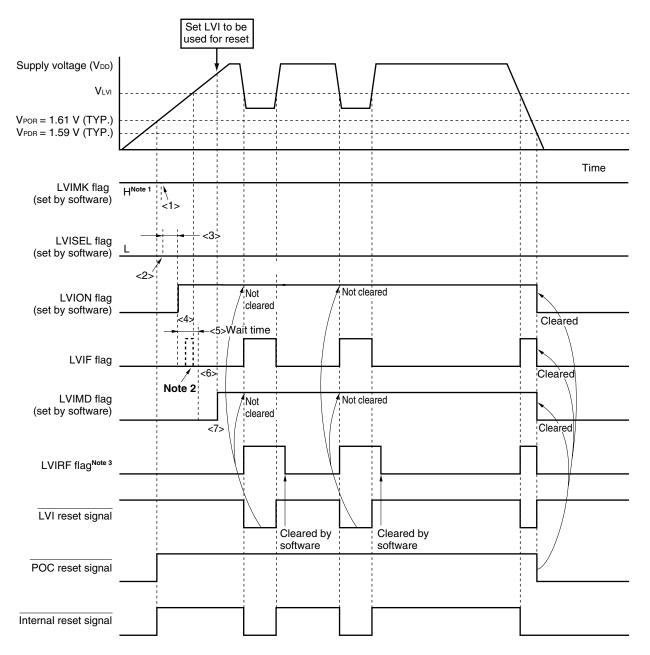

# Figure 22-5. Timing of Low-Voltage Detector Internal Reset Signal Generation (Bit: LVISEL = 0, Option Byte: LVISTART = 0)

**Notes 1.** The LVIMK flag is set to "1" by reset signal generation.

- 2. The LVIIF flag of the interrupt request flag registers and the LVIF flag may be set (1).

- 3. LVIRF is bit 0 of the reset control flag register (RESF). For details of RESF, refer to CHAPTER 20 RESET FUNCTION.

- **Remarks 1.** <1> to <7> in Figure 22-5 above correspond to <1> to <7> in the description of "When starting operation" in **22.4.1 (1) (a) When LVI default start function stopped is set (LVISTART = 0).**

- 2. VPOR: POC power supply rise detection voltage VPDR: POC power supply fall detection voltage

# CHAPTER 26 ON-CHIP DEBUG FUNCTION

### 26.1 Connecting QB-MINI2 to 78K0/Kx2-L Microcontrollers

The 78K0/Kx2-L microcontrollers use the V<sub>DD</sub>, RESET, TOOLC0/X1 (or TOOLC1/P31), TOOLD0/X2 (or TOOLD1/P32), and V<sub>ss</sub> pins to communicate with the host machine via an on-chip debug emulator (QB-MINI2). Whether TOOLC0/X1 and TOOLC1/P31, or TOOLD0/X2 and TOOLD1/P32 are used can be selected.

- Cautions 1. The 78K0/Kx2-L microcontrollers have an on-chip debug function, which is provided for development and evaluation. Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- <R>

2. When transitioning to STOP mode during on-chip debugging, oscillation of the internal high-speed oscillator continues, but the on-chip debug operation is not affected.

Remark The 78K0/KY2-L is not provided with the TOOLC1/P31 and TOOLD1/P32 pins.

| Instruction<br>Group | Mnemonic | Operands  | D: ++ - | Clocks |        |                                                                                                                                                                                                            | Flag |       |  |

|----------------------|----------|-----------|---------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--|

|                      |          |           | Bytes   | Note 1 | Note 2 | Operation                                                                                                                                                                                                  |      | AC CY |  |

| Call/return          | CALL     | !addr16   | 3       | 7      | _      | $(SP - 1) \leftarrow (PC + 3)_{H}, (SP - 2) \leftarrow (PC + 3)_{L},$<br>PC $\leftarrow$ addr16, SP $\leftarrow$ SP - 2                                                                                    |      |       |  |

|                      | CALLF    | !addr11   | 2       | 5      | _      | $\begin{split} (SP-1) \leftarrow (PC+2)_{H}, (SP-2) \leftarrow (PC+2)_{L}, \\ PC_{15-11} \leftarrow 00001, PC_{10-0} \leftarrow addr11, \\ SP \leftarrow SP-2 \end{split}$                                 |      |       |  |

|                      | CALLT    | [addr5]   | 1       | 6      | _      | $(SP - 1) \leftarrow (PC + 1)_{H}, (SP - 2) \leftarrow (PC + 1)_{L},$<br>$PC_{H} \leftarrow (addr5 + 1), PC_{L} \leftarrow (addr5),$<br>$SP \leftarrow SP - 2$                                             |      |       |  |

|                      | BRK      |           | 1       | 6      | _      | $\begin{split} (SP-1) \leftarrow PSW,  (SP-2) \leftarrow (PC+1) H, \\ (SP-3) \leftarrow (PC+1) L,  PC H \leftarrow (003FH), \\ PC L \leftarrow (003EH),  SP \leftarrow SP-3,  IE \leftarrow 0 \end{split}$ |      |       |  |

|                      | RET      |           | 1       | 6      | -      | $PC_{H} \leftarrow (SP + 1), PC_{L} \leftarrow (SP),$<br>$SP \leftarrow SP + 2$                                                                                                                            |      |       |  |

|                      | RETI     |           | 1       | 6      | -      | PC <sub>H</sub> ← (SP + 1), PC <sub>L</sub> ← (SP),<br>PSW ← (SP + 2), SP ← SP + 3                                                                                                                         | R    | RR    |  |

|                      | RETB     |           | 1       | 6      | -      | PC <sub>H</sub> ← (SP + 1), PC <sub>L</sub> ← (SP),<br>PSW ← (SP + 2), SP ← SP + 3                                                                                                                         | R    | RR    |  |

| Stack<br>manipulate  | PUSH     | PSW       | 1       | 2      | -      | $(SP - 1) \leftarrow PSW, SP \leftarrow SP - 1$                                                                                                                                                            |      |       |  |

|                      |          | rp        | 1       | 4      | -      | $(SP - 1) \leftarrow rp_H, (SP - 2) \leftarrow rp_L,$<br>$SP \leftarrow SP - 2$                                                                                                                            |      |       |  |

|                      | POP      | PSW       | 1       | 2      | -      | $PSW \leftarrow (SP),  SP \leftarrow SP + 1$                                                                                                                                                               | R    | R R   |  |

|                      |          | rp        | 1       | 4      | -      | $rp_{H} \leftarrow (SP + 1), rp_{L} \leftarrow (SP),$<br>$SP \leftarrow SP + 2$                                                                                                                            |      |       |  |

|                      | MOVW     | SP, #word | 4       | -      | 10     | $SP \leftarrow word$                                                                                                                                                                                       |      |       |  |

|                      |          | SP, AX    | 2       | -      | 8      | $SP \leftarrow AX$                                                                                                                                                                                         |      |       |  |

|                      |          | AX, SP    | 2       | -      | 8      | $AX \leftarrow SP$                                                                                                                                                                                         |      |       |  |

| Unconditional        | BR       | !addr16   | 3       | 6      | -      | $PC \leftarrow addr16$                                                                                                                                                                                     |      |       |  |

| branch               |          | \$addr16  | 2       | 6      | -      | PC ← PC + 2 + jdisp8                                                                                                                                                                                       |      |       |  |

|                      |          | AX        | 2       | 8      | -      | $PCH \leftarrow A, PC_{L} \leftarrow X$                                                                                                                                                                    |      |       |  |

| Conditional          | вс       | \$addr16  | 2       | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$ if $CY = 1$                                                                                                                                                                |      |       |  |

| branch               | BNC      | \$addr16  | 2       | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$ if $CY = 0$                                                                                                                                                                |      |       |  |

|                      | BZ       | \$addr16  | 2       | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 1$                                                                                                                                                                 |      |       |  |

|                      | BNZ      | \$addr16  | 2       | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 0$                                                                                                                                                                 |      |       |  |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

- 2. This clock cycle applies to the internal ROM program.