# E. Renesas Electronics America Inc - UPD78F0582GB-GAF-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, I <sup>2</sup> C, LINbus, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                                   |

| Number of I/O              | 33                                                                                   |

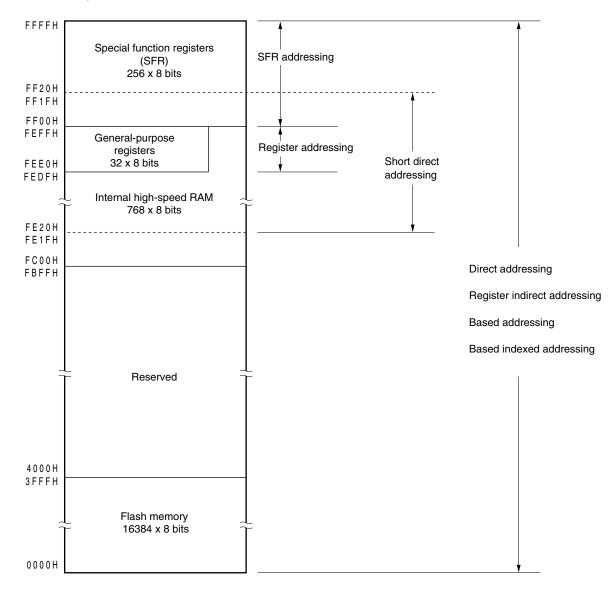

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 768 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 11x10b                                                                           |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 44-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0582gb-gaf-ax |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

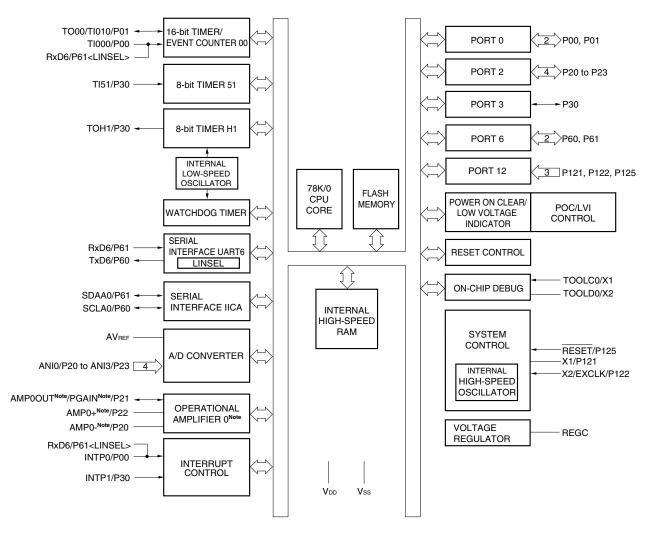

#### 1.4 Block Diagram

#### 1.4.1 78K0/KY2-L

Note µPD78F0555, 78F0556, 78F0557 (products with operational amplifier) only

- Cautions 1. Vss functions alternately as the ground potential of the A/D converter. Be sure to connect Vss to a stabilized GND (= 0 V).

- 2. Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- 3. ANI0/P20/AMP0-, ANI1/P21/AMP0OUT/PGAIN, ANI2/P22/AMP0+, and ANI3/P23 are set in the analog input mode after release of reset.

- 4. RESET/P125 immediately after release of reset is set in the external reset input.

#### (1) Port mode

P20 to P27 function as an I/O port. P20 to P27 can be set to input or output port in 1-bit units using port mode register 2 (PM2).

#### (2) Control mode

P20 to P27 function as A/D converter analog input, operational amplifier I/O, and PGA input.

#### (a) ANI0 to ANI7

These are A/D converter analog input pins. When using these pins as analog input pins, refer to (5) ANI0/P20 to ANI7/P27 and ANI8/P10 to ANI10/P12 in 12.6 Cautions for A/D Converter.

#### (b) AMP0+, AMP0-

These are operational amplifier 0 input pins.

#### (c) AMPOOUT

This is an operational amplifier 0 output pin.

#### (d) PGAIN

This is a PGA (Programmable gain amplifier) input pin.

#### Caution ANI0/P20 to ANI7/P27 are set in the analog input mode after release of reset.

#### 2.2.4 P30 to P37 (port 3)

P30 to P37 function as an I/O port. These pins also function as pins for external interrupt request input, timer I/O, clock input and data I/O for flash memory programmer/on-chip debugger, and clock I/O and data I/O for serial interface.

The timer I/O can be assigned to P34 of the 78K0/KA2-L (25-pin and 32-pin products) by setting the port alternate switch control register (MUXSEL).

| <r></r> | 78K0/KY2-L<br>(μPD78F055x) |                                                | 78K0/KA2-L<br>(μPD78F056x) |                      | 78K0/KB2-L<br>(µPD78F057x) |                         | 78K0/KC2-L<br>(μPD78F058x) |                         |

|---------|----------------------------|------------------------------------------------|----------------------------|----------------------|----------------------------|-------------------------|----------------------------|-------------------------|

|         | 16 Pins                    | 20 Pins                                        | 25 Pins                    | 32 Pins              | 30 Pins                    | 40 Pins                 | 44 Pins                    | 48 Pins                 |

|         | P30/TOH1/<br>TI51/INTP1    |                                                |                            | _                    | P30/INTP1                  | P30/INTP1               | P30/INTP1                  | P30/INTP1               |

|         | -                          | P31/INTP2/<br>TOOLC1                           | P31/INTP2/<br>TOOLC1       | P31/INTP2/<br>TOOLC1 | P31/INTP2/<br>TOOLC1       | P31/INTP2/<br>TOOLC1    | P31/INTP2/<br>TOOLC1       | P31/INTP2/<br>TOOLC1    |

|         | -                          | P32/INTP3/<br>TOOLD1                           | P32/INTP3/<br>TOOLD1       | P32/INTP3/<br>TOOLD1 | P32/INTP3/<br>TOOLD1       | P32/INTP3/<br>TOOLD1    | P32/INTP3/<br>TOOLD1       | P32/INTP3/<br>TOOLD1    |

|         | _                          | – – P33<br>– – P34/INTP4<br>(/TOH1)<br>(/TI51) |                            | P33                  | P33/TI51/<br>TO51/INTP4    | P33/TI51/<br>TO51/INTP4 | P33/TI51/<br>TO51/INTP4    | P33/TI51/<br>TO51/INTP4 |

|         | _                          |                                                |                            | P34/INTP4<br>(/TOH1) | _                          | _                       | _                          | _                       |

|         | _                          | _                                              | P35/SCK11                  | P35/SCK11            | -                          | -                       | -                          | _                       |

|         | _                          | _                                              | P36/SI11                   | P36/SI11             | -                          | _                       | _                          | _                       |

|         | _                          | _                                              | P37/SO11                   | P37/SO11             | =                          | _                       | _                          | _                       |

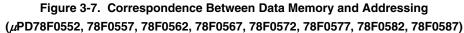

#### 3.4.9 Stack addressing

#### [Function]

The stack area is indirectly addressed with the stack pointer (SP) contents.

This addressing method is automatically employed when the PUSH, POP, subroutine call and return instructions are executed or the register is saved/reset upon generation of an interrupt request.

With stack addressing, only the internal high-speed RAM area can be accessed.

#### [Description example]

PUSH DE; when saving DE register

Operation code

1 0 1 1 0 1 0 1

#### [Illustration]

| Function Name | I/O   | Function                                                                                                                                                                                                                                                                                                                        | After Reset  | Alternate Function                                               |  |                                                         |

|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------|--|---------------------------------------------------------|

| P00           | I/O   | Port 0.                                                                                                                                                                                                                                                                                                                         | Input port   | TI000                                                            |  |                                                         |

| P01           |       | 2-bit I/O port.<br>Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                                                                                                                                                               |              | TI010/TO00                                                       |  |                                                         |

| P10           | I/O   | Port 1.                                                                                                                                                                                                                                                                                                                         | Input port   | ANI8/AMP1- <sup>Note</sup> /SCK10                                |  |                                                         |

| P11           |       | 8-bit I/O port.                                                                                                                                                                                                                                                                                                                 |              | ANI9/AMP1OUT <sup>Note</sup> /SI10                               |  |                                                         |

| P12           |       | Input/output can be specified in 1-bit units.<br>Use of an on-chip pull-up resistor can be specified by a<br>software setting.                                                                                                                                                                                                  |              | ANI10/AMP1+ <sup>Note</sup> /<br>SO10                            |  |                                                         |

| P13           |       |                                                                                                                                                                                                                                                                                                                                 |              | TxD6                                                             |  |                                                         |

| P14           |       |                                                                                                                                                                                                                                                                                                                                 |              | RxD6                                                             |  |                                                         |

| P15           |       |                                                                                                                                                                                                                                                                                                                                 |              | ТОН0                                                             |  |                                                         |

| P16           |       |                                                                                                                                                                                                                                                                                                                                 |              | TOH1/INTP5                                                       |  |                                                         |

| P17           |       |                                                                                                                                                                                                                                                                                                                                 |              | TI50/TO50                                                        |  |                                                         |

| P20           | I/O   | Port 2.                                                                                                                                                                                                                                                                                                                         | Analog input | ANI0/AMP0- <sup>Note</sup>                                       |  |                                                         |

| P21           |       |                                                                                                                                                                                                                                                                                                                                 |              | 4-bit I/O port.<br>Input/output can be specified in 1-bit units. |  | ANI1/AMP0OUT <sup>Note</sup> /<br>PGAIN <sup>Note</sup> |

| P22           |       |                                                                                                                                                                                                                                                                                                                                 |              | ANI2/AMP0+ <sup>Note</sup>                                       |  |                                                         |

| P23           |       |                                                                                                                                                                                                                                                                                                                                 |              | ANI3                                                             |  |                                                         |

| P30           | I/O   | Port 3.                                                                                                                                                                                                                                                                                                                         | Input port   | INTP1                                                            |  |                                                         |

| P31           |       | 4-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                                                                                                                                                                                |              | INTP2/TOOLC1                                                     |  |                                                         |

| P32           |       | Use of an on-chip pull-up resistor can be specified by a                                                                                                                                                                                                                                                                        |              | INTP3/TOOLD1                                                     |  |                                                         |

| P33           |       | software setting.                                                                                                                                                                                                                                                                                                               |              | TI51/TO51/INTP4                                                  |  |                                                         |

| P60           | I/O   | Port 6.                                                                                                                                                                                                                                                                                                                         | Input port   | SCLA0/INTP11                                                     |  |                                                         |

| P61           |       | <ul> <li>2-bit I/O port.</li> <li>Input/output can be specified in 1-bit units.</li> <li>Input can be set to SMBus input buffer in 1-bit units.</li> <li>Output can be set to N-ch open-drain output (V<sub>DD</sub> tolerance).</li> <li>Use of an on-chip pull-up resistor can be specified by a software setting.</li> </ul> |              | SDAA0/INTP10                                                     |  |                                                         |

| P120          | I/O   | Port 12.                                                                                                                                                                                                                                                                                                                        | Input port   | EXLVI/INTP0                                                      |  |                                                         |

| P121          | Input | 1-bit I/O port and 3-bit input port.                                                                                                                                                                                                                                                                                            |              | X1/TOOLC0                                                        |  |                                                         |

| P122          |       | For only P120 and P125, use of an on-chip pull-up resistor<br>can be specified by a software setting.                                                                                                                                                                                                                           |              | X2/EXCLK/TOOLD0                                                  |  |                                                         |

| P125          |       |                                                                                                                                                                                                                                                                                                                                 | Reset input  | RESET                                                            |  |                                                         |

| Table 4-5. Port | Functions | (78K0/KB2-L) |

|-----------------|-----------|--------------|

|-----------------|-----------|--------------|

Note  $\mu$ PD78F0576, 78F0577, and 78F0578 (products with operational amplifier) only

#### Table 5-6. CPU Clock Transition and SFR Register Setting Examples (4/4)

#### (9) CPU clock changing from subsystem clock (D) to high-speed system clock (C)<sup>Note</sup>

Note 78K0/KC2-L only

| (Setting sequence of SFR registers)                |                      |        |                    |                     |                      |                   |     |

|----------------------------------------------------|----------------------|--------|--------------------|---------------------|----------------------|-------------------|-----|

| Setting Flag of SFR Register                       | EXCLK                | OSCSEL | MSTOP              | OSTC                | XSEL <sup>Note</sup> | MCM0              | CSS |

| Status Transition                                  |                      |        |                    | Register            |                      |                   |     |

| $(D) \rightarrow (C) (X1 \text{ clock})$           | 0                    | 1      | 0                  | Must be checked     | 1                    | 1                 | 0   |

| (D) $\rightarrow$ (C) (external main system clock) | 1                    | 1      | 0                  | Must not be checked | 1                    | 1                 | 0   |

|                                                    | $\sum$               |        | $ \int $           | $\sim$              |                      | $\longrightarrow$ |     |

|                                                    | Unnecessary if these |        | Unnecessary if the |                     |                      | sary if this      |     |

registers are already set

CPU is operating with

the high-speed system clock

register is already set

Note The value of this flag can be changed only once after a reset release. This setting is not necessary if it has already been set.

#### Caution Set the clock after the supply voltage has reached the operable voltage of the clock to be set (refer to CHAPTER 28 ELECTRICAL SPECIFICATIONS).

(10) • HALT mode (E) set while CPU is operating with internal high-speed oscillation clock (B)

- HALT mode (F) set while CPU is operating with high-speed system clock (C)

- HALT mode (G) set while CPU is operating with subsystem clock (D)<sup>Note</sup>

| Status Transition                                                                 | Setting                    |

|-----------------------------------------------------------------------------------|----------------------------|

| $ \begin{array}{l} (B) \to (E) \\ (C) \to (F) \\ (D) \to (G)^{Note} \end{array} $ | Executing HALT instruction |

Note 78K0/KC2-L only

#### (11) • STOP mode (H) set while CPU is operating with internal high-speed oscillation clock (B) • STOP mode (I) set while CPU is operating with high-speed system clock (C)

| _ | (Setting sequence)                                        |                                                                   | ►                          |  |  |

|---|-----------------------------------------------------------|-------------------------------------------------------------------|----------------------------|--|--|

|   | Status Transition                                         | Setting                                                           |                            |  |  |

|   | $\begin{array}{l} (B) \to (H) \\ (C) \to (I) \end{array}$ | Stopping peripheral functions that<br>cannot operate in STOP mode | Executing STOP instruction |  |  |

<R>

Note When transitioning to the STOP mode, it is possible to achieve low power consumption by setting RMC = 56H first.

Remarks 1. (A) to (I) in Table 5-6 correspond to (A) to (I) in Figures 5-18 and 5-19.

| 2. EXCLK, OSCSEL: | Bits 7 and 6 of the clock operation mode select register (OSCCTL) |

|-------------------|-------------------------------------------------------------------|

| MSTOP:            | Bit 7 of the main OSC control register (MOC)                      |

| XSEL, MCM0:       | Bits 2 and 0 of the main clock mode register (MCM)                |

| CSS:              | Bit 4 of the processor clock control register (PCC)               |

#### 6.3 Registers Controlling 16-Bit Timer/Event Counter 00

Registers used to control 16-bit timer/event counter 00 are shown below.

- 16-bit timer mode control register 00 (TMC00)

- Capture/compare control register 00 (CRC00)

- 16-bit timer output control register 00 (TOC00)

- Prescaler mode register 00 (PRM00)

- Port alternate switch control register (MUXSEL)

- Port mode register 0 (PM0)

- Port register 0 (P0)

#### (1) 16-bit timer mode control register 00 (TMC00)

TMC00 is an 8-bit register that sets the 16-bit timer/event counter 00 operation mode, TM00 clear mode, and output timing, and detects an overflow.

Rewriting TMC00 is prohibited during operation (when TMC003 and TMC002 = other than 00). However, it can be changed when TMC003 and TMC002 are cleared to 00 (stopping operation) and when OVF00 is cleared to 0.

TMC00 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears TMC00 to 00H.

Caution 16-bit timer/event counter 00 starts operation at the moment TMC003 and TMC002 are set to values other than 00 (operation stop mode), respectively. Set TMC003 and TMC002 to 00 to stop the operation.

#### Figure 10-27. Operation when (DEV, F6, F5, F4, F3, F2, F1, F0) = (0, 0, 1, 0, 1, 1, 0, 0)

78K0/Kx2-L

|         |                         |         |         |         |         | 78K0/KC2-L<br>μPD78F058× |         |         |         |

|---------|-------------------------|---------|---------|---------|---------|--------------------------|---------|---------|---------|

| <r></r> |                         | 16 Pins | 20 Pins | 25 Pins | 32 Pins | 30 Pins                  | 40 Pins | 44 Pins | 48 Pins |

|         | 10-bit A/D<br>converter | 4 ch    | 6 ch    | 7 ch    | 11 ch   | 7 ch                     | 10 ch   | 11 ch   | 11 ch   |

#### CHAPTER 12 A/D CONVERTER

#### 12.1 Function of A/D Converter

The A/D converter converts an analog input signal into a digital value, and consists of up to 11 channels (ANI0 to ANI10) with a resolution of 10 bits.

In products with operational amplifier, ANI1 function alternately as operational amplifier 0 output (AMP0OUT) and ANI9 function alternately as operational amplifier 1 output (AMP1OUT). This enables using operational amplifiers 0 and 1 output or PGA output as an analog input source.

The A/D converter has the following function.

#### • 10-bit resolution A/D conversion

10-bit resolution A/D conversion is carried out repeatedly for one analog input channel selected from ANI0 to ANI10, operational amplifiers 0 and 1 output, and PGA output. Each time an A/D conversion operation ends, an interrupt request (INTAD) is generated.

#### (13) Bus status detector

This circuit detects whether or not the bus is released by detecting start conditions and stop conditions. However, as the bus status cannot be detected immediately following operation, the initial status is set by the STCEN bit.

Remark

STT0 bit:

Bit 1 of IICA control register 0 (IICACTL0)

SPT0 bit:

Bit 0 of IICA control register 0 (IICACTL0)

IICRSV bit:

Bit 0 of IICA flag register 0 (IICAF0)

IICBSY bit:

Bit 6 of IICA flag register 0 (IICAF0)

STCF bit:

Bit 7 of IICA flag register 0 (IICAF0)

STCEN bit:

Bit 1 of IICA flag register 0 (IICAF0)

#### 15.3 Registers Controlling Serial Interface IICA

Serial interface IICA is controlled by the following ten registers.

- IICA control register 0 (IICACTL0)

- IICA status register 0 (IICAS0)

- IICA flag register (IICAF0)

- IICA control register 1 (IICACTL1)

- IICA low-level width setting register (IICWL)

- IICA high-level width setting register (IICWH)

- Port input mode register 6 (PIM6)

- Port output mode register 6 (POM6)

- Port mode register 6 (PM6)

- Port register 6 (P6)

#### (1) IICA control register 0 (IICACTL0)

This register is used to enable/stop I<sup>2</sup>C operations, set wait timing, and set other I<sup>2</sup>C operations.

This register can be set by a 1-bit or 8-bit memory manipulation instruction. However, set the SPIE0, WTIM0, and ACKE0 bits while IICE0 = 0 or during the wait period. These bits can be set at the same time when the IICE0 bit is set from "0" to "1".

Reset signal generation clears this register to 00H.

#### **15.4 I<sup>2</sup>C Bus Mode Functions**

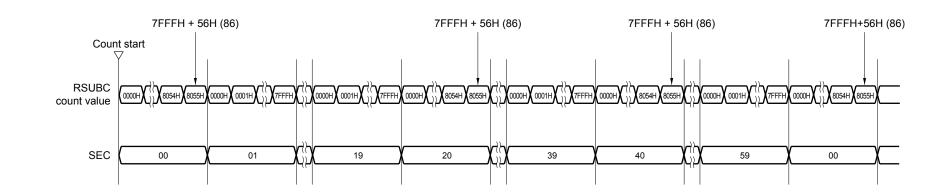

#### 15.4.1 Pin configuration

The serial clock pin (SCLA0) and serial data bus pin (SDAA0) are configured as follows.

- (1) SCLA0 .... This pin is used for serial clock input and output.

- This pin is an N-ch open-drain output for both master and slave devices. Input is Schmitt input. (2) SDAA0 .... This pin is used for serial data input and output.

This pin is an N-ch open-drain output for both master and slave devices. Input is Schmitt input.

Since outputs from the serial clock line and the serial data bus line are N-ch open-drain outputs, an external pull-up resistor is required.

Figure 15-14. Pin Configuration Diagram

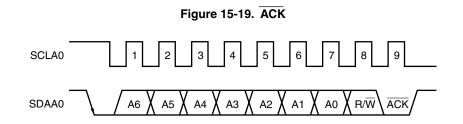

#### 15.5.4 Acknowledge (ACK)

ACK is used to check the status of serial data at the transmission and reception sides.

The reception side returns  $\overline{ACK}$  each time it has received 8-bit data.

The transmission side usually receives  $\overline{ACK}$  after transmitting 8-bit data. When  $\overline{ACK}$  is returned from the reception side, it is assumed that reception has been correctly performed and processing is continued. Whether  $\overline{ACK}$  has been detected can be checked by using bit 2 (ACKD0) of the IICA status register 0 (IICAS0).

When the master receives the last data item, it does not return  $\overrightarrow{ACK}$  and instead generates a stop condition. If a slave does not return  $\overrightarrow{ACK}$  after receiving data, the master outputs a stop condition or restart condition and stops transmission. If  $\overrightarrow{ACK}$  is not returned, the possible causes are as follows.

- <1> Reception was not performed normally.

- <2> The final data item was received.

- <3> The reception side specified by the address does not exist.

To generate ACK, the reception side makes the SDAA0 line low at the ninth clock (indicating normal reception).

Automatic generation of  $\overline{ACK}$  is enabled by setting bit 2 (ACKE0) of IICA control register 0 (IICACTL0) to 1. Bit 3 (TRC0) of the IICAS0 register is set by the data of the eighth bit that follows 7-bit address information. Usually, set ACKE0 to 1 for reception (TRC0 = 0).

If a slave can receive no more data during reception (TRC0 = 0) or does not require the next data item, then the slave must inform the master, by clearing ACKE0 to 0, that it will not receive any more data.

When the master does not require the next data item during reception (TRC0 = 0), it must clear ACKE0 to 0 so that  $\overline{ACK}$  is not generated. In this way, the master informs a slave at the transmission side that it does not require any more data (transmission will be stopped).

When the local address is received,  $\overline{ACK}$  is automatically generated, regardless of the value of the ACKE0 bit. When an address other than that of the local address is received,  $\overline{ACK}$  is not generated (NACK).

When an extension code is received, ACK is generated if the ACKE0 bit is set to 1 in advance.

How ACK is generated when data is received differs as follows depending on the setting of the wait timing.

- When 8-clock wait state is selected (bit 3 (WTIM0) of IICACTL0 register = 0): By setting the ACKE0 bit to 1 before releasing the wait state,  $\overline{ACK}$  is generated at the falling edge of the eighth clock of the SCLA0 pin.

- When 9-clock wait state is selected (bit 3 (WTIM0) of IICACTL0 register = 1): ACK is generated by setting the ACKE0 bit to 1 in advance.

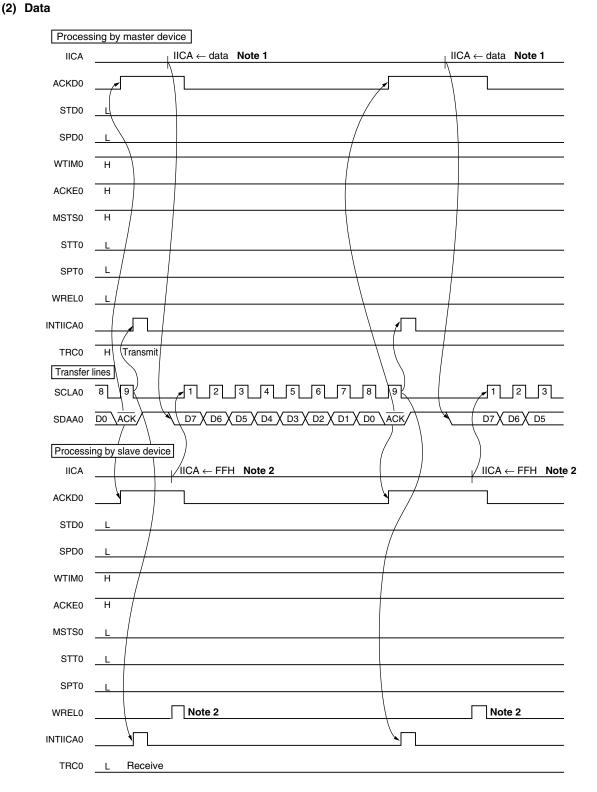

## Figure 15-33. Example of Master to Slave Communication (When 9-Clock Wait Is Selected for Both Master and Slave) (2/3)

Notes 1. Write data to IICA, not setting WREL0, in order to cancel a wait state during master transmission.2. To cancel slave wait, write "FFH" to IICA or set WREL0.

RENESAS

<R>

### Figure 17-4. Format of Interrupt Request Flag Registers (IF0L, IF0H, IF1L, IF1H) (78K0/KA2-L (25-pin and 32-pin products))

| Address: FFI | E0H After r | eset: 00H R/             | W              |                 |               |         |       |         |

|--------------|-------------|--------------------------|----------------|-----------------|---------------|---------|-------|---------|

| Symbol       | <7>         | <6>                      | <5>            | <4>             | <3>           | 2       | <1>   | <0>     |

| IFOL         | SREIF6      | PIF5                     | PIF4           | PIF3            | PIF2          | 0       | PIF0  | LVIIF   |

|              |             |                          |                |                 |               |         |       |         |

| Address: FFI | E1H After r | eset: 00H F              | R/W            |                 |               |         |       |         |

| Symbol       | <7>         | <6>                      | 5              | 4               | <3>           | <2>     | <1>   | <0>     |

| IF0H         | TMIF010     | TMIF000                  | 0              | 0               | TMIFH1        | CSIIF11 | STIF6 | SRIF6   |

|              |             |                          |                |                 |               |         |       |         |

| Address: FFI | E2H After r | eset: 00H F              | R/W            |                 |               |         |       |         |

| Symbol       | 7           | 6                        | 5              | 4               | <3>           | 2       | 1     | <0>     |

| IF1L         | 0           | 0                        | 0              | 0               | TMIF51        | 0       | 0     | ADIF    |

|              |             |                          |                |                 |               |         |       |         |

| Address: FFI | E3H After r | eset: 00H F              | R/W            |                 |               |         |       |         |

| Symbol       | 7           | 6                        | 5              | 4               | 3             | 2       | 1     | <0>     |

| IF1H         | 0           | 0                        | 0              | 0               | 0             | 0       | 0     | IICAIF0 |

|              |             |                          |                |                 |               |         |       |         |

|              | XXIFX       | X Interrupt request flag |                |                 |               |         |       |         |

|              | 0           | No interrupt             | request signa  | l is generated  |               |         |       |         |

|              | 1           | Interrupt req            | uest is genera | ated, interrupt | request statu | S       |       |         |

Caution Be sure to clear bit 2 of IF0L, bits 4 and 5 of IF0H, bits 1, 2, 4 to 7 of IF1L, and bits 1 to 7 of IF1H to 0.

### Figure 17-10. Format of Interrupt Mask Flag Registers (MK0L, MK0H, MK1L, MK1H) (78K0/KA2-L (20-pin products))

| Address: FF | E4H After re | eset: FFH     | R/W            |        |                 |        |       |         |

|-------------|--------------|---------------|----------------|--------|-----------------|--------|-------|---------|

| Symbol      | <7>          | 6             | 5              | <4>    | <3>             | <2>    | <1>   | <0>     |

| MK0L        | SREMK6       | 1             | 1              | PMK3   | PMK2            | PMK1   | PMK0  | LVIMK   |

|             |              |               |                |        |                 |        |       |         |

| Address: FF | E5H After r  | eset: FFH     | R/W            |        |                 |        |       |         |

| Symbol      | <7>          | <6>           | 5              | 4      | <3>             | 2      | <1>   | <0>     |

| МК0Н        | TMMK010      | TMMK000       | 1              | 1      | TMMKH1          | 1      | STMK6 | SRMK6   |

|             |              |               |                |        |                 |        |       |         |

| Address: FF | E6H After r  | eset: FFH     | R/W            |        |                 |        |       |         |

| Symbol      | 7            | 6             | 5              | 4      | <3>             | 2      | 1     | <0>     |

| MK1L        | 1            | 1             | 1              | 1      | TMMK51          | 1      | 1     | ADMK    |

| Address: FF | Έ7Η After r  | eset: FFH     | R/W            |        |                 |        |       |         |

| Symbol      | 7            | 6             | 5              | 4      | 3               | 2      | 1     | <0>     |

| MK1H        | , 1          | 1             | 1              | 1      | 1               | 1      | 1     | IICAMK0 |

|             |              |               |                |        |                 |        |       |         |

|             | XXMKX        |               |                | Interr | upt servicing c | ontrol |       |         |

|             | 0            | Interrupt ser | vicing enabled | k      |                 |        |       |         |

|             | 1            | Interrupt ser | vicing disable | d      |                 |        |       |         |

Caution Be sure to set bits 5 and 6 of MK0L, bits 2, 4 and 5 of MK0H, bits 1, 2, 4 to 7 of MK1L, and bits 1 to 7 of MK1H to 1.

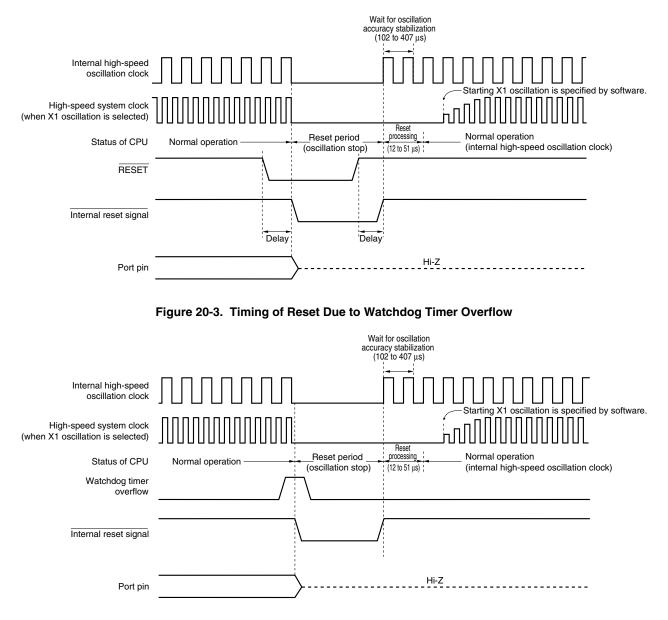

Figure 20-2. Timing of Reset by RESET Input

Caution A watchdog timer internal reset resets the watchdog timer.

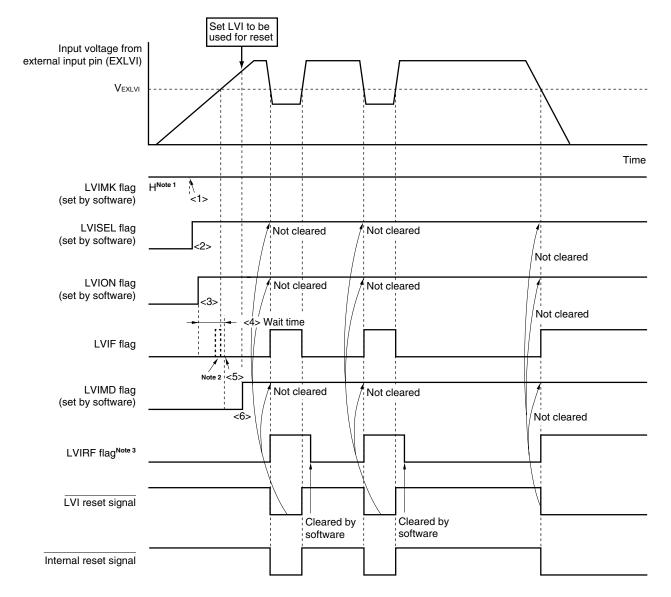

#### Figure 22-7. Timing of Low-Voltage Detector Internal Reset Signal Generation (Bit: LVISEL = 1)

- Notes 1. The LVIMK flag is set to "1" by reset signal generation.

- 2. The LVIIF flag of the interrupt request flag registers and the LVIF flag may be set (1).

- 3. LVIRF is bit 0 of the reset control flag register (RESF). For details of RESF, refer to CHAPTER 20 RESET FUNCTION.

- Remark <1> to <6> in Figure 22-7 above correspond to <1> to <6> in the description of "When starting operation" in 22.4.1 (2) When detecting level of input voltage from external input pin (EXLVI).

#### 25.3 Programming Environment

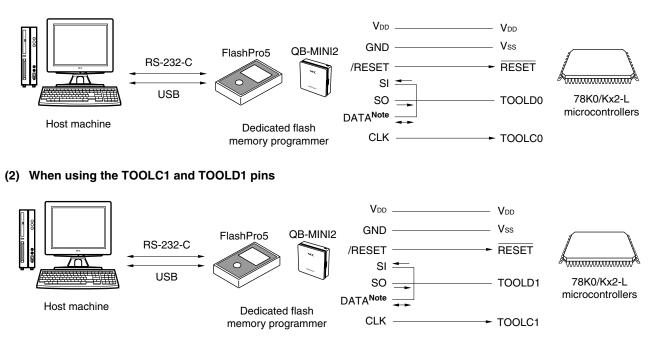

The environment required for writing a program to the flash memory of the 78K0/Kx2-L microcontrollers are illustrated below.

#### Figure 25-2. Environment for Writing Program to Flash Memory

#### (1) When using the TOOLC0 and TOOLD0 pins

#### Note QB-MINI2 only

A host machine that controls the dedicated flash memory programmer is necessary.

To interface between the dedicated flash memory programmer and the 78K0/Kx2-L microcontrollers, the TOOLD0 or TOOLD1 pins is used for manipulation such as writing and erasing via a dedicated single-line UART. To write the flash memory off-board, a dedicated program adapter (FA series) is necessary.

#### Table 25-2. Pin Connection

|                      | Dedica | 78K0/Kx2-L microcontrollers                                 |               |

|----------------------|--------|-------------------------------------------------------------|---------------|

| Signal Name          | I/O    | Pin Function                                                | Pin Name      |

| CLK                  | Output | Clock output to 78K0/Kx2-L microcontrollers                 | TOOLC0/TOOLC1 |

| SI                   | Input  | Receive signal                                              | TOOLD0/TOOLD1 |

| SO                   | Output | Transmit signal                                             |               |

| DATA <sup>Note</sup> | I/O    | Input/output signal for data communication during debugging |               |

| /RESET               | Output | Reset signal                                                | RESET         |

| VDD                  | I/O    | VDD voltage generation/power monitoring                     | Vdd           |

| GND                  | _      | Ground                                                      | Vss           |

Note QB-MINI2 only

| Instruction<br>Group    | Mnemonic | Operands      | Bytes | Clocks |        |                                                                                                                                | Flag |    | g |

|-------------------------|----------|---------------|-------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------|------|----|---|

|                         |          |               |       | Note 1 | Note 2 | Operation                                                                                                                      |      | AC | C |

| 16-bit<br>operation     | ADDW     | AX, #word     | 3     | 6      | -      | AX, CY $\leftarrow$ AX + word                                                                                                  | ×    | ×  | × |

|                         | SUBW     | AX, #word     | 3     | 6      | -      | AX, CY $\leftarrow$ AX – word                                                                                                  | ×    | ×  | × |

|                         | CMPW     | AX, #word     | 3     | 6      | -      | AX – word                                                                                                                      | ×    | ×  | × |

| Multiply/<br>divide     | MULU     | x             | 2     | 16     | -      | $AX \leftarrow A \times X$                                                                                                     |      |    |   |

|                         | DIVUW    | С             | 2     | 25     | -      | AX (Quotient), C (Remainder) $\leftarrow$ AX ÷ C                                                                               |      |    |   |

| Increment/<br>decrement | INC      | r             | 1     | 2      | -      | r ← r + 1                                                                                                                      | ×    | ×  |   |

|                         |          | saddr         | 2     | 4      | 6      | $(saddr) \leftarrow (saddr) + 1$                                                                                               | ×    | ×  |   |

|                         | DEC      | r             | 1     | 2      | _      | r ← r – 1                                                                                                                      | ×    | ×  |   |

|                         |          | saddr         | 2     | 4      | 6      | $(saddr) \leftarrow (saddr) - 1$                                                                                               | ×    | ×  |   |

|                         | INCW     | rp            | 1     | 4      | -      | $rp \leftarrow rp + 1$                                                                                                         |      |    |   |

|                         | DECW     | rp            | 1     | 4      | -      | rp ← rp – 1                                                                                                                    |      |    |   |

| Rotate                  | ROR      | A, 1          | 1     | 2      | -      | $(CY, A_7 \leftarrow A_0, A_{m-1} \leftarrow A_m) \times 1$ time                                                               |      |    | х |

|                         | ROL      | A, 1          | 1     | 2      | -      | $(CY, A_0 \leftarrow A_7, A_{m+1} \leftarrow A_m) \times 1$ time                                                               |      |    | х |

|                         | RORC     | A, 1          | 1     | 2      | _      | $(CY \leftarrow A_0, A_7 \leftarrow CY, A_{m-1} \leftarrow A_m) \times 1$ time                                                 |      |    | × |

|                         | ROLC     | A, 1          | 1     | 2      | -      | $(CY \leftarrow A_7, A_0 \leftarrow CY, A_{m+1} \leftarrow A_m) \times 1$ time                                                 |      |    | × |

|                         | ROR4     | [HL]          | 2     | 10     | 12     | A <sub>3-0</sub> ← (HL) <sub>3-0</sub> , (HL) <sub>7-4</sub> ← A <sub>3-0</sub> ,<br>(HL) <sub>3-0</sub> ← (HL) <sub>7-4</sub> |      |    |   |

|                         | ROL4     | [HL]          | 2     | 10     | 12     | $A_{3-0} \leftarrow (HL)_{7-4}, (HL)_{3-0} \leftarrow A_{3-0}, \\ (HL)_{7-4} \leftarrow (HL)_{3-0}$                            |      |    |   |

| BCD<br>adjustment       | ADJBA    |               | 2     | 4      | _      | Decimal Adjust Accumulator after Addition                                                                                      | ×    | ×  | × |

|                         | ADJBS    |               | 2     | 4      | _      | Decimal Adjust Accumulator after Subtract                                                                                      | ×    | ×  | × |

| Bit<br>manipulate       | MOV1     | CY, saddr.bit | 3     | 6      | 7      | $CY \leftarrow (saddr.bit)$                                                                                                    |      |    | × |

|                         |          | CY, sfr.bit   | 3     | -      | 7      | CY ← sfr.bit                                                                                                                   |      |    | × |

|                         |          | CY, A.bit     | 2     | 4      | -      | CY ← A.bit                                                                                                                     |      |    | × |

|                         |          | CY, PSW.bit   | 3     | -      | 7      | CY ← PSW.bit                                                                                                                   |      |    | × |

|                         |          | CY, [HL].bit  | 2     | 6      | 7      | $CY \leftarrow (HL).bit$                                                                                                       |      |    | × |

|                         |          | saddr.bit, CY | 3     | 6      | 8      | (saddr.bit) ← CY                                                                                                               |      |    |   |

|                         |          | sfr.bit, CY   | 3     | -      | 8      | sfr.bit ← CY                                                                                                                   |      |    |   |

|                         |          | A.bit, CY     | 2     | 4      | _      | A.bit ← CY                                                                                                                     |      |    |   |

|                         |          | PSW.bit, CY   | 3     | -      | 8      | PSW.bit ← CY                                                                                                                   | ×    | ×  |   |

|                         |          | [HL].bit, CY  | 2     | 6      | 8      | (HL).bit ← CY                                                                                                                  |      |    |   |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

2. This clock cycle applies to the internal ROM program.

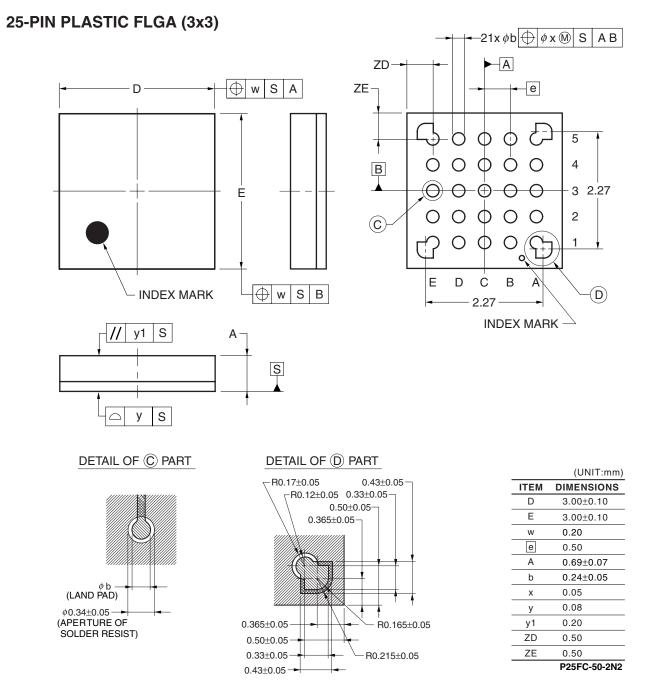

<R> • μPD78F0560FC-2N2-A, 78F0561FC-2N2-A, 78F0562FC-2N2-A, 78F0565FC-2N2-A, 78F0566FC-2N2-A, 78F0567FC-2N2-A