Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | AVR                                                                             |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 50MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 123                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                           |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3c0512c-alzr    |

# 1. Description

The AT32UC3C is a complete System-On-Chip microcontroller based on the AVR32UC RISC processor running at frequencies up to 50 MHz. AVR32UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems. Using the Secure Access Unit (SAU) together with the MPU provides the required security and integrity.

Higher computation capabilities are achievable either using a rich set of DSP instructions or using the floating-point instructions.

The AT32UC3C incorporates on-chip Flash and SRAM memories for secure and fast access. For applications requiring additional memory, an external memory interface is provided on AT32UC3C0 derivatives.

The Memory Direct Memory Access controller (MDMA) enables transfers of block of data from memories to memories without processor involvement.

The Peripheral Direct Memory Access (PDCA) controller enables data transfers between peripherals and memories without processor involvement. The PDCA drastically reduces processing overhead when transferring continuous and large data streams.

The AT32UC3C incorporates on-chip Flash and SRAM memories for secure and fast access. The FlashVault technology allows secure libraries to be programmed into the device. The secure libraries can be executed while the CPU is in Secure State, but not read by non-secure software in the device. The device can thus be shipped to end custumers, who are able to program their own code into the device, accessing the secure libraries, without any risk of compromising the proprietary secure code.

The Power Manager improves design flexibility and security. Power monitoring is supported by on-chip Power-On Reset (POR), Brown-Out Detectors (BOD18, BOD33, BOD50). The CPU runs from the on-chip RC oscillators, the PLLs, or the Multipurpose Oscillators. The Asynchronous Timer (AST) combined with the 32 KHz oscillator keeps track of the time. The AST can operate in counter or calendar mode.

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing, and pulse width modulation.

The PWM module provides four channels with many configuration options including polarity, edge alignment and waveform non overlap control. The PWM channels can operate independently, with duty cycles set independently from each other, or in interlinked mode, with multiple channels updated at the same time. It also includes safety feature with fault inputs and the ability to lock the PWM configuration registers and the PWM pin assignment.

The AT32UC3C also features many communication interfaces for communication intensive applications. In addition to standard serial interfaces like UART, SPI or TWI, other interfaces like flexible CAN, USB and Ethernet MAC are available. The USART supports different communication modes, like SPI mode and LIN mode.

The Inter-IC Sound Controller (I2SC) provides a 5-bit wide, bidirectional, synchronous, digital audio link with off-chip audio devices. The controller is compliant with the I2S bus specification.

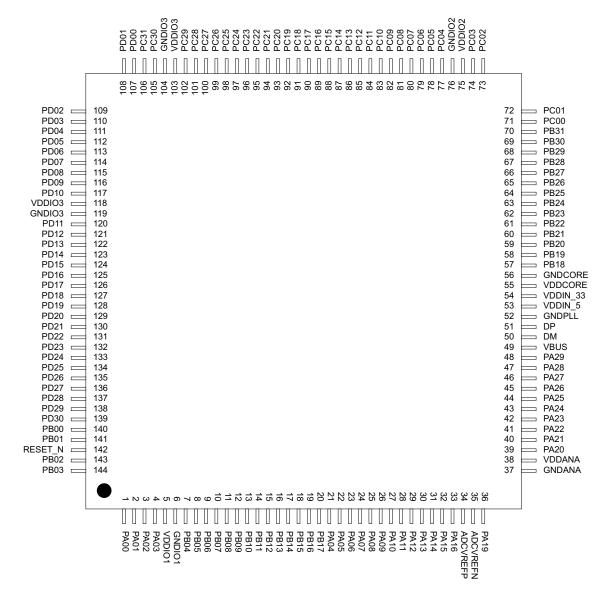

Figure 3-3. LQFP144 Pinout

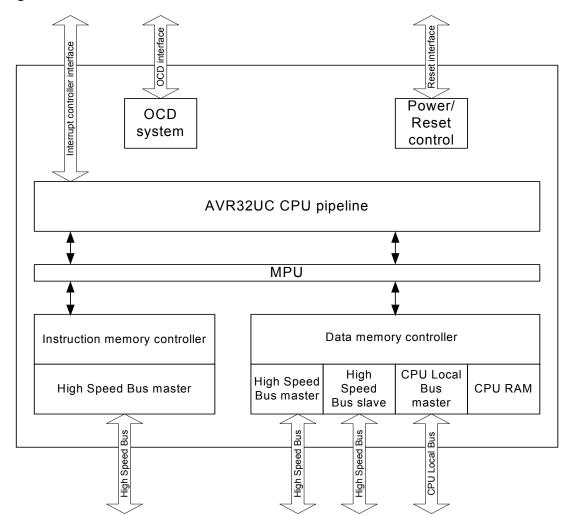

Figure 4-1. Overview of the AVR32UC CPU

# 4.3.1 Pipeline Overview

AVR32UC has three pipeline stages, Instruction Fetch (IF), Instruction Decode (ID), and Instruction Execute (EX). The EX stage is split into three parallel subsections, one arithmetic/logic (ALU) section, one multiply (MUL) section, and one load/store (LS) section.

Instructions are issued and complete in order. Certain operations require several clock cycles to complete, and in this case, the instruction resides in the ID and EX stages for the required number of clock cycles. Since there is only three pipeline stages, no internal data forwarding is required, and no data dependencies can arise in the pipeline.

Figure 4-2 on page 28 shows an overview of the AVR32UC pipeline stages.

## 4.3.2.5 Unaligned Reference Handling

AVR32UC does not support unaligned accesses, except for doubleword accesses. AVR32UC is able to perform word-aligned *st.d* and *ld.d.* Any other unaligned memory access will cause an address exception. Doubleword-sized accesses with word-aligned pointers will automatically be performed as two word-sized accesses.

The following table shows the instructions with support for unaligned addresses. All other instructions require aligned addresses.

**Table 4-1.** Instructions with Unaligned Reference Support

| Instruction Supported Alignment |      |

|---------------------------------|------|

| ld.d                            | Word |

| st.d                            | Word |

# 4.3.2.6 Unimplemented Instructions

The following instructions are unimplemented in AVR32UC, and will cause an Unimplemented Instruction Exception if executed:

- All SIMD instructions

- All coprocessor instructions if no coprocessors are present

- retj, incjosp, popjc, pushjc

- · tlbr, tlbs, tlbw

- cache

#### 4.3.2.7 CPU and Architecture Revision

Three major revisions of the AVR32UC CPU currently exist. The device described in this datasheet uses CPU revision 3.

The Architecture Revision field in the CONFIG0 system register identifies which architecture revision is implemented in a specific device.

AVR32UC CPU revision 3 is fully backward-compatible with revisions 1 and 2, ie. code compiled for revision 1 or 2 is binary-compatible with revision 3 CPUs.

Debug state can be entered as described in the *AVR32UC Technical Reference Manual*. Debug state is exited by the *retd* instruction.

#### 4.4.3.3 Secure State

The AVR32 can be set in a secure state, that allows a part of the code to execute in a state with higher security levels. The rest of the code can not access resources reserved for this secure code. Secure State is used to implement FlashVault technology. Refer to the AVR32UC Technical Reference Manual for details.

# 4.4.4 System Registers

The system registers are placed outside of the virtual memory space, and are only accessible using the privileged *mfsr* and *mtsr* instructions. The table below lists the system registers specified in the AVR32 architecture, some of which are unused in AVR32UC. The programmer is responsible for maintaining correct sequencing of any instructions following a *mtsr* instruction. For detail on the system registers, refer to the *AVR32UC Technical Reference Manual*.

Table 4-3.System Registers

| Reg# | Address | Name     | Function                               |

|------|---------|----------|----------------------------------------|

| 0    | 0       | SR       | Status Register                        |

| 1    | 4       | EVBA     | Exception Vector Base Address          |

| 2    | 8       | ACBA     | Application Call Base Address          |

| 3    | 12      | CPUCR    | CPU Control Register                   |

| 4    | 16      | ECR      | Exception Cause Register               |

| 5    | 20      | RSR_SUP  | Unused in AVR32UC                      |

| 6    | 24      | RSR_INT0 | Unused in AVR32UC                      |

| 7    | 28      | RSR_INT1 | Unused in AVR32UC                      |

| 8    | 32      | RSR_INT2 | Unused in AVR32UC                      |

| 9    | 36      | RSR_INT3 | Unused in AVR32UC                      |

| 10   | 40      | RSR_EX   | Unused in AVR32UC                      |

| 11   | 44      | RSR_NMI  | Unused in AVR32UC                      |

| 12   | 48      | RSR_DBG  | Return Status Register for Debug mode  |

| 13   | 52      | RAR_SUP  | Unused in AVR32UC                      |

| 14   | 56      | RAR_INT0 | Unused in AVR32UC                      |

| 15   | 60      | RAR_INT1 | Unused in AVR32UC                      |

| 16   | 64      | RAR_INT2 | Unused in AVR32UC                      |

| 17   | 68      | RAR_INT3 | Unused in AVR32UC                      |

| 18   | 72      | RAR_EX   | Unused in AVR32UC                      |

| 19   | 76      | RAR_NMI  | Unused in AVR32UC                      |

| 20   | 80      | RAR_DBG  | Return Address Register for Debug mode |

| 21   | 84      | JECR     | Unused in AVR32UC                      |

| 22   | 88      | JOSP     | Unused in AVR32UC                      |

| 23   | 92      | JAVA_LV0 | Unused in AVR32UC                      |

Table 4-3.

System Registers (Continued)

| Reg#    | Address  | Name      | Function                                        |

|---------|----------|-----------|-------------------------------------------------|

| 90      | 360      | MPUPSR2   | MPU Privilege Select Register region 2          |

| 91      | 364      | MPUPSR3   | MPU Privilege Select Register region 3          |

| 92      | 368      | MPUPSR4   | MPU Privilege Select Register region 4          |

| 93      | 372      | MPUPSR5   | MPU Privilege Select Register region 5          |

| 94      | 376      | MPUPSR6   | MPU Privilege Select Register region 6          |

| 95      | 380      | MPUPSR7   | MPU Privilege Select Register region 7          |

| 96      | 384      | MPUCRA    | Unused in this version of AVR32UC               |

| 97      | 388      | MPUCRB    | Unused in this version of AVR32UC               |

| 98      | 392      | MPUBRA    | Unused in this version of AVR32UC               |

| 99      | 396      | MPUBRB    | Unused in this version of AVR32UC               |

| 100     | 400      | MPUAPRA   | MPU Access Permission Register A                |

| 101     | 404      | MPUAPRB   | MPU Access Permission Register B                |

| 102     | 408      | MPUCR     | MPU Control Register                            |

| 103     | 412      | SS_STATUS | Secure State Status Register                    |

| 104     | 416      | SS_ADRF   | Secure State Address Flash Register             |

| 105     | 420      | SS_ADRR   | Secure State Address RAM Register               |

| 106     | 424      | SS_ADR0   | Secure State Address 0 Register                 |

| 107     | 428      | SS_ADR1   | Secure State Address 1 Register                 |

| 108     | 432      | SS_SP_SYS | Secure State Stack Pointer System Register      |

| 109     | 436      | SS_SP_APP | Secure State Stack Pointer Application Register |

| 110     | 440      | SS_RAR    | Secure State Return Address Register            |

| 111     | 444      | SS_RSR    | Secure State Return Status Register             |

| 112-191 | 448-764  | Reserved  | Reserved for future use                         |

| 192-255 | 768-1020 | IMPL      | IMPLEMENTATION DEFINED                          |

# 4.5 Exceptions and Interrupts

In the AVR32 architecture, events are used as a common term for exceptions and interrupts. AVR32UC incorporates a powerful event handling scheme. The different event sources, like Illegal Op-code and interrupt requests, have different priority levels, ensuring a well-defined behavior when multiple events are received simultaneously. Additionally, pending events of a higher priority class may preempt handling of ongoing events of a lower priority class.

When an event occurs, the execution of the instruction stream is halted, and execution is passed to an event handler at an address specified in Table 4-4 on page 38. Most of the handlers are placed sequentially in the code space starting at the address specified by EVBA, with four bytes between each handler. This gives ample space for a jump instruction to be placed there, jumping to the event routine itself. A few critical handlers have larger spacing between them, allowing the entire event routine to be placed directly at the address specified by the EVBA-relative offset generated by hardware. All interrupt sources have autovectored interrupt service routine (ISR) addresses. This allows the interrupt controller to directly specify the ISR address as an address

# 5. Memories

# 5.1 Embedded Memories

- Internal High-Speed Flash (See Table 5-1 on page 40)

- 512 Kbytes

- 256 Kbytes

- 128 Kbytes

- 0 Wait State Access at up to 25 MHz in Worst Case Conditions

- 1 Wait State Access at up to 50 MHz in Worst Case Conditions

- Pipelined Flash Architecture, allowing burst reads from sequential Flash locations, hiding penalty of 1 wait state access

- Pipelined Flash Architecture typically reduces the cycle penalty of 1 wait state operation to only 15% compared to 0 wait state operation

- 10 000 Write Cycles, 15-year Data Retention Capability

- Sector Lock Capabilities, Bootloader Protection, Security Bit

- 32 Fuses, Erased During Chip Erase

- User Page For Data To Be Preserved During Chip Erase

- Internal High-Speed SRAM, Single-cycle access at full speed (See Table 5-1 on page 40)

- 64 Kbytes

- 32 Kbytes

- Supplementary Internal High-Speed System SRAM (HSB RAM), Single-cycle access at full speed

- Memory space available on System Bus for peripherals data.

- 4 Kbytes

**Table 7-2.** Supply Rise Rates and Order

|                                                                   |                                          | Rise Rate |           |                                                     |  |  |

|-------------------------------------------------------------------|------------------------------------------|-----------|-----------|-----------------------------------------------------|--|--|

| Symbol                                                            | Parameter                                | Min       | Max       | Comment                                             |  |  |

| $V_{VDDIN_5}$                                                     | DC supply internal 3.3V regulator        | 0.01 V/ms | 1.25 V/us |                                                     |  |  |

| V <sub>VDDIN_33</sub>                                             | DC supply internal 1.8V regulator        | 0.01 V/ms | 1.25 V/us |                                                     |  |  |

| V <sub>VDDIO1</sub><br>V <sub>VDDIO2</sub><br>V <sub>VDDIO3</sub> | DC supply peripheral I/O                 | 0.01 V/ms | 1.25 V/us | Rise after or at the same time as VDDIN_5, VDDIN_33 |  |  |

| $V_{VDDANA}$                                                      | DC supply peripheral I/O and analog part | 0.01 V/ms | 1.25 V/us | Rise after or at the same time as VDDIN_5, VDDIN_33 |  |  |

# 7.3 Maximum Clock Frequencies

These parameters are given in the following conditions:

- V<sub>VDDCORE</sub> > 1.85 V

- Temperature = -40°C to 125°C

Table 7-3. Clock Frequencies

| Symbol              | Parameter              | Conditions              | Min | Max                | Units |

|---------------------|------------------------|-------------------------|-----|--------------------|-------|

| f <sub>CPU</sub>    | CPU clock frequency    |                         |     | 50                 | MHz   |

| f <sub>PBA</sub>    | PBA clock frequency    |                         |     | 50                 | MHz   |

| f <sub>PBB</sub>    | PBB clock frequency    |                         |     | 50                 | MHz   |

| f <sub>PBC</sub>    | PBC clock frequency    |                         |     | 50                 | MHz   |

| f <sub>GCLK0</sub>  | GCLK0 clock frequency  | Generic clock for USBC  |     | 50 <sup>(1)</sup>  | MHz   |

| f <sub>GCLK1</sub>  | GCLK1 clock frequency  | Generic clock for CANIF |     | 66 <sup>(1)</sup>  | MHz   |

| f <sub>GCLK2</sub>  | GCLK2 clock frequency  | Generic clock for AST   |     | 80 <sup>(1)</sup>  | MHz   |

| f <sub>GCLK4</sub>  | GCLK4 clock frequency  | Generic clock for PWM   |     | 120 <sup>(1)</sup> | MHz   |

| f <sub>GCLK11</sub> | GCLK11 clock frequency | Generic clock for IISC  |     | 50 <sup>(1)</sup>  | MHz   |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

# 7.4 Power Consumption

The values in Table 7-4 are measured values of power consumption under the following conditions, except where noted:

- Operating conditions core supply (Figure 7-1)

- $-V_{VDDIN 5} = V_{VDDIN 33} = 3.3V$

- $-V_{VDDCORE}$  = 1.85V, supplied by the internal regulator

- $-V_{VDDIO1} = V_{VDDIO2} = V_{VDDIO3} = 3.3V$

- $-V_{VDDANA} = 3.3V$

Table 7-36. ADC and S/H Transfer Characteristics (Continued)10-bit Resolution Mode and S/H gain from 1 to 16<sup>(1)</sup>

| Symbol | Parameter                  | Conditions                                      | Min | Тур | Max | Units |

|--------|----------------------------|-------------------------------------------------|-----|-----|-----|-------|

| RES    | Resolution                 | Differential mode,                              |     |     | 10  | Bit   |

| INL    | Integral Non-Linearity     | $V_{VDDANA} = 5V$ ,                             |     |     | 2   | LSB   |

| DNL    | Differential Non-Linearity | $V_{ADCREF0} = 3V$                              |     |     | 2   | LSB   |

|        | Offset error               | ADCFIA.SEQCFGn.SRES = 1,  S/H gain from 1 to 16 | -30 |     | 30  | mV    |

|        | Gain error                 | $(F_{adc} = 1.5MHz)$                            | -30 |     | 30  | mV    |

Note: 1. The measures are done without any I/O activity on VDDANA/GNDANA power domain.

# 7.8.7 Digital to Analog Converter (DAC) Characteristics

Table 7-37.

Channel Conversion Time and DAC Clock

| Symbol                                 | Parameter                 | Conditions                   | Min | Тур | Max                 | Units |

|----------------------------------------|---------------------------|------------------------------|-----|-----|---------------------|-------|

| f <sub>DAC</sub>                       | DAC clock frequency       |                              |     |     | 1                   | MHz   |

| t <sub>STARTUP</sub>                   | Startup time              |                              |     |     | 3                   | μs    |

| t <sub>CONV</sub> Conversion time (lat |                           | No S/H enabled, internal DAC |     |     | 1                   | μs    |

|                                        | Conversion time (latency) | One S/H                      |     |     | 1.5                 | μs    |

|                                        |                           | Two S/H                      |     |     | 2                   | μs    |

|                                        | Throughput rate           |                              |     |     | 1/t <sub>CONV</sub> | MSPS  |

Table 7-38. External Voltage Reference Input

| Symbol              | Parameter                  | Conditions | Min | Тур | Max                      | Units |

|---------------------|----------------------------|------------|-----|-----|--------------------------|-------|

| V <sub>DACREF</sub> | DACREF input voltage range |            | 1.2 |     | V <sub>VDDANA</sub> -0.7 | V     |

Table 7-39. DAC Outputs

| Symbol            | Parameter          | Conditions                  | Min | Тур | Max                      | Units |

|-------------------|--------------------|-----------------------------|-----|-----|--------------------------|-------|

|                   | Output range       | with external DAC reference | 0.2 |     | V <sub>DACREF</sub>      | V     |

|                   | Output range       | with internal DAC reference | 0.2 |     | V <sub>VDDANA</sub> -0.7 | v     |

| C <sub>LOAD</sub> | Output capacitance |                             | 0   |     | 100                      | pF    |

| R <sub>LOAD</sub> | Output resitance   |                             | 2   |     |                          | kΩ    |

# 7.8.8 Analog Comparator Characteristics

Table 7-41. Analog Comparator Characteristics<sup>(1)</sup>

| Symbol               | Parameter                    | Conditions                       | Min | Тур | Max          | Units    |  |

|----------------------|------------------------------|----------------------------------|-----|-----|--------------|----------|--|

|                      | Positive input voltage range |                                  | 0   |     | $V_{VDDANA}$ | V        |  |

|                      | Negative input voltage range |                                  | 0   |     | $V_{VDDANA}$ | V        |  |

| M                    | Offset                       | No hysteresis, Low Power mode    | -36 |     | 36           | mV       |  |

| V <sub>OFFSET</sub>  | Oliset                       | No hysteresis, High Speed mode   | -21 |     | 21           | mV       |  |

|                      | Hysteresis                   | Low hysteresis, Low Power mode   | 7   |     | 49           | mV<br>mV |  |

| W                    |                              | Low hysteresis, High Speed mode  | 5   |     | 39           |          |  |

| $V_{HYST}$           |                              | High hysteresis, Low Power mode  | 16  |     | 113          |          |  |

|                      |                              | High hysteresis, High Speed mode | 12  |     | 76           |          |  |

| +                    | Propagation delay            | Low Power mode                   |     |     | 3.3          |          |  |

| t <sub>DELAY</sub>   | Propagation delay            | High Speed mode                  |     |     | 0.102        | us       |  |

| t <sub>STARTUP</sub> | Start-up time                |                                  |     |     | 20           | μs       |  |

Note: 1. The measures are done without any I/O activity on VDDANA/GNDANA power domain.

Table 7-42. VDDANA scaled reference

| Symbol                     | Parameter                            | Min | Тур                                   | Max | Units |

|----------------------------|--------------------------------------|-----|---------------------------------------|-----|-------|

| SCF                        | ACIFA.SCFi.SCF range                 | 0   |                                       | 32  |       |

| V <sub>VDDANA</sub> scaled |                                      |     | (64 - SCF) * V <sub>VDDANA</sub> / 65 |     | V     |

|                            | V <sub>VDDANA</sub> voltage accuracy |     |                                       | 4.1 | %     |

# 7.8.9 USB Transceiver Characteristics

# 7.8.9.1 Electrical Characteristics

Table 7-43. Electrical Parameters

| Symbol           | Parameter                                | Conditions                           | Min. | Тур. | Max. | Unit |

|------------------|------------------------------------------|--------------------------------------|------|------|------|------|

| R <sub>EXT</sub> | Recommended external USB series resistor | In series with each USB pin with ±5% |      | 39   |      | Ω    |

The USB on-chip buffers comply with the Universal Serial Bus (USB) v2.0 standard. All AC parameters related to these buffers can be found within the USB 2.0 electrical specifications.

SPCK

MISO

SPI3

SPI4

MOSI

SPI5

Figure 7-12. SPI Master Mode With (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

**Table 7-48.** SPI Timing, Master Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions       | Min                              | Max  | Units |

|--------|-----------------------------------|------------------|----------------------------------|------|-------|

| SPI0   | MISO setup time before SPCK rises |                  | 30.5+ (t <sub>CLK_SPI</sub> )/2  |      | ns    |

| SPI1   | MISO hold time after SPCK rises   |                  | 0                                |      | ns    |

| SPI2   | SPCK rising to MOSI delay         | external         |                                  | 11.5 | ns    |

| SPI3   | MISO setup time before SPCK falls | capacitor = 40pF | 30.5 + (t <sub>CLK_SPI</sub> )/2 |      | ns    |

| SPI4   | MISO hold time after SPCK falls   |                  | 0                                |      | ns    |

| SPI5   | SPCK falling to MOSI delay        |                  |                                  | 11.5 | ns    |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

## Maximum SPI Frequency, Master Output

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn})$$

Where SPIn is the MOSI delay, SPI2 or SPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. Please refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

# Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

$$f_{SPCKMAX} = \frac{1}{SPIn + t_{VALID}}$$

Where  $\mathit{SPIn}$  is the MISO setup and hold time, SPI0 + SPI1 or SPI3 + SPI4 depending on CPOL and NCPHA.  $t_{VALID}$  is the SPI slave response time. Please refer to the SPI slave datasheet for  $t_{VALID}$ .

# 7.9.6 JTAG Timing

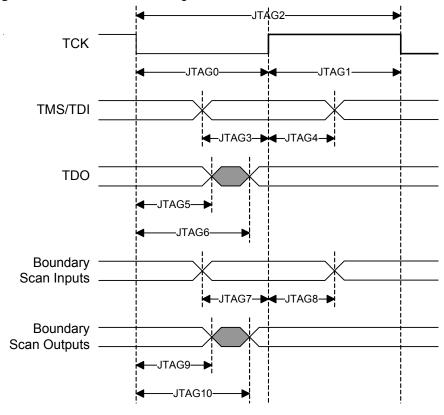

Figure 7-16. JTAG Interface Signals

Table 7-51. JTAG Timings<sup>(1)</sup>

| Symbol | Parameter                          | Conditions           | Min  | Max | Units |

|--------|------------------------------------|----------------------|------|-----|-------|

| JTAG0  | TCK Low Half-period                |                      | 23   |     | ns    |

| JTAG1  | TCK High Half-period               |                      | 9    |     | ns    |

| JTAG2  | TCK Period                         |                      | 31   |     | ns    |

| JTAG3  | TDI, TMS Setup before TCK High     |                      | 7    |     | ns    |

| JTAG4  | TDI, TMS Hold after TCK High       | external capacitor = | 0    |     | ns    |

| JTAG5  | TDO Hold Time                      |                      | 13.5 |     | ns    |

| JTAG6  | TCK Low to TDO Valid               | 40pF                 |      | 23  | ns    |

| JTAG7  | Boundary Scan Inputs Setup Time    |                      | 0    |     | ns    |

| JTAG8  | Boundary Scan Inputs Hold Time     |                      | 4.5  |     | ns    |

| JTAG9  | Boundary Scan Outputs Hold Time    |                      | 12   |     | ns    |

| JTAG10 | TCK to Boundary Scan Outputs Valid |                      |      | 19  | ns    |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

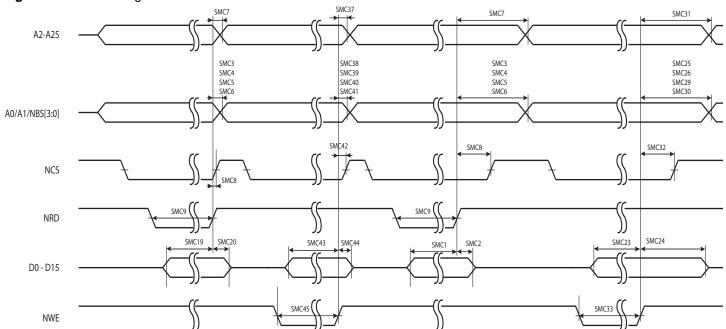

Figure 7-18. SMC Signals for NRD and NRW Controlled Accesses<sup>(1)</sup>

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

# 7.9.8 SDRAM Signals

Table 7-57. SDRAM Clock Signal

| Symbol                   | Parameter                        | Max <sup>(1)</sup> | Units |

|--------------------------|----------------------------------|--------------------|-------|

| 1/(t <sub>CPSDCK</sub> ) | SDRAM Controller clock frequency | f <sub>cpu</sub>   | MHz   |

Note: 1. The maximum frequency of the SDRAMC interface is the same as the max frequency for the HSB.

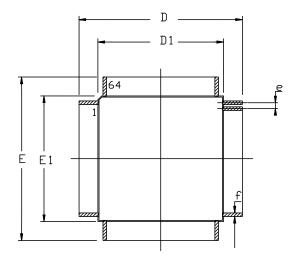

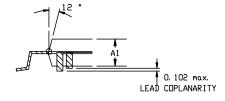

Figure 8-2. TQFP-64 package drawing

#### COMMON DIMENSIONS IN MM

| SYMBOL | Min       | Max        | NOTES |

|--------|-----------|------------|-------|

| Α      |           | 1, 20      |       |

| A1     | 0, 95     | 1, 05      |       |

| С      | 0, 09     | 0. 20      |       |

| D      | 12. 0     | 12. 00 BSC |       |

| D1     | 10. 0     | 10.00 BSC  |       |

| Е      | 12.00 BSC |            |       |

| E1     | 10.00 BSC |            |       |

| J      | 0, 05     | 0, 15      |       |

| L      | 0, 45     | 0. 75      |       |

| е      | 0.50 BSC  |            |       |

| f      | 0, 17     | 0. 27      |       |

Table 8-5.

Device and Package Maximum Weight

| ma   |

|------|

| 1119 |

|      |

Table 8-6.

Package Characteristics

| Moisture Sensitivity Level | Jdec J-STD0-20D - MSL 3 |

|----------------------------|-------------------------|

Table 8-7.Package Reference

| JEDEC Drawing Reference | MS-026 |  |  |

|-------------------------|--------|--|--|

| JESD97 Classification   | E3     |  |  |

# 8.3 Soldering Profile

Table 8-14 gives the recommended soldering profile from J-STD-20.

Table 8-14.Soldering Profile

| Profile Feature                            | Green Package            |

|--------------------------------------------|--------------------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/sec                  |

| Preheat Temperature 175°C ±25°C            | Min. 150 °C, Max. 200 °C |

| Temperature Maintained Above 217°C         | 60-150 sec               |

| Time within 5⋅C of Actual Peak Temperature | 30 sec                   |

| Peak Temperature Range                     | 260 °C                   |

| Ramp-down Rate                             | 6 °C/sec                 |

| Time 25⋅C to Peak Temperature              | Max. 8 minutes           |

Note: It is recommended to apply a soldering temperature higher than 250°C.

A maximum of three reflow passes is allowed per component.

# 9. Ordering Information

Table 9-1.

Ordering Information

| Device        | Ordering Code           | Carrier Type | Package    | Temperature Operating Range |

|---------------|-------------------------|--------------|------------|-----------------------------|

| AT32UC3C0512C | AT32UC3C0512C-ALZT      | Tray         | - LQFP 144 |                             |

| A1320C3C0312C | AT32UC3C0512C-ALZR      | Tape & Reel  | LQFF 144   |                             |

| AT32UC3C1512C | AT32UC3C1512C-AZT       | Tray         | TQFP 100   |                             |

| A132003013120 | AT32UC3C1512C-AZR       | Tape & Reel  | TQFF 100   |                             |

| AT32UC3C1256C | AT32UC3C1256C-AZT       | Tray         | TQFP 100   |                             |

| A1320C3C1256C | AT32UC3C1256C-AZR       | Tape & Reel  | TQFF 100   |                             |

| AT32UC3C2512C | AT32UC3C2512C-A2ZT      | Tray         | TQFP 64    |                             |

| A1320C3C2512C | AT32UC3C2512C-A2ZR      | Tape & Reel  |            |                             |

| AT32UC3C2512C | AT32UC3C2512C-Z2ZT      | Tray         | QFN 64     | Automotive ( 40°C to 125°C) |

| A1320C3C2512C | AT32UC3C2512C-Z2ZR      | Tape & Reel  |            | Automotive (-40°C to 125°C) |

| AT32UC3C2256C | AT32UC3C2256C-A2ZT      | Tray         | TQFP 64    |                             |

| A132003022300 | AT32UC3C2256C-A2ZR      | Tape & Reel  |            |                             |

| AT32UC3C2256C | AT32UC3C2256C-Z2ZT      | Tray         | QFN 64     |                             |

| A1320C3C2236C | AT32UC3C2256C-Z2ZR      | Tape & Reel  | QFN 04     |                             |

| AT32UC3C2128C | AT32UC3C2128C-A2ZT Tray | TOED 04      |            |                             |

| A132003021280 | AT32UC3C2128C-A2ZR      | Tape & Reel  | TQFP 64    |                             |

| AT32UC3C2128C | AT32UC3C2128C-Z2ZT      | Tray         | OFN 64     |                             |

| A132003021280 | AT32UC3C2128C-Z2ZR      | Tape & Reel  | QFN 64     |                             |

# 4 SPI bad serial clock generation on 2nd chip\_select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

#### Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

#### 10.1.7 TC

# 1 Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

#### Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the SR.CPCS bit, reconfigure the RA and RC registers for the lower channel with the real values.

#### 10.1.8 TWIM

# 1 SMBALERT bit may be set after reset

For TWIM0 and TWIM1 modules, the SMBus Alert (SMBALERT) bit in the Status Register (SR) might be erroneously set after system reset.

#### Fix/Workaround

After system reset, clear the SR.SMBALERT bit before commencing any TWI transfer.

For TWIM2 module, the SMBus Alert (SMBALERT) is not implemented but the bit in the Status Register (SR) is erroneously set once TWIM2 is enabled.

# Fix/Workaround

None.

#### 10.1.9 TWIS

#### I Clearing the NAK bit before the BTF bit is set locks up the TWI bus

When the TWIS is in transmit mode, clearing the NAK Received (NAK) bit of the Status Register (SR) before the end of the Acknowledge/Not Acknowledge cycle will cause the TWIS to attempt to continue transmitting data, thus locking up the bus.

# Fix/Workaround

Clear SR.NAK only after the Byte Transfer Finished (BTF) bit of the same register has been set.

#### 10.1.10 USBC

## 1 UPINRQx.INRQ field is limited to 8-bits

In Host mode, when using the UPINRQx.INRQ feature together with the multi-packet mode to launch a finite number of packet among multi-packet, the multi-packet size (located in the descriptor table) is limited to the UPINRQx.INRQ value multiply by the pipe size.

#### Fix/Workaround

UPINRQx.INRQ value shall be less than the number of configured multi-packet.

#### 2 In USB host mode, downstream resume feature does not work (UHCON.RESUME=1).

# 2 Requesting clocks in idle sleep modes will mask all other PB clocks than the requested

In idle or frozen sleep mode, all the PB clocks will be frozen if the TWIS or the AST need to wake the cpu up.

#### Fix/Workaround

Disable the TWIS or the AST before entering idle or frozen sleep mode.

# 3 TWIS may not wake the device from sleep mode

If the CPU is put to a sleep mode (except Idle and Frozen) directly after a TWI Start condition, the CPU may not wake upon a TWIS address match. The request is NACKed.

#### Fix/Workaround

When using the TWI address match to wake the device from sleep, do not switch to sleep modes deeper than Frozen. Another solution is to enable asynchronous EIC wake on the TWIS clock (TWCK) or TWIS data (TWD) pins, in order to wake the system up on bus events.

#### 10.2.6 SCIF

### 1 PLLCOUNT value larger than zero can cause PLLEN glitch

Initializing the PLLCOUNT with a value greater than zero creates a glitch on the PLLEN signal during asynchronous wake up.

## Fix/Workaround

The lock-masking mechanism for the PLL should not be used.

The PLLCOUNT field of the PLL Control Register should always be written to zero.

## 2 PLL lock might not clear after disable

Under certain circumstances, the lock signal from the Phase Locked Loop (PLL) oscillator may not go back to zero after the PLL oscillator has been disabled. This can cause the propagation of clock signals with the wrong frequency to parts of the system that use the PLL clock.

#### Fix/Workaround

PLL must be turned off before entering STOP, DEEPSTOP or STATIC sleep modes. If PLL has been turned off, a delay of 30us must be observed after the PLL has been enabled again before the SCIF.PLL0LOCK bit can be used as a valid indication that the PLL is locked.

## 3 BOD33 reset locks the device

If BOD33 is enabled as a reset source (SCIF.BOD33.CTRL=0x1) and when VDDIN\_33 power supply voltage falls below the BOD33 voltage (SCIF.BOD33.LEVEL), the device is locked permanently under reset even if the power supply goes back above BOD33 reset level. In order to unlock the device, an external reset event should be applied on RESET\_N.

#### Fix/Workaround

Use an external BOD on VDDIN\_33 or an external reset source.

## 10.2.7 SPI

# 1 SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0

When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI module will not start a data transfer.

#### Fix/Workaround

Disable mode fault detection by writing a one to MR.MODFDIS.

#### 10.2.12 WDT

# 1 Clearing the Watchdog Timer (WDT) counter in second half of timeout period will issue a Watchdog reset

If the WDT counter is cleared in the second half of the timeout period, the WDT will immediately issue a Watchdog reset.

#### Fix/Workaround

Use twice as long timeout period as needed and clear the WDT counter within the first half of the timeout period. If the WDT counter is cleared after the first half of the timeout period, you will get a Watchdog reset immediately. If the WDT counter is not cleared at all, the time before the reset will be twice as long as needed.

# 2 WDT Control Register does not have synchronization feedback

When writing to the Timeout Prescale Select (PSEL), Time Ban Prescale Select (TBAN), Enable (EN), or WDT Mode (MODE) fieldss of the WDT Control Register (CTRL), a synchronizer is started to propagate the values to the WDT clcok domain. This synchronization takes a finite amount of time, but only the status of the synchronization of the EN bit is reflected back to the user. Writing to the synchronized fields during synchronization can lead to undefined behavior.

### Fix/Workaround

- -When writing to the affected fields, the user must ensure a wait corresponding to 2 clock cycles of both the WDT peripheral bus clock and the selected WDT clock source.

- -When doing writes that changes the EN bit, the EN bit can be read back until it reflects the written value.

| +  | SCIF: Added VREGOR register                                  |

|----|--------------------------------------------------------------|

| 5  | AST: Updated digital tuner formula                           |

| 6  | SDRAMC: cleaned-up SDCS/NCS names. Added VERSION register    |

| 7  | SAU: Updated SR.IDLE                                         |

| 3  | USART: Updated                                               |

| 9  | CANIF: Updated address map figure                            |

| 10 | USBC: Updated                                                |

| 11 | DACIFB: Updated                                              |

| 12 | Programming and Debugging: Added JTAG Data Registers section |

| 13 | Electrical Characteristics: Updated                          |

| 14 | Ordering Information: Updated                                |

| 15 | Errata: Updated                                              |

# 11.4 Rev. A - 10/10

1 Initial revision