Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | AVR                                                                          |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 66MHz                                                                        |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                 |

| Number of I/O              | 45                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 64K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 11x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3c2256c-a2zr |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Description

The AT32UC3C is a complete System-On-Chip microcontroller based on the AVR32UC RISC processor running at frequencies up to 50 MHz. AVR32UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems. Using the Secure Access Unit (SAU) together with the MPU provides the required security and integrity.

Higher computation capabilities are achievable either using a rich set of DSP instructions or using the floating-point instructions.

The AT32UC3C incorporates on-chip Flash and SRAM memories for secure and fast access. For applications requiring additional memory, an external memory interface is provided on AT32UC3C0 derivatives.

The Memory Direct Memory Access controller (MDMA) enables transfers of block of data from memories to memories without processor involvement.

The Peripheral Direct Memory Access (PDCA) controller enables data transfers between peripherals and memories without processor involvement. The PDCA drastically reduces processing overhead when transferring continuous and large data streams.

The AT32UC3C incorporates on-chip Flash and SRAM memories for secure and fast access. The FlashVault technology allows secure libraries to be programmed into the device. The secure libraries can be executed while the CPU is in Secure State, but not read by non-secure software in the device. The device can thus be shipped to end custumers, who are able to program their own code into the device, accessing the secure libraries, without any risk of compromising the proprietary secure code.

The Power Manager improves design flexibility and security. Power monitoring is supported by on-chip Power-On Reset (POR), Brown-Out Detectors (BOD18, BOD33, BOD50). The CPU runs from the on-chip RC oscillators, the PLLs, or the Multipurpose Oscillators. The Asynchronous Timer (AST) combined with the 32 KHz oscillator keeps track of the time. The AST can operate in counter or calendar mode.

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be inde-

AT32UC3C

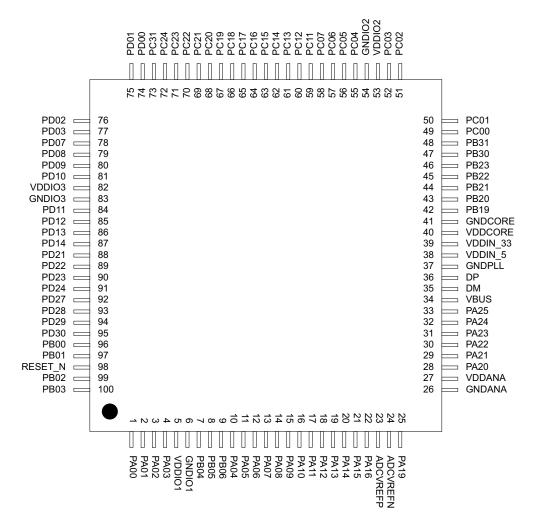

Figure 3-2. TQFP100 Pinout

# 5. Memories

# 5.1 Embedded Memories

- Internal High-Speed Flash (See Table 5-1 on page 40)

- 512 Kbytes

- 256 Kbytes

- 128 Kbytes

- O Wait State Access at up to 25 MHz in Worst Case Conditions

- 1 Wait State Access at up to 50 MHz in Worst Case Conditions

- Pipelined Flash Architecture, allowing burst reads from sequential Flash locations, hiding penalty of 1 wait state access

- Pipelined Flash Architecture typically reduces the cycle penalty of 1 wait state operation to only 15% compared to 0 wait state operation

- 10 000 Write Cycles, 15-year Data Retention Capability

- Sector Lock Capabilities, Bootloader Protection, Security Bit

- 32 Fuses, Erased During Chip Erase

- User Page For Data To Be Preserved During Chip Erase

- Internal High-Speed SRAM, Single-cycle access at full speed (See Table 5-1 on page 40)

- 64 Kbytes

- 32 Kbytes

- Supplementary Internal High-Speed System SRAM (HSB RAM), Single-cycle access at full speed

- Memory space available on System Bus for peripherals data.

- 4 Kbytes

## Table 5-3.Peripheral Address Mapping

| prierai Audres | siviapping |                                                                     |

|----------------|------------|---------------------------------------------------------------------|

| 0xFFFF0C00     | AST        | Asynchronous Timer - AST                                            |

| 0xFFFF1000     | WDT        | Watchdog Timer - WDT                                                |

| 0xFFFF1400     | EIC        | External Interrupt Controller - EIC                                 |

| 0xFFFF1800     | FREQM      | Frequency Meter - FREQM                                             |

| 0xFFFF2000     | GPIO       | General Purpose Input/Output Controller - GPIO                      |

| 0xFFFF2800     | USART0     | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART0 |

| 0xFFFF2C00     | USART2     | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART2 |

| 0xFFFF3000     | USART3     | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART3 |

| 0xFFFF3400     | SPI1       | Serial Peripheral Interface - SPI1                                  |

| 0xFFFF3800     | TWIMO      | Two-wire Master Interface - TWIM0                                   |

| 0xFFFF3C00     | TWIM1      | Two-wire Master Interface - TWIM1                                   |

| 0xFFFF4000     | TWIS0      | Two-wire Slave Interface - TWIS0                                    |

| 0xFFFF4400     | TWIS1      | Two-wire Slave Interface - TWIS1                                    |

| 0xFFFF4800     | IISC       | Inter-IC Sound (I2S) Controller - IISC                              |

| 0xFFFF4C00     | PWM        | Pulse Width Modulation Controller - PWM                             |

| 0xFFFF5000     | QDEC0      | Quadrature Decoder - QDEC0                                          |

| 0xFFFF5400     | QDEC1      | Quadrature Decoder - QDEC1                                          |

| 0xFFFF5800     | TC1        | Timer/Counter - TC1                                                 |

| 0xFFFF5C00     | PEVC       | Peripheral Event Controller - PEVC                                  |

|                |            |                                                                     |

| Port | Register                             | Mode   | Local Bus<br>Address | Access     |

|------|--------------------------------------|--------|----------------------|------------|

| В    | Output Driver Enable Register (ODER) | WRITE  | 0x40000140           | Write-only |

|      |                                      | SET    | 0x40000144           | Write-only |

|      |                                      | CLEAR  | 0x40000148           | Write-only |

|      |                                      | TOGGLE | 0x4000014C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000150           | Write-only |

|      |                                      | SET    | 0x40000154           | Write-only |

|      |                                      | CLEAR  | 0x40000158           | Write-only |

|      |                                      | TOGGLE | 0x4000015C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000160           | Read-only  |

| C (  | Output Driver Enable Register (ODER) | WRITE  | 0x40000240           | Write-only |

|      |                                      | SET    | 0x40000244           | Write-only |

|      |                                      | CLEAR  | 0x40000248           | Write-only |

|      |                                      | TOGGLE | 0x4000024C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000250           | Write-only |

|      |                                      | SET    | 0x40000254           | Write-only |

|      |                                      | CLEAR  | 0x40000258           | Write-only |

|      |                                      | TOGGLE | 0x4000025C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000260           | Read-only  |

| D    | Output Driver Enable Register (ODER) | WRITE  | 0x40000340           | Write-only |

|      |                                      | SET    | 0x40000344           | Write-only |

|      |                                      | CLEAR  | 0x40000348           | Write-only |

|      |                                      | TOGGLE | 0x4000034C           | Write-only |

|      | Output Value Register (OVR)          | WRITE  | 0x40000350           | Write-only |

|      |                                      | SET    | 0x40000354           | Write-only |

|      |                                      | CLEAR  | 0x40000358           | Write-only |

|      |                                      | TOGGLE | 0x4000035C           | Write-only |

|      | Pin Value Register (PVR)             | -      | 0x40000360           | Read-only  |

Table 5-4.

Local bus mapped GPIO registers

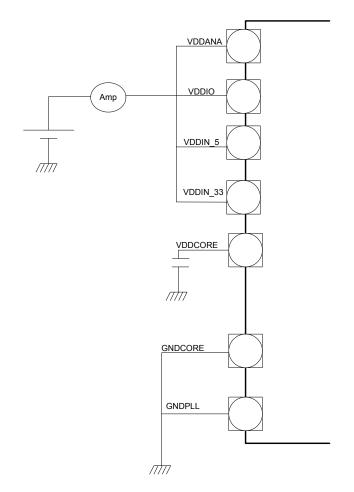

#### Figure 7-1. Measurement Schematic

#### 7.4.1 Peripheral Power Consumption

The values in Table 7-5 are measured values of power consumption under the following conditions.

• Operating conditions core supply (Figure 7-1)

$-V_{VDDIN_5} = V_{DDIN_{33}} = 3.3V$

- $V_{VDDCORE} = 1.85V$ , supplied by the internal regulator

- V<sub>VDDIO1</sub> = V<sub>VDDIO2</sub> = V<sub>VDDIO3</sub> = 3.3V

- $-V_{VDDANA} = 3.3V$

- Internal 3.3V regulator is off.

- TA = 25°C

- I/Os are configured as inputs, with internal pull-up enabled.

- Oscillators

- OSC0/1 (crystal oscillator) stopped

- OSC32K (32KHz crystal oscillator) stopped

- PLL0 running

- PLL1 stopped

- Clocks

- External clock on XIN0 as main clock source.

- CPU, HSB, and PB clocks undivided

Consumption active is the added current consumption when the module clock is turned on and when the module is doing a typical set of operations.

| Peripheral            | Typ Consumption Active | Unit   |

|-----------------------|------------------------|--------|

| ACIFA <sup>(1)</sup>  | 3                      |        |

| ADCIFA <sup>(1)</sup> | 7                      |        |

| AST                   | 3                      | -      |

| CANIF                 | 25                     | -      |

| DACIFB <sup>(1)</sup> | 3                      | -      |

| EBI                   | 23                     | -      |

| EIC                   | 0.5                    |        |

| FREQM                 | 0.5                    | _      |

| GPIO                  | 37                     | -      |

| INTC                  | 3                      | -      |

| MDMA                  | 4                      | -      |

| PDCA                  | 24                     | -      |

| PEVC                  | 15                     | -      |

| PWM                   | 40                     | -      |

| QDEC                  | 3                      | µA/MHz |

| SAU                   | 3                      |        |

| SDRAMC                | 2                      |        |

| SMC                   | 9                      |        |

| SPI                   | 5                      |        |

| тс                    | 8                      |        |

| ТШМ                   | 2                      |        |

| TWIS                  | 2                      |        |

| USART                 | 10                     |        |

| USBC                  | 5                      |        |

| WDT                   | 2                      |        |

Table 7-5.

Typical Current Consumption by Peripheral<sup>(2)</sup>

Notes: 1. Includes the current consumption on VDDANA.

2. These numbers are valid for the measured condition only and must not be extrapolated to other frequencies.

## 7.6.3 Phase Lock Loop (PLL0 and PLL1) Characteristics

| Symbol               | Parameter                          | Conditions                       | Min | Тур | Max | Unit |

|----------------------|------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>VCO</sub>     | Output frequency                   |                                  | 80  |     | 240 | MHz  |

| f <sub>IN</sub>      | Input frequency                    |                                  | 4   |     | 16  | MHz  |

| 1                    | Current consumption                | Active mode, $f_{VCO} = 80 MHz$  |     | 250 |     | μA   |

| IPLL                 |                                    | Active mode, $f_{VCO} = 240 MHz$ |     | 600 |     |      |

|                      | Startup time, from enabling        | Wide Bandwidth mode disabled     |     | 15  |     |      |

| t <sub>STARTUP</sub> | the PLL until the PLL is<br>locked | Wide Bandwidth mode enabled      |     | 45  |     | μs   |

#### **Table 7-11.**PLL Characteristics

## 7.6.4 120 MHz RC Oscillator (RC120M) Characteristics

#### Table 7-12. Internal 120MHz RC Oscillator Characteristics

| Symbol               | Parameter                       | Conditions | Min | Тур  | Max | Unit |

|----------------------|---------------------------------|------------|-----|------|-----|------|

| f <sub>OUT</sub>     | Output frequency <sup>(1)</sup> |            | 88  | 120  | 152 | MHz  |

| I <sub>RC120M</sub>  | Current consumption             |            |     | 1.85 |     | mA   |

| t <sub>STARTUP</sub> | Startup time                    |            |     | 3    |     | μs   |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

#### 7.6.5 System RC Oscillator (RCSYS) Characteristics

#### Table 7-13. System RC Oscillator Characteristics

| Symbol           | Parameter        | Conditions                         | Min | Тур   | Max | Unit |

|------------------|------------------|------------------------------------|-----|-------|-----|------|

|                  |                  | Calibrated at $T_A = 125^{\circ}C$ | 110 | 115.2 | 120 |      |

| f <sub>OUT</sub> | Output frequency | $T_A = 25^{\circ}C$                | 105 | 109   | 115 | kHz  |

|                  |                  | $T_A = -40^{\circ}C$               | 100 | 104   | 108 |      |

#### 7.6.6 8MHz/1MHz RC Oscillator (RC8M) Characteristics

#### Table 7-14. 8MHz/1MHz RC Oscillator Characteristics

| Symbol               | Parameter        | Conditions                             | Min   | Тур | Max   | Unit |

|----------------------|------------------|----------------------------------------|-------|-----|-------|------|

| f Output froquency   |                  | SCIF.RCCR8.FREQMODE = $0^{(1)}$        | 7.5   | 8   | 8.5   |      |

| t <sub>OUT</sub>     | Output frequency | SCIF.RCCR8.FREQMODE = 1 <sup>(1)</sup> | 0.925 | 1   | 1.075 | MHz  |

| t <sub>STARTUP</sub> | Startup time     |                                        |       |     | 20    | μs   |

Notes: 1. Please refer to the SCIF chapter for details.

# 7.8.6 Analog to Digital Converter (ADC) and sample and hold (S/H) Characteristics

| Symbol                            | Parameter        | Conditions                                                            | Min | Тур | Max                 | Units     |

|-----------------------------------|------------------|-----------------------------------------------------------------------|-----|-----|---------------------|-----------|

|                                   |                  | 12-bit resolution mode, $V_{VDDANA} = 3V$                             |     |     | 1.2                 |           |

|                                   |                  | 10-bit resolution mode, $V_{VDDANA} = 3V$                             |     |     | 1.6                 |           |

| £                                 | ADC clock        | 8-bit resolution mode, $V_{VDDANA} = 3V$                              |     |     | 2.2                 | MHz       |

| f <sub>ADC</sub>                  | frequency        | 12-bit resolution mode, $V_{VDDANA} = 4.5V$                           |     |     | 1.5                 |           |

|                                   |                  | 10-bit resolution mode, $V_{VDDANA} = 4.5V$                           |     |     | 2                   | _         |

|                                   |                  | 8-bit resolution mode, $V_{VDDANA} = 4.5V$                            |     |     | 2.4                 |           |

|                                   |                  | ADC cold start-up                                                     |     |     | 1                   | ms        |

| t <sub>STARTUP</sub> Startup time | ADC hot start-up |                                                                       |     | 24  | ADC clock<br>cycles |           |

|                                   | Conversion time  | (ADCIFA.SEQCFGn.SRES)/2 + 2,<br>ADCIFA.CFG.SHD = 1                    | 6   |     | 8                   | ADC clock |

| t <sub>CONV</sub>                 | (latency)        | (ADCIFA.SEQCFGn.SRES)/2 + 3,<br>ADCIFA.CFG.SHD = 0                    | 7   |     | 9                   | cycles    |

|                                   |                  | 12-bit resolution,<br>ADC clock = 1.2 MHz, V <sub>VDDANA</sub> = 3V   |     |     | 1.2                 |           |

|                                   |                  | 10-bit resolution,<br>ADC clock = 1.6 MHz, V <sub>VDDANA</sub> = 3V   |     |     | 1.6                 | MODO      |

| Inrougnput                        | Throughput rate  | 12-bit resolution,<br>ADC clock = 1.5 MHz, V <sub>VDDANA</sub> = 4.5V |     |     | 1.5                 | – MSPS    |

|                                   |                  | 10-bit resolution,<br>ADC clock = 2 MHz, V <sub>VDDANA</sub> = 4.5V   |     |     | 2                   |           |

## Table 7-27. ADC and S/H characteristics

# Table 7-28. ADC Reference Voltage

| Symbol               | Parameter                     | Conditions                                         | Min | Тур                     | Max                      | Unit<br>s |

|----------------------|-------------------------------|----------------------------------------------------|-----|-------------------------|--------------------------|-----------|

| V                    |                               | 5V Range                                           | 1   |                         | 3.5                      | V         |

| V <sub>ADCREF0</sub> | ADCREF0 input voltage range   | 3V Range                                           | 1   |                         | V <sub>VDDANA</sub> -0.7 | v         |

| V <sub>ADCREF1</sub> |                               | 5V Range                                           | 1   |                         | 3.5                      | V         |

|                      | ADCREF1 input voltage range   | 3V Range                                           | 1   |                         | V <sub>VDDANA</sub> -0.7 | - V       |

|                      |                               | 5V Range - Voltage reference applied on ADCREFP    | 1   |                         | 3.5                      | V         |

| V <sub>ADCREFP</sub> | ADCREFP input voltage         | 3V Range - Voltage reference<br>applied on ADCREFP | 1   |                         | V <sub>VDDANA</sub> -0.7 | V         |

| VADCREFN             | ADCREFN input voltage         | Voltage reference applied on<br>ADCREFN            |     | GNDANA                  |                          | V         |

|                      | Internal 1V reference         |                                                    |     | 1.0                     |                          | V         |

|                      | Internal 0.6*VDDANA reference |                                                    |     | 0.6*V <sub>VDDANA</sub> |                          | V         |

AT32UC3C

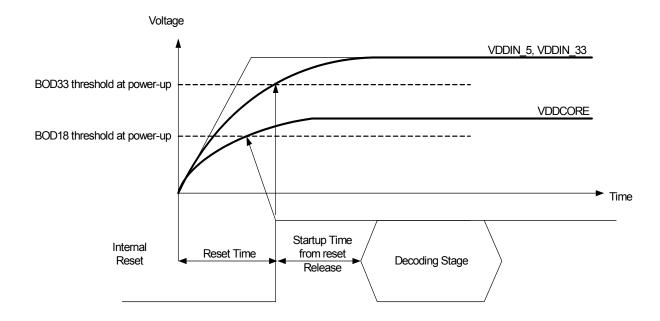

Figure 7-5. Startup and Reset Time

### 7.9.2 RESET\_N characteristics

| Symbol             | Parameter                    | Condition | Min.                   | Тур. | Max. | Units        |

|--------------------|------------------------------|-----------|------------------------|------|------|--------------|

| t <sub>RESET</sub> | RESET_N minimum pulse length |           | 2 * T <sub>RCSYS</sub> |      |      | clock cycles |

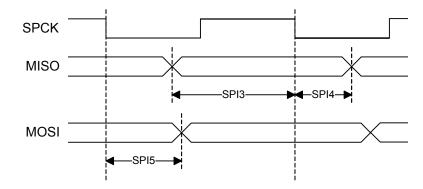

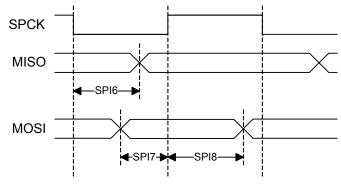

Figure 7-12. SPI Master Mode With (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

#### Table 7-48. SPI Timing, Master Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions          | Min                              | Max  | Units |

|--------|-----------------------------------|---------------------|----------------------------------|------|-------|

| SPI0   | MISO setup time before SPCK rises |                     | 30.5+ (t <sub>CLK_SPI</sub> )/2  |      | ns    |

| SPI1   | MISO hold time after SPCK rises   |                     | 0                                |      | ns    |

| SPI2   | SPCK rising to MOSI delay         | external            |                                  | 11.5 | ns    |

| SPI3   | MISO setup time before SPCK falls | capacitor =<br>40pF | 30.5 + (t <sub>CLK_SPI</sub> )/2 |      | ns    |

| SPI4   | MISO hold time after SPCK falls   |                     | 0                                |      | ns    |

| SPI5   | SPCK falling to MOSI delay        |                     |                                  | 11.5 | ns    |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

#### Maximum SPI Frequency, Master Output

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI delay, SPI2 or SPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. Please refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

#### Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

$$f_{SPCKMAX} = \frac{1}{SPIn + t_{VALID}}$$

Where *SPIn* is the MISO setup and hold time, SPI0 + SPI1 or SPI3 + SPI4 depending on CPOL and NCPHA.  $t_{VALID}$  is the SPI slave response time. Please refer to the SPI slave datasheet for  $t_{VALID}$ .

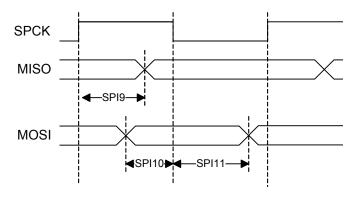

#### 7.9.4.2 Slave mode

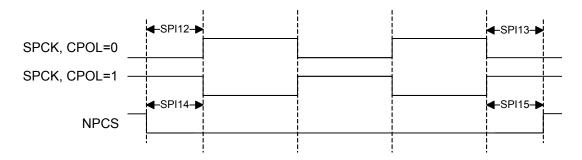

Figure 7-13. SPI Slave Mode With (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

Figure 7-14. SPI Slave Mode With (CPOL= NCPHA= 0) or (CPOL= NCPHA= 1)

Figure 7-15. SPI Slave Mode NPCS Timing

TWIM and TWIS user interface registers. Please refer to the TWIM and TWIS sections for more information.

Table 7-50. **TWI-Bus Timing Requirements**

|                         |                              |                         | Minin              | num                 | Maxin       | num                  |      |

|-------------------------|------------------------------|-------------------------|--------------------|---------------------|-------------|----------------------|------|

| Symbol                  | Parameter                    | Mode                    | Requirement        | Device              | Requirement | Device               | Unit |

| 4                       |                              | Standard <sup>(1)</sup> | -                  |                     | 100         | 00                   |      |

| t <sub>r</sub>          | TWCK and TWD rise time       | Fast <sup>(1)</sup>     | 20 + 0             | .1 C <sub>b</sub>   | 30          | 0                    | ns   |

|                         |                              | Standard <sup>(1)</sup> | -                  |                     | 30          | 0                    |      |

| t <sub>f</sub>          | TWCK and TWD fall time       | Fast <sup>(1)</sup>     | 20 + 0             | .1 C <sub>b</sub>   | 30          | 0                    | ns   |

|                         |                              | Standard <sup>(1)</sup> | 4.0                | t <sub>clkpb</sub>  | -           |                      | μs   |

| t <sub>HD-STA</sub>     | (Repeated) START hold time   | Fast <sup>(1)</sup>     | 0.6                |                     |             |                      |      |

|                         |                              | Standard <sup>(1)</sup> | 4.7                |                     |             |                      |      |

| t <sub>SU-STA</sub>     | (Repeated) START set-up time | Fast <sup>(1)</sup>     | 0.6                | t <sub>clkpb</sub>  | -           |                      | μs   |

|                         |                              | Standard <sup>(1)</sup> | 4.0                | 41                  |             |                      |      |

| t <sub>SU-STO</sub>     | STOP set-up time             | Fast <sup>(1)</sup>     | 0.6                | 4t <sub>clkpb</sub> | -           |                      | μS   |

|                         |                              | Standard <sup>(1)</sup> | 0.3 <sup>(2)</sup> | 01                  | 3.45        | 00                   |      |

| t <sub>HD-DAT</sub>     | Data hold time               | Fast <sup>(1)</sup>     | 0.3                | 2t <sub>clkpb</sub> | 0.9         | ??                   | μS   |

|                         | Dete est un time             | Standard <sup>(1)</sup> | 250                | 01                  |             |                      |      |

| t <sub>SU-DAT-I2C</sub> | Data set-up time             | Fast <sup>(1)</sup>     | 100                | 2t <sub>clkpb</sub> | -           |                      | ns   |

| t <sub>SU-DAT</sub>     |                              | -                       | -                  | t <sub>clkpb</sub>  | -           |                      | -    |

|                         | TWOK LOW paried              | Standard <sup>(1)</sup> | 4.7                | 44                  |             |                      | _    |

| t <sub>LOW-I2C</sub>    | TWCK LOW period              | Fast <sup>(1)</sup>     | 1.3                | 4t <sub>clkpb</sub> | -           |                      | μS   |

| t <sub>LOW</sub>        |                              | -                       | -                  | t <sub>clkpb</sub>  | -           |                      | -    |

|                         | TWOKLUCLEstad                | Standard <sup>(1)</sup> | 4.0                | 04                  |             |                      |      |

| t <sub>HIGH</sub>       | TWCK HIGH period             | Fast <sup>(1)</sup>     | 0.6                | 8t <sub>clkpb</sub> | -           |                      | μS   |

| t.                      |                              | Standard <sup>(1)</sup> |                    | 1                   | 100         | 1                    |      |

| f <sub>тwcк</sub>       | TWCK frequency               | Fast <sup>(1)</sup>     | -                  |                     | 400         | 12t <sub>clkpb</sub> | kHz  |

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ . 2. A device must internally provide a hold time of at least 300 ns for TWD with reference to the falling edge of TWCK.

Notations:

C<sub>b</sub> = total capacitance of one bus line in pF

$t_{clkpb}$  = period of TWI peripheral bus clock

$t_{prescaled}$  = period of TWI internal prescaled clock (see chapters on TWIM and TWIS)

The maximum  $t_{HD;DAT}$  has only to be met if the device does not stretch the LOW period ( $t_{LOW-I2C}$ ) of TWCK.

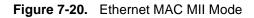

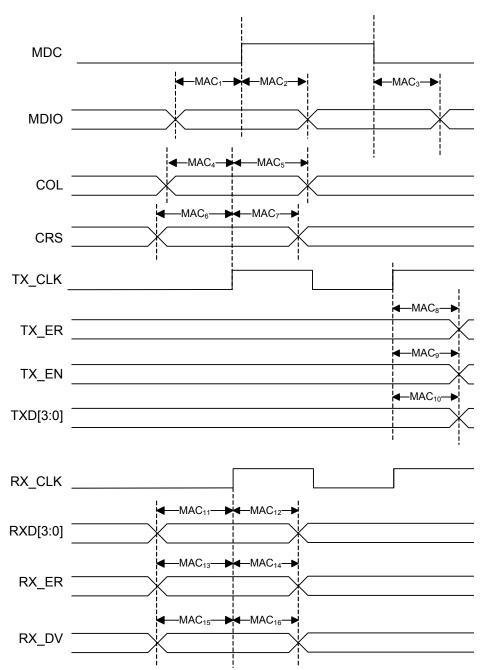

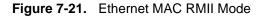

| Symbol            | Parameter                         | Conditions                                            | Min. | Max. | Unit |

|-------------------|-----------------------------------|-------------------------------------------------------|------|------|------|

| MAC <sub>21</sub> | TX_EN toggling from TX_CLK rising |                                                       | 12.5 | 13.4 | ns   |

| MAC <sub>22</sub> | TXD toggling from TX_CLK rising   | V <sub>VDD</sub> = 3.0V,                              | 12.5 | 13.4 | ns   |

| MAC <sub>23</sub> | Setup for RXD from TX_CLK         |                                                       | 4.7  |      | ns   |

| MAC <sub>24</sub> | Hold for RXD from TX_CLK          | drive strength of the pads set to the                 | 0    |      | ns   |

| MAC <sub>25</sub> | Setup for RX_ER from TX_CLK       | highest,<br>external capacitor = 10pF on MACB<br>pins | 3.6  |      | ns   |

| MAC <sub>26</sub> | Hold for RX_ER from TX_CLK        |                                                       | 0    |      | ns   |

| MAC <sub>27</sub> | Setup for RX_DV from TX_CLK       |                                                       | 4.6  |      | ns   |

| MAC <sub>28</sub> | Hold for RX_DV from TX_CLK        |                                                       | 0    |      | ns   |

#### Table 7-61. Ethernet MAC RMII Specific Signals<sup>(1)</sup>

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

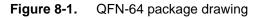

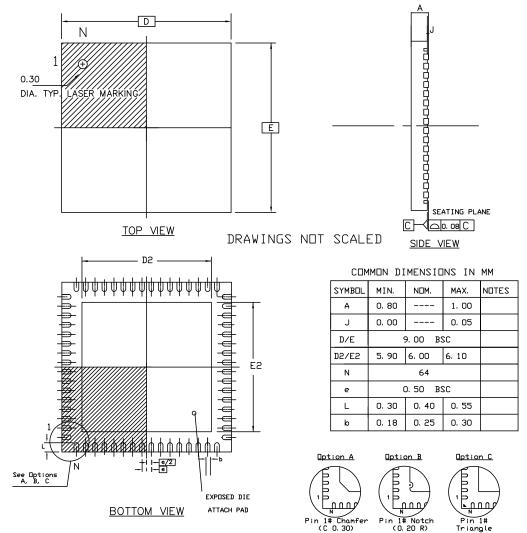

# 8.2 Package Drawings

Note: The exposed pad is not connected to anything internally, but should be soldered to ground to increase board level reliability.

| 200          |                         | mg                      |  |

|--------------|-------------------------|-------------------------|--|

| Table 8-3.   | Package Characteristics |                         |  |

| Moisture Ser | nsitivity Level         | Jdec J-STD0-20D - MSL 3 |  |

| Table 8-4.   | Package Reference       |                         |  |

| JEDEC Drav   | ving Reference          | MS-026                  |  |

| JESD97 Cla   | ssification             | E3                      |  |

Fix/Workaround

#### 2 Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

#### Fix/Workaround

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

# 3 SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode.

#### **Fix/Workaround**

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

#### 4 SPI bad serial clock generation on 2nd chip select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

#### Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

#### 10.2.8 TC

#### 1 Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

#### Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the SR.CPCS bit, reconfigure the RA and RC registers for the lower channel with the real values.

#### 10.2.9 TWIM

#### 1 SMBALERT bit may be set after reset

For TWIM0 and TWIM1 modules, the SMBus Alert (SMBALERT) bit in the Status Register (SR) might be erroneously set after system reset. Fix/Workaround

After system reset, clear the SR.SMBALERT bit before commencing any TWI transfer.

For TWIM2 module, the SMBus Alert (SMBALERT) is not implemented but the bit in the Status Register (SR) is erroneously set once TWIM2 is enabled. Fix/Workaround None.

#### 2 TWIM TWALM polarity is wrong

The TWALM signal in the TWIM is active high instead of active low. Fix/Workaround

Use an external inverter to invert the signal going into the TWIM. When using both TWIM and TWIS on the same pins, the TWALM cannot be used.

#### 10.2.12 WDT

# 1 Clearing the Watchdog Timer (WDT) counter in second half of timeout period will issue a Watchdog reset

If the WDT counter is cleared in the second half of the timeout period, the WDT will immediately issue a Watchdog reset.

#### Fix/Workaround

Use twice as long timeout period as needed and clear the WDT counter within the first half of the timeout period. If the WDT counter is cleared after the first half of the timeout period, you will get a Watchdog reset immediately. If the WDT counter is not cleared at all, the time before the reset will be twice as long as needed.

#### 2 WDT Control Register does not have synchronization feedback

When writing to the Timeout Prescale Select (PSEL), Time Ban Prescale Select (TBAN), Enable (EN), or WDT Mode (MODE) fieldss of the WDT Control Register (CTRL), a synchronizer is started to propagate the values to the WDT clcok domain. This synchronization takes a finite amount of time, but only the status of the synchronization of the EN bit is reflected back to the user. Writing to the synchronized fields during synchronization can lead to undefined behavior.

#### Fix/Workaround

-When writing to the affected fields, the user must ensure a wait corresponding to 2 clock cycles of both the WDT peripheral bus clock and the selected WDT clock source.

-When doing writes that changes the EN bit, the EN bit can be read back until it reflects the written value.

# AT32UC3C

|          | 7.7                                           | Flash Characteristics                                                       | 59                             |

|----------|-----------------------------------------------|-----------------------------------------------------------------------------|--------------------------------|

|          | 7.8                                           | Analog Characteristics                                                      | 60                             |

|          | 7.9                                           | Timing Characteristics                                                      | 69                             |

| 8        | Mecha                                         | nical Characteristics                                                       | 89                             |

|          | 8.1                                           | Thermal Considerations                                                      | 89                             |

|          | 8.2                                           | Package Drawings                                                            | 90                             |

|          | 8.3                                           | Soldering Profile                                                           | 94                             |

| 9        | Orderi                                        | ng Information                                                              | 95                             |

|          |                                               |                                                                             |                                |

| 10       | Errata                                        |                                                                             |                                |

| 10       | <i>Errata</i><br>10.1                         | rev E                                                                       |                                |

| 10       |                                               |                                                                             | 96                             |

| 10<br>11 | 10.1<br>10.2                                  | rev E                                                                       | 96<br>100                      |

| -        | 10.1<br>10.2                                  | rev E<br>rev D                                                              | 96<br>100<br><b>105</b>        |

| -        | 10.1<br>10.2<br><b>Datash</b>                 | rev E<br>rev D<br>neet Revision History                                     | 96<br>100<br><b>105</b><br>105 |

| -        | 10.1<br>10.2<br><b>Datash</b><br>11.1         | rev E<br>rev D<br><b>neet Revision History</b><br>Rev. D – 01/12            | 96<br>                         |

| -        | 10.1<br>10.2<br><b>Datash</b><br>11.1<br>11.2 | rev E<br>rev D<br>neet Revision History<br>Rev. D – 01/12<br>Rev. C – 08/11 | 96<br>                         |