Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | AVR                                                                          |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 66MHz                                                                        |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                 |

| Number of I/O              | 45                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 64K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 11x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3c2512c-a2zt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# AT32UC3C

- One 4-Channel 20-bit Pulse Width Modulation Controller (PWM)

- Complementary outputs, with Dead Time Insertion

- Output Override and Fault Protection

- Two Quadrature Decoders

- One 16-channel 12-bit Pipelined Analog-To-Digital Converter (ADC)

- Dual Sample and Hold Capability Allowing 2 Synchronous Conversions

- Single-Ended and Differential Channels, Window Function

- Two 12-bit Digital-To-Analog Converters (DAC), with Dual Output Sample System

- Four Analog Comparators

- Six 16-bit Timer/Counter (TC) Channels

- External Clock Inputs, PWM, Capture and Various Counting Capabilities

- One Peripheral Event Controller

- Trigger Actions in Peripherals Depending on Events Generated from Peripherals or from Input Pins

- Deterministic Trigger

- 34 Events and 22 Event Actions

- Five Universal Synchronous/Asynchronous Receiver/Transmitters (USART)

- Independent Baudrate Generator, Support for SPI, LIN, IrDA and ISO7816 interfaces

- Support for Hardware Handshaking, RS485 Interfaces and Modem Line

- Two Master/Slave Serial Peripheral Interfaces (SPI) with Chip Select Signals

- One Inter-IC Sound (I2S) Controller

- Compliant with I2S Bus Specification

- Time Division Multiplexed mode

- Three Master and Three Slave Two-Wire Interfaces (TWI), 400 kbit/s I<sup>2</sup>C-compatible

- QTouch<sup>®</sup> Library Support

- Capacitive Touch Buttons, Sliders, and Wheels

- QTouch<sup>®</sup> and QMatrix<sup>®</sup> Acquisition

- On-Chip Non-intrusive Debug System

- Nexus Class 2+, Runtime Control, Non-Intrusive Data and Program Trace

- aWire<sup>™</sup> single-pin programming trace and debug interface muxed with reset pin

- NanoTrace<sup>™</sup> provides trace capabilities through JTAG or aWire interface

- 3 package options

- 64-pin QFN/TQFP (45 GPIO pins)

- 100-pin TQFP (81 GPIO pins)

- 144-pin LQFP (123 GPIO pins)

- Two operating voltage ranges:

- Single 5V Power Supply

- Single 3.3V Power Supply

AT32UC3C

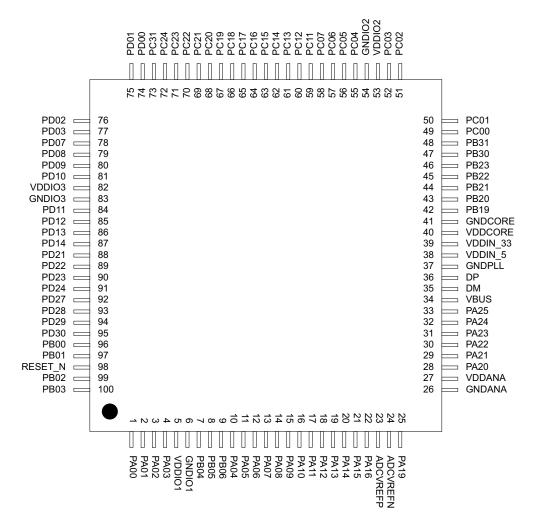

Figure 3-2. TQFP100 Pinout

| Table 3-1. | GPIO Controller Function Multiplexing |

|------------|---------------------------------------|

|------------|---------------------------------------|

| TQFP           |             |             |      | G           |        |                    |                   |                          | GPIO fu                   | Inction                   |                  |   |

|----------------|-------------|-------------|------|-------------|--------|--------------------|-------------------|--------------------------|---------------------------|---------------------------|------------------|---|

| /<br>QFN<br>64 | TQFP<br>100 | LQFP<br>144 | PIN  | P<br>I<br>O | Supply | Pin<br>Type<br>(1) | А                 | в                        | с                         | D                         | E                | F |

| 16             | 25          | 36          | PA19 | 19          | VDDANA | x1/x2              | ADCIN8            | EIC -<br>EXTINT[1]       |                           |                           |                  |   |

| 19             | 28          | 39          | PA20 | 20          | VDDANA | x1/x2              | ADCIN9            | AC0AP0                   | AC0AP0 or<br>DAC0A        |                           |                  |   |

| 20             | 29          | 40          | PA21 | 21          | VDDANA | x1/x2              | ADCIN10           | AC0BN0                   | AC0BN0 or<br>DAC0B        |                           |                  |   |

| 21             | 30          | 41          | PA22 | 22          | VDDANA | x1/x2              | ADCIN11           | AC0AN0                   | PEVC -<br>PAD_EVT<br>[4]  |                           | MACB -<br>SPEED  |   |

| 22             | 31          | 42          | PA23 | 23          | VDDANA | x1/x2              | ADCIN12           | AC0BP0                   | PEVC -<br>PAD_EVT<br>[5]  |                           | MACB -<br>WOL    |   |

|                | 32          | 43          | PA24 | 24          | VDDANA | x1/x2              | ADCIN13           | SPI1 -<br>NPCS[2]        |                           |                           |                  |   |

|                | 33          | 44          | PA25 | 25          | VDDANA | x1/x2              | ADCIN14           | SPI1 -<br>NPCS[3]        | EIC -<br>EXTINT[0]        |                           |                  |   |

|                |             | 45          | PA26 | 26          | VDDANA | x1/x2              | AC0AP1            | EIC -<br>EXTINT[1]       |                           |                           |                  |   |

|                |             | 46          | PA27 | 27          | VDDANA | x1/x2              | AC0AN1            | EIC -<br>EXTINT[2]       |                           |                           |                  |   |

|                |             | 47          | PA28 | 28          | VDDANA | x1/x2              | AC0BP1            | EIC -<br>EXTINT[3]       |                           |                           |                  |   |

|                |             | 48          | PA29 | 29          | VDDANA | x1/x2              | AC0BN1            | EIC -<br>EXTINT[0]       |                           |                           |                  |   |

| 62             | 96          | 140         | PB00 | 32          | VDDIO1 | x1                 | USART0 -<br>CLK   | CANIF -<br>RXLINE[1]     | EIC -<br>EXTINT[8]        | PEVC -<br>PAD_EVT<br>[10] |                  |   |

| 63             | 97          | 141         | PB01 | 33          | VDDIO1 | x1                 |                   | CANIF -<br>TXLINE[1]     |                           | PEVC -<br>PAD_EVT<br>[11] |                  |   |

|                | 99          | 143         | PB02 | 34          | VDDIO1 | x1                 |                   | USBC - ID                | PEVC -<br>PAD_EVT<br>[6]  | TC1 - A1                  |                  |   |

|                | 100         | 144         | PB03 | 35          | VDDIO1 | x1                 |                   | USBC -<br>VBOF           | PEVC -<br>PAD_EVT<br>[7]  |                           |                  |   |

|                | 7           | 7           | PB04 | 36          | VDDIO1 | x1/x2              | SPI1 -<br>MOSI    | CANIF -<br>RXLINE[0]     | QDEC1 -<br>QEPI           |                           | MACB -<br>TXD[2] |   |

|                | 8           | 8           | PB05 | 37          | VDDIO1 | x1/x2              | SPI1 -<br>MISO    | CANIF -<br>TXLINE[0]     | PEVC -<br>PAD_EVT<br>[12] | USART3-<br>CLK            | MACB -<br>TXD[3] |   |

|                | 9           | 9           | PB06 | 38          | VDDIO1 | x2/x4              | SPI1 -<br>SCK     |                          | QDEC1 -<br>QEPA           | USART1-<br>CLK            | MACB -<br>TX_ER  |   |

|                |             | 10          | PB07 | 39          | VDDIO1 | x1/x2              | SPI1 -<br>NPCS[0] | EIC -<br>EXTINT[2]       | QDEC1 -<br>QEPB           |                           | MACB -<br>RX_DV  |   |

|                |             | 11          | PB08 | 40          | VDDIO1 | x1/x2              | SPI1 -<br>NPCS[1] | PEVC -<br>PAD_EVT<br>[1] | PWM -<br>PWML[0]          |                           | MACB -<br>RXD[0] |   |

|                |             | 12          | PB09 | 41          | VDDIO1 | x1/x2              | SPI1 -<br>NPCS[2] |                          | PWM -<br>PWMH[0]          |                           | MACB -<br>RXD[1] |   |

|                |             | 13          | PB10 | 42          | VDDIO1 | x1/x2              | USART1 -<br>DTR   | SPI0 -<br>MOSI           | PWM -<br>PWML[1]          |                           |                  |   |

# Table 3-7.Signal Description List

| Signal Name                         | Function                                                  | Туре                           | Active<br>Level | Comments |  |  |  |  |

|-------------------------------------|-----------------------------------------------------------|--------------------------------|-----------------|----------|--|--|--|--|

| ADCVREFN                            | Analog negative reference connected to external capacitor | Analog                         |                 |          |  |  |  |  |

|                                     | Auxiliary Por                                             | rt - AUX                       |                 |          |  |  |  |  |

| MCKO Trace Data Output Clock Output |                                                           |                                |                 |          |  |  |  |  |

| MDO[5:0]                            | Trace Data Output                                         | Output                         |                 |          |  |  |  |  |

| MSEO[1:0]                           | Trace Frame Control                                       | Output                         |                 |          |  |  |  |  |

| EVTI_N                              | Event In                                                  | Output                         | Low             |          |  |  |  |  |

| EVTO_N                              | Event Out                                                 | Output                         | Low             |          |  |  |  |  |

|                                     | aWire - /                                                 | AW                             | I               |          |  |  |  |  |

| DATA                                | aWire data                                                | I/O                            |                 |          |  |  |  |  |

| DATAOUT                             | aWire data output for 2-pin mode                          | I/O                            |                 |          |  |  |  |  |

|                                     | Controller Area Network                                   | <pre>&lt; Interface - CA</pre> | NIF             |          |  |  |  |  |

| RXLINE[1:0]                         | CAN channel rxline                                        | I/O                            |                 |          |  |  |  |  |

| TXLINE[1:0]                         | CAN channel txline                                        | I/O                            |                 |          |  |  |  |  |

|                                     | DAC Interface -                                           | DACIFB0/1                      | I               | 1        |  |  |  |  |

| DAC0A, DAC0B                        | DAC0 output pins of S/H A                                 | Analog                         |                 |          |  |  |  |  |

| DAC1A, DAC1B                        | DAC output pins of S/H B                                  | Analog                         |                 |          |  |  |  |  |

| DACREF                              | Analog reference voltage input                            | Analog                         |                 |          |  |  |  |  |

|                                     | External Bus Inte                                         | erface - EBI                   | I               | 1        |  |  |  |  |

| ADDR[23:0]                          | Address Bus                                               | Output                         |                 |          |  |  |  |  |

| CAS                                 | Column Signal                                             | Output                         | Low             |          |  |  |  |  |

| DATA[15:0]                          | Data Bus                                                  | I/O                            |                 |          |  |  |  |  |

| NCS[3:0]                            | Chip Select                                               | Output                         | Low             |          |  |  |  |  |

| NRD                                 | Read Signal                                               | Output                         | Low             |          |  |  |  |  |

| NWAIT                               | External Wait Signal                                      | Input                          | Low             |          |  |  |  |  |

| NWE0                                | Write Enable 0                                            | Output                         | Low             |          |  |  |  |  |

| NWE1                                | Write Enable 1                                            | Output                         | Low             |          |  |  |  |  |

| RAS                                 | Row Signal                                                | Output                         | Low             |          |  |  |  |  |

| SDA10                               | SDRAM Address 10 Line                                     | Output                         |                 |          |  |  |  |  |

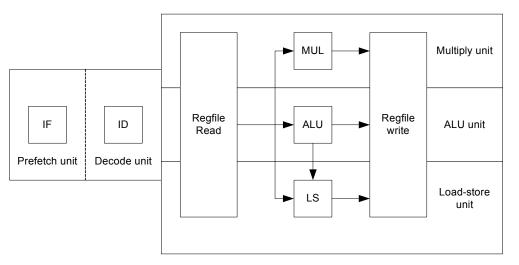

# Figure 4-2. The AVR32UC Pipeline

# 4.3.2 AVR32A Microarchitecture Compliance

AVR32UC implements an AVR32A microarchitecture. The AVR32A microarchitecture is targeted at cost-sensitive, lower-end applications like smaller microcontrollers. This microarchitecture does not provide dedicated hardware registers for shadowing of register file registers in interrupt contexts. Additionally, it does not provide hardware registers for the return address registers and return status registers. Instead, all this information is stored on the system stack. This saves chip area at the expense of slower interrupt handling.

# 4.3.2.1 Interrupt Handling

Upon interrupt initiation, registers R8-R12 are automatically pushed to the system stack. These registers are pushed regardless of the priority level of the pending interrupt. The return address and status register are also automatically pushed to stack. The interrupt handler can therefore use R8-R12 freely. Upon interrupt completion, the old R8-R12 registers and status register are restored, and execution continues at the return address stored popped from stack.

The stack is also used to store the status register and return address for exceptions and *scall*. Executing the *rete* or *rets* instruction at the completion of an exception or system call will pop this status register and continue execution at the popped return address.

# 4.3.2.2 Java Support

AVR32UC does not provide Java hardware acceleration.

# 4.3.2.3 Floating Point Support

A fused multiply-accumulate Floating Point Unit (FPU), performing a multiply and accumulate as a single operation with no intermediate rounding, therby increasing precision is provided. The floating point hardware conforms to the requirements of the C standard, which is based on the IEEE 754 floating point standard.

# 4.3.2.4 Memory Protection

The MPU allows the user to check all memory accesses for privilege violations. If an access is attempted to an illegal memory address, the access is aborted and an exception is taken. The MPU in AVR32UC is specified in the AVR32UC Technical Reference manual.

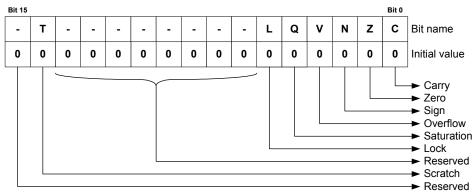

Figure 4-5. The Status Register Low Halfword

# 4.4.3 Processor States

#### 4.4.3.1 Normal RISC State

The AVR32 processor supports several different execution contexts as shown in Table 4-2.

| Priority | ty Mode Security Description |              | Description                               |

|----------|------------------------------|--------------|-------------------------------------------|

| 1        | Non Maskable Interrupt       | Privileged   | Non Maskable high priority interrupt mode |

| 2        | Exception Privileg           |              | Execute exceptions                        |

| 3        | Interrupt 3                  | Privileged   | General purpose interrupt mode            |

| 4        | Interrupt 2                  | Privileged   | General purpose interrupt mode            |

| 5        | Interrupt 1                  | Privileged   | General purpose interrupt mode            |

| 6        | Interrupt 0                  | Privileged   | General purpose interrupt mode            |

| N/A      | Supervisor                   | Privileged   | Runs supervisor calls                     |

| N/A      | Application                  | Unprivileged | Normal program execution mode             |

Table 4-2.

Overview of Execution Modes, their Priorities and Privilege Levels.

Mode changes can be made under software control, or can be caused by external interrupts or exception processing. A mode can be interrupted by a higher priority mode, but never by one with lower priority. Nested exceptions can be supported with a minimal software overhead.

When running an operating system on the AVR32, user processes will typically execute in the application mode. The programs executed in this mode are restricted from executing certain instructions. Furthermore, most system registers together with the upper halfword of the status register cannot be accessed. Protected memory areas are also not available. All other operating modes are privileged and are collectively called System Modes. They have full access to all privileged and unprivileged resources. After a reset, the processor will be in supervisor mode.

# 4.4.3.2 Debug State

The AVR32 can be set in a debug state, which allows implementation of software monitor routines that can read out and alter system information for use during application development. This implies that all system and application registers, including the status registers and program counters, are accessible in debug state. The privileged instructions are also available.

All interrupt levels are by default disabled when debug state is entered, but they can individually be switched on by the monitor routine by clearing the respective mask bit in the status register.

# 5.2 Physical Memory Map

The system bus is implemented as a bus matrix. All system bus addresses are fixed, and they are never remapped in any way, not even in boot. Note that AVR32UC CPU uses unsegmented translation, as described in the AVR32 Architecture Manual. The 32-bit physical address space is mapped as follows:

|                            |               |        | AT3              | 32UC3 Derivatives |        |

|----------------------------|---------------|--------|------------------|-------------------|--------|

| Device                     | Start Address | C0512C | C1512C<br>C2512C | C1256C<br>C2256C  | C2128C |

| Embedded SRAM              | 0x0000_0000   | 64 KB  | 64 KB            | 64 KB             | 32 KB  |

| Embedded Flash             | 0x8000_0000   | 512 KB | 512 KB           | 256 KB            | 128 KB |

| SAU                        | 0x9000_0000   | 1 KB   | 1 KB             | 1 KB              | 1 KB   |

| HSB SRAM                   | 0xA000_0000   | 4 KB   | 4 KB             | 4 KB              | 4 KB   |

| EBI SRAM CS0               | 0xC000_0000   | 16 MB  | -                | -                 | -      |

| EBI SRAM CS2               | 0xC800_0000   | 16 MB  | -                | -                 | -      |

| EBI SRAM CS3               | 0xCC00_0000   | 16 MB  | -                | -                 | -      |

| EBI SRAM CS1<br>/SDRAM CS0 | 0xD000_0000   | 128 MB | -                | -                 | -      |

| HSB-PB Bridge C            | 0xFFFD_0000   | 64 KB  | 64 KB            | 64 KB             | 64 KB  |

| HSB-PB Bridge B            | 0xFFFE_0000   | 64 KB  | 64 KB            | 64 KB             | 64 KB  |

| HSB-PB Bridge A            | 0xFFFF_0000   | 64 KB  | 64 KB            | 64 KB             | 64 KB  |

| Table 5-1. | AT32UC3C Physical Memory | Мар |

|------------|--------------------------|-----|

|------------|--------------------------|-----|

Table 5-2.Flash Memory Parameters

| Part Number                                     | Flash Size<br>(FLASH_PW) | Number of<br>pages<br>(FLASH_P) | Page size<br>(FLASH_W) |

|-------------------------------------------------|--------------------------|---------------------------------|------------------------|

| AT32UC3C0512C<br>AT32UC3C1512C<br>AT32UC3C2512C | 512 Kbytes               | 1024                            | 128 words              |

| AT32UC3C1256C<br>AT32UC3C2256C                  | 256 Kbytes               | 512                             | 128 words              |

| AT32UC3C2128C                                   | 128 Kbytes               | 256                             | 128 words              |

**Peripheral Name**

# 5.3 Peripheral Address Map

Table 5-3.Peripheral Address Mapping

Address

0xFFFD0000

PDCA

Peripheral DMA Controller - PDCA

# Table 5-3.Peripheral Address Mapping

| iprieral Audres | is mapping |                                                                      |

|-----------------|------------|----------------------------------------------------------------------|

| 0xFFFD1000      | MDMA       | Memory DMA - MDMA                                                    |

| 0xFFFD1400      | USART1     | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART1  |

| 0xFFFD1800      | SPI0       | Serial Peripheral Interface - SPI0                                   |

| 0xFFFD1C00      | CANIF      | Control Area Network interface - CANIF                               |

| 0xFFFD2000      | TC0        | Timer/Counter - TC0                                                  |

| 0xFFFD2400      | ADCIFA     | ADC controller interface with Touch Screen functionality<br>- ADCIFA |

| 0xFFFD2800      | USART4     | Universal Synchronous/Asynchronous<br>Receiver/Transmitter - USART4  |

| 0xFFFD2C00      | TWIM2      | Two-wire Master Interface - TWIM2                                    |

| 0xFFFD3000      | TWIS2      | Two-wire Slave Interface - TWIS2                                     |

| 0xFFFE0000      | HFLASHC    | Flash Controller - HFLASHC                                           |

| 0xFFFE1000      | USBC       | USB 2.0 OTG Interface - USBC                                         |

| 0xFFFE2000      | HMATRIX    | HSB Matrix - HMATRIX                                                 |

| 0xFFFE2400      | SAU        | Secure Access Unit - SAU                                             |

| 0xFFFE2800      | SMC        | Static Memory Controller - SMC                                       |

| 0xFFFE2C00      | SDRAMC     | SDRAM Controller - SDRAMC                                            |

| 0xFFFE3000      | MACB       | Ethernet MAC - MACB                                                  |

| 0xFFFF0000      | INTC       | Interrupt controller - INTC                                          |

| 0xFFFF0400      | PM         | Power Manager - PM                                                   |

| 0xFFFF0800      | SCIF       | System Control Interface - SCIF                                      |

# 6.2 Startup Considerations

This chapter summarizes the boot sequence of the AT32UC3C. The behavior after power-up is controlled by the Power Manager. For specific details, refer to the Power Manager chapter.

# 6.2.1 Starting of clocks

At power-up, the BOD33 and the BOD18 are enabled. The device will be held in a reset state by the power-up circuitry, until the VDDIN\_33 (resp. VDDCORE) has reached the reset threshold of the BOD33 (resp BOD18). Refer to the Electrical Characteristics for the BOD thresholds. Once the power has stabilized, the device will use the System RC Oscillator (RCSYS, 115KHz typical frequency) as clock source. The BOD18 and BOD33 are kept enabled or are disabled according to the fuse settings (See the Fuse Setting section in the Flash Controller chapter).

On system start-up, the PLLs are disabled. All clocks to all modules are running. No clocks have a divided frequency, all parts of the system receive a clock with the same frequency as the internal RC Oscillator.

# 6.2.2 Fetching of initial instructions

After reset has been released, the AVR32UC CPU starts fetching instructions from the reset address, which is 0x8000\_0000. This address points to the first address in the internal Flash.

The internal Flash uses VDDIO voltage during read and write operations. It is recommended to use the BOD33 to monitor this voltage and make sure the VDDIO is above the minimum level (3.0V).

The code read from the internal Flash is free to configure the system to use for example the PLLs, to divide the frequency of the clock routed to some of the peripherals, and to gate the clocks to unused peripherals.

# Table 7-2. Supply Rise Rates and Order

|                                                                   |                                          |           | Rise Rate |                                                     |  |  |  |

|-------------------------------------------------------------------|------------------------------------------|-----------|-----------|-----------------------------------------------------|--|--|--|

| Symbol                                                            | Parameter                                | Min       | Мах       | Comment                                             |  |  |  |

| $V_{VDDIN_5}$                                                     | DC supply internal 3.3V regulator        | 0.01 V/ms | 1.25 V/us |                                                     |  |  |  |

| V <sub>VDDIN_33</sub>                                             | DC supply internal 1.8V regulator        | 0.01 V/ms | 1.25 V/us |                                                     |  |  |  |

| V <sub>VDDIO1</sub><br>V <sub>VDDIO2</sub><br>V <sub>VDDIO3</sub> | DC supply peripheral I/O                 | 0.01 V/ms | 1.25 V/us | Rise after or at the same time as VDDIN_5, VDDIN_33 |  |  |  |

| V <sub>VDDANA</sub>                                               | DC supply peripheral I/O and analog part | 0.01 V/ms | 1.25 V/us | Rise after or at the same time as VDDIN_5, VDDIN_33 |  |  |  |

# 7.3 Maximum Clock Frequencies

These parameters are given in the following conditions:

- V<sub>VDDCORE</sub> > 1.85V

- Temperature = -40°C to 125°C

| Table 7-3. | Clock Frequencies |

|------------|-------------------|

|------------|-------------------|

| Symbol              | Parameter              | Conditions              | Min | Max                | Units |

|---------------------|------------------------|-------------------------|-----|--------------------|-------|

| f <sub>CPU</sub>    | CPU clock frequency    |                         |     | 50                 | MHz   |

| f <sub>PBA</sub>    | PBA clock frequency    |                         |     | 50                 | MHz   |

| f <sub>PBB</sub>    | PBB clock frequency    |                         |     | 50                 | MHz   |

| f <sub>PBC</sub>    | PBC clock frequency    |                         |     | 50                 | MHz   |

| f <sub>GCLK0</sub>  | GCLK0 clock frequency  | Generic clock for USBC  |     | 50 <sup>(1)</sup>  | MHz   |

| f <sub>GCLK1</sub>  | GCLK1 clock frequency  | Generic clock for CANIF |     | 66 <sup>(1)</sup>  | MHz   |

| f <sub>GCLK2</sub>  | GCLK2 clock frequency  | Generic clock for AST   |     | 80 <sup>(1)</sup>  | MHz   |

| f <sub>GCLK4</sub>  | GCLK4 clock frequency  | Generic clock for PWM   |     | 120 <sup>(1)</sup> | MHz   |

| f <sub>GCLK11</sub> | GCLK11 clock frequency | Generic clock for IISC  |     | 50 <sup>(1)</sup>  | MHz   |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

# 7.4 Power Consumption

The values in Table 7-4 are measured values of power consumption under the following conditions, except where noted:

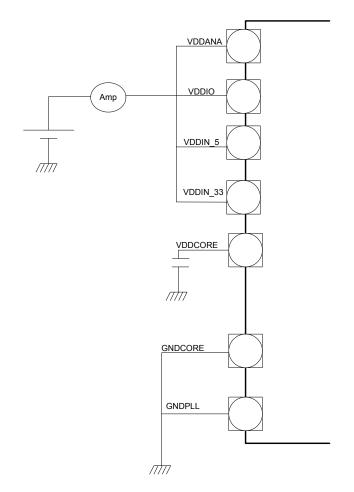

- Operating conditions core supply (Figure 7-1)

- V<sub>VDDIN\_5</sub> = V<sub>VDDIN\_33</sub> = 3.3V

- $V_{VDDCORE} = 1.85V$ , supplied by the internal regulator

- V<sub>VDDIO1</sub> = V<sub>VDDIO2</sub> = V<sub>VDDIO3</sub> = 3.3V

- $V_{VDDANA} = 3.3V$

# Figure 7-1. Measurement Schematic

# 7.4.1 Peripheral Power Consumption

The values in Table 7-5 are measured values of power consumption under the following conditions.

• Operating conditions core supply (Figure 7-1)

$-V_{VDDIN_5} = V_{DDIN_{33}} = 3.3V$

- $V_{VDDCORE} = 1.85V$ , supplied by the internal regulator

- V<sub>VDDIO1</sub> = V<sub>VDDIO2</sub> = V<sub>VDDIO3</sub> = 3.3V

- $V_{VDDANA} = 3.3V$

- Internal 3.3V regulator is off.

- TA = 25°C

- I/Os are configured as inputs, with internal pull-up enabled.

- Oscillators

- OSC0/1 (crystal oscillator) stopped

- OSC32K (32KHz crystal oscillator) stopped

- PLL0 running

# 7.8.8 Analog Comparator Characteristics

| Symbol               | Parameter                    | Conditions                       | Min | Тур | Max                 | Units |

|----------------------|------------------------------|----------------------------------|-----|-----|---------------------|-------|

|                      | Positive input voltage range |                                  | 0   |     | V <sub>VDDANA</sub> | V     |

|                      | Negative input voltage range |                                  | 0   |     | V <sub>VDDANA</sub> | V     |

| M                    | V <sub>OFFSET</sub> Offset   | No hysteresis, Low Power mode    | -36 |     | 36                  | mV    |

| VOFFSET              |                              | No hysteresis, High Speed mode   | -21 |     | 21                  | mV    |

|                      |                              | Low hysteresis, Low Power mode   | 7   |     | 49                  | mV    |

| M                    |                              | Low hysteresis, High Speed mode  | 5   |     | 39                  |       |

| V <sub>HYST</sub>    | Hysteresis                   | High hysteresis, Low Power mode  | 16  |     | 113                 | mV    |

|                      |                              | High hysteresis, High Speed mode | 12  |     | 76                  | IIIV  |

|                      | Propagation delay            | Low Power mode                   |     |     | 3.3                 |       |

| t <sub>DELAY</sub>   |                              | High Speed mode                  |     |     | 0.102               | us    |

| t <sub>STARTUP</sub> | Start-up time                |                                  |     |     | 20                  | μs    |

Table 7-41.

Analog Comparator Characteristics<sup>(1)</sup>

Note: 1. The measures are done without any I/O activity on VDDANA/GNDANA power domain.

# Table 7-42. VDDANA scaled reference

| Symbol                     | Parameter                            | Min | Тур                                   | Max | Units |

|----------------------------|--------------------------------------|-----|---------------------------------------|-----|-------|

| SCF                        | ACIFA.SCFi.SCF range                 | 0   |                                       | 32  |       |

| V <sub>VDDANA</sub> scaled |                                      |     | (64 - SCF) * V <sub>VDDANA</sub> / 65 |     | V     |

|                            | V <sub>VDDANA</sub> voltage accuracy |     |                                       | 4.1 | %     |

# 7.8.9 USB Transceiver Characteristics

7.8.9.1 Electrical Characteristics

# Table 7-43. Electrical Parameters

| Symbol           | Parameter                                | Conditions                           | Min. | Тур. | Max. | Unit |

|------------------|------------------------------------------|--------------------------------------|------|------|------|------|

| R <sub>EXT</sub> | Recommended external USB series resistor | In series with each USB pin with ±5% |      | 39   |      | Ω    |

The USB on-chip buffers comply with the Universal Serial Bus (USB) v2.0 standard. All AC parameters related to these buffers can be found within the USB 2.0 electrical specifications.

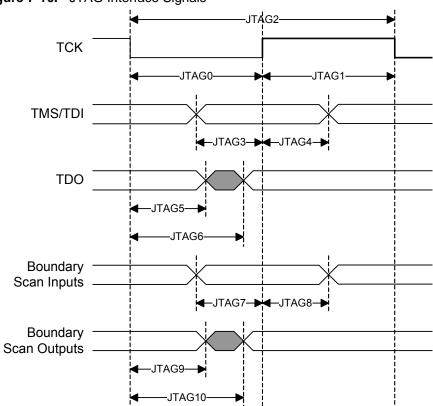

# 7.9.6 JTAG Timing

Figure 7-16. JTAG Interface Signals

| Table 7-51. | JTAG | Timings <sup>(1)</sup> |

|-------------|------|------------------------|

|-------------|------|------------------------|

| Symbol | Parameter                          | Conditions  | Min  | Max | Units |

|--------|------------------------------------|-------------|------|-----|-------|

| JTAG0  | TCK Low Half-period                |             | 23   |     | ns    |

| JTAG1  | TCK High Half-period               |             | 9    |     | ns    |

| JTAG2  | TCK Period                         |             | 31   |     | ns    |

| JTAG3  | TDI, TMS Setup before TCK High     |             | 7    |     | ns    |

| JTAG4  | TDI, TMS Hold after TCK High       | external    | 0    |     | ns    |

| JTAG5  | TDO Hold Time                      | capacitor = | 13.5 |     | ns    |

| JTAG6  | TCK Low to TDO Valid               | 40pF        |      | 23  | ns    |

| JTAG7  | Boundary Scan Inputs Setup Time    |             | 0    |     | ns    |

| JTAG8  | Boundary Scan Inputs Hold Time     |             | 4.5  |     | ns    |

| JTAG9  | Boundary Scan Outputs Hold Time    |             | 12   |     | ns    |

| JTAG10 | TCK to Boundary Scan Outputs Valid |             |      | 19  | ns    |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

| Symbol            | Parameter                        | Conditions                                                                   | Min                                   | Units |

|-------------------|----------------------------------|------------------------------------------------------------------------------|---------------------------------------|-------|

| SMC <sub>37</sub> | NWE rising to A2-A25 valid       |                                                                              | 9.1                                   |       |

| SMC <sub>38</sub> | NWE rising to NBS0/A0 valid      | _                                                                            | 7.9                                   |       |

| SMC <sub>40</sub> | NWE rising to A1/NBS2 change     | V <sub>VDD</sub> = 3.0V,<br>drive strength of the pads<br>set to the lowest, | 9.1                                   |       |

| SMC <sub>42</sub> | NWE rising to NCS rising         |                                                                              | 8.7                                   | ns    |

| SMC <sub>43</sub> | Data Out valid before NWE rising | external capacitor = 40pF                                                    | (nwe pulse length - 1) * tcpsмc - 1.5 |       |

| SMC <sub>44</sub> | Data Out valid after NWE rising  |                                                                              | 8.7                                   |       |

| SMC <sub>45</sub> | NWE pulse width                  |                                                                              | nwe pulse length * tcpsмc - 0.1       | 1     |

Table 7-56.

SMC Write Signals with No Hold Settings (NWE Controlled only)<sup>(1)</sup>

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

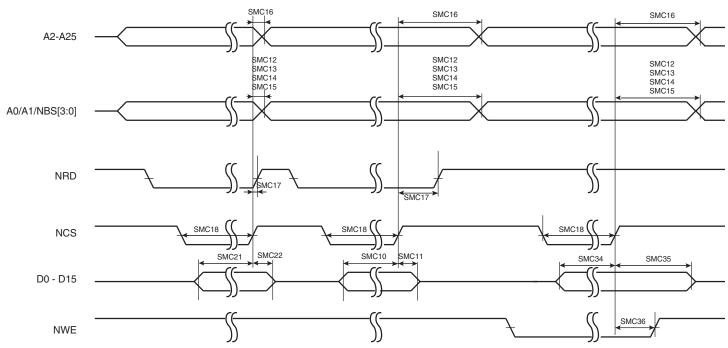

Figure 7-17. SMC Signals for NCS Controlled Accesses

# 7.9.9 MACB Characteristics

Table 7-59.

Ethernet MAC Signals<sup>(1)</sup>

| Symbol           | Parameter                      | Conditions                                     | Min. | Max. | Unit |

|------------------|--------------------------------|------------------------------------------------|------|------|------|

| MAC <sub>1</sub> | Setup for MDIO from MDC rising | $V_{VDD} = 3.0V,$                              | 0    | 2.6  | ns   |

| MAC <sub>2</sub> | Hold for MDIO from MDC rising  | drive strength of the pads set to the highest. | 0    | 0.7  | ns   |

| MAC <sub>3</sub> | MDIO toggling from MDC falling | external capacitor = 10pF on MACB<br>pins      | 0    | 1.1  | ns   |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

Table 7-60.

Ethernet MAC MII Specific Signals<sup>(1)</sup>

| Symbol            | Parameter                         | Conditions                                                        | Min. | Max. | Unit |

|-------------------|-----------------------------------|-------------------------------------------------------------------|------|------|------|

| MAC <sub>4</sub>  | Setup for COL from TX_CLK rising  |                                                                   | 0    |      | ns   |

| MAC <sub>5</sub>  | Hold for COL from TX_CLK rising   |                                                                   | 0    |      | ns   |

| MAC <sub>6</sub>  | Setup for CRS from TX_CLK rising  | _                                                                 | 0.5  |      | ns   |

| MAC <sub>7</sub>  | Hold for CRS from TX_CLK rising   | _                                                                 | 0.6  |      | ns   |

| MAC <sub>8</sub>  | TX_ER toggling from TX_CLK rising | -                                                                 | 17.3 | 19.6 | ns   |

| MAC <sub>9</sub>  | TX_EN toggling from TX_CLK rising | V <sub>VDD</sub> = 3.0V,<br>drive strength of the pads set to the | 15.5 | 16.2 | ns   |

| MAC <sub>10</sub> | TXD toggling from TX_CLK rising   | highest,                                                          | 14.9 | 19.2 | ns   |

| MAC <sub>11</sub> | Setup for RXD from RX_CLK         | external capacitor = 10pF on MACB                                 | 1.3  |      | ns   |

| MAC <sub>12</sub> | Hold for RXD from RX_CLK          | – pins                                                            | 2    |      | ns   |

| MAC <sub>13</sub> | Setup for RX_ER from RX_CLK       | -                                                                 | 3.6  |      | ns   |

| MAC <sub>14</sub> | Hold for RX_ER from RX_CLK        | -                                                                 | 0    |      | ns   |

| MAC <sub>15</sub> | Setup for RX_DV from RX_CLK       |                                                                   | 0.7  |      | ns   |

| MAC <sub>16</sub> | Hold for RX_DV from RX_CLK        |                                                                   | 1.4  |      | ns   |

Note: 1. These values are based on simulation and characterization of other AVR microcontrollers manufactured in the same process technology. These values are not covered by test limits in production.

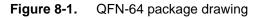

# 8.2 Package Drawings

Note: The exposed pad is not connected to anything internally, but should be soldered to ground to increase board level reliability.

| 200          |                         | mg                      |  |

|--------------|-------------------------|-------------------------|--|

| Table 8-3.   | Package Characteristics |                         |  |

| Moisture Ser | nsitivity Level         | Jdec J-STD0-20D - MSL 3 |  |

| Table 8-4.   | Package Reference       |                         |  |

| JEDEC Drav   | wing Reference          | MS-026                  |  |

| JESD97 Cla   | ssification             | E3                      |  |

# 8.3 Soldering Profile

Table 8-14 gives the recommended soldering profile from J-STD-20.

| Profile Feature                            | Green Package            |

|--------------------------------------------|--------------------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/sec                  |

| Preheat Temperature 175°C ±25°C            | Min. 150 °C, Max. 200 °C |

| Temperature Maintained Above 217°C         | 60-150 sec               |

| Time within 5.C of Actual Peak Temperature | 30 sec                   |

| Peak Temperature Range                     | 260 °C                   |

| Ramp-down Rate                             | 6 °C/sec                 |

| Time 25 C to Peak Temperature              | Max. 8 minutes           |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

# 9. Ordering Information

| Table 9-1.         Ordering Information |                    |              |            |                             |

|-----------------------------------------|--------------------|--------------|------------|-----------------------------|

| Device                                  | Ordering Code      | Carrier Type | Package    | Temperature Operating Range |

| AT32UC3C0512C                           | AT32UC3C0512C-ALZT | Tray         | LQFP 144   | Automotive (-40°C to 125°C) |

|                                         | AT32UC3C0512C-ALZR | Tape & Reel  |            |                             |

| AT32UC3C1512C                           | AT32UC3C1512C-AZT  | Tray         | TQFP 100   |                             |

|                                         | AT32UC3C1512C-AZR  | Tape & Reel  |            |                             |

| AT32UC3C1256C                           | AT32UC3C1256C-AZT  | Tray         | - TQFP 100 |                             |

|                                         | AT32UC3C1256C-AZR  | Tape & Reel  |            |                             |

| AT32UC3C2512C                           | AT32UC3C2512C-A2ZT | Tray         | TQFP 64    |                             |

|                                         | AT32UC3C2512C-A2ZR | Tape & Reel  |            |                             |

| AT32UC3C2512C                           | AT32UC3C2512C-Z2ZT | Tray         | QFN 64     |                             |

|                                         | AT32UC3C2512C-Z2ZR | Tape & Reel  |            |                             |

| AT32UC3C2256C                           | AT32UC3C2256C-A2ZT | Tray         | TQFP 64    |                             |

|                                         | AT32UC3C2256C-A2ZR | Tape & Reel  |            |                             |

| AT32UC3C2256C                           | AT32UC3C2256C-Z2ZT | Tray         | QFN 64     |                             |

|                                         | AT32UC3C2256C-Z2ZR | Tape & Reel  |            |                             |

| AT32UC3C2128C                           | AT32UC3C2128C-A2ZT | Tray         | TQFP 64    |                             |

|                                         | AT32UC3C2128C-A2ZR | Tape & Reel  |            |                             |

| AT32UC3C2128C                           | AT32UC3C2128C-Z2ZT | Tray         | QFN 64     |                             |

|                                         | AT32UC3C2128C-Z2ZR | Tape & Reel  |            |                             |

## 2 Disabling SPI has no effect on the SR.TDRE bit

Disabling SPI has no effect on the SR.TDRE bit whereas the write data command is filtered when SPI is disabled. Writing to TDR when SPI is disabled will not clear SR.TDRE. If SPI is disabled during a PDCA transfer, the PDCA will continue to write data to TDR until its buffer is empty, and this data will be lost.

#### Fix/Workaround

Disable the PDCA, add two NOPs, and disable the SPI. To continue the transfer, enable the SPI and PDCA.

# 3 SPI disable does not work in SLAVE mode

SPI disable does not work in SLAVE mode.

# **Fix/Workaround**

Read the last received data, then perform a software reset by writing a one to the Software Reset bit in the Control Register (CR.SWRST).

# 4 SPI bad serial clock generation on 2nd chip select when SCBR=1, CPOL=1, and NCPHA=0

When multiple chip selects (CS) are in use, if one of the baudrates equal 1 while one (CSRn.SCBR=1) of the others do not equal 1, and CSRn.CPOL=1 and CSRn.NCPHA=0, then an additional pulse will be generated on SCK.

#### Fix/Workaround

When multiple CS are in use, if one of the baudrates equals 1, the others must also equal 1 if CSRn.CPOL=1 and CSRn.NCPHA=0.

#### 10.2.8 TC

# 1 Channel chaining skips first pulse for upper channel

When chaining two channels using the Block Mode Register, the first pulse of the clock between the channels is skipped.

# Fix/Workaround

Configure the lower channel with RA = 0x1 and RC = 0x2 to produce a dummy clock cycle for the upper channel. After the dummy cycle has been generated, indicated by the SR.CPCS bit, reconfigure the RA and RC registers for the lower channel with the real values.

#### 10.2.9 TWIM

#### 1 SMBALERT bit may be set after reset

For TWIM0 and TWIM1 modules, the SMBus Alert (SMBALERT) bit in the Status Register (SR) might be erroneously set after system reset. Fix/Workaround

After system reset, clear the SR.SMBALERT bit before commencing any TWI transfer.

For TWIM2 module, the SMBus Alert (SMBALERT) is not implemented but the bit in the Status Register (SR) is erroneously set once TWIM2 is enabled. Fix/Workaround None.

# 2 TWIM TWALM polarity is wrong

The TWALM signal in the TWIM is active high instead of active low. Fix/Workaround

Use an external inverter to invert the signal going into the TWIM. When using both TWIM and TWIS on the same pins, the TWALM cannot be used.

# 10.2.10 TWIS

10.2.11 USBC

# 1 Clearing the NAK bit before the BTF bit is set locks up the TWI bus

When the TWIS is in transmit mode, clearing the NAK Received (NAK) bit of the Status Register (SR) before the end of the Acknowledge/Not Acknowledge cycle will cause the TWIS to attempt to continue transmitting data, thus locking up the bus. **Fix/Workaround**

Clear SR.NAK only after the Byte Transfer Finished (BTF) bit of the same register has been set.

## 2 TWIS stretch on Address match error

When the TWIS stretches TWCK due to a slave address match, it also holds TWD low for the same duration if it is to be receiving data. When TWIS releases TWCK, it releases TWD at the same time. This can cause a TWI timing violation. **Fix/Workaround**

None.

# 3 TWALM forced to GND

The TWALM pin is forced to GND when the alternate function is selected and the TWIS module is enabled.

# Fix/Workaround

None.

# 1 UPINRQx.INRQ field is limited to 8-bits

In Host mode, when using the UPINRQx.INRQ feature together with the multi-packet mode to launch a finite number of packet among multi-packet, the multi-packet size (located in the descriptor table) is limited to the UPINRQx.INRQ value multiply by the pipe size. **Fix/Workaround**

UPINRQx.INRQ value shall be less than the number of configured multi-packet.

2 In USB host mode, downstream resume feature does not work (UHCON.RESUME=1). Fix/Workaround

None.

3 In host mode, the disconnection during OUT transition is not supported In USB host mode, a pipe can not work if the previous USB device disconnection has occurred during a USB transfer. Fix/Workaround

Reset the USBC (USBCON.USB=0 and =1) after a device disconnection (UHINT.DDISCI).

# 4 In USB host mode, entering suspend mode can fail

In USB host mode, entering suspend mode can fail when UHCON.SOFE=0 is done just after a SOF reception (UHINT.HSOFI).

# Fix/Workaround

Check that UHNUM.FLENHIGH is below 185 in Full speed and below 21 in Low speed before clearing UHCON.SOFE.

5 In USB host mode, entering suspend mode for low speed device can fail when the USB freeze (USBCON.FRZCLK=1) is done just after UHCON.SOFE=0. Fix/Workaround

When entering suspend mode (UHCON.SOFE is cleared), check that USBFSM.DRDSTATE is not equal to three before freezing the clock (USBCON.FRZCLK=1).