# E·XFL

### NXP USA Inc. - SPC5603BF2CLL4 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 79                                                                     |

| Program Memory Size        | 384KB (384K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 28K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 28x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5603bf2cll4 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1, 1 | ntrodu | action                                                     |

|------|--------|------------------------------------------------------------|

| Ċ.   | 1.1    | Document overview                                          |

|      | 1.2    | Description                                                |

|      | 1.3    | Block diagram                                              |

| 2    | Pack   | age pinouts and signal descriptions                        |

|      | 2.1    | Package pinouts                                            |

|      | 2.2    | Pad configuration during reset phases                      |

|      | 2.3    | Voltage supply pins                                        |

|      | 2.4    | Pad types                                                  |

|      | 2.5    | System pins14                                              |

|      | 2.6    | Functional ports14                                         |

|      | 2.7    | Nexus 2+ pins                                              |

|      | 2.8    | Electrical characteristics                                 |

|      | 2.9    | Introduction                                               |

|      | 2.10   | Parameter classification                                   |

|      | 2.11   | NVUSRO register                                            |

|      |        | 2.11.1 NVUSRO[PAD3V5V] field description                   |

|      |        | 2.11.2 NVUSRO[OSCILLATOR_MARGIN] field description         |

|      |        | 32                                                         |

|      |        | 2.11.3 NVUSRO[WATCHDOG_EN] field description32             |

|      | 2.12   | Absolute maximum ratings                                   |

|      | 2.13   |                                                            |

|      | 2.14   | Thermal characteristics                                    |

|      |        | 2.14.1 Package thermal characteristics                     |

|      |        | 2.14.2 Power considerations                                |

|      | 2.15   | I/O pad electrical characteristics                         |

|      |        | 2.15.1 I/O pad types                                       |

|      |        | 2.15.2 I/O input DC characteristics                        |

|      |        | 2.15.3 I/O output DC characteristics                       |

|      |        | 2.15.4 Output pin transition times                         |

|      |        | 2.15.5 I/O pad current specification                       |

|      | 2.16   | RESET electrical characteristics                           |

|      | 2.17   | Power management electrical characteristics51              |

|      |        | 2.17.1 Voltage regulator electrical characteristics51      |

|      | 0.40   | 2.17.2 Low voltage detector electrical characteristics .56 |

|      | 2.18   |                                                            |

|      | 2.19   | Flash memory electrical characteristics                    |

|        | 2.20 | <ul> <li>2.19.1 Program/Erase characteristics</li></ul>              |

|--------|------|----------------------------------------------------------------------|

|        | 2.21 |                                                                      |

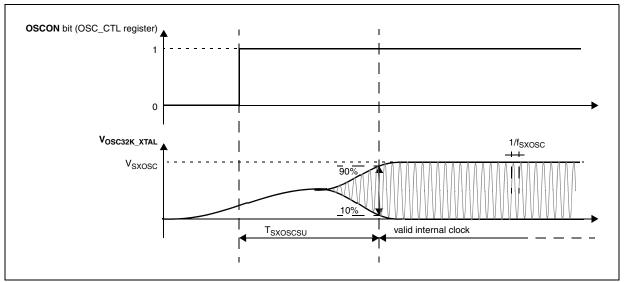

|        | 2.22 | Slow external crystal oscillator (32 kHz) electrical characteristics |

|        | 2.23 | FMPLL electrical characteristics                                     |

|        | 2.24 | Fast internal RC oscillator (16 MHz) electrical                      |

|        |      | characteristics                                                      |

|        | 2.25 | Slow internal RC oscillator (128 kHz) electrical                     |

|        |      | characteristics                                                      |

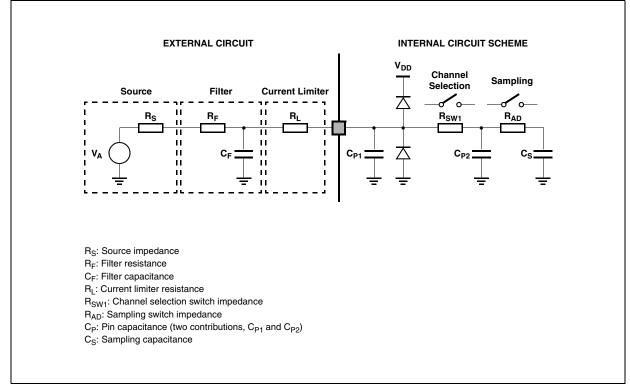

|        | 2.26 | ADC electrical characteristics                                       |

|        |      | 2.26.1 Introduction                                                  |

|        |      | 2.26.2 Input impedance and ADC accuracy                              |

|        |      | 2.26.3 ADC electrical characteristics                                |

|        | 2.27 | On-chip peripherals                                                  |

|        |      | 2.27.1 Current consumption                                           |

|        |      | 2.27.2 DSPI characteristics 80                                       |

|        |      | 2.27.3 Nexus characteristics                                         |

|        |      | 2.27.4 JTAG characteristics                                          |

| 3      |      | age characteristics                                                  |

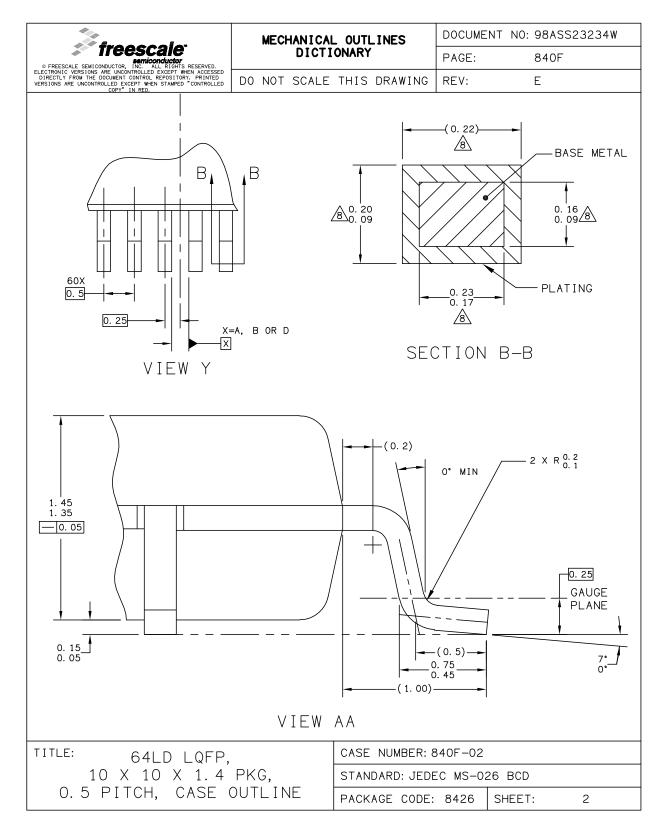

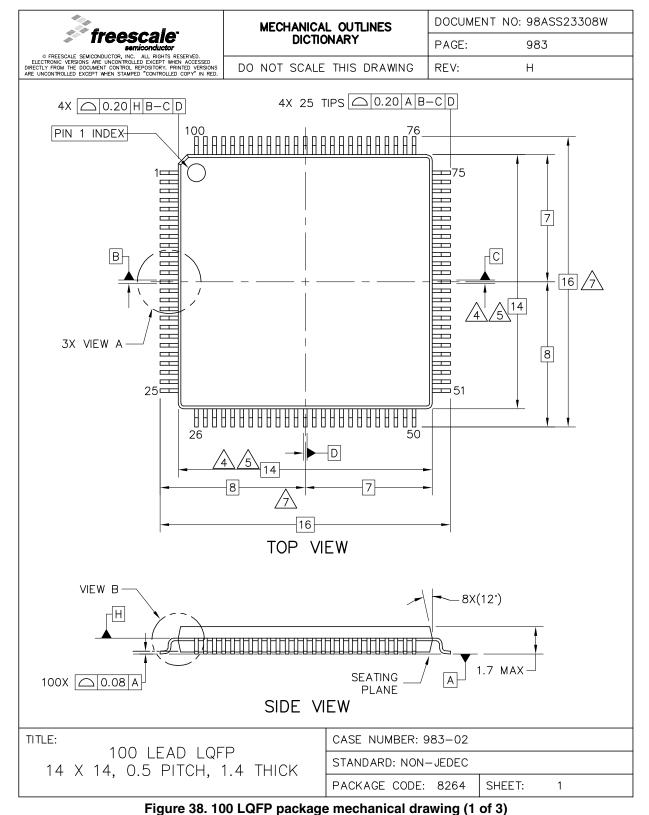

|        | 3.1  | Package mechanical data                                              |

|        |      | 3.1.1 64 LQFP                                                        |

|        |      | 3.1.2 100 LQFP                                                       |

|        |      | 3.1.3 144 LQFP                                                       |

| 4      | Orde | 3.1.4 208 MAPBGA                                                     |

| 4<br>5 |      | ring information                                                     |

| 5      | Docu | ment revision mistory                                                |

#### Introduction

Table 2 summarizes the functions of all blocks present in the MPC5604B/C series of microcontrollers. Please note that the presence and number of blocks vary by device and package.

| Block                                            | Function                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                         | A block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                        |

| Clock monitor unit (CMU)                         | Monitors clock source (internal and external) integrity                                                                                                                                                                                                                                                           |

| Cross triggering unit (CTU)                      | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Deserial serial peripheral interface (DSPI)      | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Error Correction Status Module<br>(ECSM)         | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| Enhanced Direct Memory Access<br>(eDMA)          | Performs complex data transfers with minimal intervention from a host processor via " <i>n</i> " programmable channels.                                                                                                                                                                                           |

| Enhanced modular input output system (eMIOS)     | Provides the functionality to generate or measure events                                                                                                                                                                                                                                                          |

| Flash memory                                     | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| FlexCAN (controller area network)                | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Frequency-modulated<br>phase-locked loop (FMPLL) | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Internal multiplexer (IMUX) SIU subblock         | Allows flexible mapping of peripheral interface on the different pins of the device                                                                                                                                                                                                                               |

| Inter-integrated circuit (I <sup>2</sup> C™) bus | A two wire bidirectional serial bus that provides a simple and efficient method of data exchange between devices                                                                                                                                                                                                  |

| Interrupt controller (INTC)                      | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                  | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                               | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with a minimum of CPU load                                                                                                                                                                                                |

| Clock generation module<br>(MC_CGM)              | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Mode entry module (MC_ME)                        | Provides a mechanism for controlling the device operational mode and mode<br>transition sequences in all functional states; also manages the power control unit,<br>reset generation module and clock generation module, and holds the<br>configuration, control and status registers accessible for applications |

| Power control unit (MC_PCU)                      | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

| Reset generation module<br>(MC_RGM)              | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                                                                                                     |

### Table 2. MPC5604B/C series block summary

|          |         | -                                  |                                                                                                        |                                                             |                            |          | u                   |                  | Pin              | num      | ber      |                         |

|----------|---------|------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>    | Function                                                                                               | Peripheral                                                  | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PE[8]    | PCR[72] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[72]<br>CAN2TX <sup>12</sup><br>E0UC[22]<br>CAN3TX <sup>11</sup>                                   | SIUL<br>FlexCAN_2<br>eMIOS_0<br>FlexCAN_3                   | I/O<br>O<br>I/O<br>O       | Μ        | Tristate            | _                |                  | 9        | 13       | G2                      |

| PE[9]    | PCR[73] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[73]<br>—<br>E0UC[23]<br>—<br>WKPU[7] <sup>4</sup><br>CAN2RX <sup>12</sup><br>CAN3RX <sup>11</sup> | SIUL<br>—<br>eMIOS_0<br>—<br>WKPU<br>FlexCAN_2<br>FlexCAN_3 | V   V   − − −              | S        | Tristate            |                  |                  | 10       | 14       | G1                      |

| PE[10]   | PCR[74] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[74]<br>LIN3TX<br>CS3_1<br><br>EIRQ[10]                                                            | SIUL<br>LINFlex_3<br>DSPI_1<br><br>SIUL                     | V00   -                    | S        | Tristate            |                  |                  | 11       | 15       | G3                      |

| PE[11]   | PCR[75] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[75]<br>—<br>CS4_1<br>—<br>LIN3RX<br>WKPU[14] <sup>4</sup>                                         | SIUL<br>—<br>DSPI_1<br>—<br>LINFlex_3<br>WKPU               | I/O<br>  O<br>  I<br>  I   | S        | Tristate            |                  |                  | 13       | 17       | H2                      |

| PE[12]   | PCR[76] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[76]<br>—<br>E1UC[19] <sup>13</sup><br>—<br>SIN_2<br>EIRQ[11]                                      | SIUL<br>—<br>eMIOS_1<br>—<br>DSPI_2<br>SIUL                 | V/ − V/ − −                | S        | Tristate            |                  |                  | 76       | 109      | C14                     |

| PE[13]   | PCR[77] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[77]<br>SOUT2<br>E1UC[20]<br>—                                                                     | SIUL<br>DSPI_2<br>eMIOS_1<br>—                              | I/O<br>O<br>I/O            | S        | Tristate            | _                |                  |          | 103      | D15                     |

| PE[14]   | PCR[78] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[78]<br>SCK_2<br>E1UC[21]<br>—<br>EIRQ[12]                                                         | SIUL<br>DSPI_2<br>eMIOS_1<br><br>SIUL                       | I/O<br>I/O<br>I/O<br>I     | S        | Tristate            |                  | —                |          | 112      | C13                     |

| PE[15]   | PCR[79] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[79]<br>CS0_2<br>E1UC[22]<br>—                                                                     | SIUL<br>DSPI_2<br>eMIOS_1<br>—                              | I/O<br>I/O<br>I/O          | М        | Tristate            | —                | —                | _        | 113      | A13                     |

|                     |          | <b>-</b> _                      |                                         |                                  |                            |          | uo                     |                  | Pin              | num      | ber      |                         |

|---------------------|----------|---------------------------------|-----------------------------------------|----------------------------------|----------------------------|----------|------------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin            | PCR      | Alternate function <sup>1</sup> | Function                                | Peripheral                       | I/O direction <sup>2</sup> | Pad type | RESET configuration    | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PH[2]               | PCR[114] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[114]<br>E1UC[4]<br>SCK_1<br>—      | SIUL<br>eMIOS_1<br>DSPI_1<br>—   | I/O<br>I/O<br>I/O<br>—     | М        | Tristate               | _                |                  |          | 95       | F16                     |

| PH[3]               | PCR[115] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[115]<br>E1UC[5]<br>CS0_1<br>—      | SIUL<br>eMIOS_1<br>DSPI_1<br>—   | I/O<br>I/O<br>I/O<br>—     | М        | Tristate               |                  |                  |          | 96       | F15                     |

| PH[4]               | PCR[116] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[116]<br>E1UC[6]<br>—<br>—          | SIUL<br>eMIOS_1<br>—             | I/O<br>I/O<br>             | М        | Tristate               |                  |                  |          | 134      | A6                      |

| PH[5]               | PCR[117] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[117]<br>E1UC[7]<br>—<br>—          | SIUL<br>eMIOS_1<br>—             | I/O<br>I/O<br>             | S        | Tristate               | _                |                  |          | 135      | B6                      |

| PH[6]               | PCR[118] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[118]<br>E1UC[8]<br>—<br>MA[2]      | SIUL<br>eMIOS_1<br><br>ADC       | I/O<br>I/O<br>—<br>O       | М        | Tristate               |                  |                  | _        | 136      | D5                      |

| PH[7]               | PCR[119] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[119]<br>E1UC[9]<br>CS3_2<br>MA[1]  | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC | I/O<br>I/O<br>O<br>O       | М        | Tristate               | _                |                  |          | 137      | C5                      |

| PH[8]               | PCR[120] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[120]<br>E1UC[10]<br>CS2_2<br>MA[0] | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC | I/O<br>I/O<br>O<br>O       | М        | Tristate               |                  |                  |          | 138      | A5                      |

| PH[9] <sup>9</sup>  | PCR[121] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[121]<br>—<br>TCK<br>—              | SIUL<br>—<br>JTAGC<br>—          | I/O<br>—<br>I<br>—         | S        | Input, weak<br>pull-up | 60               | 60               | 88       | 127      | B8                      |

| PH[10] <sup>9</sup> | PCR[122] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[122]<br><br>TMS<br>                | SIUL<br>—<br>JTAGC<br>—          | I/O<br>—<br>I<br>—         | S        | Input, weak<br>pull-up | 53               | 53               | 81       | 120      | B9                      |

### Table 5. Functional port pin descriptions (continued)

- <sup>1</sup> Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIUL module. PCR.PA = 00 → AF0; PCR.PA = 01 → AF1; PCR.PA = 10 → AF2; PCR.PA = 11 → AF3. This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "—".

- <sup>2</sup> Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

- <sup>3</sup> 208 MAPBGA available only as development package for Nexus2+

- <sup>4</sup> All WKPU pins also support external interrupt capability. See wakeup unit chapter for further details.

- <sup>5</sup> NMI has higher priority than alternate function. When NMI is selected, the PCR.AF field is ignored.

- <sup>6</sup> "Not applicable" because these functions are available only while the device is booting. Refer to BAM chapter of the reference manual for details.

- <sup>7</sup> Value of PCR.IBE bit must be 0

- <sup>8</sup> Be aware that this pad is used on the MPC5607B 100-pin and 144-pin to provide VDD\_HV\_ADC and VSS\_HV\_ADC1. Therefore, you should be careful in ensuring compatibility between MPC5604B/C and MPC5607B.

- <sup>9</sup> Out of reset all the functional pins except PC[0:1] and PH[9:10] are available to the user as GPIO. PC[0:1] are available as JTAG pins (TDI and TDO respectively).

PH[9:10] are available as JTAG pins (TCK and TMS respectively).

If the user configures these JTAG pins in GPIO mode the device is no longer compliant with IEEE 1149.1-2001.

- <sup>10</sup> The TDO pad has been moved into the STANDBY domain in order to allow low-power debug handshaking in STANDBY mode. However, no pull-resistor is active on the TDO pad while in STANDBY mode. At this time the pad is configured as an input. When no debugger is connected the TDO pad is floating causing additional current consumption. To avoid the extra consumption TDO must be connected. An external pull-up resistor in the range of  $47-100 \text{ k}\Omega$  should be added between the TDO pin and VDD\_HV. Only in case the TDO pin is used as application pin and a pull-up cannot be used then a pull-down resistor with the same value should be used between TDO pin and GND instead.

- <sup>11</sup> Available only on MPC560xC versions, MPC5603B 64 LQFP, MPC5604B 64 LQFP and MPC5604B 208 MAPBGA devices

- <sup>12</sup> Not available on MPC5602B devices

- <sup>13</sup> Not available in 100 LQFP package

- <sup>14</sup> Available only on MPC5604B 208 MAPBGA devices

- <sup>15</sup> Not available on MPC5603B 144-pin devices

### 2.7 Nexus 2+ pins

In the 208 MAPBGA package, eight additional debug pins are available (see Table 6).

|           |                    | I/O       |          | Function    | Pin number  |             |                |  |  |

|-----------|--------------------|-----------|----------|-------------|-------------|-------------|----------------|--|--|

| Debug pin | Function           | direction | Pad type | after reset | 100<br>LQFP | 144<br>LQFP | 208 MAP<br>BGA |  |  |

| МСКО      | Message clock out  | 0         | F        | —           |             | _           | T4             |  |  |

| MDO0      | Message data out 0 | 0         | М        | —           |             | _           | H15            |  |  |

| MDO1      | Message data out 1 | 0         | М        | —           |             | _           | H16            |  |  |

| MDO2      | Message data out 2 | 0         | М        | —           |             | _           | H14            |  |  |

| MDO3      | Message data out 3 | 0         | М        | —           | —           |             | H13            |  |  |

Table 6. Nexus 2+ pin descriptions

### 2.13 Recommended operating conditions

Table 12. Recommended operating conditions (3.3 V)

| Symbol                           |    | Parameter                                                                                        | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Va                   | lue                                                                                                                                                                                                                                                                                 | Unit |

|----------------------------------|----|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Symbol                           |    | Falameter                                                                                        | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min                  | Max                                                                                                                                                                                                                                                                                 | Unit |

| V <sub>SS</sub>                  | SR | Digital ground on VSS_HV pins                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                    | 0                                                                                                                                                                                                                                                                                   | V    |

| V <sub>DD</sub> <sup>1</sup>     | SR | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.0                  | 3.6                                                                                                                                                                                                                                                                                 | V    |

| V <sub>SS_LV</sub> <sup>2</sup>  | SR | Voltage on VSS_LV (low voltage digital supply)<br>pins with respect to ground (V <sub>SS</sub> ) | ge on VSS_LV (low voltage digital supply) —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | V <sub>SS</sub> +0.1                                                                                                                                                                                                                                                                | V    |

| V <sub>DD_BV</sub> <sup>3</sup>  | SR |                                                                                                  | $\begin{array}{c c} \mbox{or supply) with} & & 3.0 & 3.6 \\ \hline \mbox{Relative to } V_{DD} & V_{DD} - 0.1 & V_{DD} + 0.1 \\ \hline \mbox{reference) pin} & & V_{SS} - 0.1 & V_{SS} + 0.1 \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      | V                                                                                                                                                                                                                                                                                   |      |

|                                  |    | respect to ground (V <sub>SS</sub> )                                                             | Relative to $V_{\text{DD}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>DD</sub> -0.1 | Max           0           3.6           0.1 $V_{SS}+0.1$ 3.6           0.1 $V_{DD}+0.1$ 0.1 $V_{DD}+0.1$ 0.1 $V_{DD}+0.1$ 0.1 $V_{DD}+0.1$ 5           0.1 $V_{DD}+0.1$ 5           0.25[V/µs]           )           85           110           105           130           125     |      |

| V <sub>SS_ADC</sub>              | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> )              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1                                                                                                                                                                                                                                                                | V    |

| V <sub>DD_ADC</sub> <sup>4</sup> | SR | Voltage on VDD_HV_ADC pin (ADC reference)                                                        | ParameterConditionsIl ground on VSS_HV pins—0ge on VDD_HV pins with respect to ground—3.0ge on VSS_LV (low voltage digital supply)— $V_{SS}$ -0.1vith respect to ground (V_{SS})— $V_{SS}$ -0.1ge on VDD_BV pin (regulator supply) with<br>ct to ground (V_{SS})—3.0ge on VSS_HV_ADC (ADC reference) pin<br>espect to ground (V_{SS})— $V_{SS}$ -0.1ge on VDD_HV_ADC pin (ADC reference)<br>espect to ground (V_{SS})— $V_{DD}$ -0.1ge on any GPIO pin with respect to ground<br>(V_SS)— $V_{SS}$ -0.1ge on any GPIO pin with respect to ground<br>                                                                                                                                             | 3.6                  | V                                                                                                                                                                                                                                                                                   |      |

|                                  |    | with respect to ground (V <sub>SS</sub> )                                                        | Relative to $V_{\text{DD}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>DD</sub> -0.1 | $\begin{tabular}{ c c c } \hline Max \\ \hline 0 \\ \hline 3.6 \\ \hline V_{SS} + 0.1 \\ \hline 3.6 \\ \hline V_{DD} + 0.1 \\ \hline V_{SS} + 0.1 \\ \hline 0.25 [V/\mu s] \\ \hline 50 \\ \hline 0.25 [V/\mu s] \\ \hline 105 \\ \hline 130 \\ \hline 125 \\ \hline \end{tabular}$ |      |

| V <sub>IN</sub>                  | SR | <b>o j i i o</b>                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>SS</sub> -0.1 | —                                                                                                                                                                                                                                                                                   | V    |

|                                  |    | (V <sub>SS</sub> )                                                                               | Relative to $V_{\text{DD}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | Max         0 $3.6$ $V_{SS}+0.1$ $3.6$ $V_{DD}+0.1$ $3.6$ $V_{DD}+0.1$ $$ $V_{DD}+0.1$ $5$ $50$ $0.25[V/\mu s]$ ) $85$ $110$ $105$ $130$ $125$                                                                                                                                      |      |

| I <sub>INJPAD</sub>              | SR | Injected input current on any pin during overload condition                                      | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -5                   | 5                                                                                                                                                                                                                                                                                   | mA   |

| IINJSUM                          | SR | Absolute sum of all injected input currents during overload condition                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -50                  | 50                                                                                                                                                                                                                                                                                  |      |

| TV <sub>DD</sub>                 | SR | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.0 <sup>7</sup>     | 0.25[V/µs]<br>)                                                                                                                                                                                                                                                                     | V/s  |

| TA C-Grade Part                  | SR | Ambient temperature under bias                                                                   | $f_{CPU} \le 64 \text{ MHz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -40                  | 85                                                                                                                                                                                                                                                                                  | °C   |

| T <sub>J C-Grade Part</sub>      | SR | Junction temperature under bias                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -40                  | 110                                                                                                                                                                                                                                                                                 |      |

| TA V-Grade Part                  | SR | Ambient temperature under bias                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -40                  | 105                                                                                                                                                                                                                                                                                 |      |

| T <sub>J V-Grade Part</sub>      | SR | Junction temperature under bias                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -40                  | 130                                                                                                                                                                                                                                                                                 |      |

| TA M-Grade Part                  | SR | Ambient temperature under bias                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -40                  | 125                                                                                                                                                                                                                                                                                 |      |

| T <sub>J M-Grade Part</sub>      | SR | Junction temperature under bias                                                                  | round        3.0       3.6         oply) $V_{SS}$ -0.1 $V_{SS}$ +0.1         with        3.0       3.6         Relative to $V_{DD}$ $V_{DD}$ -0.1 $V_{DD}$ +0         pin $3.0^5$ $3.6$ ence) $3.0^5$ $3.6$ Relative to $V_{DD}$ $V_{DD}$ -0.1 $V_{DD}$ +0         round $3.0^5$ $3.6$ Relative to $V_{DD}$ $V_{DD}$ -0.1 $V_{DD}$ +0         round $V_{SS}$ -0.1          Relative to $V_{DD}$ $V_{DD}$ +0         erload        -5       5         during        -50       50 $3.0^7$ $0.25[V_{0})$ )         f <sub>CPU</sub> $\leq$ 64 MHz       -40       85         -40       110       -40       110         -40       130       -40       130         -40       125       -40       125 | 150                  |                                                                                                                                                                                                                                                                                     |      |

$^1\,$  100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair

$^2$  330 nF capacitance needs to be provided between each  $V_{\text{DD}\_LV}/V_{\text{SS}\_LV}$  supply pair.

<sup>3</sup> 400 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics).

$^4\,$  100 nF capacitance needs to be provided between V\_DD\_ADC/V\_SS\_ADC pair.

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

<sup>6</sup> Guaranteed by device validation.

$^7\,$  Minimum value of TV\_{DD} must be guaranteed until V\_{DD} reaches 2.6 V (maximum value of V\_{PORH}).

K is a constant for the particular part, which may be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  may be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

### 2.15 I/O pad electrical characteristics

### 2.15.1 I/O pad types

The device provides four main I/O pad types depending on the associated alternate functions:

- Slow pads—These pads are the most common pads, providing a good compromise between transition time and low electromagnetic emission.

- Medium pads—These pads provide transition fast enough for the serial communication channels with controlled current to reduce electromagnetic emission.

- Fast pads—These pads provide maximum speed. There are used for improved Nexus debugging capability.

- Input only pads—These pads are associated to ADC channels and the external 32 kHz crystal oscillator (SXOSC) providing low input leakage.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance.

### 2.15.2 I/O input DC characteristics

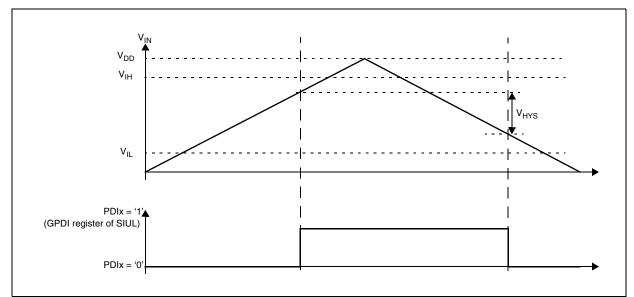

Table 15 provides input DC electrical characteristics as described in Figure 7.

Figure 7. I/O input DC electrical characteristics definition

# 2.15.4 Output pin transition times

| ev.             | mbol | ~ | Parameter                                |                         | Conditions <sup>1</sup>                                |     | Value | e   | Unit |

|-----------------|------|---|------------------------------------------|-------------------------|--------------------------------------------------------|-----|-------|-----|------|

| Sy              |      | C | Faiametei                                |                         | Conditions                                             | Min | Тур   | Max | onn  |

| t <sub>tr</sub> | CC   |   | Output transition time output            | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ | —   | —     | 50  | ns   |

|                 |      | Т | pin <sup>2</sup><br>SLOW configuration   | C <sub>L</sub> = 50 pF  |                                                        | —   | —     | 100 |      |

|                 |      | D | Ŭ                                        | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 125 |      |

|                 |      | D |                                          | C <sub>L</sub> = 25 pF  | $V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ | —   | —     | 50  |      |

|                 |      | Т |                                          | C <sub>L</sub> = 50 pF  |                                                        | —   | —     | 100 |      |

|                 |      | D |                                          | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 125 |      |

| t <sub>tr</sub> | CC   | D |                                          | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ | —   | —     | 10  | ns   |

|                 |      | Т | pin <sup>2</sup><br>MEDIUM configuration | C <sub>L</sub> = 50 pF  | SIUL.PCRx.SRC = 1                                      | —   | —     | 20  |      |

|                 |      | D |                                          | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 40  |      |

|                 |      | D |                                          | C <sub>L</sub> = 25 pF  | $V_{DD} = 3.3 V \pm 10\%$ , PAD3V5V = 1                | —   | —     | 12  |      |

|                 |      | Т |                                          | C <sub>L</sub> = 50 pF  | SIUL.PCRx.SRC = 1                                      | —   | —     | 25  |      |

|                 |      | D |                                          | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 40  |      |

| t <sub>tr</sub> | CC   | D | Output transition time output            | C <sub>L</sub> = 25 pF  | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ | —   | —     | 4   | ns   |

|                 |      |   | pin <sup>2</sup><br>FAST configuration   | C <sub>L</sub> = 50 pF  |                                                        | —   | —     | 6   |      |

|                 |      |   |                                          | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 12  |      |

|                 |      |   |                                          | C <sub>L</sub> = 25 pF  | $V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ | —   | —     | 4   |      |

|                 |      |   |                                          | C <sub>L</sub> = 50 pF  |                                                        | —   | —     | 7   |      |

|                 |      |   |                                          | C <sub>L</sub> = 100 pF |                                                        | —   | —     | 12  |      |

Table 20. Output pin transition times

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified

$^2$  C<sub>L</sub> includes device and package capacitances (C<sub>PKG</sub> < 5 pF).

### 2.15.5 I/O pad current specification

The I/O pads are distributed across the I/O supply segment. Each I/O supply segment is associated to a  $V_{DD}/V_{SS}$  supply pair as described in Table 21.

Table 21. I/O supply segment

| Package                 |             | Supply segment  |               |               |           |   |  |  |  |  |  |  |

|-------------------------|-------------|-----------------|---------------|---------------|-----------|---|--|--|--|--|--|--|

| Fachage                 | 1           | 2               | 3             | 4             | 5         | 6 |  |  |  |  |  |  |

| 208 MAPBGA <sup>1</sup> | Equivale    | ent to 144 LQFP | tribution     | МСКО          | MDOn/MSEO |   |  |  |  |  |  |  |

| 144 LQFP                | pin20–pin49 | pin51–pin99     | pin100-pin122 | pin 123–pin19 | _         | — |  |  |  |  |  |  |

| 100 LQFP                | pin16–pin35 | pin37–pin69     | pin70–pin83   | pin 84–pin15  | _         | — |  |  |  |  |  |  |

| 64 LQFP                 | pin8–pin26  | pin28–pin55     | pin56–pin7    | —             | _         | — |  |  |  |  |  |  |

| Symbo               | 1  | с | Parameter                       | Conditions <sup>1</sup>                                |     | Value |     | Unit |

|---------------------|----|---|---------------------------------|--------------------------------------------------------|-----|-------|-----|------|

| Symbol              |    | • | i uluncter                      | Conditions                                             | Min | Тур   | Max |      |

| I <sub>AVGSEG</sub> | SR |   |                                 | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 0$ |     |       | 70  | mA   |

|                     |    |   | current within a supply segment | $V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ | _   | —     | 65  |      |

Table 22. I/O consumption (continued)

Table 23 provides the weight of concurrent switching I/Os.

Due to the dynamic current limitations, the sum of the weight of concurrent switching I/Os on a single segment must not exceed 100% to ensure device functionality.

| Sup            | nlv sog     | mont                    |        |                      | 144/100 | ) LQFP       |         |            | 64 L    | QFP          |         |

|----------------|-------------|-------------------------|--------|----------------------|---------|--------------|---------|------------|---------|--------------|---------|

| Supply segment |             |                         | Pad    | Weight 5 V           |         | Weight 3.3 V |         | Weight 5 V |         | Weight 3.3 V |         |

| 144<br>LQFP    | 100<br>LQFP | 64<br>LQFP <sup>2</sup> |        | SRC <sup>3</sup> = 0 | SRC = 1 | SRC = 0      | SRC = 1 | SRC = 0    | SRC = 1 | SRC = 0      | SRC = 1 |

| 4              | 4           | 3                       | PB[3]  | 10%                  |         | 12%          | _       | 10%        | _       | 12%          |         |

|                |             |                         | PC[9]  | 10%                  |         | 12%          |         | 10%        | _       | 12%          |         |

|                |             | _                       | PC[14] | 9%                   | _       | 11%          | _       |            |         | —            | —       |

|                |             | _                       | PC[15] | 9%                   | 13%     | 11%          | 12%     | —          | _       | —            | —       |

|                |             | _                       | PG[5]  | 9%                   | —       | 11%          | —       | —          | _       | —            | —       |

|                | _           | _                       | PG[4]  | 9%                   | 12%     | 10%          | 11%     | —          | _       | —            | —       |

|                | _           | _                       | PG[3]  | 9%                   | —       | 10%          | —       | —          | _       | —            | —       |

| 4              | —           | _                       | PG[2]  | 8%                   | 12%     | 10%          | 10%     | —          | _       | —            | —       |

|                | 4           | 3                       | PA[2]  | 8%                   | —       | 9%           | —       | 8%         | _       | 9%           | —       |

|                |             | —                       | PE[0]  | 8%                   | —       | 9%           | —       | —          | _       | —            | —       |

|                |             | 3                       | PA[1]  | 7%                   | —       | 9%           | —       | 7%         | _       | 9%           | —       |

|                |             | —                       | PE[1]  | 7%                   | 10%     | 8%           | 9%      | —          | _       | —            | —       |

|                |             | —                       | PE[8]  | 7%                   | 9%      | 8%           | 8%      | —          | _       | —            | —       |

|                |             | _                       | PE[9]  | 6%                   | _       | 7%           | —       |            |         | —            | —       |

|                |             | —                       | PE[10] | 6%                   | _       | 7%           | —       | _          | _       | _            | —       |

|                |             | 3                       | PA[0]  | 5%                   | 8%      | 6%           | 7%      | 5%         | 8%      | 6%           | 7%      |

|                |             | —                       | PE[11] | 5%                   | —       | 6%           | —       | —          | _       | —            | —       |

### Table 23. I/O weight<sup>1</sup>

| 144/100 LQFP 64 LQFP |                |                         |        |                      |         |              |         |            |         |              |         |

|----------------------|----------------|-------------------------|--------|----------------------|---------|--------------|---------|------------|---------|--------------|---------|

| Sup                  | Supply segment |                         |        |                      | 144/100 | ) LQFP       |         |            | 64 L    | QFP          |         |

|                      |                |                         |        | Weight 5 V           |         | Weight 3.3 V |         | Weight 5 V |         | Weight 3.3 V |         |

| 144<br>LQFP          | 100<br>LQFP    | 64<br>LQFP <sup>2</sup> |        | SRC <sup>3</sup> = 0 | SRC = 1 | SRC = 0      | SRC = 1 | SRC = 0    | SRC = 1 | SRC = 0      | SRC = 1 |

| 2                    | 2              | 2                       | PB[13] | 10%                  |         | 12%          | —       | 18%        |         | 21%          | —       |

|                      |                | —                       | PD[14] | 10%                  | _       | 12%          | —       |            |         | —            |         |

|                      |                | 2                       | PB[14] | 10%                  | _       | 12%          | —       | 18%        | _       | 21%          | _       |

|                      |                | —                       | PD[15] | 10%                  | _       | 11%          |         |            | _       | _            |         |

|                      |                | 2                       | PB[15] | 9%                   | _       | 11%          | _       | 18%        | _       | 21%          | _       |

|                      |                |                         | PA[3]  | 9%                   | _       | 11%          | _       | 18%        | _       | 21%          | _       |

|                      | -              | —                       | PG[13] | 9%                   | 13%     | 10%          | 11%     |            |         | —            |         |

|                      | _              | —                       | PG[12] | 9%                   | 12%     | 10%          | 11%     | _          | _       | —            | _       |

|                      | _              | —                       | PH[0]  | 5%                   | 8%      | 6%           | 7%      |            | _       | —            |         |

|                      | _              | —                       | PH[1]  | 5%                   | 7%      | 6%           | 6%      |            |         | —            |         |

|                      | _              | —                       | PH[2]  | 5%                   | 6%      | 5%           | 6%      |            | _       | —            |         |

|                      | —              | —                       | PH[3]  | 4%                   | 6%      | 5%           | 5%      | —          | _       | —            | —       |

|                      | _              | —                       | PG[1]  | 4%                   |         | 4%           | —       |            |         | —            |         |

|                      | _              | —                       | PG[0]  | 3%                   | 4%      | 4%           | 4%      |            | _       | —            |         |

| 3                    | —              | —                       | PF[15] | 3%                   | _       | 4%           | —       | —          | _       | —            | —       |

|                      | —              | —                       | PF[14] | 4%                   | 5%      | 5%           | 5%      | —          | _       | —            | —       |

|                      | —              | —                       | PE[13] | 4%                   | _       | 5%           | —       | —          | _       | —            | —       |

|                      | 3              | 2                       | PA[7]  | 5%                   | _       | 6%           | —       | 16%        |         | 19%          | —       |

|                      |                |                         | PA[8]  | 5%                   | _       | 6%           | —       | 16%        | _       | 19%          | —       |

|                      |                |                         | PA[9]  | 5%                   | _       | 6%           | —       | 15%        | _       | 18%          | —       |

|                      |                |                         | PA[10] | 6%                   | _       | 7%           | —       | 15%        | _       | 18%          | —       |

|                      |                |                         | PA[11] | 6%                   |         | 8%           | —       | 14%        |         | 17%          |         |

|                      |                | —                       | PE[12] | 7%                   | _       | 8%           | —       | —          | _       | —            | —       |

|                      | _              | —                       | PG[14] | 7%                   | _       | 8%           | _       |            | _       | —            |         |

|                      | —              | —                       | PG[15] | 7%                   | 10%     | 8%           | 9%      | —          | _       | —            | —       |

|                      | —              | —                       | PE[14] | 7%                   |         | 8%           |         | —          |         | —            | —       |

|                      | -              | —                       | PE[15] | 7%                   | 9%      | 8%           | 8%      |            |         | —            |         |

|                      | —              | —                       | PG[10] | 6%                   | —       | 8%           |         | —          | _       | —            | —       |

|                      | —              | —                       | PG[11] | 6%                   | 9%      | 7%           | 8%      | —          |         | —            | —       |

|                      | 3              | 2                       | PC[3]  | 6%                   |         | 7%           |         | 7%         |         | 9%           |         |

|                      |                |                         | PC[2]  | 6%                   | 8%      | 7%           | 7%      | 6%         | 9%      | 8%           | 8%      |

### Table 23. I/O weight<sup>1</sup> (continued)

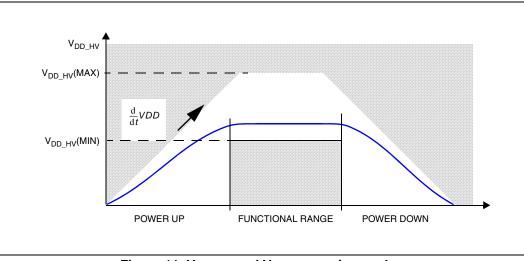

Figure 11.  $V_{DD\_HV}$  and  $V_{DD\_BV}$  maximum slope

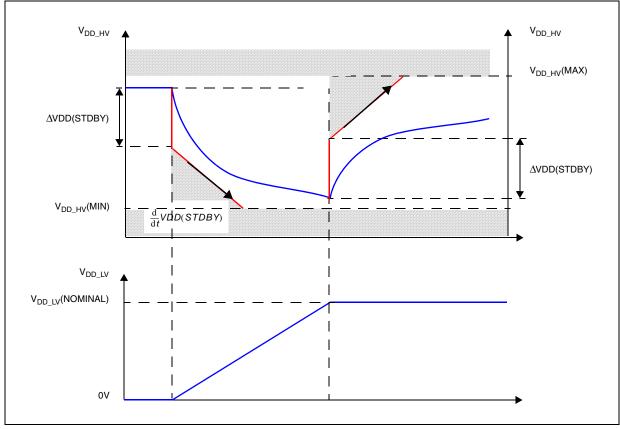

When STANDBY mode is used, further constraints are applied to the both  $V_{DD_{HV}}$  and  $V_{DD_{BV}}$  in order to guarantee correct regulator function during STANDBY exit. This is described on Figure 12.

STANDBY regulator constraints should normally be guaranteed by implementing equivalent of CSTDBY capacitance on application board (capacitance and ESR typical values), but would actually depend on exact characteristics of application external regulator.

- <sup>5</sup> Only for the "P" classification: Data and Code Flash in Normal Power. Code fetched from RAM: Serial IPs CAN and LIN in loop back mode, DSPI as Master, PLL as system Clock (4 x Multiplier) peripherals on (eMIOS/CTU/ADC) and running at max frequency, periodic SW/WDG timer reset enabled.

- <sup>6</sup> Data Flash Power Down. Code Flash in Low Power. SIRC (128 kHz) and FIRC (16 MHz) on. 10 MHz XTAL clock. FlexCAN: instances: 0, 1, 2 ON (clocked but not reception or transmission), instances: 4, 5, 6 clock gated. LINFlex: instances: 0, 1, 2 ON (clocked but not reception or transmission), instance: 3 clock gated. eMIOS: instance: 0 ON (16 channels on PA[0]–PA[11] and PC[12]–PC[15]) with PWM 20 kHz, instance: 1 clock gated. DSPI: instance: 0 (clocked but no communication). RTC/API ON. PIT ON. STM ON. ADC ON but not conversion except 2 analog watchdog.

- <sup>7</sup> Only for the "P" classification: No clock, FIRC (16 MHz) off, SIRC (128 kHz) on, PLL off, HPvreg off, ULPVreg/LPVreg on. All possible peripherals off and clock gated. Flash in power down mode.

- <sup>8</sup> When going from RUN to STOP mode and the core consumption is > 6 mA, it is normal operation for the main regulator module to be kept on by the on-chip current monitoring circuit. This is most likely to occur with junction temperatures exceeding 125 °C and under these circumstances, it is possible for the current to initially exceed the maximum STOP specification by up to 2 mA. After entering stop, the application junction temperature will reduce to the ambient level and the main regulator will be automatically switched off when the load current is below 6 mA.

- <sup>9</sup> Only for the "P" classification: ULPreg on, HP/LPVreg off, 32 KB RAM on, device configured for minimum consumption, all possible modules switched off.

- <sup>10</sup> ULPreg on, HP/LPVreg off, 8 KB RAM on, device configured for minimum consumption, all possible modules switched off.

# 2.19 Flash memory electrical characteristics

### 2.19.1 **Program/Erase characteristics**

Table 28 shows the program and erase characteristics.

| Symbol                   |    |   |                                                 |     | Va               | lue                         |                  |      |

|--------------------------|----|---|-------------------------------------------------|-----|------------------|-----------------------------|------------------|------|

|                          |    | С | Parameter                                       | Min | Typ <sup>1</sup> | Initial<br>max <sup>2</sup> | Max <sup>3</sup> | Unit |

| T <sub>dwprogram</sub>   | СС | С | Double word (64 bits) program time <sup>4</sup> | _   | 22               | 50                          | 500              | μs   |

| T <sub>16Kpperase</sub>  |    |   | 16 KB block preprogram and erase time           | _   | 300              | 500                         | 5000             | ms   |

| T <sub>32Kpperase</sub>  |    |   | 32 KB block preprogram and erase time           | _   | 400              | 600                         | 5000             | ms   |

| T <sub>128Kpperase</sub> |    |   | 128 KB block preprogram and erase time          | _   | 800              | 1300                        | 7500             | ms   |

| T <sub>esus</sub>        | СС | D | Erase suspend latency                           | _   | _                | 30                          | 30               | μs   |

#### Table 28. Program and erase specifications

<sup>1</sup> Typical program and erase times assume nominal supply values and operation at 25 °C.

<sup>2</sup> Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

<sup>3</sup> The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

<sup>4</sup> Actual hardware programming times. This does not include software overhead.

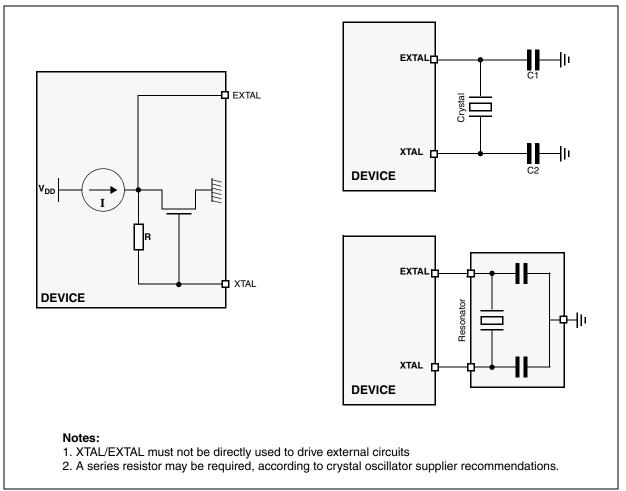

### Figure 14. Crystal oscillator and resonator connection scheme

| Nominal<br>frequency<br>(MHz) | NDK crystal<br>reference | Crystal<br>equivalent<br>series<br>resistance<br>ESR Ω | Crystal<br>motional<br>capacitance<br>(C <sub>m</sub> ) fF | Crystal<br>motional<br>inductance<br>(L <sub>m</sub> ) mH | Load on<br>xtalin/xtalout<br>C1 = C2<br>(pF) <sup>1</sup> | Shunt<br>capacitance<br>between<br>xtalout<br>and xtalin<br>C0 <sup>2</sup> (pF) |

|-------------------------------|--------------------------|--------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|

| 4                             | NX8045GB                 | 300                                                    | 2.68                                                       | 591.0                                                     | 21                                                        | 2.93                                                                             |

| 8                             | NX5032GA                 | 300                                                    | 2.46                                                       | 160.7                                                     | 17                                                        | 3.01                                                                             |