Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | -                                                                      |

| Core Size                  | -                                                                      |

| Speed                      | -                                                                      |

| Connectivity               | -                                                                      |

| Peripherals                | -                                                                      |

| Number of I/O              | -                                                                      |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | -                                                                      |

| EEPROM Size                | -                                                                      |

| RAM Size                   | -                                                                      |

| Voltage - Supply (Vcc/Vdd) | -                                                                      |

| Data Converters            | -                                                                      |

| Oscillator Type            | -                                                                      |

| Operating Temperature      | -                                                                      |

| Mounting Type              | -                                                                      |

| Package / Case             | -                                                                      |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5603bf2cll6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                       |                     | Device         |             |            |                    |            |                 |             |            |             |                 |             |             |                 |             |                            |

|---------------------------------------|---------------------|----------------|-------------|------------|--------------------|------------|-----------------|-------------|------------|-------------|-----------------|-------------|-------------|-----------------|-------------|----------------------------|

| Feature                               |                     |                |             |            | MPC56<br>02CxLL    |            | MPC56<br>03BxLL |             |            |             | MPC56<br>04BxLH |             |             | MPC56<br>04CxLH |             | MPC5604<br>BxMG            |

| • PWM +<br>IC/OC <sup>4</sup>         | 10 ch               | 20 ch          | 40 ch       | 10 ch      | 20 ch              | 10 ch      | 20 ch           | 40 ch       | 10 ch      | 20 ch       | 10 ch           | 20 ch       | 40 ch       | 10 ch           | 20 ch       | 40 ch                      |

| <ul> <li>IC/OC<sup>4</sup></li> </ul> | —                   | 3 ch           | 6 ch        | —          | 3 ch               | —          | 3 ch            | 6 ch        | —          | 3 ch        | —               | 3 ch        | 6 ch        | —               | 3 ch        | 6 ch                       |

| SCI (LINFlex)                         | x) 3 <sup>5</sup> 4 |                |             |            |                    |            |                 |             |            |             |                 |             |             |                 |             |                            |

| SPI (DSPI)                            | 2 3                 |                |             | 2          | 3                  | 2          | :               | 3           | 2          | 3           | 2 3             |             | 2           |                 | 3           |                            |

| CAN<br>(FlexCAN)                      |                     | 2 <sup>6</sup> |             | 5          | 5 6 3 <sup>7</sup> |            |                 | 5           | 6          | 37          |                 |             | 5           | 6               |             |                            |

| I <sup>2</sup> C                      |                     |                |             |            |                    |            |                 |             | 1          |             |                 |             |             |                 |             |                            |

| 32 kHz<br>oscillator                  |                     |                |             |            |                    |            |                 |             | Yes        |             |                 |             |             |                 |             |                            |

| GPIO <sup>8</sup>                     | 45                  | 79             | 123         | 45         | 79                 | 45         | 79              | 123         | 45         | 79          | 45              | 79          | 123         | 45              | 79          | 123                        |

| Debug                                 |                     |                | •           | •          | •                  | •          | •               | JTAG        | •          | •           | •               |             |             | •               |             | Nexus2+                    |

| Package                               | 64<br>LQFP          | 100<br>LQFP    | 144<br>LQFP | 64<br>LQFP | 100<br>LQFP        | 64<br>LQFP | 100<br>LQFP     | 144<br>LQFP | 64<br>LQFP | 100<br>LQFP | 64<br>LQFP      | 100<br>LQFP | 144<br>LQFP | 64<br>LQFP      | 100<br>LQFP | 208<br>MAPBGA <sup>9</sup> |

Table 1. MPC5604B/C device comparison<sup>1</sup> (continued)

Feature set dependent on selected peripheral multiplexing—table shows example implementation.

<sup>2</sup> Based on 125 °C ambient operating temperature.

<sup>3</sup> See the eMIOS section of the device reference manual for information on the channel configuration and functions.

<sup>4</sup> IC – Input Capture; OC – Output Compare; PWM – Pulse Width Modulation; MC – Modulus counter.

<sup>5</sup> SCI0, SCI1 and SCI2 are available. SCI3 is not available.

<sup>6</sup> CAN0, CAN1 are available. CAN2, CAN3, CAN4 and CAN5 are not available.

<sup>7</sup> CAN0, CAN3 and either CAN1 or CAN4 are available. CAN2, CAN5 and CAN6 are not available

<sup>8</sup> I/O count based on multiplexing with peripherals.

<sup>9</sup> 208 MAPBGA available only as development package for Nexus2+.

MPC5604B/C Microcontroller Data Sheet, Rev.

14

Note: Availability of port pin alternate functions depends on product selection.

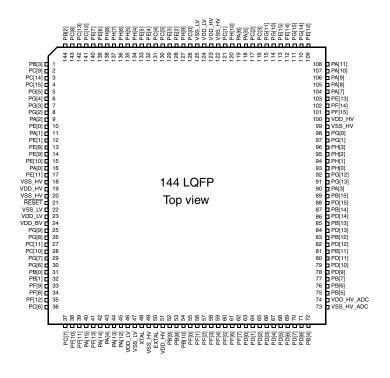

Figure 5. LQFP 144-pin configuration

|          |         | -                                  |                                                                              |                                                  |                                   |          | u                   |                  | Pin              | num      | ber      |                         |

|----------|---------|------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>    | Function                                                                     | Peripheral                                       | I/O direction <sup>2</sup>        | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PC[7]    | PCR[39] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[39]<br>—<br>—<br>LIN1RX<br>WKPU[12] <sup>4</sup>                        | SIUL<br>—<br>—<br>LINFlex_1<br>WKPU              | I/O<br>—<br>—<br>—<br>—<br>—      | S        | Tristate            | 17               | 17               | 26       | 37       | P3                      |

| PC[8]    | PCR[40] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[40]<br>LIN2TX<br>—<br>—                                                 | SIUL<br>LINFlex_2<br>—                           | I/O<br>O<br>                      | S        | Tristate            | 63               | 63               | 99       | 143      | A1                      |

| PC[9]    | PCR[41] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[41]<br>—<br>—<br>LIN2RX<br>WKPU[13] <sup>4</sup>                        | SIUL<br>—<br>—<br>LINFlex_2<br>WKPU              | I/O<br>   <br>   <br>             | S        | Tristate            | 2                | 2                | 2        | 2        | B1                      |

| PC[10]   | PCR[42] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[42]<br>CAN1TX<br>CAN4TX <sup>11</sup><br>MA[1]                          | SIUL<br>FlexCAN_1<br>FlexCAN_4<br>ADC            | I/O<br>O<br>O<br>O                | М        | Tristate            | 13               | 13               | 22       | 28       | MЗ                      |

| PC[11]   | PCR[43] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[43]<br>—<br>—<br>CAN1RX<br>CAN4RX <sup>11</sup><br>WKPU[5] <sup>4</sup> | SIUL<br>—<br>—<br>FlexCAN_1<br>FlexCAN_4<br>WKPU | I/O<br>—<br>—<br>—<br>—<br>—<br>— | S        | Tristate            |                  |                  | 21       | 27       | M4                      |

| PC[12]   | PCR[44] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[44]<br>E0UC[12]<br><br>SIN_2                                            | SIUL<br>eMIOS_0<br>—<br>DSPI_2                   | I/O<br>I/O<br>—<br>I              | Μ        | Tristate            |                  |                  | 97       | 141      | B4                      |

| PC[13]   | PCR[45] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[45]<br>E0UC[13]<br>SOUT_2<br>—                                          | SIUL<br>eMIOS_0<br>DSPI_2<br>—                   | I/O<br>I/O<br>O                   | S        | Tristate            |                  | _                | 98       | 142      | A2                      |

| PC[14]   | PCR[46] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[46]<br>E0UC[14]<br>SCK_2<br>—<br>EIRQ[8]                                | SIUL<br>eMIOS_0<br>DSPI_2<br>—<br>SIUL           | I/O<br>I/O<br>I/O<br>I            | S        | Tristate            |                  |                  | 3        | 3        | C1                      |

### Table 5. Functional port pin descriptions (continued)

|          |         | -                                       |                                                                   |                                                  |                                        |          | u                   |                  | Pin              | num      | ber      |                         |

|----------|---------|-----------------------------------------|-------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>         | Function                                                          | Peripheral                                       | I/O direction <sup>2</sup>             | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PF[8]    | PCR[88] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[88]<br>CAN3TX <sup>14</sup><br>CS4_0<br>CAN2TX <sup>15</sup> | SIUL<br>FlexCAN_3<br>DSPI_0<br>FlexCAN_2         | 1/0 0 0 0                              | М        | Tristate            |                  |                  |          | 34       | P1                      |

| PF[9]    | PCR[89] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[89]<br>                                                      | SIUL<br><br>DSPI_0<br><br>FlexCAN_2<br>FlexCAN_3 | I/O<br>— O<br>— I<br>— I               | S        | Tristate            | _                |                  |          | 33       | N2                      |

| PF[10]   | PCR[90] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[90]<br>—<br>—<br>—                                           | SIUL<br>—<br>—<br>—                              | I/O<br>  _                             | М        | Tristate            | —                |                  |          | 38       | R3                      |

| PF[11]   | PCR[91] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[91]<br>—<br>—<br>—<br>WKPU[15] <sup>4</sup>                  | SIUL<br>—<br>—<br>—<br>WKPU                      | I/O<br>—<br>—<br>—<br>—                | S        | Tristate            | _                | _                | _        | 39       | R4                      |

| PF[12]   | PCR[92] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[92]<br>E1UC[25]<br>—<br>—                                    | SIUL<br>eMIOS_1<br>—                             | I/O<br>I/O<br>                         | М        | Tristate            | _                | _                |          | 35       | R1                      |

| PF[13]   | PCR[93] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[93]<br>E1UC[26]<br>—<br>WKPU[16] <sup>4</sup>                | SIUL<br>eMIOS_1<br><br>WKPU                      | I/O<br>I/O<br>I                        | S        | Tristate            | _                | _                |          | 41       | T6                      |

| PF[14]   | PCR[94] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[94]<br>CAN4TX <sup>11</sup><br>E1UC[27]<br>CAN1TX            | SIUL<br>FlexCAN_4<br>eMIOS_1<br>FlexCAN_4        | I/O<br>O<br>I/O<br>O                   | М        | Tristate            |                  | 43               |          | 102      | D14                     |

| PF[15]   | PCR[95] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[95]<br>—<br>—<br>CAN1RX<br>CAN4RX <sup>11</sup><br>EIRQ[13]  | SIUL<br>—<br>—<br>FlexCAN_1<br>FlexCAN_4<br>SIUL | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>— | S        | Tristate            | _                | 42               |          | 101      | E15                     |

### Table 5. Functional port pin descriptions (continued)

|                     |          | <b>-</b> _                      |                                         |                                  |                            |          | uo                     |                  | Pin              | num      | ber      |                         |

|---------------------|----------|---------------------------------|-----------------------------------------|----------------------------------|----------------------------|----------|------------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin            | PCR      | Alternate function <sup>1</sup> | Function                                | Peripheral                       | I/O direction <sup>2</sup> | Pad type | RESET configuration    | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PH[2]               | PCR[114] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[114]<br>E1UC[4]<br>SCK_1<br>—      | SIUL<br>eMIOS_1<br>DSPI_1<br>—   | I/O<br>I/O<br>I/O<br>—     | М        | Tristate               | _                |                  |          | 95       | F16                     |

| PH[3]               | PCR[115] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[115]<br>E1UC[5]<br>CS0_1<br>—      | SIUL<br>eMIOS_1<br>DSPI_1<br>—   | I/O<br>I/O<br>I/O<br>—     | М        | Tristate               |                  |                  |          | 96       | F15                     |

| PH[4]               | PCR[116] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[116]<br>E1UC[6]<br>—<br>—          | SIUL<br>eMIOS_1<br>—             | I/O<br>I/O<br>             | М        | Tristate               |                  |                  |          | 134      | A6                      |

| PH[5]               | PCR[117] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[117]<br>E1UC[7]<br>—<br>—          | SIUL<br>eMIOS_1<br>—             | I/O<br>I/O<br>             | S        | Tristate               | _                |                  |          | 135      | B6                      |

| PH[6]               | PCR[118] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[118]<br>E1UC[8]<br>—<br>MA[2]      | SIUL<br>eMIOS_1<br><br>ADC       | I/O<br>I/O<br>—<br>O       | М        | Tristate               |                  |                  | _        | 136      | D5                      |

| PH[7]               | PCR[119] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[119]<br>E1UC[9]<br>CS3_2<br>MA[1]  | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC | I/O<br>I/O<br>O<br>O       | М        | Tristate               |                  |                  |          | 137      | C5                      |

| PH[8]               | PCR[120] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[120]<br>E1UC[10]<br>CS2_2<br>MA[0] | SIUL<br>eMIOS_1<br>DSPI_2<br>ADC | I/O<br>I/O<br>O<br>O       | М        | Tristate               |                  |                  |          | 138      | A5                      |

| PH[9] <sup>9</sup>  | PCR[121] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[121]<br>—<br>TCK<br>—              | SIUL<br>—<br>JTAGC<br>—          | I/O<br>—<br>I<br>—         | S        | Input, weak<br>pull-up | 60               | 60               | 88       | 127      | B8                      |

| PH[10] <sup>9</sup> | PCR[122] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[122]<br><br>TMS<br>                | SIUL<br>—<br>JTAGC<br>—          | I/O<br>—<br>I<br>—         | S        | Input, weak<br>pull-up | 53               | 53               | 81       | 120      | B9                      |

### Table 5. Functional port pin descriptions (continued)

# 2.8 Electrical characteristics

# 2.9 Introduction

This section contains electrical characteristics of the device as well as temperature and power considerations.

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid applying any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This could be done by the internal pull-up and pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

# 2.10 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 7 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

| Table 7. | Parameter | classifications |

|----------|-----------|-----------------|

|----------|-----------|-----------------|

## NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 2.11 NVUSRO register

Bit values in the Non-Volatile User Options (NVUSRO) Register control portions of the device configuration, namely electrical parameters such as high voltage supply and oscillator margin, as well as digital functionality (watchdog enable/disable after reset).

For a detailed description of the NVUSRO register, please refer to the device reference manual.

## 2.11.1 NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. Table 8 shows how NVUSRO[PAD3V5V] controls the device configuration.

Table 8. PAD3V5V field description

| Value <sup>1</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

<sup>1</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

## 2.11.2 NVUSRO[OSCILLATOR\_MARGIN] field description

The fast external crystal oscillator consumption is dependent on the OSCILLATOR\_MARGIN bit value. Table 9 shows how NVUSRO[OSCILLATOR\_MARGIN] controls the device configuration.

Table 9. OSCILLATOR\_MARGIN field description

| Value <sup>1</sup> | Description                                |  |  |  |  |

|--------------------|--------------------------------------------|--|--|--|--|

| 0                  | ow consumption configuration (4 MHz/8 MHz) |  |  |  |  |

| 1                  | High margin configuration (4 MHz/16 MHz)   |  |  |  |  |

| 1                  |                                            |  |  |  |  |

<sup>1</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

## 2.11.3 NVUSRO[WATCHDOG\_EN] field description

The watchdog enable/disable configuration after reset is dependent on the WATCHDOG\_EN bit value. Table 10 shows how NVUSRO[WATCHDOG\_EN] controls the device configuration.

### Table 10. WATCHDOG\_EN field description

| Value <sup>1</sup> | Description         |

|--------------------|---------------------|

| 0                  | Disable after reset |

| 1                  | Enable after reset  |

<sup>1</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

| Symbol                           |    | Parametar                                                                                     | Conditions                  | Va                   | lue                  | Unit |

|----------------------------------|----|-----------------------------------------------------------------------------------------------|-----------------------------|----------------------|----------------------|------|

| Symbol                           |    | Parameter                                                                                     | Conditions                  | Min                  | Max                  | Unit |

| V <sub>SS</sub>                  | SR | Digital ground on VSS_HV pins                                                                 | _                           | 0                    | 0                    | V    |

| V <sub>DD</sub> <sup>1</sup>     | SR | Voltage on VDD_HV pins with respect to                                                        | _                           | 4.5                  | 5.5                  | V    |

|                                  |    | ground (V <sub>SS</sub> )                                                                     | Voltage drop <sup>2</sup>   | 3.0                  | 5.5                  |      |

| V <sub>SS_LV</sub> <sup>3</sup>  | SR | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | —                           | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_BV</sub> <sup>4</sup>  | SR | Voltage on VDD_BV pin (regulator supply)                                                      | _                           | 4.5                  | 5.5                  | V    |

|                                  |    | with respect to ground (V <sub>SS</sub> )                                                     | Voltage drop <sup>2</sup>   | 3.0                  | 5.5                  |      |

|                                  |    |                                                                                               | Relative to V <sub>DD</sub> | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |

| V <sub>SS_ADC</sub>              | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub>             | —                           | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_ADC</sub> <sup>5</sup> | SR | Voltage on VDD_HV_ADC pin (ADC                                                                |                             | 4.5                  | 5.5                  | V    |

|                                  |    | reference) with respect to ground $(V_{SS})$                                                  | Voltage drop <sup>2</sup>   | 3.0                  | 5.5                  |      |

|                                  |    |                                                                                               | Relative to V <sub>DD</sub> | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |

| V <sub>IN</sub>                  | SR | 5 5 1 1                                                                                       |                             | V <sub>SS</sub> -0.1 | —                    | V    |

|                                  |    | ground (V <sub>SS</sub> )                                                                     | Relative to V <sub>DD</sub> | —                    | V <sub>DD</sub> +0.1 |      |

| I <sub>INJPAD</sub>              | SR | Injected input current on any pin during<br>overload condition                                | —                           | -5                   | 5                    | mA   |

| I <sub>INJSUM</sub>              | SR | Absolute sum of all injected input currents during overload condition                         | —                           | -50                  | 50                   |      |

| TV <sub>DD</sub>                 | SR | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                                 |                             | 3.0 <sup>7</sup>     | 0.25 V/µs            | V/s  |

| TA C-Grade Part                  | SR | Ambient temperature under bias                                                                | f <sub>CPU</sub> ≤64 MHz    | -40                  | 85                   | °C   |

| T <sub>J C-Grade Part</sub>      | SR | Junction temperature under bias                                                               |                             | -40                  | 110                  |      |

| TA V-Grade Part                  | SR | Ambient temperature under bias                                                                | 1                           | -40                  | 105                  |      |

| T <sub>J V-Grade Part</sub>      | SR | Junction temperature under bias                                                               |                             | -40                  | 130                  |      |

| TA M-Grade Part                  | SR | Ambient temperature under bias                                                                |                             | -40                  | 125                  |      |

| T <sub>J M-Grade</sub> Part      | SR | Junction temperature under bias                                                               |                             | -40                  | 150                  |      |

| Table 13 | . Recommended | operating | conditions | (5.0 V) | ) |

|----------|---------------|-----------|------------|---------|---|

|----------|---------------|-----------|------------|---------|---|

$^1$  100 nF capacitance needs to be provided between each  $V_{\text{DD}}/V_{\text{SS}}$  pair.

<sup>2</sup> Full device operation is guaranteed by design when the voltage drops below 4.5 V down to 3.0 V. However, certain analog electrical characteristics will not be guaranteed to stay within the stated limits.

$^3~$  330 nF capacitance needs to be provided between each V\_{DD\\_LV}/V\_{SS\\_LV} supply pair.

<sup>4</sup> 100 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics).

<sup>5</sup> 1 μF (electrolithic/tantalum) + 47 nF (ceramic) capacitance needs to be provided between V<sub>DD\_ADC</sub>/V<sub>SS\_ADC</sub> pair. Another ceramic cap of 10 nF with low inductance package can be added.

<sup>6</sup> Guaranteed by device validation.

<sup>7</sup> Minimum value of TV<sub>DD</sub> must be guaranteed until V<sub>DD</sub> reaches 2.6 V (maximum value of V<sub>PORH</sub>).

| Sym                | Symbol C |   | Parameter                                         | Conditions <sup>2</sup> | Pin count | Value | Unit |

|--------------------|----------|---|---------------------------------------------------|-------------------------|-----------|-------|------|

| $\Psi_{\text{JC}}$ | CC       | D | Junction-to-case thermal                          | Single-layer board - 1s | 64        | TBD   | °C/W |

|                    |          |   | characterization parameter,<br>natural convection |                         | 100       | 9     |      |

|                    |          |   |                                                   |                         | 144       | 10    |      |

|                    |          |   |                                                   | Four-layer board - 2s2p | 64        | TBD   |      |

|                    |          |   |                                                   |                         | 100       | 9     |      |

|                    |          |   |                                                   |                         | 144       | 10    |      |

Table 14. LQFP thermal characteristics<sup>1</sup> (continued)

<sup>1</sup> Thermal characteristics are based on simulation.

$^2~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C

<sup>3</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>4</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

<sup>5</sup> Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

## 2.14.2 Power considerations

The average chip-junction temperature, T<sub>I</sub>, in degrees Celsius, may be calculated using Equation 1:

$$T_{J} = T_{A} + (P_{D} \times R_{\theta JA})$$

Eqn. 7

Where:

$T_A$  is the ambient temperature in °C.

$R_{\theta JA}$  is the package junction-to-ambient thermal resistance, in °C/W.

$P_D$  is the sum of  $P_{INT}$  and  $P_{I/O} (P_D = P_{INT} + P_{I/O})$ .

P<sub>INT</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in watts. This is the chip internal power.

$P_{I/O}$  represents the power dissipation on input and output pins; user determined.

Most of the time for the applications,  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant, if the device is configured to continuously drive external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$P_{\rm D} = K / (T_{\rm J} + 273 \,^{\circ}{\rm C})$$

Eqn. 2

Therefore, solving equations 1 and 2:

$$K = P_D x (T_A + 273 °C) + R_{\theta JA} x P_D^2$$

Eqn. 3

Where:

MPC5604B/C Microcontroller Data Sheet, Rev. 14

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

Table 22 provides I/O consumption figures.

In order to ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{\rm AVGSEG}$  maximum value.

| Symbo                            |    | с | Parameter                                       | Condi                           | tions <sup>1</sup>                            |     | Value   |      | Unit |

|----------------------------------|----|---|-------------------------------------------------|---------------------------------|-----------------------------------------------|-----|---------|------|------|

| Symbo                            | 1  | Č | Farameter                                       | Condi                           | 10115                                         | Min | Тур     | Max  | Onne |

| I <sub>SWTSLW</sub> <sup>2</sup> | СС | D | Dynamic I/O current for SLOW configuration      | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     |     | —       | 20   | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     |         | 16   |      |

| I <sub>SWTMED</sub> <sup>2</sup> | СС | D | Dynamic I/O current for<br>MEDIUM configuration | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _   |         | 29   | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     |         | 17   |      |

| I <sub>SWTFST</sub> <sup>2</sup> | сс | D | Dynamic I/O current for<br>FAST configuration   | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _   |         | 110  | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   |         | 50   |      |

| I <sub>RMSSLW</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 5.0 V \pm 10\%,$                    |     | —       | 2.3  | mA   |

|                                  |    |   | current for SLOW<br>configuration               | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 0                                   |     | - — 3.2 | 3.2  |      |

|                                  |    |   | 0                                               | C <sub>L</sub> = 100 pF, 2 MHz  |                                               |     | —       | 6.6  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 3.3 V \pm 10\%,$                    |     | —       | 1.6  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 1                                   |     | —       | 2.3  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 2 MHz  |                                               |     | —       | 4.7  |      |

| I <sub>RMSMED</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 5.0 V \pm 10\%,$                    |     | —       | 6.6  | mA   |

|                                  |    |   | current for MEDIUM<br>configuration             | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 0                                   |     | —       | 13.4 |      |

|                                  |    |   | Ū.                                              | C <sub>L</sub> = 100 pF, 13 MHz |                                               | _   | _       | 18.3 |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 3.3 V \pm 10\%,$                    |     | —       | 5    |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 1                                   |     | _       | 8.5  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 13 MHz |                                               |     | _       | 11   |      |

| I <sub>RMSFST</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 40 MHz  | $V_{DD} = 5.0 V \pm 10\%$ ,                   |     |         | 22   | mA   |

|                                  |    |   | current for FAST<br>configuration               | C <sub>L</sub> = 25 pF, 64 MHz  | PAD3V5V = 0                                   |     | _       | 33   |      |

|                                  |    |   | 5                                               | C <sub>L</sub> = 100 pF, 40 MHz | ]                                             | —   | _       | 56   |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 40 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   | —   | —       | 14   |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 64 MHz  | PAD3V5V = 1                                   | —   | —       | 20   |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 40 MHz |                                               |     |         | 35   |      |

Table 22. I/O consumption

| Symbo               | I        | с | Parameter                       | Conditions <sup>1</sup>                                |     | Unit |     |    |

|---------------------|----------|---|---------------------------------|--------------------------------------------------------|-----|------|-----|----|

| Cymbo               | Symbol C |   | i urumeter                      | Conditions                                             | Min | Тур  | Max |    |

| I <sub>AVGSEG</sub> | SR       |   |                                 | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0             | _   | _    | 70  | mA |

|                     |          |   | current within a supply segment | $V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1$ | _   |      | 65  |    |

Table 22. I/O consumption (continued)

Table 23 provides the weight of concurrent switching I/Os.

Due to the dynamic current limitations, the sum of the weight of concurrent switching I/Os on a single segment must not exceed 100% to ensure device functionality.

| Sup         | Supply segment |                         |        |                      | 144/100 | ) LQFP       |         |         | 64 L    | QFP     |         |

|-------------|----------------|-------------------------|--------|----------------------|---------|--------------|---------|---------|---------|---------|---------|

| Sup         | piy seg        | ment                    | Pad    | Weigh                | nt 5 V  | Weight 3.3 V |         | Weig    | ht 5 V  | Weigh   | t 3.3 V |

| 144<br>LQFP | 100<br>LQFP    | 64<br>LQFP <sup>2</sup> |        | SRC <sup>3</sup> = 0 | SRC = 1 | SRC = 0      | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 |

| 4           | 4              | 3                       | PB[3]  | 10%                  | —       | 12%          | —       | 10%     | _       | 12%     |         |

|             |                |                         | PC[9]  | 10%                  | _       | 12%          | _       | 10%     |         | 12%     | _       |

|             |                | _                       | PC[14] | 9%                   | —       | 11%          | —       | —       | _       | —       | _       |

|             |                | —                       | PC[15] | 9%                   | 13%     | 11%          | 12%     | —       | _       | —       | —       |

|             |                | —                       | PG[5]  | 9%                   | —       | 11%          | —       | —       | _       | —       | —       |

|             |                | —                       | PG[4]  | 9%                   | 12%     | 10%          | 11%     | —       |         | —       | —       |

|             |                | —                       | PG[3]  | 9%                   | —       | 10%          | —       | —       | _       | —       | —       |

| 4           |                | —                       | PG[2]  | 8%                   | 12%     | 10%          | 10%     | —       | _       | —       | —       |

|             | 4              | 3                       | PA[2]  | 8%                   | —       | 9%           | —       | 8%      |         | 9%      | —       |

|             |                | —                       | PE[0]  | 8%                   | —       | 9%           | —       | —       | _       | —       | —       |

|             |                | 3                       | PA[1]  | 7%                   | —       | 9%           | —       | 7%      | _       | 9%      | —       |

|             |                | —                       | PE[1]  | 7%                   | 10%     | 8%           | 9%      | —       |         | —       | —       |

|             |                | —                       | PE[8]  | 7%                   | 9%      | 8%           | 8%      | —       |         | —       | —       |

|             |                | _                       | PE[9]  | 6%                   | —       | 7%           | —       | —       | _       | —       | —       |

|             |                | _                       | PE[10] | 6%                   | —       | 7%           | —       | —       | _       | —       | —       |

|             |                | 3                       | PA[0]  | 5%                   | 8%      | 6%           | 7%      | 5%      | 8%      | 6%      | 7%      |

|             |                | _                       | PE[11] | 5%                   | _       | 6%           | _       | _       |         | _       | —       |

### Table 23. I/O weight<sup>1</sup>

### Example 2. Simplified regulator

The regulator should be able to provide significant amount of the current during the standby exit process. For example, in case of an ideal voltage regulator providing 200 mA current, it is possible to recalculate the equivalent  $\text{ESR}_{\text{STDBY}}(\text{MAX})$  and  $\text{C}_{\text{STDBY}}(\text{MIN})$  as follows:

$ESR_{STDBY}(MAX) = |\Delta_{VDD(STDBY)}|/(I_{DD BV} - 200 mA) = (30 mV)/(100 mA) = 0.3 \Omega$

$C_{STDBY}(MIN) = (I_{DD_BV} - 200 \text{ mA})/dVDD(STDBY)/dt = (300 \text{ mA} - 200 \text{ mA})/(15 \text{ mV/}\mu s) = 6.7 \mu F$

In case optimization is required,  $C_{STDBY}(MIN)$  and  $ESR_{STDBY}(MAX)$  should be calculated based on the regulator characteristics as well as the board  $V_{DD}$  plane characteristics.

## 2.17.2 Low voltage detector electrical characteristics

The device implements a Power-on Reset (POR) module to ensure correct power-up initialization, as well as four low voltage detectors (LVDs) to monitor the  $V_{DD}$  and the  $V_{DD}$  LV voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_POR in device reference manual)

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27 in device reference manual)

- LVDHV5 monitors V<sub>DD</sub> when application uses device in the 5.0 V ± 10% range (refer to RGM Functional Event Status (RGM\_FES) Register flag F\_LVD45 in device reference manual)

- LVDLVCOR monitors power domain No. 1 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD1 in device reference manual

- LVDLVBKP monitors power domain No. 0 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD0 in device reference manual)

## NOTE

When enabled, power domain No. 2 is monitored through LVDLVBKP.

| Symbo     | 4  | с | Parameter                                                                   | Conditions                               |         |         | Unit |        |  |

|-----------|----|---|-----------------------------------------------------------------------------|------------------------------------------|---------|---------|------|--------|--|

| Symbol    |    | Ŭ | rarameter                                                                   | Conditions                               | Min     | Тур     | Max  |        |  |

| P/E       | СС |   | Number of program/erase cycles                                              | 16 KB blocks                             | 100,000 | —       | —    | cycles |  |

|           |    |   | per block over the operating temperature range (T <sub>.1</sub> )           | 32 KB blocks                             | 10,000  | 100,000 | _    |        |  |

|           |    |   |                                                                             | 128 KB blocks                            | 1,000   | 100,000 | _    |        |  |

| Retention | СС |   | Minimum data retention at 85 °C<br>average ambient temperature <sup>1</sup> | Blocks with<br>0–1,000 P/E cycles        | 20      | —       | _    | years  |  |

|           |    |   |                                                                             | Blocks with<br>1,001–10,000 P/E cycles   | 10      | —       | _    |        |  |

|           |    |   |                                                                             | Blocks with<br>10,001–100,000 P/E cycles | 5       | —       | —    |        |  |

Table 29. Flash module life

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

ECC circuitry provides correction of single bit faults and is used to improve further automotive reliability results. Some units will experience single bit corrections throughout the life of the product with no impact to product reliability.

Table 30. Flash read access timing

| Symb              | ol | С | Parameter                           | Conditions <sup>1</sup> | Max | Unit |

|-------------------|----|---|-------------------------------------|-------------------------|-----|------|

| f <sub>READ</sub> | CC | Ρ | Maximum frequency for Flash reading | 2 wait states           | 64  | MHz  |

|                   |    | С |                                     | 1 wait state            | 40  |      |

|                   |    | С |                                     | 0 wait states           | 20  |      |

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified

## 2.19.2 Flash power supply DC characteristics

Table 31 shows the power supply DC characteristics on external supply.

#### Table 31. Flash memory power supply DC electrical characteristics

| Symbol C                        |    | C | Parameter                                                          | Conditions <sup>1</sup>                                                 |     |     | Unit |    |

|---------------------------------|----|---|--------------------------------------------------------------------|-------------------------------------------------------------------------|-----|-----|------|----|

|                                 |    | Ũ |                                                                    | oonaliono                                                               | Min | Тур | Max  |    |

| I <sub>FREAD</sub> <sup>2</sup> | СС | D | Sum of the current consumption on VDD_HV and VDD_BV on read access | Code flash memory module read $f_{CPU} = 64 \text{ MHz}^3$              |     | 15  | 33   | mA |

|                                 |    |   |                                                                    | Data flash memory module read<br>f <sub>CPU</sub> = 64 MHz <sup>3</sup> |     | 15  | 33   |    |

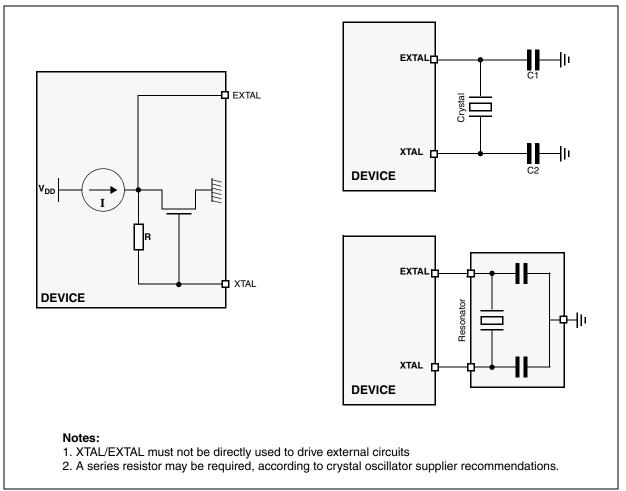

#### Figure 14. Crystal oscillator and resonator connection scheme

| Nominal<br>frequency<br>(MHz) | NDK crystal<br>reference | Crystal<br>equivalent<br>series<br>resistance<br>ESR Ω | Crystal<br>motional<br>capacitance<br>(C <sub>m</sub> ) fF | Crystal<br>motional<br>inductance<br>(L <sub>m</sub> ) mH | Load on<br>xtalin/xtalout<br>C1 = C2<br>(pF) <sup>1</sup> | Shunt<br>capacitance<br>between<br>xtalout<br>and xtalin<br>C0 <sup>2</sup> (pF) |

|-------------------------------|--------------------------|--------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|

| 4                             | NX8045GB                 | 300                                                    | 2.68                                                       | 591.0                                                     | 21                                                        | 2.93                                                                             |

| 8                             | NX5032GA                 | 300                                                    | 2.46                                                       | 160.7                                                     | 17                                                        | 3.01                                                                             |

| 10                            |                          | 150                                                    | 2.93                                                       | 86.6                                                      | 15                                                        | 2.91                                                                             |

| 12                            |                          | 120                                                    | 3.11                                                       | 56.5                                                      | 15                                                        | 2.93                                                                             |

| 16                            |                          | 120                                                    | 3.90                                                       | 25.3                                                      | 10                                                        | 3.00                                                                             |

Table 36. Crystal description

<sup>1</sup> The values specified for C1 and C2 are the same as used in simulations. It should be ensured that the testing includes all the parasitics (from the board, probe, crystal, etc.) as the AC / transient behavior depends upon them.

<sup>2</sup> The value of C0 specified here includes 2 pF additional capacitance for parasitics (to be seen with bond-pads, package, etc.).

- <sup>2</sup> This is the recommended range of load capacitance at OSC32K\_XTAL and OSC32K\_EXTAL with respect to ground. It includes all the parasitics due to board traces, crystal and package.

- <sup>3</sup> Maximum ESR ( $R_m$ ) of the crystal is 50 k $\Omega$

- <sup>4</sup> C0 includes a parasitic capacitance of 2.0 pF between OSC32K\_XTAL and OSC32K\_EXTAL pins

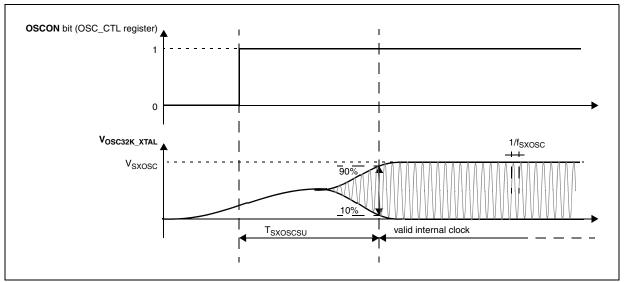

Figure 18. Slow external crystal oscillator (32 kHz) timing diagram

| Symbol                 |    | С | Parameter                                      | Conditions <sup>1</sup> |     |        | Unit           |     |

|------------------------|----|---|------------------------------------------------|-------------------------|-----|--------|----------------|-----|

| Symbol                 |    | C | r ai ainetei                                   | Conditions              | Min | Тур    | Max            | onn |

| f <sub>sxosc</sub>     | SR | — | Slow external crystal oscillator frequency     |                         | 32  | 32.768 | 40             | kHz |

| V <sub>SXOSC</sub>     | СС | Т | Oscillation amplitude                          | _                       | _   | 2.1    | _              | V   |

| I <sub>SXOSCBIAS</sub> | СС | Т | Oscillation bias current                       | _                       | _   | 2.5    | _              | μA  |

| I <sub>SXOSC</sub>     | СС | Т | Slow external crystal oscillator consumption   | _                       | _   | —      | 8              | μA  |

| T <sub>SXOSCSU</sub>   | СС | Т | Slow external crystal oscillator start-up time | _                       |     | —      | 2 <sup>2</sup> | S   |

Table 39. Slow external crystal oscillator (32 kHz) electrical characteristics

<sup>1</sup>  $V_{DD} = 3.3 V \pm 10\% / 5.0 V \pm 10\%$ ,  $T_A = -40$  to 125 °C, unless otherwise specified. Values are specified for no neighbor GPIO pin activity. If oscillator is enabled (OSC32K\_XTAL and OSC32K\_EXTAL pins), neighboring pins should not toggle.

<sup>2</sup> Start-up time has been measured with EPSON TOYOCOM MC306 crystal. Variation may be seen with other crystal.

## 2.23 FMPLL electrical characteristics

The device provides a frequency-modulated phase-locked loop (FMPLL) module to generate a fast system clock from the main oscillator driver.

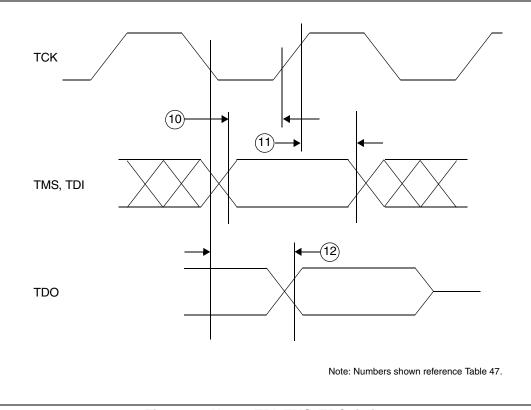

Figure 33. Nexus TDI, TMS, TDO timing

## 2.27.4 JTAG characteristics

### Table 48. JTAG characteristics

| No  | No. Symbol        |    | C Parameter |                        |     |     | Unit |      |

|-----|-------------------|----|-------------|------------------------|-----|-----|------|------|

| NO. | Synt              |    |             | Falanciel              | Min | Тур | Max  | Onit |

| 1   | t <sub>JCYC</sub> | CC | D           | TCK cycle time         | 64  | _   | _    | ns   |

| 2   | t <sub>TDIS</sub> | СС | D           | TDI setup time         | 15  | _   | _    | ns   |

| 3   | t <sub>TDIH</sub> | CC | D           | TDI hold time          | 5   | _   | _    | ns   |

| 4   | t <sub>TMSS</sub> | СС | D           | TMS setup time         | 15  | _   | _    | ns   |

| 5   | t <sub>TMSH</sub> | СС | D           | TMS hold time          | 5   | _   | _    | ns   |

| 6   | t <sub>TDOV</sub> | CC | D           | TCK low to TDO valid   | _   | _   | 33   | ns   |

| 7   | t <sub>TDOI</sub> | СС | D           | TCK low to TDO invalid | 6   |     | _    | ns   |

#### Package characteristics

|                                                                                                                                                                                                                                                        | MECHANICA         | L OUTLINES     | DOCUME  | ENT NO: 98ASS23308W |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|---------|---------------------|

|                                                                                                                                                                                                                                                        |                   | NARY           | PAGE:   | 983                 |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPORTIORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. | DO NOT SCALE      | THIS DRAWING   | REV:    | Н                   |

| NOTES:                                                                                                                                                                                                                                                 |                   |                |         |                     |

| 1. ALL DIMENSIONS ARE IN MILL                                                                                                                                                                                                                          | IMETERS.          |                |         |                     |

| 2. INTERPRET DIMENSIONS AND                                                                                                                                                                                                                            | TOLERANCES PER    | ASME Y14.5M-1  | 994.    |                     |

| 3. DATUMS B, C AND D TO BE                                                                                                                                                                                                                             | DETERMINED AT I   | DATUM PLANE H. |         |                     |

| 4. THE TOP PACKAGE BODY SIZ<br>BY A MAXIMUM OF 0.1 MM.                                                                                                                                                                                                 | E MAY BE SMALL    | ER THAN THE BC | TTOM PA | CKAGE SIZE          |

| 5. DIMENSIONS DO NOT INCLUDE<br>PROTRUSION IS 0.25 mm PE<br>SIZE DIMENSIONS INCLUDING                                                                                                                                                                  | ER SIDE. THE DIMI |                |         |                     |

| 6. DIMENSION DOES NOT INCLUE<br>CAUSE THE LEAD WIDTH TO<br>AND AN ADJACENT LEAD SH                                                                                                                                                                     | EXCEED 0.35. MII  | NIMUM SPACE BE |         |                     |

| 7. dimensions are determined                                                                                                                                                                                                                           | AT THE SEATING    | G PLANE, DATUM | Α.      |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

|                                                                                                                                                                                                                                                        |                   |                |         |                     |

| TITLE:<br>100 LEAD LQF                                                                                                                                                                                                                                 | Ð                 | CASE NUMBER: S | 983–02  |                     |

| 14 X 14, 0.5 PITCH,                                                                                                                                                                                                                                    |                   | STANDARD: NON  | -JEDEC  |                     |

| , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                |                   | PACKAGE CODE:  | 8264    | SHEET: 3            |

### Figure 40. 100 LQFP package mechanical drawing (3 of 3)

MPC5604B/C Microcontroller Data Sheet, Rev. 14

## 3.1.3 144 LQFP

Figure 41. 144 LQFP package mechanical drawing (1 of 2)

Figure 42. 144 LQFP package mechanical drawing (2 of 2)

#### **Document revision history**

| 9 | 16 June 2011 | Formatting and minor editorial changes throughout<br>Harmonized oscillator nomenclature<br>Removed all instances of note "All 64 LQFP information is indicative and must be<br>confirmed during silicon validation."                                                                                                                                                                                                                                                             |

|---|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |              | Removed all instances of note "All 64 LQFP information is indicative and must be<br>confirmed during silicon validation."                                                                                                                                                                                                                                                                                                                                                        |

|   |              | confirmed during silicon validation."                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |              | Device comparison table: changed temperature value in footnote 2 from 105 °C to 125 °C<br>MPC560xB LQFP 64-pin configuration and MPC560xC LQFP 64-pin configuration:<br>renamed pin 6 from VPP_TEST to VSS_HV                                                                                                                                                                                                                                                                    |

|   |              | Removed "Pin Muxing" section; added sections "Pad configuration during reset phases",<br>"Voltage supply pins", "Pad types", "System pins," "Functional ports", and "Nexus 2+<br>pins"                                                                                                                                                                                                                                                                                           |

|   |              | Section "NVUSRO register": edited content to separate configuration into electrical<br>parameters and digital functionality; updated footnote describing default value of '1' in<br>field descriptions NVUSRO[PAD3V5V] and NVUSRO[OSCILLATOR_MARGIN]                                                                                                                                                                                                                             |

|   |              | Added section "NVUSRO[WATCHDOG_EN] field description"                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |              | Recommended operating conditions (3.3 V) and Recommended operating conditions (5.0 V): updated conditions for ambient and junction temperature characteristics I/O input DC electrical characteristics: updated I <sub>LKG</sub> characteristics                                                                                                                                                                                                                                 |

|   |              | Section "I/O pad current specification": removed content referencing the I <sub>DYNSEG</sub><br>maximum value                                                                                                                                                                                                                                                                                                                                                                    |

|   |              | I/O consumption: replaced instances of "Root medium square" with "Root mean square"                                                                                                                                                                                                                                                                                                                                                                                              |

|   |              | I/O weight: replaced instances of bit "SRE" with "SRC"; added pads PH[9] and PH[10];<br>added supply segments; removed weight values in 64-pin LQFP for pads that do not<br>exist in that package                                                                                                                                                                                                                                                                                |

|   |              | Reset electrical characteristics: updated parameter classification for II <sub>WPU</sub> I<br>Updated Voltage regulator electrical characteristics                                                                                                                                                                                                                                                                                                                               |

|   |              | Section "Low voltage detector electrical characteristics": changed title (was "Voltage monitor electrical characteristics"); added event status flag names found in RGM chapter of device reference manual to POR module and LVD descriptions; replaced instances of "Low voltage monitor" with "Low voltage detector"; updated values for V <sub>LVDLVBKPL</sub> and V <sub>LVDLVCORL</sub> ; replaced "LVD_DIGBKP" with "LVDLVBKP" in note Updated section "Power consumption" |

|   |              | Fast external crystal oscillator (4 to 16 MHz) electrical characteristics: updated parameter                                                                                                                                                                                                                                                                                                                                                                                     |

|   |              | classification for V <sub>FXOSCOP</sub><br>Crystal oscillator and resonator connection scheme: added footnote about possibility of<br>adding a series resistor                                                                                                                                                                                                                                                                                                                   |

|   |              | Slow external crystal oscillator (32 kHz) electrical characteristics: updated footnote 1                                                                                                                                                                                                                                                                                                                                                                                         |

|   |              | FMPLL electrical characteristics: added short term jitter characteristics; inserted "—" in<br>empty min value cell of t <sub>lock</sub> row                                                                                                                                                                                                                                                                                                                                      |

|   |              | Section "Input impedance and ADC accuracy": changed "V <sub>A</sub> /V <sub>A2</sub> " to "V <sub>A2</sub> /V <sub>A</sub> " in Equation 11                                                                                                                                                                                                                                                                                                                                      |