Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | -                                                                      |

| Core Size                  | -                                                                      |

| Speed                      | -                                                                      |

| Connectivity               | -                                                                      |

| Peripherals                | -                                                                      |

| Number of I/O              | -                                                                      |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | -                                                                      |

| EEPROM Size                | -                                                                      |

| RAM Size                   | -                                                                      |

| Voltage - Supply (Vcc/Vdd) | -                                                                      |

| Data Converters            | -                                                                      |

| Oscillator Type            | -                                                                      |

| Operating Temperature      | -                                                                      |

| Mounting Type              | -                                                                      |

| Package / Case             | -                                                                      |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5603bf2mll4 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     | 1        | 2      | 3        | 4        | 5      | 6      | 7        | 8         | 9                | 10     | 11       | 12     | 13     | 14             | 15              | 16     |   |  |

|-----|----------|--------|----------|----------|--------|--------|----------|-----------|------------------|--------|----------|--------|--------|----------------|-----------------|--------|---|--|

| A   | PC[8]    | PC[13] | NC       | NC       | PH[8]  | PH[4]  | PC[5]    | PC[0]     | NC               | NC     | PC[2]    | NC     | PE[15] | NC             | NC              | NC     | А |  |

| В   | PC[9]    | PB[2]  | NC       | PC[12]   | PE[6]  | PH[5]  | PC[4]    | PH[9]     | PH[10]           | NC     | PC[3]    | PG[11] | PG[15] | PG[14]         | PA[11]          | PA[10] | в |  |

| С   | PC[14]   | VDD_HV | PB[3]    | PE[7]    | PH[7]  | PE[5]  | PE[3]    | VSS_LV    | PC[1]            | NC     | PA[5]    | NC     | PE[14] | PE[12]         | PA[9]           | PA[8]  | с |  |

| D   | NC       | NC     | PC[15]   | NC       | PH[6]  | PE[4]  | PE[2]    | VDD_LV    | VDD_HV           | NC     | PA[6]    | NC     | PG[10] | PF[14]         | PE[13]          | PA[7]  | D |  |

| Е   | PG[4]    | PG[5]  | PG[3]    | PG[2]    |        |        | •        |           |                  |        |          |        | PG[1]  | PG[0]          | PF[15]          | VDD_HV | Е |  |

| F   | PE[0]    | PA[2]  | PA[1]    | PE[1]    |        |        |          |           |                  |        |          |        | PH[0]  | PH[1]          | PH[3]           | PH[2]  | F |  |

| G   | PE[9]    | PE[8]  | PE[10]   | PA[0]    |        |        | VSS_HV   | VSS_HV    | VSS_HV           | VSS_HV |          |        | VDD_HV | NC             | NC              | MSEO   | G |  |

| н   | VSS_HV   | PE[11] | VDD_HV   | NC       |        |        | VSS_HV   | VSS_HV    | VSS_HV           | VSS_HV |          |        | MDO3   | MDO2           | MDO0            | MDO1   | н |  |

| J   | RESET    | VSS_LV | NC       | NC       |        |        | VSS_HV   | VSS_HV    | VSS_HV           | VSS_HV |          |        | NC     | NC             | NC              | NC     | J |  |

| к   | EVTI     | NC     | VDD_BV   | VDD_LV   |        |        | VSS_HV   | VSS_HV    | VSS_HV           | VSS_HV |          |        | NC     | PG[12]         | PA[3]           | PG[13] | к |  |

| L   | PG[9]    | PG[8]  | NC       | EVTO     |        |        |          | 1         |                  | 1      | <u>i</u> |        | PB[15] | PD[15]         | PD[14]          | PB[14] | L |  |

| М   | PG[7]    | PG[6]  | PC[10]   | PC[11]   |        |        |          |           |                  |        |          |        | PB[13] | PD[13]         | PD[12]          | PB[12] | м |  |

| Ν   | PB[1]    | PF[9]  | PB[0]    | NC       | NC     | PA[4]  | VSS_LV   | EXTAL     | VDD_HV           | PF[0]  | PF[4]    | NC     | PB[11] | PD[10]         | PD[9]           | PD[11] | N |  |

| Ρ   | PF[8]    | NC     | PC[7]    | NC       | NC     | PA[14] | VDD_LV   | XTAL      | PB[10]           | PF[1]  | PF[5]    | PD[0]  | PD[3]  | VDD_HV<br>_ADC | PB[6]           | PB[7]  | Р |  |

| R   | PF[12]   | PC[6]  | PF[10]   | PF[11]   | VDD_HV | PA[15] | PA[13]   | NC        | OSC32K<br>_XTAL  | PF[3]  | PF[7]    | PD[2]  | PD[4]  | PD[7]          | VSS_HV<br>_ADC  | PB[5]  | R |  |

| т   | NC       | NC     | NC       | МСКО     | NC     | PF[13] | PA[12]   | NC        | OSC32K<br>_EXTAL | PF[2]  | PF[6]    | PD[1]  | PD[5]  | PD[6]          | PD[8]           | PB[4]  | т |  |

|     | 1        | 2      | 3        | 4        | 5      | 6      | 7        | 8         | 9                | 10     | 11       | 12     | 13     | 14             | 15              | 16     |   |  |

| Not | e: 208 I | MAPBG  | A availa | ble only | as dev | elopme | nt packa | age for I | Vexus 2          | +.     |          |        |        | NC             | = Not connected |        |   |  |

Figure 6. 208 MAPBGA configuration

# 2.2 Pad configuration during reset phases

All pads have a fixed configuration under reset.

During the power-up phase, all pads are forced to tristate.

After power-up phase, all pads are forced to tristate with the following exceptions:

- PA[9] (FAB) is pull-down. Without external strong pull-up the device starts fetching from flash.

- PA[8] (ABS[0]) is pull-up.

- RESET pad is driven low. This is pull-up only after PHASE2 reset completion.

- JTAG pads (TCK, TMS and TDI) are pull-up whilst TDO remains tristate.

- Precise ADC pads (PB[7:4] and PD[11:0]) are left tristate (no output buffer available).

|          |         | -                                                      |                                                          |                                                 |                                    |          | u                      |                  | Pin              | num      | ber      |                         |

|----------|---------|--------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------|------------------------------------|----------|------------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | РСК     | Alternate function <sup>1</sup>                        | Function                                                 | Peripheral                                      | I/O direction <sup>2</sup>         | Pad type | RESET configuration    | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PA[8]    | PCR[8]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>N/A <sup>6</sup><br>— | GPIO[8]<br>E0UC[8]<br>—<br>EIRQ[3]<br>ABS[0]<br>LIN3RX   | SIUL<br>eMIOS_0<br><br>SIUL<br>BAM<br>LINFlex_3 | /O<br> /O<br> -<br> <br> <br> <br> | S        | Input, weak<br>pull-up | 45               | 45               | 72       | 105      | C16                     |

| PA[9]    | PCR[9]  | AF0<br>AF1<br>AF2<br>AF3<br>N/A <sup>6</sup>           | GPIO[9]<br>E0UC[9]<br>—<br>FAB                           | SIUL<br>eMIOS_0<br>—<br>BAM                     | /O<br> /O<br><br>                  | S        | Pull-down              | 46               | 46               | 73       | 106      | C15                     |

| PA[10]   | PCR[10] | AF0<br>AF1<br>AF2<br>AF3                               | GPIO[10]<br>E0UC[10]<br>SDA<br>—                         | SIUL<br>eMIOS_0<br>I2C_0<br>—                   | I/O<br>I/O<br>I/O<br>—             | S        | Tristate               | 47               | 47               | 74       | 107      | B16                     |

| PA[11]   | PCR[11] | AF0<br>AF1<br>AF2<br>AF3                               | GPIO[11]<br>E0UC[11]<br>SCL<br>—                         | SIUL<br>eMIOS_0<br>I2C_0<br>—                   | I/O<br>I/O<br>I/O<br>—             | S        | Tristate               | 48               | 48               | 75       | 108      | B15                     |

| PA[12]   | PCR[12] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[12]<br>—<br>—<br>—<br>SIN_0                         | SIUL<br>—<br>—<br>—<br>DSPI0                    | /O<br><br><br>_<br>I               | S        | Tristate               | 22               | 22               | 31       | 45       | Τ7                      |

| PA[13]   | PCR[13] | AF0<br>AF1<br>AF2<br>AF3                               | GPIO[13]<br>SOUT_0<br>—                                  | SIUL<br>DSPI_0<br>—<br>—                        | I/O<br>O<br>—                      | М        | Tristate               | 21               | 21               | 30       | 44       | R7                      |

| PA[14]   | PCR[14] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[14]<br>SCK_0<br>CS0_0<br>—<br>EIRQ[4]               | SIUL<br>DSPI_0<br>DSPI_0<br><br>SIUL            | /O<br> /O<br> /O<br>               | М        | Tristate               | 19               | 19               | 28       | 42       | P6                      |

| PA[15]   | PCR[15] | AF0<br>AF1<br>AF2<br>AF3<br>—                          | GPIO[15]<br>CS0_0<br>SCK_0<br>—<br>WKPU[10] <sup>4</sup> | SIUL<br>DSPI_0<br>DSPI_0<br>—<br>WKPU           | /O<br> /O<br> /O<br>               | М        | Tristate               | 18               | 18               | 27       | 40       | R6                      |

### Table 5. Functional port pin descriptions (continued)

|          |         | -                               |                                    |                                |                            |          | u                   |                  | Pir              | num      | ber      |                         |

|----------|---------|---------------------------------|------------------------------------|--------------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | РСК     | Alternate function <sup>1</sup> | Function                           | Peripheral                     | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PC[15]   | PCR[47] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[47]<br>E0UC[15]<br>CS0_2<br>— | SIUL<br>eMIOS_0<br>DSPI_2<br>— | I/O<br>I/O<br>I/O<br>—     | М        | Tristate            | _                |                  | 4        | 4        | D3                      |

| PD[0]    | PCR[48] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[48]<br>—<br>—<br>GPI[4]       | SIUL<br> -<br> <br>ADC         | <br> -<br> <br>            | Ι        | Tristate            |                  |                  | 41       | 63       | P12                     |

| PD[1]    | PCR[49] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[49]<br>—<br>—<br>GPI[5]       | SIUL<br>—<br>—<br>ADC          | <br> -<br> <br>            | I        | Tristate            | _                |                  | 42       | 64       | T12                     |

| PD[2]    | PCR[50] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[50]<br>—<br>—<br>GPI[6]       | SIUL<br> -<br>ADC              | <br> -<br> <br>            | -        | Tristate            | _                | _                | 43       | 65       | R12                     |

| PD[3]    | PCR[51] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[51]<br>—<br>—<br>—<br>GPI[7]  | SIUL<br>—<br>—<br>ADC          | <br> -<br> <br>            | I        | Tristate            | _                | _                | 44       | 66       | P13                     |

| PD[4]    | PCR[52] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[52]<br>—<br>—<br>—<br>GPI[8]  | SIUL<br>—<br>—<br>ADC          | <br><br><br>               | I        | Tristate            | _                |                  | 45       | 67       | R13                     |

| PD[5]    | PCR[53] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[53]<br>—<br>—<br>—<br>GPI[9]  | SIUL<br>—<br>—<br>ADC          | <br> -<br> <br>            | Ι        | Tristate            | _                |                  | 46       | 68       | T13                     |

| PD[6]    | PCR[54] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[54]<br>—<br>—<br>—<br>GPI[10] | SIUL<br>—<br>—<br>ADC          | <br> -<br> <br>            | Ι        | Tristate            |                  |                  | 47       | 69       | T14                     |

Table 5. Functional port pin descriptions (continued)

|          |         | -                               |                                                                          |                                          |                             |          | uo                  |                  | Pin              | num      | ber      |                         |

|----------|---------|---------------------------------|--------------------------------------------------------------------------|------------------------------------------|-----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | РСК     | Alternate function <sup>1</sup> | Function                                                                 | Peripheral                               | I/O direction <sup>2</sup>  | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PD[15]   | PCR[63] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[63]<br>CS2_1<br>E0UC[27]<br>—<br>ANS[7]                             | SIUL<br>DSPI_1<br>eMIOS_0<br>—<br>ADC    | I/O<br>O<br>I/O<br>_<br>I   | J        | Tristate            | _                | _                | 66       | 88       | L14                     |

| PE[0]    | PCR[64] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[64]<br>E0UC[16]<br><br>CAN5RX <sup>11</sup><br>WKPU[6] <sup>4</sup> | SIUL<br>eMIOS_0<br><br>FlexCAN_5<br>WKPU | /O<br> /O<br><br> <br> <br> | S        | Tristate            | —                | —                | 6        | 10       | F1                      |

| PE[1]    | PCR[65] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[65]<br>E0UC[17]<br>CAN5TX <sup>11</sup><br>—                        | SIUL<br>eMIOS_0<br>FlexCAN_5<br>—        | I/O<br>I/O<br>O             | М        | Tristate            | _                |                  | 8        | 12       | F4                      |

| PE[2]    | PCR[66] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[66]<br>E0UC[18]<br><br>SIN_1                                        | SIUL<br>eMIOS_0<br>—<br>DSPI_1           | /O<br> /O<br><br>           | Μ        | Tristate            | —                | _                | 89       | 128      | D7                      |

| PE[3]    | PCR[67] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[67]<br>E0UC[19]<br>SOUT_1<br>—                                      | SIUL<br>eMIOS_0<br>DSPI_1<br>—           | I/O<br>I/O<br>O             | Μ        | Tristate            |                  |                  | 90       | 129      | C7                      |

| PE[4]    | PCR[68] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[68]<br>E0UC[20]<br>SCK_1<br>—<br>EIRQ[9]                            | SIUL<br>eMIOS_0<br>DSPI_1<br>—<br>SIUL   | /O<br> /O<br> /O<br> <br>   | М        | Tristate            | _                | _                | 93       | 132      | D6                      |

| PE[5]    | PCR[69] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[69]<br>E0UC[21]<br>CS0_1<br>MA[2]                                   | SIUL<br>eMIOS_0<br>DSPI_1<br>ADC         | I/O<br>I/O<br>I/O<br>O      | М        | Tristate            | —                |                  | 94       | 133      | C6                      |

| PE[6]    | PCR[70] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[70]<br>E0UC[22]<br>CS3_0<br>MA[1]                                   | SIUL<br>eMIOS_0<br>DSPI_0<br>ADC         | I/O<br>I/O<br>O             | М        | Tristate            | _                | _                | 95       | 139      | B5                      |

| PE[7]    | PCR[71] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[71]<br>E0UC[23]<br>CS2_0<br>MA[0]                                   | SIUL<br>eMIOS_0<br>DSPI_0<br>ADC         | I/O<br>I/O<br>O<br>O        | М        | Tristate            |                  |                  | 96       | 140      | C4                      |

| Table 5. Functional | port pi | n descri | ptions | (continued) | ) |

|---------------------|---------|----------|--------|-------------|---|

|                     |         |          |        |             |   |

|          |          | -                               |                                                                    |                                                |                            |          | F                   |                  | Pin              | num      | ber      |                         |

|----------|----------|---------------------------------|--------------------------------------------------------------------|------------------------------------------------|----------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | РСК      | Alternate function <sup>1</sup> | Function                                                           | Peripheral                                     | I/O direction <sup>2</sup> | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PG[0]    | PCR[96]  | AF0<br>AF1<br>AF2<br>AF3        | GPIO[96]<br>CAN5TX <sup>11</sup><br>E1UC[23]<br>—                  | SIUL<br>FlexCAN_5<br>eMIOS_1<br>—              | I/O<br>O<br>I/O<br>—       | М        | Tristate            | _                | 41               |          | 98       | E14                     |

| PG[1]    | PCR[97]  | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[97]<br>—<br>E1UC[24]<br>—<br>CAN5RX <sup>11</sup><br>EIRQ[14] | SIUL<br>—<br>eMIOS_1<br>—<br>FlexCAN_5<br>SIUL | I/O<br>I/O<br>I -<br>I     | S        | Tristate            |                  | 40               |          | 97       | E13                     |

| PG[2]    | PCR[98]  | AF0<br>AF1<br>AF2<br>AF3        | GPIO[98]<br>E1UC[11]<br>—<br>—                                     | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>             | М        | Tristate            | —                | —                | —        | 8        | E4                      |

| PG[3]    | PCR[99]  | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[99]<br>E1UC[12]<br>—<br>—<br>WKPU[17] <sup>4</sup>            | SIUL<br>eMIOS_1<br>—<br>WKPU                   | I/O<br>I/O<br>I            | S        | Tristate            | _                | _                | _        | 7        | E3                      |

| PG[4]    | PCR[100] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[100]<br>E1UC[13]<br>—<br>—                                    | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>             | М        | Tristate            | _                | _                |          | 6        | E1                      |

| PG[5]    | PCR[101] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[101]<br>E1UC[14]<br>—<br>WKPU[18] <sup>4</sup>                | SIUL<br>eMIOS_1<br>—<br>WKPU                   | I/O<br>I/O<br>I            | S        | Tristate            | _                | _                | _        | 5        | E2                      |

| PG[6]    | PCR[102] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[102]<br>E1UC[15]<br>—<br>—                                    | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>             | М        | Tristate            |                  |                  |          | 30       | M2                      |

| PG[7]    | PCR[103] | AF0<br>AF1<br>AF2<br>AF3        | GPIO[103]<br>E1UC[16]<br>—<br>—                                    | SIUL<br>eMIOS_1<br>—                           | I/O<br>I/O<br>             | М        | Tristate            |                  |                  |          | 29       | M1                      |

| PG[8]    | PCR[104] | AF0<br>AF1<br>AF2<br>AF3<br>—   | GPIO[104]<br>E1UC[17]<br>—<br>CS0_2<br>EIRQ[15]                    | SIUL<br>eMIOS_1<br><br>DSPI_2<br>SIUL          | I/O<br>I/O<br>I/O<br>I     | S        | Tristate            |                  |                  |          | 26       | L2                      |

| Table 5. Functional port pin descriptions (continued) |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Sym                | nbol C Parameter |   | Conditions <sup>2</sup>                           | Pin count               | Value | Unit |      |

|--------------------|------------------|---|---------------------------------------------------|-------------------------|-------|------|------|

| $\Psi_{\text{JC}}$ | CC               | D | Junction-to-case thermal                          | Single-layer board - 1s | 64    | TBD  | °C/W |

|                    |                  |   | characterization parameter,<br>natural convection |                         | 100   | 9    |      |

|                    |                  |   |                                                   |                         | 144   | 10   |      |

|                    |                  |   |                                                   | Four-layer board - 2s2p | 64    | TBD  |      |

|                    |                  |   |                                                   |                         | 100   | 9    |      |

|                    |                  |   |                                                   |                         | 144   | 10   |      |

Table 14. LQFP thermal characteristics<sup>1</sup> (continued)

<sup>1</sup> Thermal characteristics are based on simulation.

$^2~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C

<sup>3</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>4</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

<sup>5</sup> Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

## 2.14.2 Power considerations

The average chip-junction temperature, T<sub>I</sub>, in degrees Celsius, may be calculated using Equation 1:

$$T_{J} = T_{A} + (P_{D} \times R_{\theta JA})$$

Eqn. 7

Where:

$T_A$  is the ambient temperature in °C.

$R_{\theta JA}$  is the package junction-to-ambient thermal resistance, in °C/W.

$P_D$  is the sum of  $P_{INT}$  and  $P_{I/O} (P_D = P_{INT} + P_{I/O})$ .

P<sub>INT</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in watts. This is the chip internal power.

$P_{I/O}$  represents the power dissipation on input and output pins; user determined.

Most of the time for the applications,  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant, if the device is configured to continuously drive external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$P_{\rm D} = K / (T_{\rm J} + 273 \,^{\circ}{\rm C})$$

Eqn. 2

Therefore, solving equations 1 and 2:

$$K = P_D x (T_A + 273 °C) + R_{\theta JA} x P_D^2$$

Eqn. 3

Where:

<sup>1</sup> 208 MAPBGA available only as development package for Nexus2+

Table 22 provides I/O consumption figures.

In order to ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{\rm AVGSEG}$  maximum value.

| Symbo                            |    | с | Parameter                                       | Condi                           | Conditions <sup>1</sup>                       |     | Value |      | Unit |

|----------------------------------|----|---|-------------------------------------------------|---------------------------------|-----------------------------------------------|-----|-------|------|------|

| Symbo                            | 1  | Č | Farameter                                       | Condi                           | 10115                                         | Min | Тур   | Max  | Onne |

| I <sub>SWTSLW</sub> <sup>2</sup> | СС | D | Dynamic I/O current for SLOW configuration      | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     |     | —     | 20   | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     |       | 16   |      |

| I <sub>SWTMED</sub> <sup>2</sup> | СС | D | Dynamic I/O current for<br>MEDIUM configuration | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _   |       | 29   | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 |     |       | 17   |      |

| I <sub>SWTFST</sub> <sup>2</sup> | сс | D | Dynamic I/O current for<br>FAST configuration   | C <sub>L</sub> = 25 pF          | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | _   |       | 110  | mA   |

|                                  |    |   |                                                 |                                 | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | _   |       | 50   |      |

| I <sub>RMSSLW</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 5.0 V \pm 10\%,$                    |     | —     | 2.3  | mA   |

|                                  |    |   | current for SLOW<br>configuration               | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 0                                   |     | —     | 3.2  |      |

|                                  |    | 0 | C <sub>L</sub> = 100 pF, 2 MHz                  | z                               |                                               | —   | 6.6   |      |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 2 MHz   | $V_{DD} = 3.3 V \pm 10\%,$                    |     | —     | 1.6  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 4 MHz   | PAD3V5V = 1                                   |     | —     | 2.3  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 2 MHz  |                                               |     | —     | 4.7  |      |

| I <sub>RMSMED</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 5.0 V \pm 10\%,$                    |     | —     | 6.6  | mA   |

|                                  |    |   | current for MEDIUM<br>configuration             | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 0                                   |     | —     | 13.4 |      |

|                                  |    |   | Ū                                               | C <sub>L</sub> = 100 pF, 13 MHz |                                               | _   | _     | 18.3 |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 13 MHz  | $V_{DD} = 3.3 V \pm 10\%,$                    |     | —     | 5    |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 40 MHz  | PAD3V5V = 1                                   |     | _     | 8.5  |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 13 MHz |                                               |     | _     | 11   |      |

| I <sub>RMSFST</sub>              | СС | D | Root mean square I/O                            | C <sub>L</sub> = 25 pF, 40 MHz  | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     |     |       | 22   | mA   |

|                                  |    |   | current for FAST<br>configuration               | C <sub>L</sub> = 25 pF, 64 MHz  |                                               |     | _     | 33   |      |

|                                  |    |   | 5                                               | C <sub>L</sub> = 100 pF, 40 MHz | ]                                             | —   | _     | 56   |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 40 MHz  | $V_{DD} = 3.3 V \pm 10\%$ ,                   | —   | —     | 14   |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 25 pF, 64 MHz  | PAD3V5V = 1                                   | —   | —     | 20   |      |

|                                  |    |   |                                                 | C <sub>L</sub> = 100 pF, 40 MHz |                                               |     |       | 35   |      |

Table 22. I/O consumption

### Example 2. Simplified regulator

The regulator should be able to provide significant amount of the current during the standby exit process. For example, in case of an ideal voltage regulator providing 200 mA current, it is possible to recalculate the equivalent  $\text{ESR}_{\text{STDBY}}(\text{MAX})$  and  $\text{C}_{\text{STDBY}}(\text{MIN})$  as follows:

$ESR_{STDBY}(MAX) = |\Delta_{VDD(STDBY)}|/(I_{DD BV} - 200 mA) = (30 mV)/(100 mA) = 0.3 \Omega$

$C_{STDBY}(MIN) = (I_{DD_BV} - 200 \text{ mA})/dVDD(STDBY)/dt = (300 \text{ mA} - 200 \text{ mA})/(15 \text{ mV/}\mu s) = 6.7 \mu F$

In case optimization is required,  $C_{STDBY}(MIN)$  and  $ESR_{STDBY}(MAX)$  should be calculated based on the regulator characteristics as well as the board  $V_{DD}$  plane characteristics.

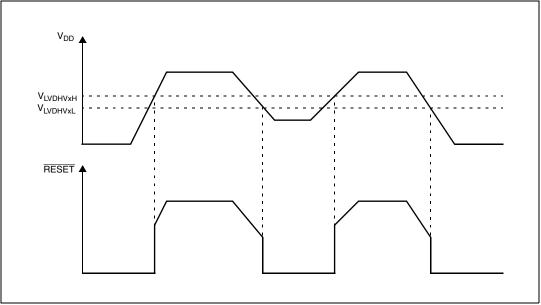

## 2.17.2 Low voltage detector electrical characteristics

The device implements a Power-on Reset (POR) module to ensure correct power-up initialization, as well as four low voltage detectors (LVDs) to monitor the  $V_{DD}$  and the  $V_{DD}$  LV voltage while device is supplied:

- POR monitors V<sub>DD</sub> during the power-up phase to ensure device is maintained in a safe reset state (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_POR in device reference manual)

- LVDHV3 monitors V<sub>DD</sub> to ensure device reset below minimum functional supply (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD27 in device reference manual)

- LVDHV5 monitors V<sub>DD</sub> when application uses device in the 5.0 V ± 10% range (refer to RGM Functional Event Status (RGM\_FES) Register flag F\_LVD45 in device reference manual)

- LVDLVCOR monitors power domain No. 1 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD1 in device reference manual

- LVDLVBKP monitors power domain No. 0 (refer to RGM Destructive Event Status (RGM\_DES) Register flag F\_LVD12\_PD0 in device reference manual)

## NOTE

When enabled, power domain No. 2 is monitored through LVDLVBKP.

Figure 13. Low voltage detector vs reset

### NOTE

Figure 13 does not apply to LVDHV5 low voltage detector because LVDHV5 is automatically disabled during reset and it must be enabled by software again. Once the device is forced to reset by LVDHV5, the LVDHV5 is disabled and reset is released as soon as internal reset sequence is completed regardless of LVDHV5H threshold.

| Symbol                 | Symbol |   | Parameter                                   | Conditions <sup>1</sup>                | Value |     |      | Unit     |

|------------------------|--------|---|---------------------------------------------|----------------------------------------|-------|-----|------|----------|

| Cymbol                 |        |   | i aranceei                                  | Conditions                             | Min   | Тур | Мах  | <b>U</b> |

| V <sub>PORUP</sub>     | SR     | Ρ | Supply for functional POR module            | —                                      | 1.0   | _   | 5.5  | V        |

| V <sub>PORH</sub>      | СС     | Ρ | Power-on reset threshold                    | $T_A = 25 \ ^{\circ}C,$ after trimming | 1.5   |     | 2.6  |          |

|                        |        | Т |                                             | _                                      | 1.5   |     | 2.6  |          |

| V <sub>LVDHV3H</sub>   | СС     | Т | LVDHV3 low voltage detector high threshold  | —                                      |       |     | 2.95 |          |

| V <sub>LVDHV3L</sub>   | СС     | Ρ | LVDHV3 low voltage detector low threshold   |                                        | 2.6   | _   | 2.9  |          |

| V <sub>LVDHV5H</sub>   | СС     | Т | LVDHV5 low voltage detector high threshold  |                                        | —     | _   | 4.5  |          |

| V <sub>LVDHV5L</sub>   | сс     | Ρ | LVDHV5 low voltage detector low threshold   |                                        | 3.8   | _   | 4.4  |          |

| V <sub>LVDLVCORL</sub> | СС     | Ρ | LVDLVCOR low voltage detector low threshold |                                        | 1.08  | _   | 1.16 |          |

| V <sub>LVDLVBKPL</sub> | СС     | Ρ | LVDLVBKP low voltage detector low threshold |                                        | 1.08  | _   | 1.16 |          |

$\overline{}^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

- <sup>5</sup> Only for the "P" classification: Data and Code Flash in Normal Power. Code fetched from RAM: Serial IPs CAN and LIN in loop back mode, DSPI as Master, PLL as system Clock (4 x Multiplier) peripherals on (eMIOS/CTU/ADC) and running at max frequency, periodic SW/WDG timer reset enabled.

- <sup>6</sup> Data Flash Power Down. Code Flash in Low Power. SIRC (128 kHz) and FIRC (16 MHz) on. 10 MHz XTAL clock. FlexCAN: instances: 0, 1, 2 ON (clocked but not reception or transmission), instances: 4, 5, 6 clock gated. LINFlex: instances: 0, 1, 2 ON (clocked but not reception or transmission), instance: 3 clock gated. eMIOS: instance: 0 ON (16 channels on PA[0]–PA[11] and PC[12]–PC[15]) with PWM 20 kHz, instance: 1 clock gated. DSPI: instance: 0 (clocked but no communication). RTC/API ON. PIT ON. STM ON. ADC ON but not conversion except 2 analog watchdog.

- <sup>7</sup> Only for the "P" classification: No clock, FIRC (16 MHz) off, SIRC (128 kHz) on, PLL off, HPvreg off, ULPVreg/LPVreg on. All possible peripherals off and clock gated. Flash in power down mode.

- <sup>8</sup> When going from RUN to STOP mode and the core consumption is > 6 mA, it is normal operation for the main regulator module to be kept on by the on-chip current monitoring circuit. This is most likely to occur with junction temperatures exceeding 125 °C and under these circumstances, it is possible for the current to initially exceed the maximum STOP specification by up to 2 mA. After entering stop, the application junction temperature will reduce to the ambient level and the main regulator will be automatically switched off when the load current is below 6 mA.

- <sup>9</sup> Only for the "P" classification: ULPreg on, HP/LPVreg off, 32 KB RAM on, device configured for minimum consumption, all possible modules switched off.

- <sup>10</sup> ULPreg on, HP/LPVreg off, 8 KB RAM on, device configured for minimum consumption, all possible modules switched off.

# 2.19 Flash memory electrical characteristics

## 2.19.1 **Program/Erase characteristics**

Table 28 shows the program and erase characteristics.

|                          |    |   |                                                 |     | Va               | lue                         |                  |      |  |

|--------------------------|----|---|-------------------------------------------------|-----|------------------|-----------------------------|------------------|------|--|

| Symbol                   |    | С | Parameter                                       | Min | Typ <sup>1</sup> | Initial<br>max <sup>2</sup> | Max <sup>3</sup> | Unit |  |

| T <sub>dwprogram</sub>   | CC | С | Double word (64 bits) program time <sup>4</sup> | —   | 22               | 50                          | 500              | μs   |  |

| T <sub>16Kpperase</sub>  |    |   | 16 KB block preprogram and erase time           | —   | 300              | 500                         | 5000             | ms   |  |

| T <sub>32Kpperase</sub>  |    |   | 32 KB block preprogram and erase time           | —   | 400              | 600                         | 5000             | ms   |  |

| T <sub>128Kpperase</sub> |    |   | 128 KB block preprogram and erase time          | _   | 800              | 1300                        | 7500             | ms   |  |

| T <sub>esus</sub>        | СС | D | Erase suspend latency                           | —   | _                | 30                          | 30               | μs   |  |

### Table 28. Program and erase specifications

<sup>1</sup> Typical program and erase times assume nominal supply values and operation at 25 °C.

<sup>2</sup> Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

<sup>3</sup> The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

<sup>4</sup> Actual hardware programming times. This does not include software overhead.

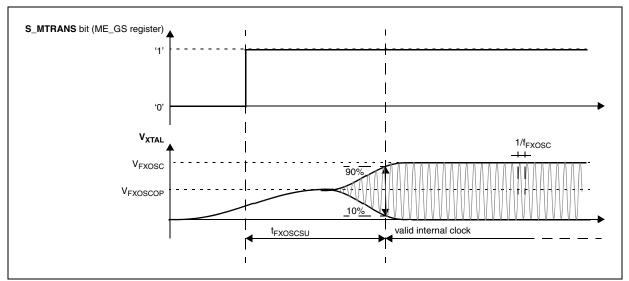

Figure 15. Fast external crystal oscillator (4 to 16 MHz) timing diagram

| Symbo                 |    | с | Parameter                                                                                                                                                 | Cor                               | nditions <sup>1</sup> | Value |      |     | Unit |

|-----------------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|-------|------|-----|------|

| Symbol                |    | Ŭ | i didileter                                                                                                                                               | 001                               |                       | Min   | Тур  | Max | onne |

| I <sub>FIRCSTOP</sub> | СС | Т | Fast internal RC oscillator high                                                                                                                          | T <sub>A</sub> = 25 °C            | sysclk = off          |       | 500  | _   | μΑ   |

|                       |    |   | frequency and system clock current in stop mode                                                                                                           |                                   | sysclk = 2 MHz        | _     | 600  |     |      |

|                       |    |   | •                                                                                                                                                         |                                   | sysclk = 4 MHz        | —     | 700  |     |      |

|                       |    |   |                                                                                                                                                           | :                                 | sysclk = 8 MHz        | —     | 900  |     |      |

|                       |    |   |                                                                                                                                                           |                                   | sysclk = 16 MHz       | —     | 1250 | _   |      |

| t <sub>FIRCSU</sub>   | СС | С | Fast internal RC oscillator start-up time                                                                                                                 | $V_{DD} = 5.0 \text{ V} \pm 10\%$ |                       | _     | 1.1  | 2.0 | μs   |

| $\Delta_{FIRCPRE}$    | СС | Т | Fast internal RC oscillator precision after software trimming of f <sub>FIRC</sub>                                                                        | T <sub>A</sub> = 25 °C            |                       | -1    | _    | +1  | %    |

| $\Delta_{FIRCTRIM}$   | СС | Т | Fast internal RC oscillator trimming step                                                                                                                 | T <sub>A</sub> = 25 °C            |                       | _     | 1.6  |     | %    |

|                       | CC | Ρ | Fast internal RC oscillator variation<br>in over temperature and supply with<br>respect to $f_{FIRC}$ at $T_A = 25$ °C in<br>high-frequency configuration |                                   | _                     | -5    |      | +5  | %    |

Table 41. Fast internal RC oscillator (16 MHz) electrical characteristics (continued)

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

<sup>2</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

# 2.25 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz slow internal RC oscillator. This can be used as the reference clock for the RTC module.

| Symbol                          | Symbol |   | Parameter                                                                          | Conditions <sup>1</sup>                           |     | Unit |     |     |

|---------------------------------|--------|---|------------------------------------------------------------------------------------|---------------------------------------------------|-----|------|-----|-----|

| Cymber                          |        | С | i didineter                                                                        | Conditions                                        | Min | Тур  | Max |     |

| f <sub>SIRC</sub>               | CC     | Ρ | Slow internal RC oscillator low                                                    | T <sub>A</sub> = 25 °C, trimmed                   |     | 128  | _   | kHz |

|                                 | SR     | _ | frequency                                                                          | _                                                 | 100 | _    | 150 |     |

| I <sub>SIRC</sub> <sup>2,</sup> | СС     |   | Slow internal RC oscillator low<br>frequency current                               | T <sub>A</sub> = 25 °C, trimmed                   |     |      | 5   | μA  |

| t <sub>SIRCSU</sub>             | СС     | Ρ | Slow internal RC oscillator start-up time                                          | $T_A = 25 \ ^{\circ}C, V_{DD} = 5.0 \ V \pm 10\%$ | _   | 8    | 12  | μs  |

| $\Delta_{SIRCPRE}$              | СС     | С | Slow internal RC oscillator precision after software trimming of f <sub>SIRC</sub> | T <sub>A</sub> = 25 °C                            | -2  | _    | +2  | %   |

|                                 | СС     | С | Slow internal RC oscillator trimming step                                          | —                                                 |     | 2.7  | —   |     |

Table 42. Slow internal RC oscillator (128 kHz) electrical characteristics

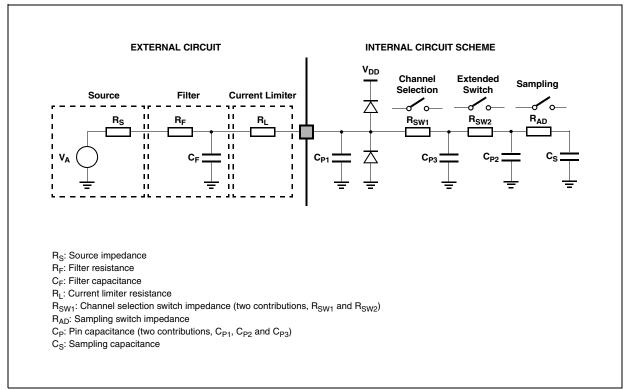

Figure 21. Input equivalent circuit (extended channels)

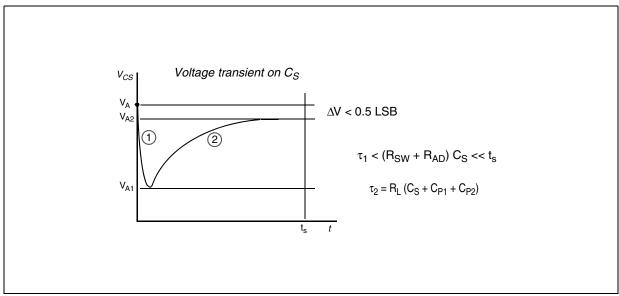

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  are initially charged at the source voltage  $V_A$  (refer to the equivalent circuit in Figure 20): A charge sharing phenomenon is installed when the sampling phase is started (A/D switch close).

Figure 22. Transient behavior during sampling phase

In particular two different transient periods can be distinguished:

| Cumh             |    | С | Deveneter                                    | Conditions <sup>1</sup>                              |                                  |     | Unit |     |     |  |

|------------------|----|---|----------------------------------------------|------------------------------------------------------|----------------------------------|-----|------|-----|-----|--|

| Symbol           |    | C | Parameter                                    | Conditions                                           |                                  | Min | Тур  | Мах |     |  |

| C <sub>P3</sub>  | СС | D | ADC input pin<br>capacitance 3               | -                                                    | —                                |     | —    | 1   | pF  |  |

| R <sub>SW1</sub> | СС | D | Internal resistance of<br>analog source      | -                                                    | _                                | —   | -    | 3   | kΩ  |  |

| R <sub>SW2</sub> | СС | D | Internal resistance of<br>analog source      | _                                                    | _                                | —   | -    | 2   | kΩ  |  |

| R <sub>AD</sub>  | СС | D | Internal resistance of<br>analog source      | _                                                    | _                                | —   | —    | 2   | kΩ  |  |

| I <sub>INJ</sub> | SR | — | Input current Injection                      | Current<br>injection on one                          | V <sub>DD</sub> =<br>3.3 V ± 10% | -5  | —    | 5   | mA  |  |

|                  |    |   |                                              | ADC input,<br>different from<br>the converted<br>one | V <sub>DD</sub> =<br>5.0 V ± 10% | -5  | -    | 5   |     |  |

| INL              | СС | Т | Absolute value for<br>integral non-linearity | No overload                                          | 1                                | —   | 0.5  | 1.5 | LSB |  |

| DNL              | СС | Т | Absolute differential non-linearity          | No overload                                          |                                  | _   | 0.5  | 1.0 | LSB |  |

| E <sub>O</sub>   | СС | Т | Absolute offset error                        | -                                                    | _                                | -   | 0.5  | _   | LSB |  |

| E <sub>G</sub>   | СС | Т | Absolute gain error                          | —                                                    |                                  | —   | 0.6  | _   | LSB |  |

| TUEp             | СС | Ρ | Total unadjusted error <sup>7</sup>          | Without current injection                            |                                  | -2  | 0.6  | 2   | LSB |  |

|                  |    | Т | for precise channels,<br>input only pins     | With current injection                               |                                  | -3  |      | 3   |     |  |

| TUEx             | СС | Т | Total unadjusted error <sup>7</sup>          | Without current                                      | injection                        | -3  | 1    | 3   | LSB |  |

|                  |    | Т | for extended channel                         | With current injection                               |                                  | -4  |      | 4   |     |  |

Table 44. ADC conversion characteristics (continued)

$^1~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

$^2$  Analog and digital V<sub>SS</sub> **must** be common (to be tied together externally).

<sup>3</sup> V<sub>AINx</sub> may exceed V<sub>SS\_ADC</sub> and V<sub>DD\_ADC</sub> limits, remaining on absolute maximum ratings, but the results of the conversion will be clamped respectively to 0x000 or 0x3FF.

<sup>4</sup> Duty cycle is ensured by using system clock without prescaling. When ADCLKSEL = 0, the duty cycle is ensured by internal divider by 2.

<sup>5</sup> During the sampling time the input capacitance  $C_S$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_s$ . After the end of the sampling time  $t_s$ , changes of the analog input voltage have no effect on the conversion result. Values for the sample clock  $t_s$  depend on programming.

<sup>6</sup> This parameter does not include the sampling time t<sub>s</sub>, but only the time for determining the digital result and the time to load the result's register with the conversion result.

<sup>7</sup> Total Unadjusted Error: The maximum error that occurs without adjusting Offset and Gain errors. This error is a combination of Offset, Gain and Integral Linearity errors.

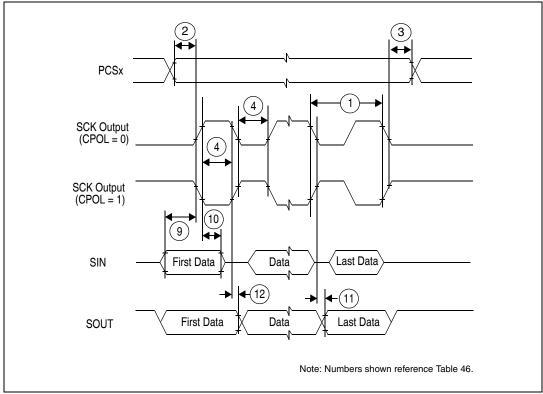

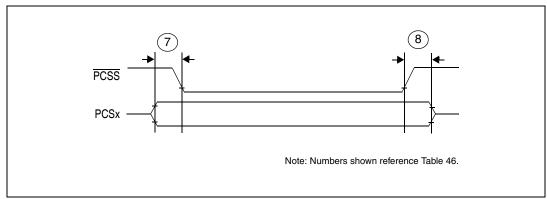

Figure 24. DSPI classic SPI timing – master, CPHA = 0

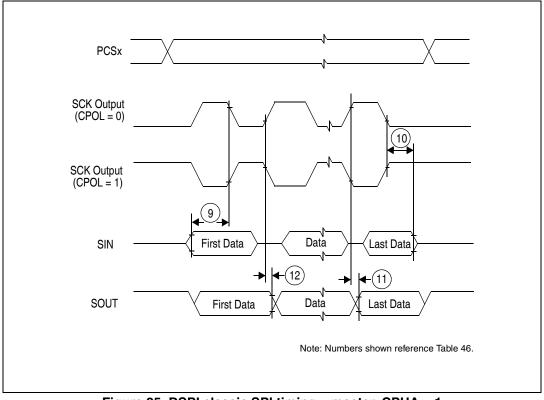

Figure 25. DSPI classic SPI timing – master, CPHA = 1

## 2.27.3 Nexus characteristics

| No. | Symb               |    | с | Parameter                     |     | Value |     | Unit |  |

|-----|--------------------|----|---|-------------------------------|-----|-------|-----|------|--|

| NO. | Symbol             |    | C | Falameter                     | Min | Тур   | Max |      |  |

| 1   | t <sub>TCYC</sub>  | CC | D | TCK cycle time                | 64  | —     | —   | ns   |  |

| 2   | t <sub>MCYC</sub>  | CC | D | MCKO cycle time               | 32  | —     | _   | ns   |  |

| 3   | t <sub>MDOV</sub>  | CC | D | MCKO low to MDO data valid    | —   | —     | 8   | ns   |  |

| 4   | t <sub>MSEOV</sub> | CC | D | MCKO low to MSEO_b data valid | —   | —     | 8   | ns   |  |

| 5   | t <sub>EVTOV</sub> | CC | D | MCKO low to EVTO data valid   | —   | —     | 8   | ns   |  |

| 10  | t <sub>NTDIS</sub> | CC | D | TDI data setup time           | 15  | —     | —   | ns   |  |

|     | t <sub>NTMSS</sub> | CC | D | TMS data setup time           | 15  | —     | —   | ns   |  |

| 11  | t <sub>NTDIH</sub> | CC | D | TDI data hold time            | 5   | —     | —   | ns   |  |

|     | t <sub>NTMSH</sub> | CC | D | TMS data hold time            | 5   | —     | —   | ns   |  |

| 12  | t <sub>TDOV</sub>  | CC | D | TCK low to TDO data valid     | 35  | —     | —   | ns   |  |

| 13  | t <sub>TDOI</sub>  | CC | D | TCK low to TDO data invalid   | 6   | —     | —   | ns   |  |

| Table 47. | Nexus | characteristics |

|-----------|-------|-----------------|

|-----------|-------|-----------------|

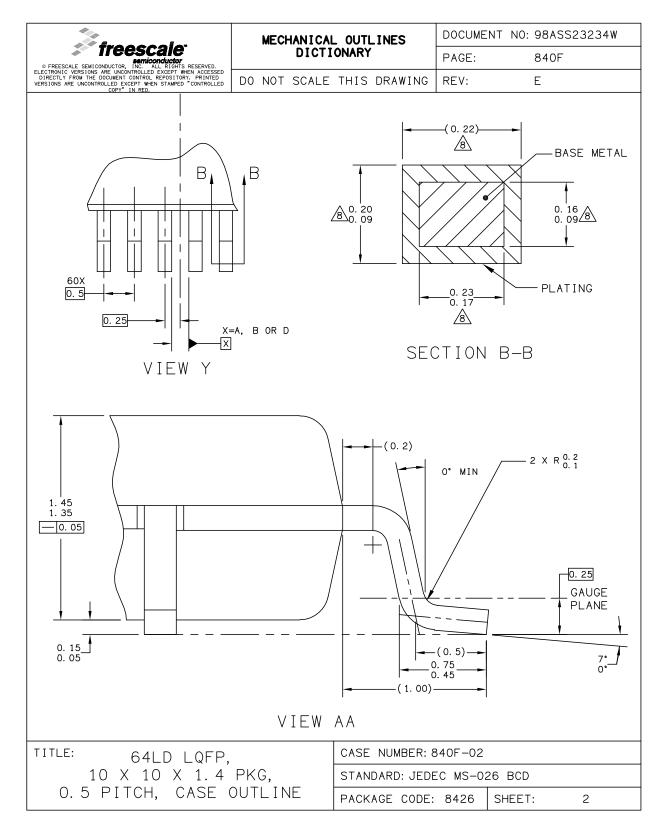

Package characteristics

Figure 36. 64 LQFP package mechanical drawing (2 of 3)

## 3.1.4 208 MAPBGA

Figure 43. 208 MAPBGA package mechanical drawing (1 of 2)

### **Document revision history**

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 15-Mar-2010 | In the "Introduction" section, relocated a note.<br>In the "MPC5604B/C device comparison" table, added footnote regarding SCI and CAN.<br>In the "Absolute maximum ratings" table, removed the min value of V <sub>IN</sub> relative to V <sub>DD</sub> .<br>In the "Recommended operating conditions (3.3 V)" table:<br>* T <sub>A</sub> C-Grade Part, T <sub>J</sub> C-Grade Part, T <sub>A</sub> V-Grade Part, T <sub>J</sub> V-Grade Part, T <sub>A</sub> M-Grade Part, T <sub>J</sub> M-Grade Part:<br>added new rows.<br>* TV <sub>DD</sub> : made single row.<br>In the "LQFP thermal characteristics" table, added more rows.<br>Removed "208 MAPBGA thermal characteristics" table.<br>In the "I/Q consumption" table:<br>* Removed I <sub>DVNSEG</sub> row.<br>* Added "I/O weight" table.<br>In the "Voltage regulator electrical characteristics" table:<br>* Updated the values.<br>* Removed I <sub>VREGREF</sub> and I <sub>VREDLVD12</sub> .<br>* Added a note about I <sub>DD_BC</sub> .<br>In the "Low voltage monitor electrical characteristics" table:<br>* Updated V <sub>PORH</sub> values.<br>* Updated V <sub>PORH</sub> values.<br>* Updated V <sub>DONCORL</sub> value.<br>Entirely updated the "Eash power supply DC electrical characteristics" table.<br>In the "Crystal oscillator and resonator connection scheme" figure, relocated a note.<br>In the "Crystal oscillator and resonator conscheme" figure, relocated a note.<br>In the "Crystal oscillator and resonator conscheme" figure, relocated a note.<br>In the "Crystal oscillator and resonator conscheme" figure, relocated a note.<br>In the "Crystal oscillator (32 kHz) electrical characteristics" table:<br>* Removed g <sub>MSXOSC</sub> row.<br>* Inserted values of I <sub>SXOSCEIAS</sub> :<br>Entirely updated the "Fast internal RC oscillator (16 MHz) electrical characteristics" table.<br>In the "Orderable part number summary" table, modified some orderable part number.<br>Updated the "Commercial product code structure" figure.<br>Removed the note about the condition from "Flash read access timing" table<br>Removed the notes that assert the values need to be confirmed before validation<br>Exchanged the order of "LQFP 100-pin configuration" and "LQFP 144-pin configuration"<br>Exchanged the order of "LQFP 100-pin configuration" and "LQFP 144-pin configur |

How to Reach Us: Home Page: nxp.com Web Support: nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must bevalidated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can befound at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C.5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C.Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, AMBA, Arm Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and ÏVision are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. Arm7, Arm9, Arm11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, Mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2017 NXP B.V.

Document Number: MPC5604BC Rev. 14 11/2017