#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | e200z0h                                                      |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 48MHz                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                   |

| Peripherals                | DMA, POR, PWM, WDT                                           |

| Number of I/O              | 79                                                           |

| Program Memory Size        | 384KB (384K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64K x 8                                                      |

| RAM Size                   | 28K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | A/D 28x10b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 100-LQFP                                                     |

| Supplier Device Package    | 100-LQFP (14x14)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5603bf2mll4r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

### 1.1 Document overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device. To ensure a complete understanding of the device functionality, refer also to the device reference manual and errata sheet.

# 1.2 Description

The MPC5604B/C is a family of next generation microcontrollers built on the Power Architecture® embedded category.

The MPC5604B/C family of 32-bit microcontrollers is the latest achievement in integrated automotive application controllers. It belongs to an expanding family of automotive-focused products designed to address the next wave of body electronics applications within the vehicle. The advanced and cost-efficient host processor core of this automotive controller family complies with the Power Architecture embedded category and only implements the VLE (variable-length encoding) APU, providing improved code density. It operates at speeds of up to 64 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

|                                       |       |                       |        |      |                  |                  |                  | De               | evice            |                  |                  |                  |                  |                  |                  |                  |

|---------------------------------------|-------|-----------------------|--------|------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Feature                               |       |                       |        |      | MPC56<br>02CxLL  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  | MPC5604<br>BxMG  |

| CPU                                   |       | e200z0h               |        |      |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

| Execution<br>speed <sup>2</sup>       |       | Static – up to 64 MHz |        |      |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

| Code Flash                            |       |                       | 256 KB |      |                  |                  |                  | 384 KB           |                  |                  |                  |                  | 51               | 2 KB             |                  |                  |

| Data Flash                            |       |                       |        |      |                  |                  |                  | 64 KB (4         | 4 × 16 KE        | 3)               |                  |                  |                  |                  |                  |                  |

| RAM                                   |       | 24 KB                 |        | 32   | KB               | 28 KB 40 KB      |                  |                  |                  | 32 KB            |                  |                  |                  | 48 KB            |                  |                  |

| MPU                                   |       |                       |        |      |                  |                  |                  | 8-0              | entry            |                  |                  |                  |                  | I                |                  |                  |

| ADC (10-bit)                          | 12 ch | 28 ch                 | 36 ch  | 8 ch | 28 ch            | 12 ch            | 28 ch            | 36 ch            | 8 ch             | 28 ch            | 12 ch            | 28 ch            | 36 ch            | 8 ch             | 28 ch            | 36 ch            |

| CTU                                   |       |                       |        |      |                  |                  |                  | ```              | /es              |                  |                  |                  |                  |                  |                  |                  |

| Total timer<br>I/O <sup>3</sup> eMIOS |       |                       |        |      | 28 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit | 56 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit | 56 ch,<br>16-bit | 12 ch,<br>16-bit | 28 ch,<br>16-bit | 56 ch,<br>16-bit |

| • PWM+MC<br>+ IC/OC <sup>4</sup>      | 2 ch  | 5 ch                  | 10 ch  | 2 ch | 5 ch             | 2 ch             | 5 ch             | 10 ch            | 2 ch             | 5 ch             | 2 ch             | 5 ch             | 10 ch            | 2 ch             | 5 ch             | 10 ch            |

### Table 1. MPC5604B/C device comparison<sup>1</sup>

MPC5604B/C Microcontroller Data Sheet, Rev.

14

|                    |         | <del>.</del>                       |                                                                              |                                                              |                               |          | u                      |                  | Pin              | num      | ber      |                         |

|--------------------|---------|------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------|----------|------------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin           | PCR     | Alternate function <sup>1</sup>    | Function                                                                     | Peripheral                                                   | I/O direction <sup>2</sup>    | Pad type | RESET configuration    | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PB[15]             | PCR[31] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[31]<br>E0UC[7]<br>—<br>CS4_0<br>ANX[3]                                  | SIUL<br>eMIOS_0<br><br>DSPI_0<br>ADC                         | I/O<br>I/O<br>—<br>0<br>I     | J        | Tristate               | 42               | 38               | 67       | 89       | L13                     |

| PC[0] <sup>9</sup> | PCR[32] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[32]<br>—<br>TDI<br>—                                                    | SIUL<br>—<br>JTAGC<br>—                                      | I/O<br> <br>                  | М        | Input, weak<br>pull-up | 59               | 59               | 87       | 126      | A8                      |

| PC[1] <sup>9</sup> | PCR[33] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[33]<br>—<br>TDO <sup>10</sup><br>—                                      | SIUL<br>—<br>JTAGC<br>—                                      | I/O<br>  O<br>                | М        | Tristate               | 54               | 54               | 82       | 121      | C9                      |

| PC[2]              | PCR[34] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[34]<br>SCK_1<br>CAN4TX <sup>11</sup><br>—<br>EIRQ[5]                    | SIUL<br>DSPI_1<br>FlexCAN_4<br>—<br>SIUL                     | I/O<br>I/O<br>O<br>I          | М        | Tristate               | 50               | 50               | 78       | 117      | A11                     |

| PC[3]              | PCR[35] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[35]<br>CS0_1<br>MA[0]<br>—<br>CAN1RX<br>CAN4RX <sup>11</sup><br>EIRQ[6] | SIUL<br>DSPI_1<br>ADC<br>—<br>FlexCAN_1<br>FlexCAN_4<br>SIUL | /0<br> /0<br> -<br> <br> <br> | S        | Tristate               | 49               | 49               | 77       | 116      | B11                     |

| PC[4]              | PCR[36] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[36]<br>—<br>—<br>SIN_1<br>CAN3RX <sup>11</sup>                          | SIUL<br>—<br>—<br>DSPI_1<br>FlexCAN_3                        | I/O<br>—<br>—<br>—<br>—<br>—  | М        | Tristate               | 62               | 62               | 92       | 131      | B7                      |

| PC[5]              | PCR[37] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[37]<br>SOUT_1<br>CAN3TX <sup>11</sup><br>—<br>EIRQ[7]                   | SIUL<br>DSPI1<br>FlexCAN_3<br>—<br>SIUL                      | I/O<br>O<br>O<br>I            | М        | Tristate               | 61               | 61               | 91       | 130      | A7                      |

| PC[6]              | PCR[38] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[38]<br>LIN1TX<br>—<br>—                                                 | SIUL<br>LINFlex_1<br>—                                       | I/O<br>O<br>—                 | S        | Tristate               | 16               | 16               | 25       | 36       | R2                      |

### Table 5. Functional port pin descriptions (continued)

|          |         | -                                       |                                                                   |                                                  |                                        |          | u                   |                  | Pin              | num      | ber      |                         |

|----------|---------|-----------------------------------------|-------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|----------|---------------------|------------------|------------------|----------|----------|-------------------------|

| Port pin | PCR     | Alternate function <sup>1</sup>         | Function                                                          | Peripheral                                       | I/O direction <sup>2</sup>             | Pad type | RESET configuration | MPC560xB 64 LQFP | MPC560xC 64 LQFP | 100 LQFP | 144 LQFP | 208 MAPBGA <sup>3</sup> |

| PF[8]    | PCR[88] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[88]<br>CAN3TX <sup>14</sup><br>CS4_0<br>CAN2TX <sup>15</sup> | SIUL<br>FlexCAN_3<br>DSPI_0<br>FlexCAN_2         | 1/0 0 0 0                              | М        | Tristate            |                  |                  |          | 34       | P1                      |

| PF[9]    | PCR[89] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[89]<br>                                                      | SIUL<br><br>DSPI_0<br><br>FlexCAN_2<br>FlexCAN_3 | I/O<br>— O<br>— I<br>— I               | S        | Tristate            | _                |                  |          | 33       | N2                      |

| PF[10]   | PCR[90] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[90]<br>—<br>—<br>—                                           | SIUL<br>—<br>—<br>—                              | I/O<br>  _                             | М        | Tristate            | —                |                  |          | 38       | R3                      |

| PF[11]   | PCR[91] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[91]<br>—<br>—<br>—<br>WKPU[15] <sup>4</sup>                  | SIUL<br>—<br>—<br>—<br>WKPU                      | I/O<br>—<br>—<br>—<br>—                | S        | Tristate            | _                | _                | _        | 39       | R4                      |

| PF[12]   | PCR[92] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[92]<br>E1UC[25]<br>—<br>—                                    | SIUL<br>eMIOS_1<br>—                             | I/O<br>I/O<br>                         | М        | Tristate            | _                | _                |          | 35       | R1                      |

| PF[13]   | PCR[93] | AF0<br>AF1<br>AF2<br>AF3<br>—           | GPIO[93]<br>E1UC[26]<br>—<br>WKPU[16] <sup>4</sup>                | SIUL<br>eMIOS_1<br><br>WKPU                      | I/O<br>I/O<br>I                        | S        | Tristate            | _                | _                |          | 41       | T6                      |

| PF[14]   | PCR[94] | AF0<br>AF1<br>AF2<br>AF3                | GPIO[94]<br>CAN4TX <sup>11</sup><br>E1UC[27]<br>CAN1TX            | SIUL<br>FlexCAN_4<br>eMIOS_1<br>FlexCAN_4        | I/O<br>O<br>I/O<br>O                   | М        | Tristate            |                  | 43               |          | 102      | D14                     |

| PF[15]   | PCR[95] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—<br>— | GPIO[95]<br>—<br>—<br>CAN1RX<br>CAN4RX <sup>11</sup><br>EIRQ[13]  | SIUL<br>—<br>—<br>FlexCAN_1<br>FlexCAN_4<br>SIUL | I/O<br>—<br>—<br>—<br>—<br>—<br>—<br>— | S        | Tristate            | _                | 42               |          | 101      | E15                     |

### Table 5. Functional port pin descriptions (continued)

### 2.13 Recommended operating conditions

Table 12. Recommended operating conditions (3.3 V)

| Symbol                           |    | Parameter                                                                                        | Conditions                   | Va                   | lue                  | Unit |

|----------------------------------|----|--------------------------------------------------------------------------------------------------|------------------------------|----------------------|----------------------|------|

| Symbol                           |    | Falameter                                                                                        | Conditions                   | Min                  | Max                  | Unit |

| V <sub>SS</sub>                  | SR | Digital ground on VSS_HV pins                                                                    | —                            | 0                    | 0                    | V    |

| V <sub>DD</sub> <sup>1</sup>     | SR | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                                 | —                            | 3.0                  | 3.6                  | V    |

| V <sub>SS_LV</sub> <sup>2</sup>  | SR | Voltage on VSS_LV (low voltage digital supply)<br>pins with respect to ground (V <sub>SS</sub> ) |                              | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_BV</sub> <sup>3</sup>  | SR |                                                                                                  | —                            | 3.0                  | 3.6                  | V    |

|                                  |    | respect to ground (V <sub>SS</sub> )                                                             | Relative to $V_{\text{DD}}$  | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |

| V <sub>SS_ADC</sub>              | SR | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> )              | —                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> +0.1 | V    |

| V <sub>DD_ADC</sub> <sup>4</sup> | SR | Voltage on VDD_HV_ADC pin (ADC reference)                                                        | —                            | 3.0 <sup>5</sup>     | 3.6                  | V    |

|                                  |    | with respect to ground (V <sub>SS</sub> )                                                        | Relative to $V_{\text{DD}}$  | V <sub>DD</sub> -0.1 | V <sub>DD</sub> +0.1 |      |

| V <sub>IN</sub>                  | SR | <b>o j i i o</b>                                                                                 | —                            | V <sub>SS</sub> -0.1 | —                    | V    |

|                                  |    | (V <sub>SS</sub> )                                                                               | Relative to $V_{\text{DD}}$  |                      | V <sub>DD</sub> +0.1 |      |

| I <sub>INJPAD</sub>              | SR | Injected input current on any pin during overload condition                                      | —                            | -5                   | 5                    | mA   |

| IINJSUM                          | SR | Absolute sum of all injected input currents during overload condition                            | —                            | -50                  | 50                   |      |

| TV <sub>DD</sub>                 | SR | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                                    | —                            | 3.0 <sup>7</sup>     | 0.25[V/µs]<br>)      | V/s  |

| TA C-Grade Part                  | SR | Ambient temperature under bias                                                                   | $f_{CPU} \le 64 \text{ MHz}$ | -40                  | 85                   | °C   |

| T <sub>J C-Grade Part</sub>      | SR | Junction temperature under bias                                                                  |                              | -40                  | 110                  |      |

| TA V-Grade Part                  | SR | Ambient temperature under bias                                                                   |                              | -40                  | 105                  |      |

| T <sub>J V-Grade Part</sub>      | SR | Junction temperature under bias                                                                  |                              | -40                  | 130                  |      |

| TA M-Grade Part                  | SR | Ambient temperature under bias                                                                   |                              | -40                  | 125                  |      |

| T <sub>J M-Grade Part</sub>      | SR | Junction temperature under bias                                                                  |                              | -40                  | 150                  |      |

$^1\,$  100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair

$^2$  330 nF capacitance needs to be provided between each  $V_{\text{DD}\_LV}/V_{\text{SS}\_LV}$  supply pair.

<sup>3</sup> 400 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics).

$^4\,$  100 nF capacitance needs to be provided between V\_DD\_ADC/V\_SS\_ADC pair.

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

<sup>6</sup> Guaranteed by device validation.

$^7\,$  Minimum value of TV\_{DD} must be guaranteed until V\_{DD} reaches 2.6 V (maximum value of V\_{PORH}).

| Sym                | nbol | С | Parameter                                         | Conditions <sup>2</sup> | Pin count | Value | Unit |

|--------------------|------|---|---------------------------------------------------|-------------------------|-----------|-------|------|

| $\Psi_{\text{JC}}$ | CC   | D | Junction-to-case thermal                          | Single-layer board - 1s | 64        | TBD   | °C/W |

|                    |      |   | characterization parameter,<br>natural convection |                         | 100       | 9     |      |

|                    |      |   |                                                   |                         | 144       | 10    |      |

|                    |      |   |                                                   | Four-layer board - 2s2p | 64        | TBD   |      |

|                    |      |   |                                                   |                         | 100       | 9     |      |

|                    |      |   |                                                   |                         | 144       | 10    |      |

Table 14. LQFP thermal characteristics<sup>1</sup> (continued)

<sup>1</sup> Thermal characteristics are based on simulation.

$^2~V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C

<sup>3</sup> Junction-to-ambient thermal resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>4</sup> Junction-to-board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

<sup>5</sup> Junction-to-case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

### 2.14.2 Power considerations

The average chip-junction temperature, T<sub>I</sub>, in degrees Celsius, may be calculated using Equation 1:

$$T_{J} = T_{A} + (P_{D} \times R_{\theta JA})$$

Eqn. 7

Where:

$T_A$  is the ambient temperature in °C.

$R_{\theta JA}$  is the package junction-to-ambient thermal resistance, in °C/W.

$P_D$  is the sum of  $P_{INT}$  and  $P_{I/O} (P_D = P_{INT} + P_{I/O})$ .

P<sub>INT</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in watts. This is the chip internal power.

$P_{I/O}$  represents the power dissipation on input and output pins; user determined.

Most of the time for the applications,  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant, if the device is configured to continuously drive external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$P_{\rm D} = K / (T_{\rm J} + 273 \,^{\circ}{\rm C})$$

Eqn. 2

Therefore, solving equations 1 and 2:

$$K = P_D x (T_A + 273 °C) + R_{\theta JA} x P_D^2$$

Eqn. 3

Where:

MPC5604B/C Microcontroller Data Sheet, Rev. 14

### Package pinouts and signal descriptions

| Course              | - 1 | ~ | Deveneter                                         | Conditions1                                                                                |                    | Value |                     | 1.1 |

|---------------------|-----|---|---------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------|-------|---------------------|-----|

| Symbo               | OI  | С | Parameter                                         | Conditions <sup>1</sup>                                                                    | Min                | Тур   | Мах                 | Uni |

| V <sub>IL</sub>     | SR  | Ρ | Input low Level CMOS<br>(Schmitt Trigger)         | _                                                                                          | -0.4               | —     | 0.35V <sub>DD</sub> | V   |

| V <sub>HYS</sub>    | СС  | С | Input hysteresis CMOS<br>(Schmitt Trigger)        | _                                                                                          | 0.1V <sub>DD</sub> | _     | -                   | V   |

| V <sub>OL</sub>     | СС  | Ρ | Output low level                                  | Push Pull, $I_{OL} = 2mA$ ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | —                  | _     | 0.1V <sub>DD</sub>  | V   |

|                     |     | С |                                                   | Push Pull, $I_{OL}$ = 1mA,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>      | —                  | —     | 0.1V <sub>DD</sub>  |     |

|                     |     | С |                                                   | Push Pull, $I_{OL} = 1mA$ ,<br>$V_{DD} = 3.3 V \pm 10\%$ , PAD3V5V = 1<br>(recommended)    | _                  | _     | 0.5                 |     |

| t <sub>tr</sub>     | СС  | D | Output transition time<br>output pin <sup>3</sup> | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                       | —                  | _     | 10                  | ns  |

|                     |     |   |                                                   | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                       | —                  | _     | 20                  |     |

|                     |     |   |                                                   | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0                      | —                  |       | 40                  |     |

|                     |     |   |                                                   | C <sub>L</sub> = 25pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                       | —                  | _     | 12                  |     |

|                     |     |   |                                                   | C <sub>L</sub> = 50pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                       | —                  | _     | 25                  |     |

|                     |     |   |                                                   | C <sub>L</sub> = 100pF,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                      | —                  | —     | 40                  | -   |

| W <sub>FRST</sub>   | SR  | Ρ | RESET input filtered pulse                        | _                                                                                          | —                  | _     | 40                  | ns  |

| W <sub>NFRST</sub>  | SR  | Ρ | RESET input not filtered pulse                    | _                                                                                          | 1000               | —     | -                   | ns  |

| ll <sub>WPU</sub> l | СС  | Ρ | Weak pull-up current                              | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1                                                 | 10                 | —     | 150                 | μA  |

|                     |     | D | absolute value                                    | $V_{DD} = 5.0 V \pm 10\%$ , PAD3V5V = 0                                                    | 10                 |       | 150                 |     |

|                     |     | Ρ |                                                   | $V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ PAD3V5V} = 1^2$                                   | 10                 | _     | 250                 |     |

<sup>1</sup>  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C, unless otherwise specified <sup>2</sup> This transient configuration does not occurs when device is used in the  $V_{DD} = 3.3 \text{ V} \pm 10\%$  range. <sup>3</sup>  $C_L$  includes device and package capacitance ( $C_{PKG} < 5 \text{ pF}$ ).

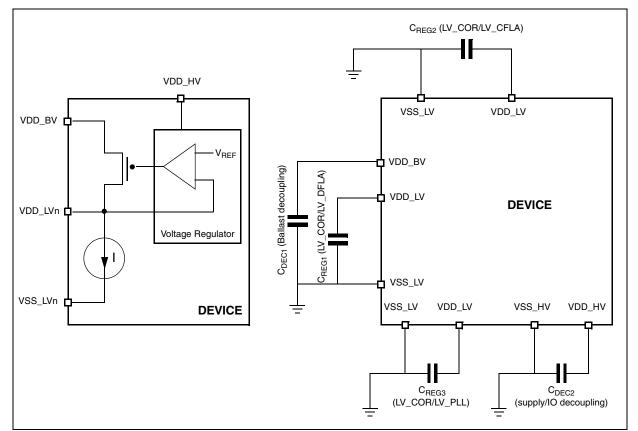

Figure 10. Voltage regulator capacitance connection

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

Each decoupling capacitor must be placed between each of the three  $V_{DD_LV}/V_{SS_LV}$  supply pairs to ensure stable voltage (see 2.13, Recommended operating conditions).

The internal voltage regulator requires a controlled slew rate of both  $V_{DD_{HV}}$  and  $V_{DD_{BV}}$  as described in Figure 11.

#### Package pinouts and signal descriptions

| Symbo     | 4  | с | Parameter                                                                   | Conditions                               |         | Value   |     | Unit   |

|-----------|----|---|-----------------------------------------------------------------------------|------------------------------------------|---------|---------|-----|--------|

| Gymbe     |    | Ŭ | rarameter                                                                   | Conditions                               | Min     | Тур     | Max | Onic   |

| P/E       | СС |   | Number of program/erase cycles                                              | 16 KB blocks                             | 100,000 | —       | —   | cycles |

|           |    |   | per block over the operating temperature range (T <sub>.1</sub> )           | 32 KB blocks                             | 10,000  | 100,000 | _   |        |

|           |    |   |                                                                             | 128 KB blocks                            | 1,000   | 100,000 | _   |        |

| Retention | СС |   | Minimum data retention at 85 °C<br>average ambient temperature <sup>1</sup> | Blocks with<br>0–1,000 P/E cycles        | 20      | —       | _   | years  |

|           |    |   |                                                                             | Blocks with<br>1,001–10,000 P/E cycles   | 10      | —       | _   |        |

|           |    |   |                                                                             | Blocks with<br>10,001–100,000 P/E cycles | 5       | —       | —   |        |

Table 29. Flash module life

<sup>1</sup> Ambient temperature averaged over duration of application, not to exceed recommended product operating temperature range.

ECC circuitry provides correction of single bit faults and is used to improve further automotive reliability results. Some units will experience single bit corrections throughout the life of the product with no impact to product reliability.

Table 30. Flash read access timing

| Symb              | ool | С | Parameter                           | Conditions <sup>1</sup> | Max | Unit |

|-------------------|-----|---|-------------------------------------|-------------------------|-----|------|

| f <sub>READ</sub> | CC  | Ρ | Maximum frequency for Flash reading | 2 wait states           | 64  | MHz  |

|                   |     | С |                                     | 1 wait state            | 40  |      |

|                   |     | С |                                     | 0 wait states           | 20  |      |

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified

### 2.19.2 Flash power supply DC characteristics

Table 31 shows the power supply DC characteristics on external supply.

### Table 31. Flash memory power supply DC electrical characteristics

| Symbo                           | Symbol |   | Parameter                                                          | Conditions <sup>1</sup>                                                 |  |     | Unit |     |

|---------------------------------|--------|---|--------------------------------------------------------------------|-------------------------------------------------------------------------|--|-----|------|-----|

| Cymb                            | 01     | С |                                                                    |                                                                         |  | Тур | Max  | onn |

| I <sub>FREAD</sub> <sup>2</sup> | СС     | D | Sum of the current consumption on VDD_HV and VDD_BV on read access | Code flash memory module read $f_{CPU} = 64 \text{ MHz}^3$              |  | 15  | 33   | mA  |

|                                 |        |   |                                                                    | Data flash memory module read<br>f <sub>CPU</sub> = 64 MHz <sup>3</sup> |  | 15  | 33   |     |

Package pinouts and signal descriptions

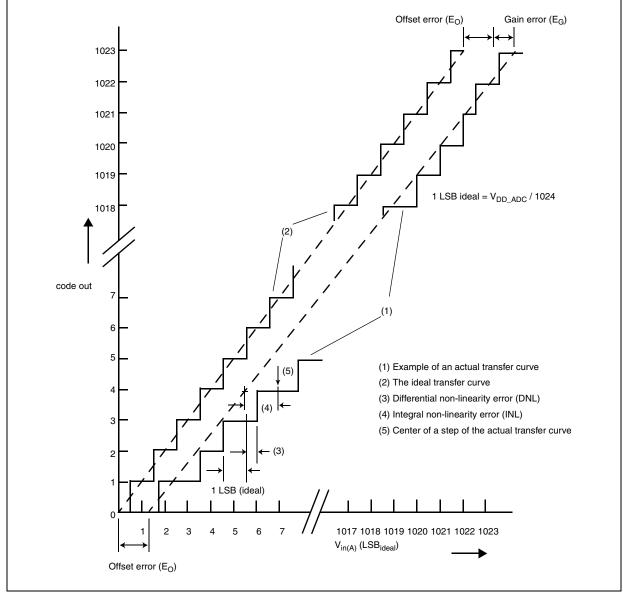

# 2.26 ADC electrical characteristics

### 2.26.1 Introduction

The device provides a 10-bit Successive Approximation Register (SAR) analog-to-digital converter.

Figure 19. ADC characteristic and error definitions

### 2.26.2 Input impedance and ADC accuracy

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can

# 2.26.3 ADC electrical characteristics

| Sym              | bol  | 0 | Parameter             |                         | Conditions                           |     | Value |     | Unit |

|------------------|------|---|-----------------------|-------------------------|--------------------------------------|-----|-------|-----|------|

| J                | 1001 | Ŭ | i arameter            |                         | Conditions                           | Min | Тур   | Мах | onne |

| I <sub>LKG</sub> | СС   | D | Input leakage current | $T_A = -40 \ ^\circ C$  | No current injection on adjacent pin |     | 1     | 70  | nA   |

|                  |      | D |                       | T <sub>A</sub> = 25 °C  |                                      |     | 1     | 70  |      |

|                  |      | D |                       | T <sub>A</sub> = 85 °C  |                                      |     | 3     | 100 |      |

|                  |      | D |                       | T <sub>A</sub> = 105 °C |                                      |     | 8     | 200 |      |

|                  |      | Ρ |                       | T <sub>A</sub> = 125 °C |                                      | _   | 45    | 400 |      |

### Table 43. ADC input leakage current

### Table 44. ADC conversion characteristics

| Symbol              |    | С | Devenator                                                                                                    | Conditions <sup>1</sup>                 | Value                    |     |                          |      |

|---------------------|----|---|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------|-----|--------------------------|------|

|                     |    | C | Parameter                                                                                                    | Conditions                              | Min                      | Тур | Max                      | Unit |

| V <sub>SS_ADC</sub> | SR | _ | Voltage on<br>VSS_HV_ADC (ADC<br>reference) pin with<br>respect to ground<br>(V <sub>SS</sub> ) <sup>2</sup> | _                                       | -0.1                     |     | 0.1                      | V    |

| V <sub>DD_ADC</sub> | SR |   | Voltage on<br>VDD_HV_ADC pin<br>(ADC reference) with<br>respect to ground<br>(V <sub>SS</sub> )              | _                                       | V <sub>DD</sub> -0.1     | _   | V <sub>DD</sub> +0.1     | V    |

| V <sub>AINx</sub>   | SR | — | Analog input voltage <sup>3</sup>                                                                            | —                                       | V <sub>SS_ADC</sub> -0.1 | _   | V <sub>DD_ADC</sub> +0.1 | V    |

| f <sub>ADC</sub>    | SR | — | ADC analog frequency                                                                                         | —                                       | 6                        |     | 32 + 4%                  | MHz  |

| $\Delta_{ADC_SYS}$  | SR | _ | ADC digital clock duty cycle (ipg_clk)                                                                       | ADCLKSEL = 1 <sup>4</sup>               | 45                       |     | 55                       | %    |

| IADCPWD             | SR | — | ADC0 consumption in power down mode                                                                          | _                                       | _                        |     | 50                       | μA   |

| IADCRUN             | SR | — | ADC0 consumption in running mode                                                                             | _                                       | _                        | _   | 4                        | mA   |

| t <sub>ADC_PU</sub> | SR | — | ADC power up delay                                                                                           | _                                       | —                        | _   | 1.5                      | μs   |

| t <sub>s</sub>      | СС | Т | Sampling time <sup>5</sup>                                                                                   | f <sub>ADC</sub> = 32 MHz, INPSAMP = 17 | 0.5                      | _   |                          | μs   |

|                     |    |   |                                                                                                              | f <sub>ADC</sub> = 6 MHz, INPSAMP = 255 | —                        |     | 42                       |      |

| t <sub>c</sub>      | СС | Ρ | Conversion time <sup>6</sup>                                                                                 | f <sub>ADC</sub> = 32 MHz, INPCMP = 2   | 0.625                    |     |                          | μs   |

| C <sub>S</sub>      | СС | D | ADC input sampling capacitance                                                                               | _                                       | _                        | —   | 3                        | pF   |

| C <sub>P1</sub>     | СС | D | ADC input pin<br>capacitance 1                                                                               | _                                       |                          |     | 3                        | pF   |

| C <sub>P2</sub>     | СС | D | ADC input pin<br>capacitance 2                                                                               | _                                       | _                        | —   | 1                        | pF   |

#### Package pinouts and signal descriptions

- <sup>3</sup> Maximum value is reached when CSn pad is configured as MEDIUM pad while SCK pad is configured as SLOW. A positive value means that CSn is deasserted before SCK. DSPI0 and DSPI1 have only MEDIUM SCK available.

- <sup>4</sup> The t<sub>CSC</sub> delay value is configurable through a register. When configuring t<sub>CSC</sub> (using PCSSCK and CSSCK fields in DSPI\_CTARx registers), delay between internal CS and internal SCK must be higher than Δt<sub>CSC</sub> to ensure positive t<sub>CSCext</sub>.

- <sup>5</sup> The  $t_{ASC}$  delay value is configurable through a register. When configuring  $t_{ASC}$  (using PASC and ASC fields in DSPI\_CTARx registers), delay between internal CS and internal SCK must be higher than  $\Delta t_{ASC}$  to ensure positive  $t_{ASCext}$ .

- <sup>6</sup> This delay value corresponds to SMPL\_PT = 00b which is bit field 9 and 8 of the DSPI\_MCR.

- <sup>7</sup> SCK and SOUT configured as MEDIUM pad

# 2.27.3 Nexus characteristics

| No. | Symbol             |    | с | Parameter                     |     | Value |     |      |

|-----|--------------------|----|---|-------------------------------|-----|-------|-----|------|

| NO. |                    |    | C | Parameter                     | Min | Тур   | Max | Unit |

| 1   | t <sub>TCYC</sub>  | CC | D | TCK cycle time                | 64  | —     | —   | ns   |

| 2   | t <sub>MCYC</sub>  | CC | D | MCKO cycle time               | 32  | —     | _   | ns   |

| 3   | t <sub>MDOV</sub>  | CC | D | MCKO low to MDO data valid    | —   | —     | 8   | ns   |

| 4   | t <sub>MSEOV</sub> | CC | D | MCKO low to MSEO_b data valid | —   | —     | 8   | ns   |

| 5   | t <sub>EVTOV</sub> | CC | D | MCKO low to EVTO data valid   | —   | —     | 8   | ns   |

| 10  | t <sub>NTDIS</sub> | CC | D | TDI data setup time           | 15  | —     | —   | ns   |

|     | t <sub>NTMSS</sub> | CC | D | TMS data setup time           | 15  | —     | —   | ns   |

| 11  | t <sub>NTDIH</sub> | CC | D | TDI data hold time            | 5   | —     | —   | ns   |

|     | t <sub>NTMSH</sub> | CC | D | TMS data hold time            | 5   | —     | —   | ns   |

| 12  | t <sub>TDOV</sub>  | CC | D | TCK low to TDO data valid     | 35  | —     | —   | ns   |

| 13  | t <sub>TDOI</sub>  | CC | D | TCK low to TDO data invalid   | 6   | —     | —   | ns   |

| Table 47. | Nexus | characteristics |

|-----------|-------|-----------------|

|-----------|-------|-----------------|

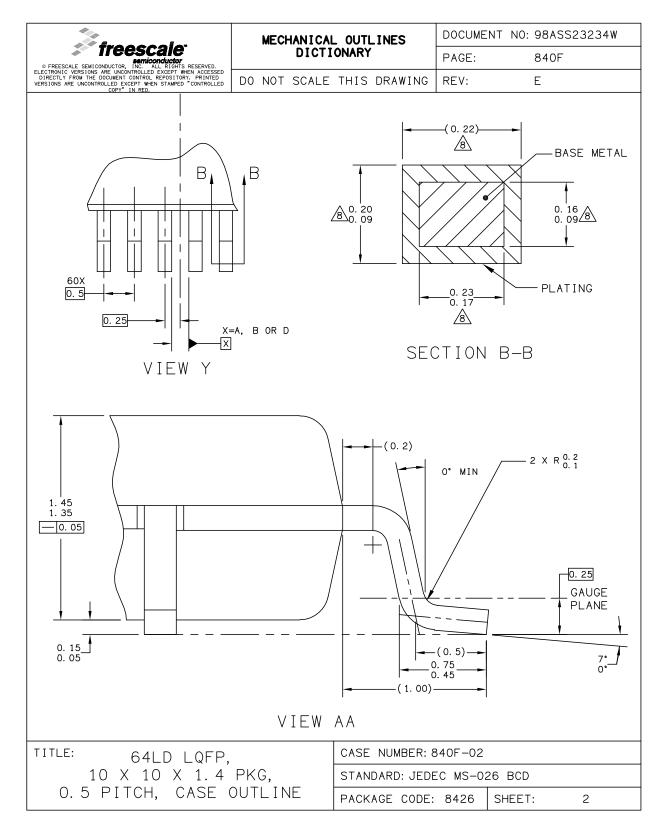

Package characteristics

Figure 36. 64 LQFP package mechanical drawing (2 of 3)

MPC5604B/C Microcontroller Data Sheet, Rev. 14

Package characteristics

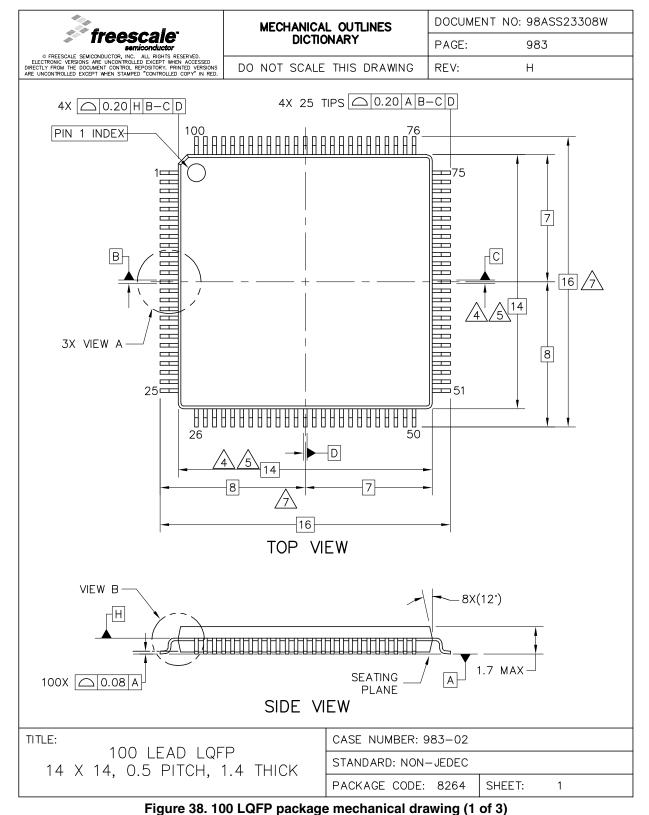

# 3.1.2 100 LQFP

igure 30. Too Lair Package mechanical drawing (1 of a

MPC5604B/C Microcontroller Data Sheet, Rev. 14

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5        | 02-Nov-2009 | <ul> <li>In the "MPC5604B/C series block summary" table, added a new row.</li> <li>In the "Absolute maximum ratings" table, changed max value of V<sub>DD_BV</sub>, V<sub>DD_ADC</sub>, and V<sub>IN</sub>.</li> <li>In the "Recommended operating conditions (3.3 V)" table, deleted min value of TV<sub>DD</sub>.</li> <li>In the "Recommended operating conditions (3.3 V)" table, deleted min value of TV<sub>DD</sub>.</li> <li>In the "Reset electrical characteristics" table, changed footnotes 3 and 5.</li> <li>In the "Voltage regulator electrical characteristics" table:</li> <li>C<sub>REGn</sub>: changed max value.</li> <li>C<sub>DEC1</sub>: split into 2 rows.</li> <li>Updated voltage values in footnote 4</li> <li>In the "Low voltage monitor electrical characteristics" table:</li> <li>Updated column Conditions.</li> <li>V<sub>LVDLVCORL</sub>, V<sub>LVDLVBKPL</sub>: changed min/max value.</li> <li>In the "Program and erase specifications" table, added initial max value of T<sub>dwprogram</sub>.</li> <li>In the "Flash module life" table, changed min value for blocks with 100K P/E cycles</li> <li>In the "Flash power supply DC electrical characteristics" table:</li> <li>IFREAD, IFMOD: added typ value.</li> <li>Added footnote 1.</li> <li>Added footnote 1.</li> <li>Added "NVUSRO[WATCHDOG_EN] field description" section.</li> <li>Section 4.18: "ADC electrical characteristics" has been moved up in hierarchy (it was Section 4.18.5).</li> <li>In the "ADC conversion characteristics" table, changed initial max value of R<sub>AD</sub>.</li> <li>In the "On-chip peripherals current consumption" table:</li> <li>Removed min/max from the heading.</li> <li>Changed unit of measurement and consequently rounded the values.</li> </ul> |

### Table 49. Revision history (continued)

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 15-Mar-2010 | In the "Introduction" section, relocated a note.<br>In the "MPC5604B/C device comparison" table, added footnote regarding SCI and CAN.<br>In the "Absolute maximum ratings" table, removed the min value of V <sub>IN</sub> relative to V <sub>DD</sub> .<br>In the "Recommended operating conditions (3.3 V)" table:<br>* T <sub>A</sub> C-Grade Part, T <sub>J</sub> C-Grade Part, T <sub>A</sub> V-Grade Part, T <sub>J</sub> V-Grade Part, T <sub>A</sub> M-Grade Part, T <sub>J</sub> M-Grade Part:<br>added new rows.<br>* TV <sub>DD</sub> : made single row.<br>In the "LQFP thermal characteristics" table, added more rows.<br>Removed "208 MAPBGA thermal characteristics" table.<br>In the "I/Q consumption" table:<br>* Removed I <sub>DVNSEG</sub> row.<br>* Added "I/O weight" table.<br>In the "Voltage regulator electrical characteristics" table:<br>* Updated the values.<br>* Removed I <sub>VREGREF</sub> and I <sub>VREDLVD12</sub> .<br>* Added a note about I <sub>DD_BC</sub> .<br>In the "Low voltage monitor electrical characteristics" table:<br>* Updated V <sub>PORH</sub> values.<br>* Updated V <sub>PORH</sub> values.<br>* Updated V <sub>DONCORL</sub> value.<br>Entirely updated the "Eash power supply DC electrical characteristics" table.<br>In the "Crystal oscillator and resonator connection scheme" figure, relocated a note.<br>In the "Crystal oscillator and resonator conscheme" figure, relocated a note.<br>In the "Crystal oscillator and resonator conscheme" figure, relocated a note.<br>In the "Crystal oscillator and resonator conscheme" figure, relocated a note.<br>In the "Crystal oscillator (32 kHz) electrical characteristics" table:<br>* Removed g <sub>MSXOSC</sub> row.<br>* Inserted values of I <sub>SXOSCEIAS</sub> :<br>Entirely updated the "Fast internal RC oscillator (16 MHz) electrical characteristics" table.<br>In the "Orderable part number summary" table, modified some orderable part number.<br>Updated the "Commercial product code structure" figure.<br>Removed the note about the condition from "Flash read access timing" table<br>Removed the notes that assert the values need to be confirmed before validation<br>Exchanged the order of "LQFP 100-pin configuration" and "LQFP 144-pin configuration"<br>Exchanged the order of "LQFP 100-pin configuration" and "LQFP 144-pin configur |

| Revision | Date         | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9        | 16 June 2011 | Formatting and minor editorial changes throughout                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |              | Harmonized oscillator nomenclature                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |              | Removed all instances of note "All 64 LQFP information is indicative and must be                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |              | confirmed during silicon validation."                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |              | Device comparison table: changed temperature value in footnote 2 from 105 °C to 125 °C MPC560xB LQFP 64-pin configuration and MPC560xC LQFP 64-pin configuration: renamed pin 6 from VPP_TEST to VSS_HV                                                                                                                                                                                                                                                                          |

|          |              | Removed "Pin Muxing" section; added sections "Pad configuration during reset phases",<br>"Voltage supply pins", "Pad types", "System pins," "Functional ports", and "Nexus 2+<br>pins"                                                                                                                                                                                                                                                                                           |

|          |              | Section "NVUSRO register": edited content to separate configuration into electrical<br>parameters and digital functionality; updated footnote describing default value of '1' in<br>field descriptions NVUSRO[PAD3V5V] and NVUSRO[OSCILLATOR_MARGIN]                                                                                                                                                                                                                             |

|          |              | Added section "NVUSRO[WATCHDOG_EN] field description"                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |              | Recommended operating conditions (3.3 V) and Recommended operating conditions (5.0 V): updated conditions for ambient and junction temperature characteristics I/O input DC electrical characteristics: updated I <sub>LKG</sub> characteristics                                                                                                                                                                                                                                 |

|          |              | Section "I/O pad current specification": removed content referencing the I <sub>DYNSEG</sub><br>maximum value                                                                                                                                                                                                                                                                                                                                                                    |

|          |              | I/O consumption: replaced instances of "Root medium square" with "Root mean square"                                                                                                                                                                                                                                                                                                                                                                                              |

|          |              | I/O weight: replaced instances of bit "SRE" with "SRC"; added pads PH[9] and PH[10];<br>added supply segments; removed weight values in 64-pin LQFP for pads that do not<br>exist in that package                                                                                                                                                                                                                                                                                |

|          |              | Reset electrical characteristics: updated parameter classification for II <sub>WPU</sub> I<br>Updated Voltage regulator electrical characteristics                                                                                                                                                                                                                                                                                                                               |

|          |              | Section "Low voltage detector electrical characteristics": changed title (was "Voltage monitor electrical characteristics"); added event status flag names found in RGM chapter of device reference manual to POR module and LVD descriptions; replaced instances of "Low voltage monitor" with "Low voltage detector"; updated values for V <sub>LVDLVBKPL</sub> and V <sub>LVDLVCORL</sub> ; replaced "LVD_DIGBKP" with "LVDLVBKP" in note Updated section "Power consumption" |

|          |              | Fast external crystal oscillator (4 to 16 MHz) electrical characteristics: updated parameter<br>classification for V <sub>FXOSCOP</sub>                                                                                                                                                                                                                                                                                                                                          |

|          |              | Crystal oscillator and resonator connection scheme: added footnote about possibility of<br>adding a series resistor                                                                                                                                                                                                                                                                                                                                                              |

|          |              | Slow external crystal oscillator (32 kHz) electrical characteristics: updated footnote 1                                                                                                                                                                                                                                                                                                                                                                                         |

|          |              | FMPLL electrical characteristics: added short term jitter characteristics; inserted "" in<br>empty min value cell of t <sub>lock</sub> row                                                                                                                                                                                                                                                                                                                                       |

|          |              | Section "Input impedance and ADC accuracy": changed "V <sub>A</sub> /V <sub>A2</sub> " to "V <sub>A2</sub> /V <sub>A</sub> " in Equation 11                                                                                                                                                                                                                                                                                                                                      |

|          |              | ADC input leakage current: updated ILKG characteristics                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |              | ADC conversion characteristics: updated symbols                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |              | On-chip peripherals current consumption: changed "supply current on "V <sub>DD_HV_ADC</sub> " to<br>"supply current on" V <sub>DD_HV</sub> " in I <sub>DD_HV(FLASH)</sub> row; updated I <sub>DD_HV(PLL)</sub> value—was<br>3 * f <sub>periph</sub> , is 30 * f <sub>periph</sub> ; updated footnotes<br>DSPI deprocedurations added rows t                                                                                                                                      |

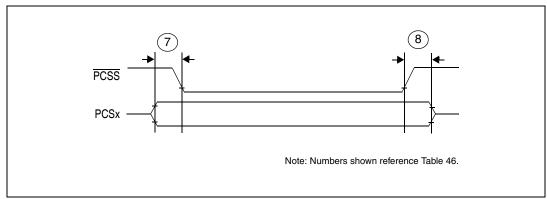

|          |              | DSPI characteristics: added rows t <sub>PCSC</sub> and t <sub>PASC</sub><br>Added DSPI PCS strobe (PCSS) timing diagram                                                                                                                                                                                                                                                                                                                                                          |

| Revision | Date        | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13       | 19 Jan 2015 | <ul> <li>In Table 1 (MPC5604B/C device comparison):</li> <li>changed the MPC5604BxLH entry for CAN (FlexCAN) from 3<sup>7</sup> to 2<sup>6</sup>.</li> <li>updated tablenote 7.</li> <li>In Table 13 (Recommended operating conditions (5.0 V)), updated tablenote 5 to: "1 μF (electrolithic/tantalum) + 47 nF (ceramic) capacitance needs to be provided between V<sub>DD_ADC</sub>/V<sub>SS_ADC</sub> pair. Another ceramic cap of 10nF with low inductance package can be added".</li> <li>In Section 2.17.2, "Low voltage detector electrical characteristics, added a note on LVHVD5 detector.</li> <li>In Section 4, "Ordering information, added a note: "Not all options are available on all devices".</li> </ul> |

| 14       | 30 oct 2017 | In Table 1 (MPC5604B/C device comparison) for MPC56 04BxLH changed the CAN from 2 to 3.<br>In Table 12 (Recommended operating conditions (3.3 V)) added Min value for $TV_{DD}$<br>In Table 13 (Recommended operating conditions (5.0 V)) added Min value for $TV_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Table 49. Revisio | n history | (continued) |

|-------------------|-----------|-------------|

|-------------------|-----------|-------------|

Abbreviations

# **Appendix A Abbreviations**

Table A-1 lists abbreviations used but not defined elsewhere in this document.

Table A-1. Abbreviations

| Abbreviation | Meaning                                 |

|--------------|-----------------------------------------|

| CMOS         | Complementary metal-oxide-semiconductor |

| СРНА         | Clock phase                             |

| CPOL         | Clock polarity                          |

| CS           | Peripheral chip select                  |

| EVTO         | Event out                               |

| МСКО         | Message clock out                       |

| MDO          | Message data out                        |

| MSEO         | Message start/end out                   |

| MTFE         | Modified timing format enable           |

| SCK          | Serial communications clock             |

| SOUT         | Serial data out                         |

| TBD          | To be defined                           |

| ТСК          | Test clock input                        |

| TDI          | Test data input                         |

| TDO          | Test data output                        |

| TMS          | Test mode select                        |

How to Reach Us: Home Page: nxp.com Web Support: nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must bevalidated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can befound at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C.5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C.Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, AMBA, Arm Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and ÏVision are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. Arm7, Arm9, Arm11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, Mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2017 NXP B.V.

Document Number: MPC5604BC Rev. 14 11/2017