# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 38                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-QFN-EP (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac16cfde |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.6 **FLASH Registers and Control Bits**

The FLASH module has nine 8-bit registers in the high-page register space, three locations in the nonvolatile register space in FLASH memory which are copied into three corresponding high-page control registers at reset. There is also an 8-byte comparison key in FLASH memory. Refer to Table 4-3 and Table 4-4 for the absolute address assignments for all FLASH registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

### 4.6.1 FLASH Clock Divider Register (FCDIV)

Bit 7 of this register is a read-only status flag. Bits 6 through 0 may be read at any time but can be written only one time. Before any erase or programming operations are possible, write to this register to set the frequency of the clock for the nonvolatile memory system within acceptable limits.

|       | 7     | 6                           | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-------|-------|-----------------------------|------|------|------|------|------|------|--|

| R     | DIVLD |                             |      |      |      |      |      | DIV0 |  |

| w     |       | PRDIV8                      | DIV5 | DIV4 | DIV3 | DIV2 | DIV1 |      |  |

| Reset | 0     | 0                           | 0    | 0    | 0    | 0    | 0    | 0    |  |

|       |       | = Unimplemented or Reserved |      |      |      |      |      |      |  |

Figure 4-5. FLASH Clock Divider Register (FCDIV)

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DIVLD      | <ul> <li>Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.</li> <li>0 FCDIV has not been written since reset; erase and program operations disabled for FLASH.</li> <li>1 FCDIV has been written since reset; erase and program operations enabled for FLASH.</li> </ul>                                                                                                                                                      |

| 6<br>PRDIV8     | <ul> <li>Prescale (Divide) FLASH Clock by 8</li> <li>O Clock input to the FLASH clock divider is the bus rate clock.</li> <li>1 Clock input to the FLASH clock divider is the bus rate clock divided by 8.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5:0<br>DIV[5:0] | <b>Divisor for FLASH Clock Divider</b> — The FLASH clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV5:DIV0 field plus one. The resulting frequency of the internal FLASH clock must fall within the range of 200 kHz to 150 kHz for proper FLASH operations. Program/Erase timing pulses are one cycle of this internal FLASH clock which corresponds to a range of 5 $\mu$ s to 6.7 $\mu$ s. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1, Equation 4-2, and Table 4-6. |

#### Table 4-6. FCDIV Register Field Descriptions

### if PRDIV8 = 0 — $f_{FCLK} = f_{Bus} \div ([DIV5:DIV0] + 1)$ Eqn. 4-1

if PRDIV8 = 1 —

$$f_{FCLK} = f_{Bus} \div (8 \times ([DIV5:DIV0] + 1))$$

Eqn. 4-2

Table 4-7 shows the appropriate values for PRDIV8 and DIV5:DIV0 for selected bus frequencies.

# Chapter 5 Resets, Interrupts, and System Configuration

# 5.1 Introduction

This chapter discusses basic reset and interrupt mechanisms and the various sources of reset and interrupts in the MC9S08AC16 Series. Some interrupt sources from peripheral modules are discussed in greater detail within other chapters of this data manual. This chapter gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer operating properly (COP) watchdog and real-time interrupt (RTI), are not part of on-chip peripheral systems with their own sections but are part of the system control logic.

# 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation:

- Power-on detection (POR)

- Low voltage detection (LVD) with enable

- External RESET pin

- COP watchdog with enable and two timeout choices

- Illegal opcode

- Illegal address

- Serial command from a background debug host

- Reset status register (SRS) to indicate source of most recent reset

- Separate interrupt vectors for each module (reduces polling overhead) (see Table 5-11)

### 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is loaded from the reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose high-impedance inputs with pullup devices disabled. The I bit in the condition code register (CCR) is set to block maskable interrupts so the user program has a chance to initialize the stack pointer (SP) and system control settings. SP is forced to 0x00FF at reset.

The following sources of reset are available on the MC9S08AC16 Series:

- Power-on reset (POR)

- Low-voltage detect (LVD)

# Chapter 6 Parallel Input/Output

# 6.1 Introduction

This chapter explains software controls related to parallel input/output (I/O). The MC9S08AC16 has seven I/O ports which include a total of 38 general-purpose I/O pins. See Chapter 2, "Pins and Connections" for more information about the logic and hardware aspects of these pins.

Many of these pins are shared with on-chip peripherals such as timer systems, communication systems, or keyboard interrupts. When these other modules are not controlling the port pins, they revert to general-purpose I/O control.

### NOTE

Not all general-purpose I/O pins are available on all packages. To avoid extra current drain from floating input pins, the user's reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unconnected pins to outputs so the pins do not float.

#### **Chapter 6 Parallel Input/Output**

| _      | 7      | 6 | 5 | 4 | 3 | 2      | 1      | 0      |

|--------|--------|---|---|---|---|--------|--------|--------|

| R<br>W | PTASE7 | R | R | R | R | PTASE2 | PTASE1 | PTASE0 |

| Reset  | 0      | 0 | 0 | 0 | 0 | 0      | 0      | 0      |

Figure 6-13. Output Slew Rate Control Enable for Port A (PTASE)<sup>1</sup>

<sup>1</sup> Bits 6 through 3 are reserved bits that must always be written to 0.

#### Table 6-4. PTASE Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 2:0<br>PTASEn | <ul> <li>Output Slew Rate Control Enable for Port A Bits — Each of these control bits determine whether output slew rate control is enabled for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port A bit n.</li> <li>Output slew rate control enabled for port A bit n.</li> </ul> |

|        | 7      | 6 | 5 | 4 | 3 | 2      | 1      | 0      |   |

|--------|--------|---|---|---|---|--------|--------|--------|---|

| R<br>W | PTADS7 | R | R | R | R | PTADS2 | PTADS1 | PTADS0 | ĺ |

| Reset  | 0      | 0 | 0 | 0 | 0 | 0      | 0      | 0      |   |

### Figure 6-14. Output Drive Strength Selection for Port A (PTADS)<sup>1</sup>

<sup>1</sup> Bits 6 through 3 are reserved bits that must always be written to 0.

#### Table 6-5. PTADS Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 2:0<br>PTADSn | <ul> <li>Output Drive Strength Selection for Port A Bits — Each of these control bits selects between low and high output drive for the associated PTA pin.</li> <li>0 Low output drive enabled for port A bit n.</li> <li>1 High output drive enabled for port A bit n.</li> </ul> |

**Chapter 6 Parallel Input/Output**

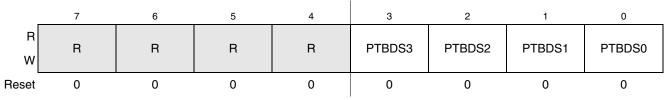

#### Figure 6-19. Output Drive Strength Selection for Port B (PTBDS)<sup>1</sup>

<sup>1</sup> Bits 7 through 4 are reserved bits that must always be written to 0.

#### Table 6-10. PTBDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTBDS[3:0] | <ul> <li>Output Drive Strength Selection for Port B Bits — Each of these control bits selects between low and high output drive for the associated PTB pin.</li> <li>0 Low output drive enabled for port B bit n.</li> <li>1 High output drive enabled for port B bit n.</li> </ul> |

### 6.7.5 Port C I/O Registers (PTCD and PTCDD)

Port C parallel I/O function is controlled by the registers listed below.

| _      | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|---|---|-------|-------|-------|-------|-------|-------|

| R<br>W | 0 | R | PTCD5 | PTCD4 | PTCD3 | PTCD2 | PTCD1 | PTCD0 |

| Reset  | 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 6-20. Port C Data Register (PTCD)<sup>1</sup>

<sup>1</sup> Bit 6 is a reserved bit that must always be written to 0.

#### Table 6-11. PTCD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0<br>PTCD[5:0] | Port C Data Register Bits — For port C pins that are inputs, reads return the logic level on the pin. For port C pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port C pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTCD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1*.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

### 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

Chapter 7 Central Processor Unit (S08CPUV2)

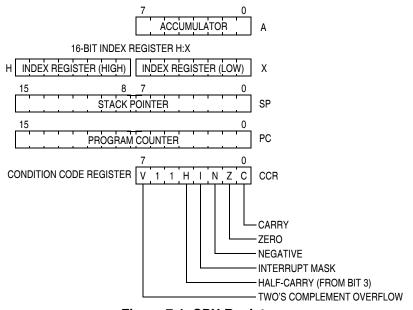

# 7.2 Programmer's Model and CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

### 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the address where the specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

### 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

#### Chapter 7 Central Processor Unit (S08CPUV2)

|                         |                                           |                      |                      |                       |                       | 012)                 |                     |                        |                      |                      |              |                      |                      |                      |                     |

|-------------------------|-------------------------------------------|----------------------|----------------------|-----------------------|-----------------------|----------------------|---------------------|------------------------|----------------------|----------------------|--------------|----------------------|----------------------|----------------------|---------------------|

| Bit-Man                 | Bit-Manipulation Branch Read-Modify-Write |                      |                      |                       |                       | ntrol                |                     | -                      |                      | r/Memory             |              |                      |                      |                      |                     |

| 00 5                    | 10 5                                      | 20 3                 | 30 5                 | 40 1                  | 50 1                  | 60 5                 | 70 4                | 80 9                   | 90 3                 | A0 2                 | B0 3         | C0 4                 | D0 4                 | E0 3                 | F0 3                |

| BRSET0                  | BSET0                                     | BRA                  | NEG                  | NEGA                  | NEGX                  | NEG                  | NEG                 | RTI                    | BGE                  | SUB                  | SUB          | SUB                  | SUB                  | SUB                  | SUB                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 01 5                    | 11 5                                      | 21 3                 | 31 5                 | 41 4                  | 51 4                  | 61 5                 | 71 5                | 81 6                   | 91 3                 | A1 2                 | B1 3         | CMP                  | D1 4                 | E1 3                 | F1 3                |

| BRCLR0                  | BCLR0                                     | BRN                  | CBEQ                 | CBEQA                 | CBEQX                 | CBEQ                 | CBEQ                | RTS                    | BLT                  | CMP                  | CMP          |                      | CMP                  | CMP                  | CMP                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 3 DIR                | 3 IMM                 | 3 IMM                 | 3 IX1+               | 2 IX+               | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR        |                      | 3 IX2                | 2 IX1                | 1 IX                |

| 02 5                    | 12 5                                      | 22 3                 | 32 5                 | 42 5                  | 52 6                  | 62 1                 | 72 1                | 82 5+                  | 92 3                 | A2 2                 | B2 3         | C2 4                 | D2 4                 | E2 3                 | F2 3                |

| BRSET1                  | BSET1                                     | BHI                  | LDHX                 | MUL                   | DIV                   | NSA                  | DAA                 | BGND                   | BGT                  | SBC                  | SBC          | SBC                  | SBC                  | SBC                  | SBC                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 3 EXT                | 1 INH                 | 1 INH                 | 1 INH                | 1 INH               | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 03 5                    | 13 5                                      | 23 3                 | 33 5                 | 43 1                  | 53 1                  | 63 5                 | 73 4                | 83 11                  | 93 3                 | A3 2                 | B3 3         | C3 4                 | D3 4                 | E3 3                 | F3 3                |

| BRCLR1                  | BCLR1                                     | BLS                  | COM                  | COMA                  | COMX                  | COM                  | COM                 | SWI                    | BLE                  | CPX                  | CPX          | CPX                  | CPX                  | CPX                  | CPX                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 2 REL                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 04 5<br>BRSET2<br>3 DIR | 14 5<br>BSET2<br>2 DIR                    | 24 3<br>BCC<br>2 REL | 34 5<br>LSR<br>2 DIR | 44 1<br>LSRA<br>1 INH | 54 1<br>LSRX<br>1 INH | 64 5<br>LSR<br>2 IX1 | 74 4<br>LSR<br>1 IX | 84 1<br>TAP<br>1 INH   | 94 2<br>TXS<br>1 INH | A4 2<br>AND<br>2 IMM | B4 3<br>AND  | C4 4<br>AND<br>3 EXT | D4 4<br>AND<br>3 IX2 | E4 3<br>AND<br>2 IX1 | F4 3<br>AND<br>1 IX |

| 05 5                    | 15 5                                      | 25 3                 | 35 4                 | 45 3                  | 55 4                  | 65 3                 | 75 5                | 85 1                   | 95 2                 | A5 2                 | B5 3         | C5 4                 | D5 4                 | E5 3                 | F5 3                |

| BRCLR2                  | BCLR2                                     | BCS                  | STHX                 | LDHX                  | LDHX                  | CPHX                 | CPHX                | TPA                    | TSX                  | BIT                  | BIT          | BIT                  | BIT                  | BIT                  | BIT                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 3 IMM                 | 2 DIR                 | 3 IMM                | 2 DIR               | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 06 5                    | 16 5                                      | 26 3                 | 36 5                 | 46 1                  | 56 1                  | 66 5                 | 76 4                | 86 3                   | 96 5                 | A6 2                 | B6 3         | C6 4                 | D6 4                 | E6 3                 | F6 3                |

| BRSET3                  | BSET3                                     | BNE                  | ROR                  | RORA                  | RORX                  | ROR                  | ROR                 | PULA                   | STHX                 | LDA                  | LDA          | LDA                  | LDA                  | LDA                  | LDA                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 3 EXT                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 07 5                    | 17 5                                      | 27 3                 | 37 5                 | 47 1                  | 57 1                  | 67 5                 | 77 4                | 87 2                   | 97 1                 | A7 2                 | B7 3         | C7 4                 | D7 4                 | E7 3                 | F7 2                |

| BRCLR3                  | BCLR3                                     | BEQ                  | ASR                  | ASRA                  | ASRX                  | ASR                  | ASR                 | PSHA                   | TAX                  | AIS                  | STA          | STA                  | STA                  | STA                  | STA                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 08 5                    | 18 5                                      | 28 3                 | 38 5                 | 48 1                  | 58 1                  | 68 5                 | 78 4                | 88 3                   | 98 1                 | A8 2                 | B8 3         | C8 4                 | D8 4                 | E8 3                 | F8 3                |

| BRSET4                  | BSET4                                     | BHCC                 | LSL                  | LSLA                  | LSLX                  | LSL                  | LSL                 | PULX                   | CLC                  | EOR                  | EOR          | EOR                  | EOR                  | EOR                  | EOR                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 09 5                    | 19 5                                      | 29 3                 | 39 5                 | 49 1                  | 59 1                  | 69 5                 | 79 4                | 89 2                   | 99 1                 | A9 2                 | B9 3         | C9 4                 | D9 4                 | E9 3                 | F9 3                |

| BRCLR4                  | BCLR4                                     | BHCS                 | ROL                  | ROLA                  | ROLX                  | ROL                  | ROL                 | PSHX                   | SEC                  | ADC                  | ADC          | ADC                  | ADC                  | ADC                  | ADC                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0A 5                    | 1A 5                                      | 2A 3                 | 3A 5                 | 4A 1                  | 5A 1                  | 6A 5                 | 7A 4                | 8A 3                   | 9A 1                 | AA 2                 | BA 3         | CA 4                 | DA 4                 | EA 3                 | FA 3                |

| BRSET5                  | BSET5                                     | BPL                  | DEC                  | DECA                  | DECX                  | DEC                  | DEC                 | PULH                   | CLI                  | ORA                  | ORA          | ORA                  | ORA                  | ORA                  | ORA                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0B 5                    |                                           | 2B 3                 | 3B 7                 | 4B 4                  | 5B 4                  | 6B 7                 | 7B 6                | 8B 2                   | 9B 1                 | AB 2                 | BB 3         | CB 4                 | DB 4                 | EB 3                 | FB 3                |

| BRCLR5                  |                                           | BMI                  | DBNZ                 | DBNZA                 | DBNZX                 | DBNZ                 | DBNZ                | PSHH                   | SEI                  | ADD                  | ADD          | ADD                  | ADD                  | ADD                  | ADD                 |

| 3 DIR                   |                                           | 2 REL                | 3 DIR                | 2 INH                 | 2 INH                 | 3 IX1                | 2 IX                | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0C 5                    | 1C 5                                      | 2C 3                 | 3C 5                 | 4C 1                  | 5C 1                  | 6C 5                 | 7C 4                | 8C 1                   | 9C 1                 |                      | BC 3         | CC 4                 | DC 4                 | EC 3                 | FC 3                |

| BRSET6                  | BSET6                                     | BMC                  | INC                  | INCA                  | INCX                  | INC                  | INC                 | CLRH                   | RSP                  |                      | JMP          | JMP                  | JMP                  | JMP                  | JMP                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 1 INH                |                      | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0D 5                    | 1D 5                                      | 2D 3                 | 3D 4                 | 4D 1                  | 5D 1                  | 6D 4                 | 7D 3                |                        | 9D 1                 | AD 5                 | BD 5         | CD 6                 | DD 6                 | ED 5                 | FD 5                |

| BRCLR6                  | BCLR6                                     | BMS                  | TST                  | TSTA                  | TSTX                  | TST                  | TST                 |                        | NOP                  | BSR                  | JSR          | JSR                  | JSR                  | JSR                  | JSR                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                |                        | 1 INH                | 2 REL                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

| 0E 5<br>BRSET7<br>3 DIR | 1E 5<br>BSET7<br>2 DIR                    | 2E 3<br>BIL<br>2 REL |                      | 4E 5<br>MOV<br>3 DD   | 5E 5<br>MOV<br>2 DIX+ | 6E 4<br>MOV<br>3 IMD | MOV<br>2 IX+D       | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2         | AE 2<br>LDX<br>2 IMM | LDX<br>2 DIR | LDX<br>3 EXT         | LDX<br>3 IX2         | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5                    | 1F 5                                      | 2F 3                 | 3F 5                 | 4F 1                  | 5F 1                  | 6F 5                 | 7F 4                | 8F 2+                  | 9F 1                 | AF 2                 | BF 3         | CF 4                 | DF 4                 | EF 3                 | FF 2                |

| BRCLR7                  | BCLR7                                     | BIH                  | CLR                  | CLRA                  | CLRX                  | CLR                  | CLR                 | WAIT                   | TXA                  | AIX                  | STX          | STX                  | STX                  | STX                  | STX                 |

| 3 DIR                   | 2 DIR                                     | 2 REL                | 2 DIR                | 1 INH                 | 1 INH                 | 2 IX1                | 1 IX                | 1 INH                  | 1 INH                | 2 IMM                | 2 DIR        | 3 EXT                | 3 IX2                | 2 IX1                | 1 IX                |

### Table 7-3. Opcode Map (Sheet 1 of 2)

| INH  | Inherent   |

|------|------------|

| IMM  | Immediate  |

| DIR  | Direct     |

| EXT  | Extended   |

| DD   | DIR to DIR |

| IX+D | IX+ to DIR |

|      |            |

Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+ REL IX IX1 IX2 IMD DIX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment SP1 SP2 IX+

IX1+

Opcode in Hexadecimal F0 3 SUB Instruction Mnemonic 1 IX Addressing Mode Number of Bytes

Internal Clock Generator (S08ICGV4)

### 8.5.4 Example #3: No External Crystal Connection, 5.4 MHz Bus Frequency

In this example, the FLL will be used (in FEI mode) to multiply the internal 243 kHz (approximate) reference clock up to 10.8 MHz to achieve 5.4 MHz bus frequency. This system will also use the trim function to fine tune the frequency based on an external reference signal.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately 8 MHz on ICGOUT which corresponds to a 4 MHz bus frequency (f<sub>Bus</sub>).

The clock scheme will be FLL engaged, internal (FEI). So

Solving for N / R gives:

A trim procedure will be required to hone the frequency to exactly 5.4 MHz. An example of the trim procedure is shown in example #4.

The values needed in each register to set up the desired operation are:

### **ICGC1 = \$28 (%00101000)**

| Bit 7    | HGO     | 0  | Configures oscillator for low power                                          |

|----------|---------|----|------------------------------------------------------------------------------|

| Bit 6    | RANGE   | 0  | Configures oscillator for low-frequency range; FLL prescale factor is 64     |

| Bit 5    | REFS    | 1  | Oscillator using crystal or resonator requested (bit is really a don't care) |

| Bits 4:3 | CLKS    | 01 | FLL engaged, internal reference clock mode                                   |

| Bit 2    | OSCSTEN | 0  | Disables the oscillator                                                      |

| Bit 1    | LOCD    | 0  | Loss-of-clock enabled                                                        |

| Bit 0    |         | 0  | Unimplemented or reserved, always reads zero                                 |

ICGC2 = \$31 (%00110001)

| Bit 7   | LOLRE | 0   | Generates an interrupt request on loss of lock  |

|---------|-------|-----|-------------------------------------------------|

| Bit 6:4 | MFD   | 011 | Sets the MFD multiplication factor to 10        |

| Bit 3   | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bit 2:0 | RFD   | 001 | Sets the RFD division factor to $\div 2$        |

### ICGS1 = \$xx

This is read only except for clearing interrupt flag

### ICGS2 = \$xx

This is read only; good idea to read this before performing time critical operations

### ICGFLTLU/L = \$xx

Not used in this example

Keyboard Interrupt (S08KBIV1)

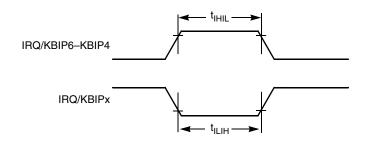

### 9.5.3 KBI Interrupt Controls

The KBF status flag becomes set (1) when an edge event has been detected on any KBI input pin. If KBIE = 1 in the KBISC register, a hardware interrupt will be requested whenever KBF = 1. The KBF flag is cleared by writing a 1 to the keyboard acknowledge (KBACK) bit.

When KBIMOD = 0 (selecting edge-only operation), KBF is always cleared by writing 1 to KBACK. When KBIMOD = 1 (selecting edge-and-level operation), KBF cannot be cleared as long as any keyboard input is at its asserted level.

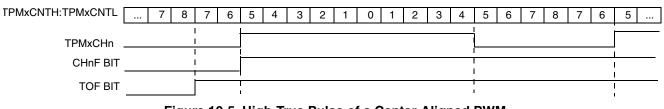

#### Timer/PWM Module (S08TPMV3)

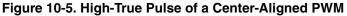

When the TPM is configured for center-aligned PWM (and ELSnB:ELSnA not = 0:0), the data direction for all channels in this TPM are overridden, the TPMxCHn pins are forced to be outputs controlled by the TPM, and the ELSnA bits control the polarity of each TPMxCHn output. If ELSnB:ELSnA=1:0, the corresponding TPMxCHn pin is cleared when the timer counter is counting up, and the channel value register matches the timer counter; the TPMxCHn pin is set when the timer counter is counting down, and the channel value register matches the timer counter. If ELSnA=1, the corresponding TPMxCHn pin is set when the timer counter; the TPMxCHn pin is cleared when the channel value register matches the timer counter is counting up and the channel value register matches the timer counter; the TPMxCHn pin is cleared when the timer counter is the timer counter; the timer counter is counting up and the channel value register matches the timer counter is counting the timer counter; the timer counter is counter is counter; the timer counter is counter is counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

Figure 10-6. Low-True Pulse of a Center-Aligned PWM

#### Timer/PWM Module (S08TPMV3)

| EPWM mode<br>TPMxMODH:TPMxMODL<br>TPMxCnVH:TPMxCnVL = |    |    |         |           |           |

|-------------------------------------------------------|----|----|---------|-----------|-----------|

| RESET (active low)                                    |    |    |         |           |           |

| BUS CLOCK                                             |    |    | יויויו  | וויוי     |           |

| TPMxCNTH:TPMxCNTL                                     |    | 0  | 1 2 3 4 | 5 6 7     | 0 1 2     |

| CLKSB:CLKSA BITS                                      |    | 00 |         | 01        |           |

| MSnB:MSnA BITS                                        | 00 | 10 |         |           | <br>      |

| ELSnB:ELSnA BITS                                      | 00 | 01 |         | <br> <br> | <br> <br> |

| TPMv2 TPMxCHn                                         |    |    |         |           |           |

| TPMv3 TPMxCHn                                         |    |    |         |           |           |

| CHnF BIT<br>(in TPMv2 and TPMv3)                      |    |    |         | <u> </u>  |           |

#### Figure 10-18. Generation of low-true EPWM signal by TPM v2 and v3 after the reset

The following procedure can be used in TPM v3 (when the channel pin is also a port pin) to emulate the high-true EPWM generated by TPM v2 after the reset.

•••

configure the channel pin as output port pin and set the output pin;

configure the channel to generate the EPWM signal but keep ELSnB:ELSnA as 00;

configure the other registers (TPMxMODH, TPMxMODL, TPMxCnVH, TPMxCnVL, ...);

configure CLKSB:CLKSA bits (TPM v3 starts to generate the high-true EPWM signal, however TPM does not control the channel pin, so the EPWM signal is not available);

wait until the TOF is set (or use the TOF interrupt);

enable the channel output by configuring ELSnB:ELSnA bits (now EPWM signal is available);

•••

# 11.2 Register Definition

The SCI has eight 8-bit registers to control baud rate, select SCI options, report SCI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SCI registers. This section refers to registers and control bits only by their names.

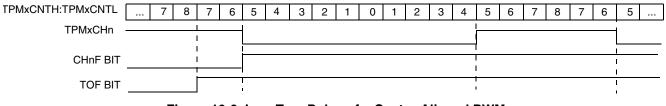

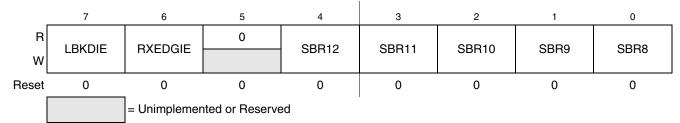

### 11.2.1 SCI Baud Rate Registers (SCIxBDH, SCIxBDL)

This pair of registers controls the prescale divisor for SCI baud rate generation. To update the 13-bit baud rate setting [SBR12:SBR0], first write to SCIxBDH to buffer the high half of the new value and then write to SCIxBDL. The working value in SCIxBDH does not change until SCIxBDL is written.

SCIxBDL is reset to a non-zero value, so after reset the baud rate generator remains disabled until the first time the receiver or transmitter is enabled (RE or TE bits in SCIxC2 are written to 1).

Figure 11-4. SCI Baud Rate Register (SCIxBDH)

| Table 11-1. | SCIxBDH | Field Des | criptions |

|-------------|---------|-----------|-----------|

|-------------|---------|-----------|-----------|

| Field            | Description                                                                                                                                                                                                                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LBKDIE      | <ul> <li>LIN Break Detect Interrupt Enable (for LBKDIF)</li> <li>0 Hardware interrupts from LBKDIF disabled (use polling).</li> <li>1 Hardware interrupt requested when LBKDIF flag is 1.</li> </ul>                                                                                                                                                   |

| 6<br>RXEDGIE     | <b>RxD Input Active Edge Interrupt Enable (for RXEDGIF)</b> 0011Hardware interrupt requested when RXEDGIF flag is 1.                                                                                                                                                                                                                                   |

| 4:0<br>SBR[12:8] | <b>Baud Rate Modulo Divisor</b> — The 13 bits in SBR[12:0] are referred to collectively as BR, and they set the modulo divide rate for the SCI baud rate generator. When BR = 0, the SCI baud rate generator is disabled to reduce supply current. When BR = 1 to 8191, the SCI baud rate = BUSCLK/( $16 \times BR$ ). See also BR bits in Table 11-2. |

Figure 11-5. SCI Baud Rate Register (SCIxBDL)

# 12.3 Modes of Operation

### 12.3.1 SPI in Stop Modes

The SPI is disabled in all stop modes, regardless of the settings before executing the STOP instruction. During either stop1 or stop2 mode, the SPI module will be fully powered down. Upon wake-up from stop1 or stop2 mode, the SPI module will be in the reset state. During stop3 mode, clocks to the SPI module are halted. No registers are affected. If stop3 is exited with a reset, the SPI will be put into its reset state. If stop3 is exited with an interrupt, the SPI continues from the state it was in when stop3 was entered.

# 12.4 Register Definition

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

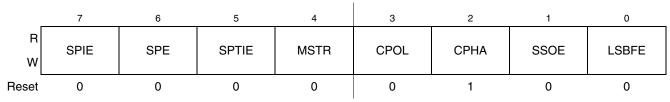

# 12.4.1 SPI Control Register 1 (SPI1C1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 12-5. SPI Control Register 1 (SPI1C1)

| Field      | Description                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable (for SPRF and MODF) — This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.</li> <li>Interrupts from SPRF and MODF inhibited (use polling)</li> <li>When SPRF or MODF is 1, request a hardware interrupt</li> </ul>                        |

| 6<br>SPE   | <ul> <li>SPI System Enable — Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.</li> <li>O SPI system inactive</li> <li>1 SPI system enabled</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).</li> <li>Interrupts from SPTEF inhibited (use polling)</li> <li>When SPTEF is 1, hardware interrupt requested</li> </ul>                                                                        |

Serial Peripheral Interface (S08SPIV3)

| SPPR2:SPPR1:SPPR0 | Prescaler Divisor |

|-------------------|-------------------|

| 0:0:0             | 1                 |

| 0:0:1             | 2                 |

| 0:1:0             | 3                 |

| 0:1:1             | 4                 |

| 1:0:0             | 5                 |

| 1:0:1             | 6                 |

| 1:1:0             | 7                 |

| 1:1:1             | 8                 |

#### Table 12-5. SPI Baud Rate Prescaler Divisor

#### Table 12-6. SPI Baud Rate Divisor

| SPR2:SPR1:SPR0 | Rate Divisor |

|----------------|--------------|

| 0:0:0          | 2            |

| 0:0:1          | 4            |

| 0:1:0          | 8            |

| 0:1:1          | 16           |

| 1:0:0          | 32           |

| 1:0:1          | 64           |

| 1:1:0          | 128          |

| 1:1:1          | 256          |

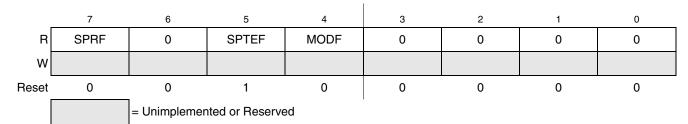

### 12.4.4 SPI Status Register (SPI1S)

This register has three read-only status bits. Bits 6, 3, 2, 1, and 0 are not implemented and always read 0. Writes have no meaning or effect.

Figure 12-8. SPI Status Register (SPI1S)

| Field      | Description                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC1 | <ul> <li>ADC Pin Control 1 — ADPC1 is used to control the pin associated with channel AD1.</li> <li>0 AD1 pin I/O control enabled</li> <li>1 AD1 pin I/O control disabled</li> </ul> |

| 0<br>ADPC0 | <ul> <li>ADC Pin Control 0 — ADPC0 is used to control the pin associated with channel AD0.</li> <li>0 AD0 pin I/O control enabled</li> <li>1 AD0 pin I/O control disabled</li> </ul> |

#### Table 14-9. APCTL1 Register Field Descriptions (continued)

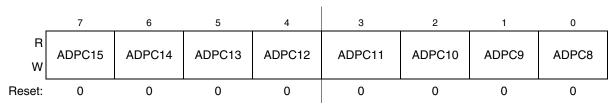

### 14.4.9 Pin Control 2 Register (APCTL2)

APCTL2 is used to control channels 8–15 of the ADC module.

Figure 14-12. Pin Control 2 Register (APCTL2)

#### Table 14-10. APCTL2 Register Field Descriptions

| Field       | Description                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADPC15 | <ul> <li>ADC Pin Control 15 — ADPC15 is used to control the pin associated with channel AD15.</li> <li>0 AD15 pin I/O control enabled</li> <li>1 AD15 pin I/O control disabled</li> </ul> |

| 6<br>ADPC14 | <ul> <li>ADC Pin Control 14 — ADPC14 is used to control the pin associated with channel AD14.</li> <li>0 AD14 pin I/O control enabled</li> <li>1 AD14 pin I/O control disabled</li> </ul> |

| 5<br>ADPC13 | <ul> <li>ADC Pin Control 13 — ADPC13 is used to control the pin associated with channel AD13.</li> <li>0 AD13 pin I/O control enabled</li> <li>1 AD13 pin I/O control disabled</li> </ul> |

| 4<br>ADPC12 | <ul> <li>ADC Pin Control 12 — ADPC12 is used to control the pin associated with channel AD12.</li> <li>0 AD12 pin I/O control enabled</li> <li>1 AD12 pin I/O control disabled</li> </ul> |

| 3<br>ADPC11 | <ul> <li>ADC Pin Control 11 — ADPC11 is used to control the pin associated with channel AD11.</li> <li>0 AD11 pin I/O control enabled</li> <li>1 AD11 pin I/O control disabled</li> </ul> |

| 2<br>ADPC10 | <ul> <li>ADC Pin Control 10 — ADPC10 is used to control the pin associated with channel AD10.</li> <li>0 AD10 pin I/O control enabled</li> <li>1 AD10 pin I/O control disabled</li> </ul> |

| Field      | Description                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC9 | <ul> <li>ADC Pin Control 9 — ADPC9 is used to control the pin associated with channel AD9.</li> <li>0 AD9 pin I/O control enabled</li> <li>1 AD9 pin I/O control disabled</li> </ul> |

| 0<br>ADPC8 | <ul> <li>ADC Pin Control 8 — ADPC8 is used to control the pin associated with channel AD8.</li> <li>0 AD8 pin I/O control enabled</li> <li>1 AD8 pin I/O control disabled</li> </ul> |

Table 14-10. APCTL2 Register Field Descriptions (continued)

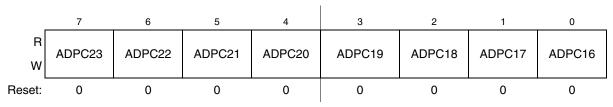

# 14.4.10 Pin Control 3 Register (APCTL3)

APCTL3 is used to control channels 16–23 of the ADC module.

Figure 14-13. Pin Control 3 Register (APCTL3)

| Table 14-11. APCTL3 Register Field Descriptions |

|-------------------------------------------------|

|-------------------------------------------------|

| Field       | Description                                                                                                                                                                               |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>ADPC23 | <ul> <li>ADC Pin Control 23 — ADPC23 is used to control the pin associated with channel AD23.</li> <li>0 AD23 pin I/O control enabled</li> <li>1 AD23 pin I/O control disabled</li> </ul> |  |  |  |  |

| 6<br>ADPC22 | <ul> <li>ADC Pin Control 22 — ADPC22 is used to control the pin associated with channel AD22.</li> <li>0 AD22 pin I/O control enabled</li> <li>1 AD22 pin I/O control disabled</li> </ul> |  |  |  |  |

| 5<br>ADPC21 | <ul> <li>ADC Pin Control 21 — ADPC21 is used to control the pin associated with channel AD21.</li> <li>0 AD21 pin I/O control enabled</li> <li>1 AD21 pin I/O control disabled</li> </ul> |  |  |  |  |

| 4<br>ADPC20 | <ul> <li>ADC Pin Control 20 — ADPC20 is used to control the pin associated with channel AD20.</li> <li>0 AD20 pin I/O control enabled</li> <li>1 AD20 pin I/O control disabled</li> </ul> |  |  |  |  |

| 3<br>ADPC19 | <ul> <li>ADC Pin Control 19 — ADPC19 is used to control the pin associated with channel AD19.</li> <li>0 AD19 pin I/O control enabled</li> <li>1 AD19 pin I/O control disabled</li> </ul> |  |  |  |  |

| 2<br>ADPC18 | <ul> <li>ADC Pin Control 18 — ADPC18 is used to control the pin associated with channel AD18.</li> <li>0 AD18 pin I/O control enabled</li> <li>1 AD18 pin I/O control disabled</li> </ul> |  |  |  |  |

### 15.3.6 Hardware Breakpoints

The BRKEN control bit in the DBGC register may be set to 1 to allow any of the trigger conditions described in Section 15.3.5, "Trigger Modes," to be used to generate a hardware breakpoint request to the CPU. TAG in DBGC controls whether the breakpoint request will be treated as a tag-type breakpoint or a force-type breakpoint. A tag breakpoint causes the current opcode to be marked as it enters the instruction queue. If a tagged opcode reaches the end of the pipe, the CPU executes a BGND instruction to go to active background mode rather than executing the tagged opcode. A force-type breakpoint causes the CPU to finish the current instruction and then go to active background mode.

If the background mode has not been enabled (ENBDM = 1) by a serial WRITE\_CONTROL command through the BKGD pin, the CPU will execute an SWI instruction instead of going to active background mode.

### 15.4 Register Definition

This section contains the descriptions of the BDC and DBG registers and control bits.

Refer to the high-page register summary in the device overview chapter of this data sheet for the absolute address assignments for all DBG registers. This section refers to registers and control bits only by their names.

### 15.4.1 BDC Registers and Control Bits

The BDC has two registers:

- The BDC status and control register (BDCSCR) is an 8-bit register containing control and status bits for the background debug controller.

- The BDC breakpoint match register (BDCBKPT) holds a 16-bit breakpoint match address.

These registers are accessed with dedicated serial BDC commands and are not located in the memory space of the target MCU (so they do not have addresses and cannot be accessed by user programs).

Some of the bits in the BDCSCR have write limitations; otherwise, these registers may be read or written at any time. For example, the ENBDM control bit may not be written while the MCU is in active background mode. (This prevents the ambiguous condition of the control bit forbidding active background mode while the MCU is already in active background mode.) Also, the four status bits (BDMACT, WS, WSF, and DVF) are read-only status indicators and can never be written by the WRITE\_CONTROL serial BDC command. The clock switch (CLKSW) control bit may be read or written at any time.

Appendix A Electrical Characteristics and Timing Specifications

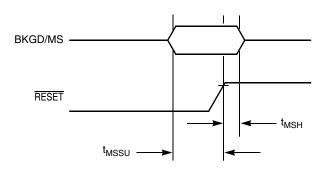

Figure A-11. Active Background Debug Mode Latch Timing

### A.10.2 Timer/PWM (TPM) Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| Function                  | Symbol              | Min | Мах                 | Unit             |

|---------------------------|---------------------|-----|---------------------|------------------|

| External clock frequency  | f <sub>TPMext</sub> | dc  | f <sub>Bus</sub> /4 | MHz              |

| External clock period     | t <sub>TPMext</sub> | 4   | _                   | t <sub>cyc</sub> |

| External clock high time  | t <sub>clkh</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| External clock low time   | t <sub>ciki</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

Table A-13. TPM Input Timing