Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 34                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LQFP                                                                |

| Supplier Device Package    | 44-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac16cfge |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 1 Introduction**

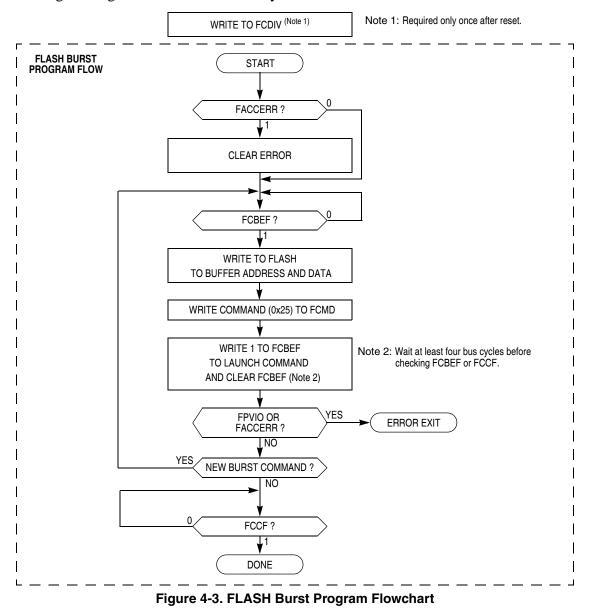

• The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst program time provided that the conditions above are met. In the case the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

MC9S08AC16 Series Data Sheet, Rev. 9

| SEC01:SEC00 | Description |

|-------------|-------------|

| 0:0         | secure      |

| 0:1         | secure      |

| 1:0         | unsecured   |

| 1:1         | secure      |

Table 4-9. Security States

SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH.

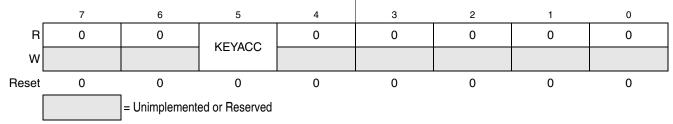

### 4.6.3 FLASH Configuration Register (FCNFG)

Bits 7 through 5 may be read or written at any time. Bits 4 through 0 always read 0 and cannot be written.

### Figure 4-7. FLASH Configuration Register (FCNFG)

| Table 4-10. | FCNFG | Register | Field | Descriptions |

|-------------|-------|----------|-------|--------------|

|-------------|-------|----------|-------|--------------|

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.5, "Security."</li> <li>0 Writes to 0xFFB0–0xFFB7 are interpreted as the start of a FLASH programming or erase command.</li> <li>1 Writes to NVBACKKEY (0xFFB0–0xFFB7) are interpreted as comparison key writes.</li> </ul> |

Chapter 4 Memory

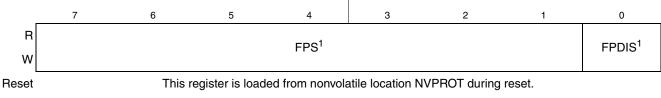

# 4.6.4 FLASH Protection Register (FPROT and NVPROT)

During reset, the contents of the nonvolatile location NVPROT are copied from FLASH into FPROT. This register can be read at any time. If FPDIS = 0, protection can be increased, i.e., a smaller value of FPS can be written. If FPDIS = 1, writes do not change protection.

<sup>1</sup> Background commands can be used to change the contents of these bits in FPROT.

### Figure 4-8. FLASH Protection Register (FPROT)

### Table 4-11. FPROT Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1<br>FPS[7:1] | <b>FLASH Protect Select Bits</b> — When FPDIS = 0, this 7-bit field determines the ending address of unprotected FLASH locations at the high address end of the FLASH. Protected FLASH locations cannot be erased or programmed. |

| 0<br>FPDIS      | <ul> <li>FLASH Protection Disable</li> <li>0 FLASH block specified by FPS[7:1] is block protected (program and erase not allowed).</li> <li>1 No FLASH block is protected.</li> </ul>                                            |

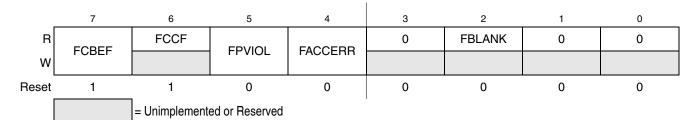

### 4.6.5 FLASH Status Register (FSTAT)

Bits 3, 1, and 0 always read 0 and writes have no meaning or effect. The remaining five bits are status bits that can be read at any time. Writes to these bits have special meanings that are discussed in the bit descriptions.

Figure 4-9. FLASH Status Register (FSTAT)

#### Table 5-4. SRS Register Field Descriptions (continued)

| Field     | Description                                                                                                                                                                                                                                                                                                                                   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>ILAD | Illegal Address— Reset was caused by an attempt to access a designated illegal address.0Reset not caused by an illegal address access.1Reset caused by an illegal address access.                                                                                                                                                             |

|           | Illegal address areas in the MC9S08AC16 are:<br>0x0470 - 0x17FF — Gap from end of RAM to start of high page registers<br>0x1860 - 0xBFFF — Gap from end of high page registers to start of Flash memory<br>Unused and reserved locations in register areas are not considered illegal addresses and do not trigger illegal<br>address resets. |

| 2<br>ICG  | Internal Clock Generation Module Reset — Reset was caused by an ICG module reset.         0       Reset not caused by ICG module.         1       Reset caused by ICG module.                                                                                                                                                                 |

| 1<br>LVD  | <ul> <li>Low Voltage Detect — If the LVDRE and LVDSE bits are set and the supply drops below the LVD trip voltage, an LVD reset will occur. This bit is also set by POR.</li> <li>Reset not caused by LVD trip or POR.</li> <li>Reset caused by LVD trip or POR.</li> </ul>                                                                   |

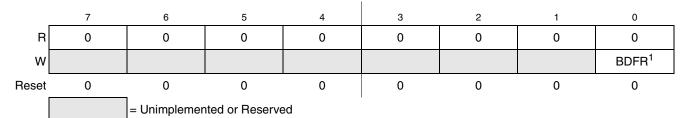

### 5.9.3 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial background command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

<sup>1</sup> BDFR is writable only through serial background debug commands, not from user programs.

### Figure 5-4. System Background Debug Force Reset Register (SBDFR)

#### Table 5-5. SBDFR Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>BDFR | <b>Background Debug Force Reset</b> — A serial background command such as WRITE_BYTE may be used to allow an external debug host to force a target system reset. Writing logic 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |

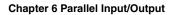

## 6.7.7 Port D I/O Registers (PTDD and PTDDD)

Port D parallel I/O function is controlled by the registers listed below.

### Figure 6-25. Port D Data Register (PTDD)<sup>1</sup>

<sup>1</sup> Bits 7 through 4 are reserved bits that must always be written to 0.

| Table 0-10. FIDD negister Tield Descriptions | Table 6-16. | PTDD Register Field Descriptions |

|----------------------------------------------|-------------|----------------------------------|

|----------------------------------------------|-------------|----------------------------------|

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTDD[3:0] | Port D Data Register Bits — For port D pins that are inputs, reads return the logic level on the pin. For port D pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port D pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTDD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

|        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

| R<br>W | R | R | R | R | PTDDD3 | PTDDD2 | PTDDD1 | PTDDD0 |

| Reset  | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

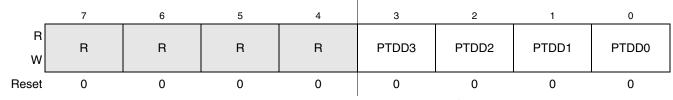

Figure 6-26. Data Direction for Port D (PTDDD)<sup>1</sup>

<sup>1</sup> Bits 7 through 4 are reserved bits that must always be written to 0.

### Table 6-17. PTDDD Register Field Descriptions

| Field             | Description                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTDDD[3:0] | <b>Data Direction for Port D Bits</b> — These read/write bits control the direction of port D pins and what is read for PTDD reads.                                              |

|                   | <ul><li>0 Input (output driver disabled) and reads return the pin value.</li><li>1 Output driver enabled for port D bit n and PTDD reads return the contents of PTDDn.</li></ul> |

| Field  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>V | <ul> <li>Two's Complement Overflow Flag — The CPU sets the overflow flag when a two's complement overflow occurs.</li> <li>The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.</li> <li>No overflow</li> <li>1 Overflow</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4<br>H | <ul> <li>Half-Carry Flag — The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C condition code bits to automatically add a correction value to the result from a previous ADD or ADC on BCD operands to correct the result to a valid BCD value.</li> <li>No carry between bits 3 and 4</li> <li>Carry between bits 3 and 4</li> </ul>                                                                                |

| 3      | Interrupt Mask Bit — When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the first instruction of the interrupt service routine is executed.<br>Interrupts are not recognized at the instruction boundary after any instruction that clears I (CLI or TAP). This ensures that the next instruction after a CLI or TAP will always be executed without the possibility of an intervening interrupt, provided I was set.<br>0 Interrupts disabled |

| 2<br>N | <ul> <li>Negative Flag — The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result. Simply loading or storing an 8-bit or 16-bit value causes N to be set if the most significant bit of the loaded or stored value was 1.</li> <li>0 Non-negative result</li> <li>1 Negative result</li> </ul>                                                                                                                                                                                                                                                                     |

| 1<br>Z | <ul> <li>Zero Flag — The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of 0x00 or 0x0000. Simply loading or storing an 8-bit or 16-bit value causes Z to be set if the loaded or stored value was all 0s.</li> <li>0 Non-zero result</li> <li>1 Zero result</li> </ul>                                                                                                                                                                                                                                                                                                                                |

| 0<br>C | <ul> <li>Carry/Borrow Flag — The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.</li> <li>0 No carry out of bit 7</li> <li>1 Carry out of bit 7</li> </ul>                                                                                                                                                                                                                                                                               |

### Table 7-1. CCR Register Field Descriptions

## 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location

Internal Clock Generator (S08ICGV4)

## 8.4.11 Fixed Frequency Clock

The ICG provides a fixed frequency clock output, XCLK, for use by on-chip peripherals. This output is equal to the internal bus clock, BUSCLK, in all modes except FEE. In FEE mode, XCLK is equal to ICGERCLK  $\div$  2 when the following conditions are met:

- (P × N) ÷ R ≥ 4 where P is determined by RANGE (see Table 8-11), N and R are determined by MFD and RFD respectively (see Table 8-12).

- LOCK = 1.

If the above conditions are not true, then XCLK is equal to BUSCLK.

When the ICG is in either FEI or SCM mode, XCLK is turned off. Any peripherals which can use XCLK as a clock source must not do so when the ICG is in FEI or SCM mode.

### 8.4.12 High Gain Oscillator

The oscillator has the option of running in a high gain oscillator (HGO) mode, which improves the oscillator's resistance to EMC noise when running in FBE or FEE modes. This option is selected by writing a 1 to the HGO bit in the ICGC1 register. HGO is used with both the high and low range oscillators but is only valid when REFS = 1 in the ICGC1 register. When HGO = 0, the standard low-power oscillator is selected. This bit is writable only once after any reset.

# 8.5 Initialization/Application Information

### 8.5.1 Introduction

The section is intended to give some basic direction on which configuration a user would want to select when initializing the ICG. For some applications, the serial communication link may dictate the accuracy of the clock reference. For other applications, lowest power consumption may be the chief clock consideration. Still others may have lowest cost as the primary goal. The ICG allows great flexibility in choosing which is best for any application.

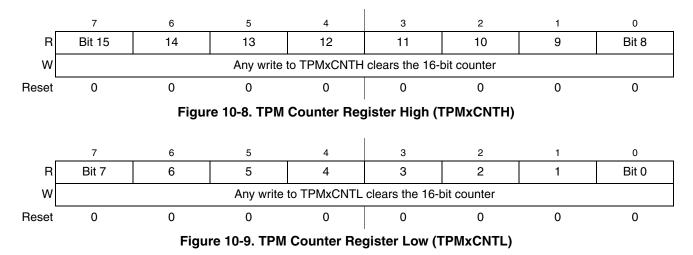

Reset clears the TPM counter registers. Writing any value to TPMxCNTH or TPMxCNTL also clears the TPM counter (TPMxCNTH:TPMxCNTL) and resets the coherency mechanism, regardless of the data involved in the write.

When BDM is active, the timer counter is frozen (this is the value that will be read by user); the coherency mechanism is frozen such that the buffer latches remain in the state they were in when the BDM became active, even if one or both counter halves are read while BDM is active. This assures that if the user was in the middle of reading a 16-bit register when BDM became active, it will read the appropriate value from the other half of the 16-bit value after returning to normal execution.

In BDM mode, writing any value to TPMxSC, TPMxCNTH or TPMxCNTL registers resets the read coherency mechanism of the TPMxCNTH:L registers, regardless of the data involved in the write.

## 10.5.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL)

The read/write TPM modulo registers contain the modulo value for the TPM counter. After the TPM counter reaches the modulo value, the TPM counter resumes counting from 0x0000 at the next clock, and the overflow flag (TOF) becomes set. Writing to TPMxMODH or TPMxMODL inhibits the TOF bit and overflow interrupts until the other byte is written. Reset sets the TPM counter modulo registers to 0x0000 which results in a free running timer counter (modulo disabled).

Writing to either byte (TPMxMODH or TPMxMODL) latches the value into a buffer and the registers are updated with the value of their write buffer according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), then the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), then the registers are updated after both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter, the update is made when the TPM counter changes from 0xFFFE to 0xFFFF

The latching mechanism may be manually reset by writing to the TPMxSC address (whether BDM is active or not).

Serial Communications Interface (S08SCIV4)

#### Serial Peripheral Interface (S08SPIV3)

The most common uses of the SPI system include connecting simple shift registers for adding input or output ports or connecting small peripheral devices such as serial A/D or D/A converters. Although Figure 12-2 shows a system where data is exchanged between two MCUs, many practical systems involve simpler connections where data is unidirectionally transferred from the master MCU to a slave or from a slave to the master MCU.

### 12.1.2.2 SPI Module Block Diagram

Figure 12-3 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPI1D) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPI1D). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK pin, the shifter output is routed to MOSI, and the shifter input is routed from the MISO pin.

When the SPI is configured as a slave, the SPSCK pin is routed to the clock input of the SPI, the shifter output is routed to MISO, and the shifter input is routed from the MOSI pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

Inter-Integrated Circuit (S08IICV2)

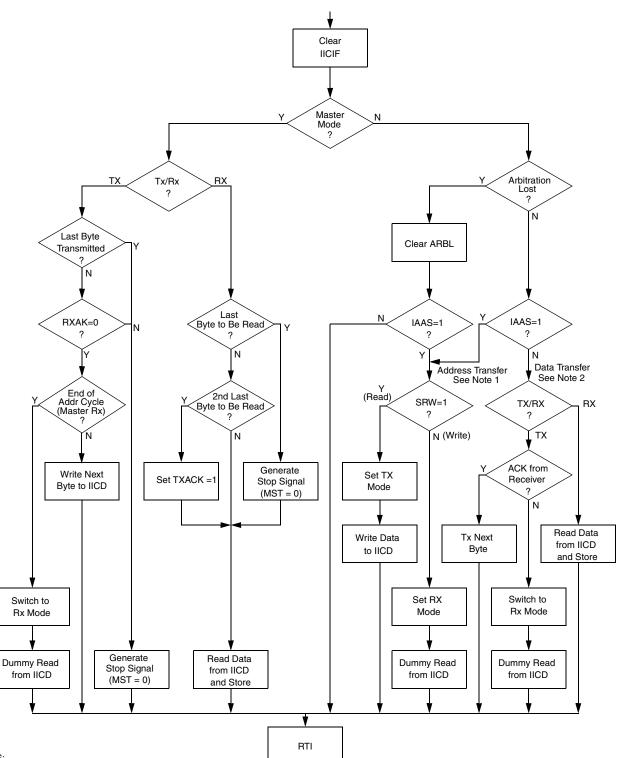

### NOTES:

- 1. If general call is enabled, a check must be done to determine whether the received address was a general call address (0x00). If the received address was a general call address, then the general call must be handled by user software.

- 2. When 10-bit addressing is used to address a slave, the slave sees an interrupt following the first byte of the extended address. User software must ensure that for this interrupt, the contents of IICD are ignored and not treated as a valid data transfer.

### Figure 13-12. Typical IIC Interrupt Routine

MC9S08AC16 Series Data Sheet, Rev. 9

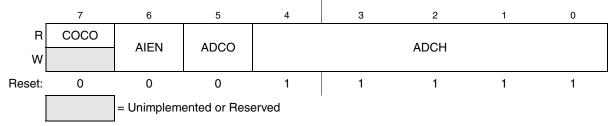

Figure 14-3. Status and Control Register (ADC1SC1)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COCO   | <ul> <li>Conversion Complete Flag — The COCO flag is a read-only bit which is set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1) the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared whenever ADC1SC1 is written or whenever ADC1RL is read.</li> <li>Conversion not completed</li> <li>Conversion completed</li> </ul>                                                                                                                                                                                                                                                                               |

| 6<br>AIEN   | <ul> <li>Interrupt Enable — AIEN is used to enable conversion complete interrupts. When COCO becomes set while AIEN is high, an interrupt is asserted.</li> <li>0 Conversion complete interrupt disabled</li> <li>1 Conversion complete interrupt enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5<br>ADCO   | <ul> <li>Continuous Conversion Enable — ADCO is used to enable continuous conversions.</li> <li>One conversion following a write to the ADC1SC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.</li> <li>Continuous conversions initiated following a write to ADC1SC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.</li> </ul>                                                                                                                                                                                                                   |

| 4:0<br>ADCH | Input Channel Select — The ADCH bits form a 5-bit field which is used to select one of the input channels. The input channels are detailed in Figure 14-4.<br>The successive approximation converter subsystem is turned off when the channel select bits are all set to 1.<br>This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources.<br>Terminating continuous conversions this way will prevent an additional, single conversion from being performed.<br>It is not necessary to set the channel select bits to all 1s to place the ADC in a low-power state when continuous conversions are not enabled because the module automatically enters a low-power state when a conversion completes. |

### Figure 14-4. Input Channel Select

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| 00100 | AD4          |

| 00101 | AD5          |

| 00110 | AD6          |

| 00111 | AD7          |

| ADCH  | Input Select |

|-------|--------------|

| 10000 | AD16         |

| 10001 | AD17         |

| 10010 | AD18         |

| 10011 | AD19         |

| 10100 | AD20         |

| 10101 | AD21         |

| 10110 | AD22         |

| 10111 | AD23         |

Development Support

A-Only — Trigger when the address matches the value in comparator A

A OR B — Trigger when the address matches either the value in comparator A or the value in comparator B

A Then B — Trigger when the address matches the value in comparator B but only after the address for another cycle matched the value in comparator A. There can be any number of cycles after the A match and before the B match.

A AND B Data (Full Mode) — This is called a full mode because address, data, and R/W (optionally) must match within the same bus cycle to cause a trigger event. Comparator A checks address, the low byte of comparator B checks data, and R/W is checked against RWA if RWAEN = 1. The high-order half of comparator B is not used.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

A AND NOT B Data (Full Mode) — Address must match comparator A, data must not match the low half of comparator B, and R/W must match RWA if RWAEN = 1. All three conditions must be met within the same bus cycle to cause a trigger.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**Event-Only B** (Store Data) — Trigger events occur each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

A Then Event-Only B (Store Data) — After the address has matched the value in comparator A, a trigger event occurs each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

**Inside Range (** $A \le Address \le B$ **)** — A trigger occurs when the address is greater than or equal to the value in comparator A and less than or equal to the value in comparator B at the same time.

**Outside Range** (Address < A or Address > B) — A trigger occurs when the address is either less than the value in comparator A or greater than the value in comparator B.

#### **A.8 ADC Characteristics**

Table A-8. 5 Volt 10-bit ADC Operating Conditions

| Characteristic                              | Conditions                                                                  | Symb              | Min               | Typ <sup>1</sup>  | Max               | Unit |

|---------------------------------------------|-----------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------|

| Supply voltage                              | Absolute                                                                    | V <sub>DDAD</sub> | 2.7               | _                 | 5.5               | V    |

|                                             | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> ) <sup>2</sup> | $\Delta V_{DDAD}$ | -100              | 0                 | +100              | mV   |

| Ground voltage                              | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSAD</sub> ) <sup>2</sup> | $\Delta V_{SSAD}$ | -100              | 0                 | +100              | mV   |

| Ref voltage high                            |                                                                             | V <sub>REFH</sub> | 2.7               | V <sub>DDAD</sub> | V <sub>DDAD</sub> | V    |

| Ref voltage low                             |                                                                             | V <sub>REFL</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V <sub>SSAD</sub> | V    |

| Supply current                              | Stop, reset, module off                                                     | I <sub>DDAD</sub> | —                 | 0.011             | 1                 | μA   |

| Input Voltage                               |                                                                             | V <sub>ADIN</sub> | V <sub>REFL</sub> | —                 | V <sub>REFH</sub> | V    |

| Input capacitance                           |                                                                             | C <sub>ADIN</sub> | —                 | 4.5               | 5.5               | pF   |

| Input resistance                            |                                                                             | R <sub>ADIN</sub> | —                 | 3                 | 5                 | kΩ   |

| Analog source resistance<br>External to MCU | 10-bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz         | R <sub>AS</sub>   |                   |                   | 5<br>10           | kΩ   |

|                                             | 8-bit mode (all valid f <sub>ADCK</sub> )                                   |                   | —                 | _                 | 10                |      |

| ADC conversion clock frequency              | High speed (ADLPC = 0)                                                      | f <sub>ADCK</sub> | 0.4               | _                 | 8.0               | MHz  |

|                                             | Low power (ADLPC = 1)                                                       |                   | 0.4               | —                 | 4.0               | Ī    |

<sup>1</sup> Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> dc potential difference.

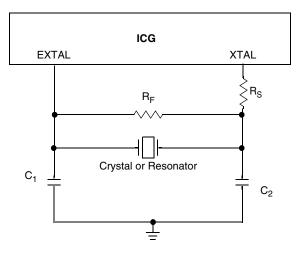

# A.9 Internal Clock Generation Module Characteristics

### Table A-10. ICG DC Electrical Specifications (Temperature Range = -40 to 125°C Ambient)

| Characteristic                                                                                                                                                         | Symbol                           | Min                   | Typ <sup>1</sup>          | Max | Unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|---------------------------|-----|----------|

| Load capacitors                                                                                                                                                        | C <sub>1</sub><br>C <sub>2</sub> | See Note <sup>2</sup> |                           |     |          |

| Feedback resistor<br>Low range (32k to 100 kHz)<br>High range (1M – 16 MHz)                                                                                            | R <sub>F</sub>                   |                       | 10<br>1                   |     | ΜΩ<br>ΜΩ |

| Series resistor<br>Low range<br>Low Gain (HGO = 0)<br>High Gain (HGO = 1)<br>High range<br>Low Gain (HGO = 0)<br>High Gain (HGO = 1)<br>$\geq 8$ MHz<br>4 MHz<br>1 MHz | R <sub>S</sub>                   |                       | 0<br>100<br>0<br>10<br>20 |     | kΩ       |

$^1$  Typical values are based on characterization data at V\_{DD} = 5.0V, 25 ^{\circ}C or is typical recommended value.

<sup>2</sup> See crystal or resonator manufacturer's recommendation.

### Table A-11. ICG Frequency Specifications (continued)

| Num | С | Characteristic                                                                                                                                                                     | Symbol               | Min | Typ <sup>1</sup> | Max      | Unit |

|-----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------------------|----------|------|

|     |   | MC9S08ACxx: Internal oscillator deviation from<br>trimmed frequency <sup>9</sup><br>$V_{DD} = 2.7 - 5.5 V$ , (constant temperature)<br>$V_{DD} = 5.0 V \pm 10\%$ , -40° C to 125°C | ACC <sub>int</sub>   |     | ±0.5<br>±0.5     | ±2<br>±2 | %    |

| 18  | с | <b>S9S08AW</b> <i>xx</i> <b>A:</b> Internal oscillator deviation from trimmed frequency <sup>10</sup><br>$V_{DD} = 2.7 - 5.5 V$ , (constant temperature)                           | 400                  | _   | ±0.5             | ±1.5     |      |

|     | Р | $V_{DD} = 5.0 \text{ V} \pm 10\%, -40^{\circ} \text{ C} \text{ to } 85^{\circ}\text{C}$                                                                                            | - ACC <sub>int</sub> | —   | ±0.5             | ±1.5     | %    |

|     | Р | $V_{DD} = 5.0 \text{ V} \pm 10\%, -40^{\circ} \text{ C} \text{ to } 125^{\circ}\text{C}$                                                                                           |                      |     | ±0.5             | ±2.0     | 1    |

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0V, 25°C unless otherwise stated.

<sup>2</sup> Self-clocked mode frequency is the frequency that the DCO generates when the FLL is open-loop.

<sup>3</sup> Loss of reference frequency is the reference frequency detected internally, which transitions the ICG into self-clocked mode if it is not in the desired range.

<sup>4</sup> Loss of DCO frequency is the DCO frequency detected internally, which transitions the ICG into FLL bypassed external mode (if an external reference exists) if it is not in the desired range.

<sup>5</sup> This parameter is characterized before qualification rather than 100% tested.

<sup>6</sup> Proper PC board layout procedures must be followed to achieve specifications.

<sup>7</sup> This specification applies to the period of time required for the FLL to lock after entering FLL engaged internal or external modes. If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>8</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>ICGOUT</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DDA</sub> and V<sub>SSA</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval.

<sup>9</sup> See Figure A-9.

<sup>10</sup> See Figure A-9.

Appendix A Electrical Characteristics and Timing Specifications

# A.11 SPI Characteristics

Table A-14 and Figure A-15 through Figure A-18 describe the timing requirements for the SPI system.

| Num | С | Characteristic <sup>1</sup>                 |                | Symbol                                   | Min                          | Max                                        | Unit                                 |

|-----|---|---------------------------------------------|----------------|------------------------------------------|------------------------------|--------------------------------------------|--------------------------------------|

|     |   |                                             | aster<br>Slave | f <sub>op</sub><br>f <sub>op</sub>       | f <sub>Bus</sub> /2048<br>dc | f <sub>Bus</sub> /2<br>f <sub>Bus</sub> /4 | Hz                                   |

| 1   |   |                                             | aster<br>Slave | t <sub>SCK</sub><br>t <sub>SCK</sub>     | 2<br>4                       | 2048<br>—                                  | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 2   |   |                                             | aster<br>Slave | t <sub>Lead</sub><br>t <sub>Lead</sub>   | <br>1/2                      | 1/2                                        | t <sub>SCK</sub><br>t <sub>SCK</sub> |

| 3   |   |                                             | aster<br>Slave | t <sub>Lag</sub><br>t <sub>Lag</sub>     | <br>1/2                      | 1/2                                        | t <sub>SCK</sub><br>t <sub>SCK</sub> |

| 4   |   | Clock (SPSCK) high time<br>Master and Slave |                | t <sub>scкн</sub>                        | 1/2 t <sub>SCK</sub> – 25    | _                                          | ns                                   |

| 5   |   | Clock (SPSCK) low time Mas<br>and Slave     | ster           | t <sub>SCKL</sub>                        | 1/2 t <sub>SCK</sub> – 25    | _                                          | ns                                   |

| 6   |   |                                             | aster<br>Slave | t <sub>SI(M)</sub><br>t <sub>SI(S)</sub> | 30<br>30                     | _                                          | ns<br>ns                             |

| 7   |   |                                             | aster<br>Slave | t <sub>HI(M)</sub><br>t <sub>HI(S)</sub> | 30<br>30                     | _                                          | ns<br>ns                             |

| 8   |   | Access time, slave <sup>2</sup>             |                | t <sub>A</sub>                           | 0                            | 40                                         | ns                                   |

| 9   |   | Disable time, slave <sup>3</sup>            |                | t <sub>dis</sub>                         | —                            | 40                                         | ns                                   |

| 10  |   |                                             | aster<br>Slave | t <sub>SO</sub><br>t <sub>SO</sub>       | 25<br>25                     | _                                          | ns<br>ns                             |

| 11  |   |                                             | aster<br>Slave | t <sub>HO</sub><br>t <sub>HO</sub>       | -10<br>-10                   |                                            | ns<br>ns                             |

Table A-14. SPI Electrical Characteristic

<sup>1</sup> All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins. All timing assumes slew rate control disabled and high drive strength enabled for SPI output pins.

$^{2}$  Time to data active from high-impedance state.

<sup>3</sup> Hold time to high-impedance state.

NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFN.

4. COPLANARITY APPLIES TO LEADS, CORNER LEADS, AND DIE ATTACH PAD.

5. MIN METAL GAP SHOULD BE 0.2MM.

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. | MECHANICA   | L OUTLINE      | PRINT VERSION NO  | T TO SCALE |

|---------------------------------------------------------|-------------|----------------|-------------------|------------|

| TITLE: THERMALLY ENHANCED                               | DOCUMENT NO | ): 98ARH99048A | REV: F            |            |

| FLAT NON-LEADED PACKA                                   | CASE NUMBER |                | 05 DEC 2005       |            |

| 48 TERMINAL, 0.5 PITCH (                                | / X / X 1)  | STANDARD: JE   | DEC-MO-220 VKKD-2 | 2          |

NOTES:

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER

- 3. DATUM PLANE H IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS L, M AND N TO BE DETERMINED AT DATUM PLANE H.

5. DIMENSIONS TO BE DETERMINED AT SEATING PLANE T.

6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 PER SIDE. DIMENSIONS DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE H.

/1. DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE DIMENSION TO EXCEED 0.53. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07.

| © FREESCALE SEMICONDUCTOR, INC. MECHANICA        |             | L OUTLINE      | PRINT VERSION NE | IT TO SCALE |

|--------------------------------------------------|-------------|----------------|------------------|-------------|

| TITLE:                                           | DOCUMENT NE | ]: 98ASS23225W | RE∨: D           |             |

| 44 LD LQFP,<br>10 X 10 PKG, 0.8 PITCH, 1.4 THICK |             | CASE NUMBER    | 2: 824D-02       | 26 FEB 2007 |

|                                                  |             | STANDARD: JE   | DEC MS-026 BCB   |             |