Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LQFP                                                                 |

| Supplier Device Package    | 44-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac16cfger |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 2 Pins and Connections**

## 2.3.7 General-Purpose I/O and Peripheral Ports

The remaining pins are shared among general-purpose I/O and on-chip peripheral functions such as timers and serial I/O systems. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pullup devices disabled.

#### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unused pins to outputs so the pins do not float.

For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output." For information about how and when on-chip peripheral systems use these pins, refer to the appropriate chapter from Table 2-2.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. See the Chapter 6, "Parallel Input/Output" chapter for more details.

Pullup enable bits for each input pin control whether on-chip pullup devices are enabled whenever the pin is acting as an input even if it is being controlled by an on-chip peripheral module. When the PTD3, PTD2, and PTG4 pins are controlled by the KBI module and are configured for rising-edge/high-level sensitivity, the pullup enable control bits enable pulldown devices rather than pullup devices. Similarly, when IRQ is configured as the IRQ input and is set to detect rising edges, the pullup enable control bit enables a pulldown device.

#### NOTE

When an alternative function is first enabled it is possible to get a spurious edge to the module, user software should clear out any associated flags before interrupts are enabled. Table 2-1 illustrates the priority if multiple modules are enabled. The highest priority module will have control over the pin. Selecting a higher priority pin function with a lower priority function already enabled can cause spurious edges to the lower priority module. It is recommended that all modules that share a pin be disabled before enabling another module.

Chapter 4 Memory

| Address           | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|-------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x1843            | Reserved      | _      | —      | —      | —      | —      | —      | —      | —      |

| 0x1844            | PTBPE         | R      | R      | R      | R      | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1845            | PTBSE         | R      | R      | R      | R      | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x1846            | PTBDS         | R      | R      | R      | R      | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x1847            | Reserved      | —      | _      |        | _      | _      | _      | _      | —      |

| 0x1848            | PTCPE         | 0      | R      | PTCPE5 | PTCPE4 | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

| 0x1849            | PTCSE         | 0      | R      | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| 0x184A            | PTCDS         | 0      | R      | PTCDS5 | PTCDS4 | PTCDS3 | PTCDS2 | PTCDS1 | PTCDS0 |

| 0x184B            | Reserved      | —      | —      |        | _      | _      |        | _      | —      |

| 0x184C            | PTDPE         | R      | R      | R      | R      | PTDPE3 | PTDPE2 | PTDPE1 | PTDPE0 |

| 0x184D            | PTDSE         | R      | R      | R      | R      | PTDSE3 | PTDSE2 | PTDSE1 | PTDSE0 |

| 0x184E            | PTDDS         | R      | R      | R      | R      | PTDDS3 | PTDDS2 | PTDDS1 | PTDDS0 |

| 0x184F            | Reserved      | —      | —      |        | -      | _      |        | _      | —      |

| 0x1850            | PTEPE         | PTEPE7 | PTEPE6 | PTEPE5 | PTEPE4 | PTEPE3 | PTEPE2 | PTEPE1 | PTEPE0 |

| 0x1851            | PTESE         | PTESE7 | PTESE6 | PTESE5 | PTESE4 | PTESE3 | PTESE2 | PTESE1 | PTESE0 |

| 0x1852            | PTEDS         | PTEDS7 | PTEDS6 | PTEDS5 | PTEDS4 | PTEDS3 | PTEDS2 | PTEDS1 | PTEDS0 |

| 0x1853            | Reserved      | _      | —      |        | -      | —      |        | _      | —      |

| 0x1854            | PTFPE         | R      | PTFPE6 | PTFPE5 | PTFPE4 | R      | R      | PTFPE1 | PTFPE0 |

| 0x1855            | PTFSE         | R      | PTFSE6 | PTFSE5 | PTFSE4 | R      | R      | PTFSE1 | PTFSE0 |

| 0x1856            | PTFDS         | R      | PTFDS6 | PTFDS5 | PTFDS4 | R      | R      | PTFDS1 | PTFDS0 |

| 0x1857            | Reserved      | —      | —      |        | _      | _      |        | _      | —      |

| 0x1858            | PTGPE         | 0      | PTGPE6 | PTGPE5 | PTGPE4 | PTGPE3 | PTGPE2 | PTGPE1 | PTGPE0 |

| 0x1859            | PTGSE         | 0      | PTGSE6 | PTGSE5 | PTGSE4 | PTGSE3 | PTGSE2 | PTGSE1 | PTGSE0 |

| 0x185A            | PTGDS         | 0      | PTGDS6 | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| 0x185B–<br>0x185F | Reserved      | —      |        |        |        |        |        |        | _      |

Table 4-3. High-Page Register Summary (Sheet 3 of 3)

<sup>1</sup> This reserved bit must always be written to 0.

Nonvolatile FLASH registers, shown in Table 4-4, are located in the FLASH memory. These registers include an 8-byte backdoor key which optionally can be used to gain access to secure memory resources. During reset events, the contents of NVPROT and NVOPT in the nonvolatile register area of the FLASH memory are transferred into corresponding FPROT and FOPT working registers in the high-page registers to control security and block protection options.

Chapter 5 Resets, Interrupts, and System Configuration

Either RTI clock source can be used when the MCU is in run, wait or stop3 mode. When using the external oscillator in stop3, it must be enabled in stop (OSCSTEN = 1) and configured for low bandwidth operation (RANGE = 0). Only the internal 1-kHz clock source can be selected to wake the MCU from stop2 mode.

The SRTISC register includes a read-only status flag, a write-only acknowledge bit, and a 3-bit control value (RTIS2:RTIS1:RTIS0) used to disable the clock source to the real-time interrupt or select one of seven wakeup periods. The RTI has a local interrupt enable, RTIE, to allow masking of the real-time interrupt. The RTI can be disabled by writing each bit of RTIS to zeroes, and no interrupts will be generated. See Section 5.9.7, "System Real-Time Interrupt Status and Control Register (SRTISC)," for detailed information about this register.

# 5.8 MCLK Output

The PTC2 pin is shared with the MCLK clock output. Setting the pin enable bit, MPE, causes the PTC2 pin to output a divided version of the internal MCU bus clock. The divide ratio is determined by the MCSEL bits. When MPE is set, the PTC2 pin is forced to operate as an output pin regardless of the state of the port data direction control bit for the pin. If the MCSEL bits are all 0s, the pin is driven low. The slew rate and drive strength for the pin are controlled by PTCSE2 and PTCDS2, respectively. The maximum clock output frequency is limited if slew rate control is enabled, see the electrical chapter for pin rise and fall times with slew rate enabled.

# 5.9 Reset, Interrupt, and System Control Registers and Control Bits

One 8-bit register in the direct page register space and eight 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to the direct-page register summary in Chapter 4, "Memory," of this data sheet for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

## 6.7.12 Port F Pin Control Registers (PTFPE, PTFSE, PTFDS)

In addition to the I/O control, port F pins are controlled by the registers listed below.

|        | 7 | 6      | 5      | 4      | 3 | 2 | 1      | 0      |

|--------|---|--------|--------|--------|---|---|--------|--------|

| R<br>W | R | PTFPE6 | PTFPE5 | PTFPE4 | R | R | PTFPE1 | PTFPE0 |

| Reset  | 0 | 0      | 0      | 0      | 0 | 0 | 0      | 0      |

#### Figure 6-37. Internal Pullup Enable for Port F (PTFPE)<sup>1</sup>

$^{1}\,$  Bits 7, 3 and 2 are reserved bits that must always be written to 0.

| Table 6-28. | PTFPE | Register | Field | Descriptions |

|-------------|-------|----------|-------|--------------|

|-------------|-------|----------|-------|--------------|

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4, 1:0<br>PTFPEn | <ul> <li>Internal Pullup Enable for Port F Bits — Each of these control bits determines if the internal pullup device is enabled for the associated PTF pin. For port F pins that are configured as outputs, these bits have no effect and the internal pullup devices are disabled.</li> <li>Internal pullup device disabled for port F bit n.</li> <li>Internal pullup device enabled for port F bit n.</li> </ul> |

|        | 7 | 6      | 5      | 4      | 3 | 2 | 1      | 0      |

|--------|---|--------|--------|--------|---|---|--------|--------|

| R<br>W | R | PTFSE6 | PTFSE5 | PTFSE4 | R | R | PTFSE1 | PTFSE0 |

| Reset  | 0 | 0      | 0      | 0      | 0 | 0 | 0      | 0      |

#### Figure 6-38. Output Slew Rate Control Enable for Port F (PTFSE)<sup>1</sup>

<sup>1</sup> Bits 7, 3 and 2 are reserved bits that must always be written to 0.

#### Table 6-29. PTFSE Register Field Descriptions

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4, 1:0<br>PTFSEn | <ul> <li>Output Slew Rate Control Enable for Port F Bits — Each of these control bits determine whether output slew rate control is enabled for the associated PTF pin. For port F pins that are configured as inputs, these bits have no effect.</li> <li>O Output slew rate control disabled for port F bit n.</li> <li>1 Output slew rate control enabled for port F bit n.</li> </ul> |

#### Chapter 7 Central Processor Unit (S08CPUV2)

| Source<br>Form                                                                                                  | Operation                                                                                                | Address<br>Mode                                                                                          | Object Code                                                                      | Cycles                                                   | Cyc-by-Cyc<br>Details                                                         |                       | Affect<br>on CCR |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|------------------|--|

| 1 onin                                                                                                          |                                                                                                          | βq                                                                                                       |                                                                                  | ΰ                                                        | Details                                                                       | <b>V</b> 1 1 <b>H</b> | INZC             |  |

| BCC rel                                                                                                         | Branch if Carry Bit Clear<br>(if C = 0)                                                                  | REL                                                                                                      | 24 rr                                                                            | 3                                                        | qqq                                                                           | - 1 1 -               |                  |  |

| BCLR n,opr8a                                                                                                    | Clear Bit n in Memory<br>(Mn ← 0)                                                                        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11 dd<br>13 dd<br>15 dd<br>17 dd<br>19 dd<br>1B dd<br>1D dd<br>1F dd             | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp | - 1 1 -               |                  |  |

| BCS rel                                                                                                         | Branch if Carry Bit Set (if C = 1)<br>(Same as BLO)                                                      | REL                                                                                                      | 25 rr                                                                            | 3                                                        | qqq                                                                           | - 1 1 -               |                  |  |

| BEQ rel                                                                                                         | Branch if Equal (if Z = 1)                                                                               | REL                                                                                                      | 27 rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BGE <i>rel</i>                                                                                                  | Branch if Greater Than or Equal To (if $N \oplus V = 0$ ) (Signed)                                       | REL                                                                                                      | 90 rr                                                                            | 3                                                        | qqq                                                                           | - 1 1 -               |                  |  |

| BGND                                                                                                            | Enter active background if ENBDM=1<br>Waits for and processes BDM commands<br>until GO, TRACE1, or TAGGO | INH                                                                                                      | 82                                                                               | 5+                                                       | fpppp                                                                         | - 1 1 -               |                  |  |

| BGT <i>rel</i>                                                                                                  | Branch if Greater Than (if $Z \mid (N \oplus V) = 0$ ) (Signed)                                          | REL                                                                                                      | 92 rr                                                                            | 3                                                        | qqq                                                                           | - 1 1 -               |                  |  |

| BHCC rel                                                                                                        | Branch if Half Carry Bit Clear (if H = 0)                                                                | REL                                                                                                      | 28 rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BHCS rel                                                                                                        | Branch if Half Carry Bit Set (if H = 1)                                                                  | REL                                                                                                      | 29 rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BHI <i>rel</i>                                                                                                  | Branch if Higher (if $C \mid Z = 0$ )                                                                    | REL                                                                                                      | 22 rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BHS rel                                                                                                         | Branch if Higher or Same (if C = 0)<br>(Same as BCC)                                                     | REL                                                                                                      | 24 rr                                                                            | 3                                                        | qqq                                                                           | - 1 1 -               |                  |  |

| BIH <i>rel</i>                                                                                                  | Branch if IRQ Pin High (if IRQ pin = 1)                                                                  | REL                                                                                                      | 2F rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BIL <i>rel</i>                                                                                                  | Branch if IRQ Pin Low (if IRQ pin = 0)                                                                   | REL                                                                                                      | 2E rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BIT #opr8i<br>BIT opr8a<br>BIT opr16a<br>BIT oprx16,X<br>BIT oprx8,X<br>BIT ,X<br>BIT oprx16,SP<br>BIT oprx8,SP | Bit Test<br>(A) & (M)<br>(CCR Updated but Operands Not Changed)                                          | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                                      | A5 ii<br>B5 dd<br>C5 hh ll<br>D5 ee ff<br>E5 ff<br>F5<br>9E D5 ee ff<br>9E E5 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4                          | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp                      | 011-                  | - ↓ ↓ -          |  |

| BLE rel                                                                                                         | Branch if Less Than or Equal To (if Z I (N $\oplus$ V) = 1) (Signed)                                     | REL                                                                                                      | 93 rr                                                                            | 3                                                        | qqq                                                                           | - 1 1 -               |                  |  |

| BLO rel                                                                                                         | Branch if Lower (if $C = 1$ ) (Same as BCS)                                                              | REL                                                                                                      | 25 rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BLS rel                                                                                                         | Branch if Lower or Same (if $C \mid Z = 1$ )                                                             | REL                                                                                                      | 23 rr                                                                            | 3                                                        | ррр                                                                           | -11-                  |                  |  |

| BLT rel                                                                                                         | Branch if Less Than (if $N \oplus V = 1$ ) (Signed)                                                      | REL                                                                                                      | 91 rr                                                                            | 3                                                        | ррр                                                                           | -11-                  |                  |  |

| BMC rel                                                                                                         | Branch if Interrupt Mask Clear (if I = 0)                                                                | REL                                                                                                      | 2C rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BMI rel                                                                                                         | Branch if Minus (if N = 1)                                                                               | REL                                                                                                      | 2B rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BMS rel                                                                                                         | Branch if Interrupt Mask Set (if I = 1)                                                                  | REL                                                                                                      | 2D rr                                                                            | 3                                                        | ppp                                                                           | -11-                  |                  |  |

| BNE rel                                                                                                         | Branch if Not Equal (if Z = 0)                                                                           | REL                                                                                                      | 26 rr                                                                            | 3                                                        | qqq                                                                           | -11-                  |                  |  |

Table 7-2. . Instruction Set Summary (Sheet 2 of 9)

MC9S08AC16 Series Data Sheet, Rev. 9

| Source<br>Form                                                                                                   | Operation                                                                                                                                                                     | Address<br>Mode                                                                                          | Object Code                                                                                  | Cycles                                    | Cyc-by-Cyc<br>Details                                                | Aff<br>on C           |         |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|-----------------------|---------|

| T OIL                                                                                                            |                                                                                                                                                                               | Pd                                                                                                       |                                                                                              | ර                                         | Details                                                              | <b>V</b> 1 1 <b>H</b> | INZC    |

| BPL rel                                                                                                          | Branch if Plus (if N = 0)                                                                                                                                                     | REL                                                                                                      | 2A rr                                                                                        | 3                                         | ppp                                                                  | -11-                  |         |

| BRA <i>rel</i>                                                                                                   | Branch Always (if I = 1)                                                                                                                                                      | REL                                                                                                      | 20 rr                                                                                        | 3                                         | ppp                                                                  | -11-                  |         |

| BRCLR n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Clear (if (Mn) = 0)                                                                                                                          | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01 dd rr<br>03 dd rr<br>05 dd rr<br>07 dd rr<br>09 dd rr<br>0B dd rr<br>0D dd rr<br>0F dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp          | - 1 1 -               | \$      |

| BRN <i>rel</i>                                                                                                   | Branch Never (if I = 0)                                                                                                                                                       | REL                                                                                                      | 21 rr                                                                                        | 3                                         | ppp                                                                  | -11-                  |         |

| BRSET n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Set (if (Mn) = 1)                                                                                                                            | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00 dd rr<br>02 dd rr<br>04 dd rr<br>06 dd rr<br>08 dd rr<br>0A dd rr<br>0C dd rr<br>0E dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp | - 1 1 -               | \$      |

| BSET <i>n,opr8a</i>                                                                                              | Set Bit <i>n</i> in Memory (Mn ← 1)                                                                                                                                           | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10 dd<br>12 dd<br>14 dd<br>16 dd<br>18 dd<br>1A dd<br>1C dd<br>1E dd                         | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp | - 1 1 -               |         |

| BSR rel                                                                                                          | Branch to Subroutine<br>$PC \leftarrow (PC) + \$0002$<br>push (PCL); $SP \leftarrow (SP) - \$0001$<br>push (PCH); $SP \leftarrow (SP) - \$0001$<br>$PC \leftarrow (PC) + rel$ | REL                                                                                                      | AD rr                                                                                        | 5                                         | qqqaa                                                                | - 1 1 -               |         |

| CBEQ opr8a,rel<br>CBEQA #opr8i,rel<br>CBEQX #opr8i,rel<br>CBEQ oprx8,X+,rel<br>CBEQ ,X+,rel<br>CBEQ oprx8,SP,rel | Compare and Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(X) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$                | DIR<br>IMM<br>IX1+<br>IX+<br>SP1                                                                         | 31 dd rr<br>41 ii rr<br>51 ii rr<br>61 ff rr<br>71 rr<br>9E 61 ff rr                         | 5<br>4<br>5<br>5<br>6                     | rpppp<br>pppp<br>pppp<br>rpppp<br>rfppp<br>prpppp                    | -11-                  |         |

| CLC                                                                                                              | Clear Carry Bit (C $\leftarrow$ 0)                                                                                                                                            | INH                                                                                                      | 98                                                                                           | 1                                         | р                                                                    | -11-                  | 0       |

| CLI                                                                                                              | Clear Interrupt Mask Bit (I $\leftarrow$ 0)                                                                                                                                   | INH                                                                                                      | 9A                                                                                           | 1                                         | р                                                                    | -11-                  | 0       |

| CLR opr8a<br>CLRA<br>CLRX<br>CLRH<br>CLR oprx8,X<br>CLR ,X<br>CLR oprx8,SP                                       | Clear $M \leftarrow \$00$<br>$A \leftarrow \$00$<br>$X \leftarrow \$00$<br>$H \leftarrow \$00$<br>$M \leftarrow \$00$<br>$M \leftarrow \$00$<br>$M \leftarrow \$00$           | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 3F dd<br>4F<br>5F<br>8C<br>6F ff<br>7F<br>9E 6F ff                                           | 5<br>1<br>1<br>5<br>4<br>6                | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp                           | 011-                  | - 0 1 - |

| Table 7-2. | Instruction | Set | Summarv   | (Sheet 3  | of 9) |

|------------|-------------|-----|-----------|-----------|-------|

|            |             | 00. | o annar y | (011001.0 | 0.0,  |

#### Chapter 7 Central Processor Unit (S08CPUV2)

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                   |                       | Affect<br>on CCR |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------|-----------------------|------------------|--|

| 1 Onit                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                    | βq<br>M                                             |                                                                                  | δ                               | Details                                                 | <b>V</b> 1 1 <b>H</b> | INZC             |  |

| SUB #opr8i<br>SUB opr8a<br>SUB opr16a<br>SUB oprx16,X<br>SUB oprx8,X<br>SUB ,X<br>SUB oprx16,SP<br>SUB oprx8,SP | Subtract<br>A $\leftarrow$ (A) – (M)                                                                                                                                                                                                                                                                                                                                                               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A0 ii<br>B0 dd<br>C0 hh ll<br>D0 ee ff<br>E0 ff<br>F0<br>9E D0 ee ff<br>9E E0 ff | 2<br>3<br>4<br>4<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>prpp<br>prpp<br>prpp | ↓ 1 1 -               | - \$ \$ \$       |  |

| SWI                                                                                                             | Software Interrupt<br>PC $\leftarrow$ (PC) + \$0001<br>Push (PCL); SP $\leftarrow$ (SP) - \$0001<br>Push (PCH); SP $\leftarrow$ (SP) - \$0001<br>Push (X); SP $\leftarrow$ (SP) - \$0001<br>Push (A); SP $\leftarrow$ (SP) - \$0001<br>Push (CCR); SP $\leftarrow$ (SP) - \$0001<br>I $\leftarrow$ 1;<br>PCH $\leftarrow$ Interrupt Vector High Byte<br>PCL $\leftarrow$ Interrupt Vector Low Byte | INH                                                 | 83                                                                               | 11                              | sssssvvfppp                                             | - 1 1 -               | 1 – – –          |  |

| ТАР                                                                                                             | Transfer Accumulator to CCR CCR $\leftarrow$ (A)                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 84                                                                               | 1                               | p                                                       | \$1 1\$               | ¢¢¢¢             |  |

| ТАХ                                                                                                             | Transfer Accumulator to X (Index Register Low)<br>$X \leftarrow (A)$                                                                                                                                                                                                                                                                                                                               | INH                                                 | 97                                                                               | 1                               | p                                                       | -11-                  |                  |  |

| ТРА                                                                                                             | Transfer CCR to Accumulator $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 85                                                                               | 1                               | q                                                       | - 1 1 -               |                  |  |

| TST opr8a<br>TSTA<br>TSTX<br>TST oprx8,X<br>TST ,X<br>TST oprx8,SP                                              | Test for Negative or Zero (M) – \$00<br>(A) – \$00<br>(X) – \$00<br>(M) – \$00<br>(M) – \$00<br>(M) – \$00<br>(M) – \$00                                                                                                                                                                                                                                                                           | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3D dd<br>4D<br>5D<br>6D ff<br>7D<br>9E 6D ff                                     | 4<br>1<br>4<br>3<br>5           | rfpp<br>p<br>rfpp<br>rfp<br>prfpp                       | 011-                  | -\$\$-           |  |

| тѕх                                                                                                             | Transfer SP to Index Reg.<br>H:X ← (SP) + \$0001                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 95                                                                               | 2                               | fp                                                      | - 1 1 -               |                  |  |

| ТХА                                                                                                             | Transfer X (Index Reg. Low) to Accumulator $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                      | INH                                                 | 9F                                                                               | 1                               | p                                                       | -11-                  |                  |  |

| Table 7-2. | . Instruction | Set S | Summary | (Sheet 8 | of 9) |

|------------|---------------|-------|---------|----------|-------|

|------------|---------------|-------|---------|----------|-------|

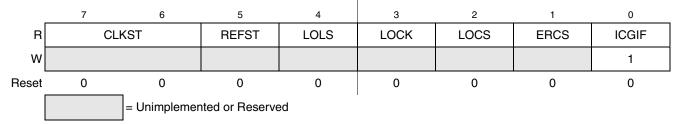

## 8.3.3 ICG Status Register 1 (ICGS1)

#### Figure 8-8. ICG Status Register 1 (ICGS1)

| Table 8-3. ICGS1 | Register | Field Descriptions | 5 |

|------------------|----------|--------------------|---|

|------------------|----------|--------------------|---|

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7:6<br>CLKST | Clock Mode Status — The CLKST bits indicate the current clock mode. The CLKST bits don't update<br>immediately after a write to the CLKS bits due to internal synchronization between clock domains.<br>00 Self-clocked<br>01 FLL engaged, internal reference<br>10 FLL bypassed, external reference<br>11 FLL engaged, external reference                                                                                                                                                                                                                                      |  |  |

| 5<br>REFST   | Reference Clock Status — The REFST bit indicates which clock reference is currently selected by the Reference Select circuit.         0       External Clock selected.         1       Crystal/Resonator selected.                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 4<br>LOLS    | <ul> <li>FLL Loss of Lock Status — The LOLS bit is a sticky indication of FLL lock status.</li> <li>FLL has not unexpectedly lost lock since LOLS was last cleared.</li> <li>FLL has unexpectedly lost lock since LOLS was last cleared, LOLRE determines action taken.FLL has unexpectedly lost lock since LOLS was last cleared, LOLRE determines action taken.</li> </ul>                                                                                                                                                                                                    |  |  |

| 3<br>LOCK    | <ul> <li>FLL Lock Status — The LOCK bit indicates whether the FLL has acquired lock. The LOCK bit is cleared in off, self-clocked, and FLL bypassed modes.</li> <li>FLL is currently unlocked.</li> <li>FLL is currently locked.</li> </ul>                                                                                                                                                                                                                                                                                                                                     |  |  |

| 2<br>LOCS    | Loss Of Clock Status — The LOCS bit is an indication of ICG loss of clock status.         0       ICG has not lost clock since LOCS was last cleared.         1       ICG has lost clock since LOCS was last cleared, LOCRE determines action taken.                                                                                                                                                                                                                                                                                                                            |  |  |

| 1<br>ERCS    | <ul> <li>External Reference Clock Status — The ERCS bit is an indication of whether or not the external reference clock (ICGERCLK) meets the minimum frequency requirement.</li> <li>0 External reference clock is not stable, frequency requirement is not met.</li> <li>1 External reference clock is stable, frequency requirement is met.</li> </ul>                                                                                                                                                                                                                        |  |  |

| 0<br>ICGIF   | <ul> <li>ICG Interrupt Flag — The ICGIF read/write flag is set when an ICG interrupt request is pending. It is cleared by a reset or by reading the ICG status register when ICGIF is set and then writing a logic 1 to ICGIF. If another ICG interrupt occurs before the clearing sequence is complete, the sequence is reset so ICGIF would remain set after the clear sequence was completed for the earlier interrupt. Writing a logic 0 to ICGIF has no effect.</li> <li>0 No ICG interrupt request is pending.</li> <li>1 An ICG interrupt request is pending.</li> </ul> |  |  |

Internal Clock Generator (S08ICGV4)

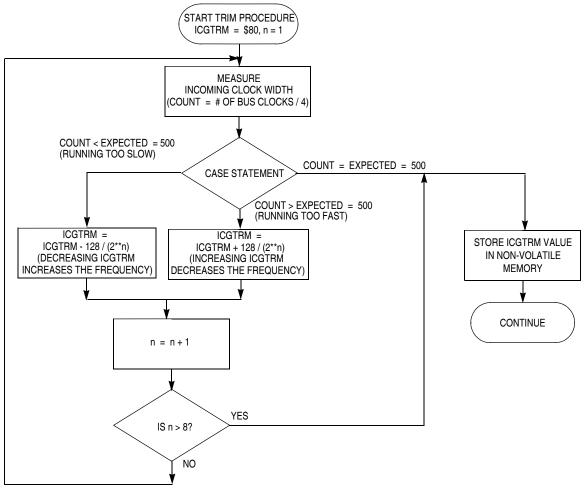

## 8.5.5 Example #4: Internal Clock Generator Trim

The internally generated clock source is guaranteed to have a period  $\pm 25\%$  of the nominal value. In some cases, this may be sufficient accuracy. For other applications that require a tight frequency tolerance, a trimming procedure is provided that will allow a very accurate source. This section outlines one example of trimming the internal oscillator. Many other possible trimming procedures are valid and can be used.

Initial conditions:

- 1) Clock supplied from ATE has 500  $\mu$ sec duty period

- 2) ICG configured for internal reference with 4 MHz bus

Figure 8-17. Trim Procedure

In this particular case, the MCU has been attached to a PCB and the entire assembly is undergoing final test with automated test equipment. A separate signal or message is provided to the MCU operating under user provided software control. The MCU initiates a trim procedure as outlined in Figure 8-17 while the tester supplies a precision reference signal.

If the intended bus frequency is near the maximum allowed for the device, it is recommended to trim using a reduction divisor (R) twice the final value. After the trim procedure is complete, the reduction divisor can be restored. This will prevent accidental overshoot of the maximum clock frequency.

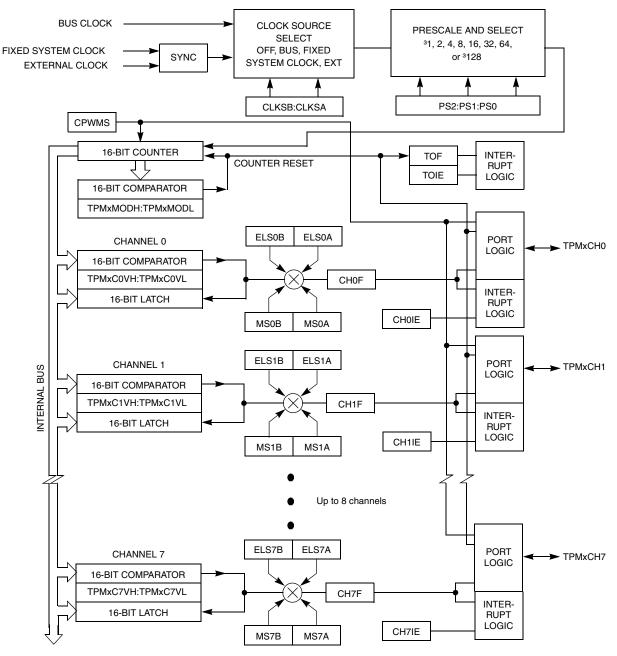

Timer/PWM Module (S08TPMV3)

Figure 10-2. TPM Block Diagram

```

Timer/PWM Module (S08TPMV3)

```

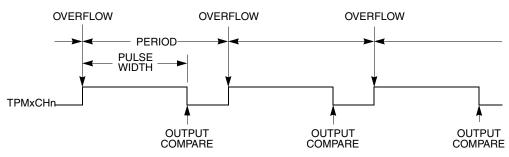

Figure 10-15. PWM Period and Pulse Width (ELSnA=0)

When the channel value register is set to 0x0000, the duty cycle is 0%. 100% duty cycle can be achieved by setting the timer-channel register (TPMxCnVH:TPMxCnVL) to a value greater than the modulus setting. This implies that the modulus setting must be less than 0xFFFF in order to get 100% duty cycle.

Because the TPM may be used in an 8-bit MCU, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers TPMxCnVH and TPMxCnVL, actually write to buffer registers. In edge-aligned PWM mode, values are transferred to the corresponding timer-channel registers according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter then the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

### 10.6.2.4 Center-Aligned PWM Mode

This type of PWM output uses the up/down counting mode of the timer counter (CPWMS=1). The output compare value in TPMxCnVH:TPMxCnVL determines the pulse width (duty cycle) of the PWM signal while the period is determined by the value in TPMxMODH:TPMxMODL. TPMxMODH:TPMxMODL should be kept in the range of 0x0001 to 0x7FFF because values outside this range can produce ambiguous results. ELSnA will determine the polarity of the CPWM output.

```

pulse width = 2 x (TPMxCnVH:TPMxCnVL)

period = 2 x (TPMxMODH:TPMxMODL); TPMxMODH:TPMxMODL=0x0001-0x7FFF

```

If the channel-value register TPMxCnVH:TPMxCnVL is zero or negative (bit 15 set), the duty cycle will be 0%. If TPMxCnVH:TPMxCnVL is a positive value (bit 15 clear) and is greater than the (non-zero) modulus setting, the duty cycle will be 100% because the duty cycle compare will never occur. This implies the usable range of periods set by the modulus register is 0x0001 through 0x7FFE (0x7FFF if you do not need to generate 100% duty cycle). This is not a significant limitation. The resulting period would be much longer than required for normal applications.

TPMxMODH:TPMxMODL=0x0000 is a special case that should not be used with center-aligned PWM mode. When CPWMS=0, this case corresponds to the counter running free from 0x0000 through 0xFFFF, but when CPWMS=1 the counter needs a valid match to the modulus register somewhere other than at 0x0000 in order to change directions from up-counting to down-counting.

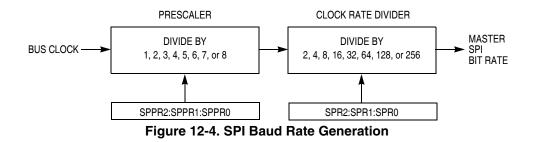

Serial Peripheral Interface (S08SPIV3)

## 12.2 External Signal Description

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control bits. When the SPI is disabled (SPE = 0), these four pins revert to being general-purpose port I/O pins that are not controlled by the SPI.

## 12.2.1 SPSCK — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master, this pin is the serial clock output.

## 12.2.2 MOSI — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data input. If SPC0 = 1 to select single-wire bidirectional mode, and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and slave mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

## 12.2.3 MISO — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data output. If SPC0 = 1 to select single-wire bidirectional mode, and slave mode is selected, this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

# 12.2.4 SS — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as a master and mode fault enable is off (MODFEN = 0), this pin is not used by the SPI and reverts to being a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN = 1, the slave select output enable bit determines whether this pin acts as the mode fault input (SSOE = 0) or as the slave select output (SSOE = 1).

### 13.1.1 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated start signal generation

- Acknowledge bit generation/detection

- Bus busy detection

- General call recognition

- 10-bit address extension

### 13.1.2 Modes of Operation

A brief description of the IIC in the various MCU modes is given here.

- **Run mode** This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module continues to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- **Stop mode** The IIC is inactive in stop3 mode for reduced power consumption. The stop instruction does not affect IIC register states. Stop2 resets the register contents.

### 13.1.3 Block Diagram

Figure 13-2 is a block diagram of the IIC.

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

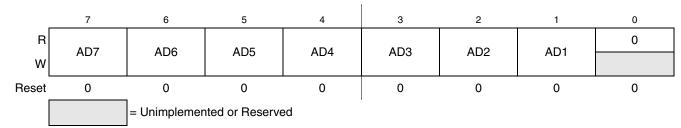

# 13.3.1 IIC Address Register (IIC1A)

Figure 13-3. IIC Address Register (IIC1A)

Table 13-1. IIC1A Field Descriptions

| Field | Description                                                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Slave Address.</b> The AD[7:1] field contains the slave address to be used by the IIC module. This field is used on the 7-bit address scheme and the lower seven bits of the 10-bit address scheme. |

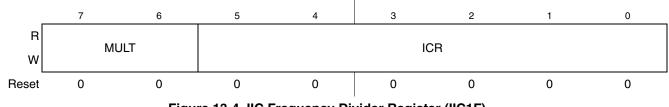

## 13.3.2 IIC Frequency Divider Register (IIC1F)

Figure 13-4. IIC Frequency Divider Register (IIC1F)

Inter-Integrated Circuit (S08IICV2)

## 13.6.2 Address Detect Interrupt

When the calling address matches the programmed slave address (IIC address register) or when the GCAEN bit is set and a general call is received, the IAAS bit in the status register is set. The CPU is interrupted, provided the IICIE is set. The CPU must check the SRW bit and set its Tx mode accordingly.

## 13.6.3 Arbitration Lost Interrupt

The IIC is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, the relative priority of the contending masters is determined by a data arbitration procedure. The IIC module asserts this interrupt when it loses the data arbitration process and the ARBL bit in the status register is set.

Arbitration is lost in the following circumstances:

- SDA sampled as a low when the master drives a high during an address or data transmit cycle.

- SDA sampled as a low when the master drives a high during the acknowledge bit of a data receive cycle.

- A start cycle is attempted when the bus is busy.

- A repeated start cycle is requested in slave mode.

- A stop condition is detected when the master did not request it.

This bit must be cleared by software writing a 1 to it.

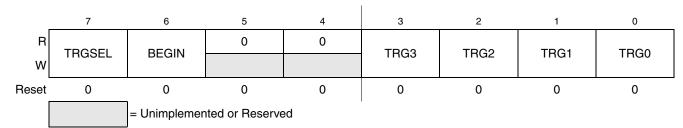

## 15.4.3.8 Debug Trigger Register (DBGT)

This register can be read any time, but may be written only if ARM = 0, except bits 4 and 5 are hard-wired to 0s.

#### Figure 15-8. Debug Trigger Register (DBGT)

#### Table 15-5. DBGT Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>TRGSEL     | <ul> <li>Trigger Type — Controls whether the match outputs from comparators A and B are qualified with the opcode tracking logic in the debug module. If TRGSEL is set, a match signal from comparator A or B must propagate through the opcode tracking logic and a trigger event is only signalled to the FIFO logic if the opcode at the match address is actually executed.</li> <li>0 Trigger on access to compare address (force)</li> <li>1 Trigger if opcode at compare address is executed (tag)</li> </ul> |  |  |

| 6<br>BEGIN      | <ul> <li>Begin/End Trigger Select — Controls whether the FIFO starts filling at a trigger or fills in a circular manner until a trigger ends the capture of information. In event-only trigger modes, this bit is ignored and all debug runs are assumed to be begin traces.</li> <li>0 Data stored in FIFO until trigger (end trace)</li> <li>1 Trigger initiates data storage (begin trace)</li> </ul>                                                                                                             |  |  |

| 3:0<br>TRG[3:0] | Select Trigger Mode — Selects one of nine triggering modes, as described below.         0000 A-only         0001 A OR B         0010 A Then B         0011 Event-only B (store data)         0100 A then event-only B (store data)         0101 A AND B data (full mode)         0110 A AND NOT B data (full mode)         0111 Inside range: A ≤ address ≤ B         1000 Outside range: address < A or address > B         1001 - 1111 (No trigger)                                                                |  |  |

## **B.3** Mechanical Drawings

This following pages contain mechanical specifications for MC9S08AC16 Series package options. See the following tables for the document numbers that correspond to each package type.

| Pin Count | Туре | Designator | Document No. |

|-----------|------|------------|--------------|

| 48        | QFN  | FD         | 98ARH99048A  |

| 44        | LQFP | FG         | 98ASS23225W  |

| 42        | SDIP | В          | 98ASB42767B  |

| 32        | LQFP | FJ         | 98ASH70029A  |

#### Table B-2. MC9S08AC16 and MC9S08AC8 Consumer & Industrial Package Information

| Table B-3 | . S9S08AW16A a | and S9S08AW8A | Automotive | Package Information |

|-----------|----------------|---------------|------------|---------------------|

|-----------|----------------|---------------|------------|---------------------|

| Pin Count | Туре | Designator | Document No. |

|-----------|------|------------|--------------|

| 48        | QFN  | FT         | 98ARH99048A  |

| 44        | LQFP | LD         | 98ASS23225W  |

| 32        | LQFP | LC         | 98ASH70029A  |

Appendix B Ordering Information and Mechanical Drawings

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

MC9S08AC16 Rev. 9, 8/2011 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2007-2011. All rights reserved.