#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 22                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 6x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac16cfje |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SEC01:SEC00 | Description |

|-------------|-------------|

| 0:0         | secure      |

| 0:1         | secure      |

| 1:0         | unsecured   |

| 1:1         | secure      |

Table 4-9. Security States

SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH.

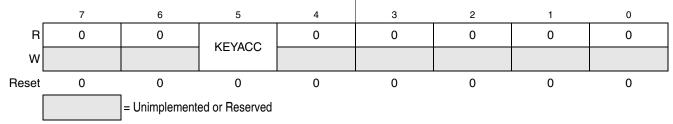

## 4.6.3 FLASH Configuration Register (FCNFG)

Bits 7 through 5 may be read or written at any time. Bits 4 through 0 always read 0 and cannot be written.

### Figure 4-7. FLASH Configuration Register (FCNFG)

| Table 4-10. | FCNFG | Register | Field | Descriptions |

|-------------|-------|----------|-------|--------------|

|-------------|-------|----------|-------|--------------|

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.5, "Security."</li> <li>0 Writes to 0xFFB0–0xFFB7 are interpreted as the start of a FLASH programming or erase command.</li> <li>1 Writes to NVBACKKEY (0xFFB0–0xFFB7) are interpreted as comparison key writes.</li> </ul> |

# Chapter 5 Resets, Interrupts, and System Configuration

# 5.1 Introduction

This chapter discusses basic reset and interrupt mechanisms and the various sources of reset and interrupts in the MC9S08AC16 Series. Some interrupt sources from peripheral modules are discussed in greater detail within other chapters of this data manual. This chapter gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer operating properly (COP) watchdog and real-time interrupt (RTI), are not part of on-chip peripheral systems with their own sections but are part of the system control logic.

# 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation:

- Power-on detection (POR)

- Low voltage detection (LVD) with enable

- External RESET pin

- COP watchdog with enable and two timeout choices

- Illegal opcode

- Illegal address

- Serial command from a background debug host

- Reset status register (SRS) to indicate source of most recent reset

- Separate interrupt vectors for each module (reduces polling overhead) (see Table 5-11)

## 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is loaded from the reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose high-impedance inputs with pullup devices disabled. The I bit in the condition code register (CCR) is set to block maskable interrupts so the user program has a chance to initialize the stack pointer (SP) and system control settings. SP is forced to 0x00FF at reset.

The following sources of reset are available on the MC9S08AC16 Series:

- Power-on reset (POR)

- Low-voltage detect (LVD)

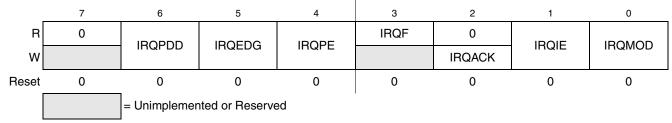

## 5.9.1 Interrupt Pin Request Status and Control Register (IRQSC)

This direct page register includes status and control bits which are used to configure the IRQ function, report status, and acknowledge IRQ events.

### Figure 5-2. Interrupt Request Status and Control Register (IRQSC)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>IRQPDD | Interrupt Request (IRQ) Pull Device Disable— This read/write control bit is used to disable the internal pull-up/pull-down device when the IRQ pin is enabled (IRQPE = 1) allowing for an external device to be used.<br>0 IRQ pull device enabled if IRQPE = 1.<br>1 IRQ pull device disabled if IRQPE = 1.                                                                                                                                                                                                                                                                                                                                         |

| 5<br>IRQEDG | <ul> <li>Interrupt Request (IRQ) Edge Select — This read/write control bit is used to select the polarity of edges or levels on the IRQ pin that cause IRQF to be set. The IRQMOD control bit determines whether the IRQ pin is sensitive to both edges and levels or only edges. When the IRQ pin is enabled as the IRQ input and is configured to detect rising edges, it has a pull-down. When the IRQ pin is enabled as the IRQ input and is configured to detect falling edges, it has a pull-up.</li> <li>IRQ is falling edge or falling edge/low-level sensitive.</li> <li>IRQ is rising edge or rising edge/high-level sensitive.</li> </ul> |

| 4<br>IRQPE  | <ul> <li>IRQ Pin Enable — This read/write control bit enables the IRQ pin function. When this bit is set the IRQ pin can be used as an interrupt request.</li> <li>IRQ pin function is disabled.</li> <li>IRQ pin function is enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3<br>IRQF   | <ul> <li>IRQ Flag — This read-only status bit indicates when an interrupt request event has occurred.</li> <li>0 No IRQ request.</li> <li>1 IRQ event detected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2<br>IRQACK | <b>IRQ Acknowledge</b> — This write-only bit is used to acknowledge interrupt request events (write 1 to clear IRQF). Writing 0 has no meaning or effect. Reads always return 0. If edge-and-level detection is selected (IRQMOD = 1), IRQF cannot be cleared while the IRQ pin remains at its asserted level.                                                                                                                                                                                                                                                                                                                                       |

| 1<br>IRQIE  | <ul> <li>IRQ Interrupt Enable — This read/write control bit determines whether IRQ events generate an interrupt request.</li> <li>0 Interrupt request when IRQF set is disabled (use polling).</li> <li>1 Interrupt requested whenever IRQF = 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

| 0<br>IRQMOD | <ul> <li>IRQ Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level detection. The IRQEDG control bit determines the polarity of edges and levels that are detected as interrupt request events. See Section 5.5.2.2, "Edge and Level Sensitivity" for more details.</li> <li>IRQ event on falling edges or rising edges only.</li> <li>IRQ event on falling edges and low levels or on rising edges and high levels.</li> </ul>                                                                                                                                                                          |

# Chapter 6 Parallel Input/Output

# 6.1 Introduction

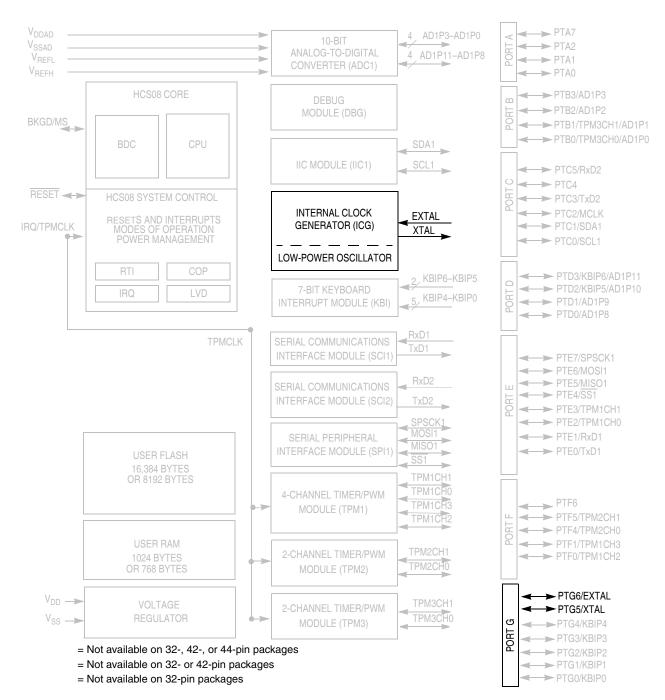

This chapter explains software controls related to parallel input/output (I/O). The MC9S08AC16 has seven I/O ports which include a total of 38 general-purpose I/O pins. See Chapter 2, "Pins and Connections" for more information about the logic and hardware aspects of these pins.

Many of these pins are shared with on-chip peripherals such as timer systems, communication systems, or keyboard interrupts. When these other modules are not controlling the port pins, they revert to general-purpose I/O control.

### NOTE

Not all general-purpose I/O pins are available on all packages. To avoid extra current drain from floating input pins, the user's reset initialization routine in the application program should either enable on-chip pullup devices or change the direction of unconnected pins to outputs so the pins do not float.

**Chapter 6 Parallel Input/Output**

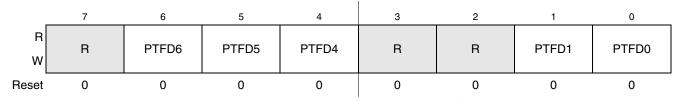

# 6.7.11 Port F I/O Registers (PTFD and PTFDD)

Port F parallel I/O function is controlled by the registers listed below.

### Figure 6-35. Port F Data Register (PTFD)<sup>1</sup>

$^{1}\,$  Bits 7, 3 and 2 are reserved bits that must always be written to 0.

#### Table 6-26. PTFD Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4, 1:0<br>PTFDn | Port F Data Register Bits— For port F pins that are inputs, reads return the logic level on the pin. For port F pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port F pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTFD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

|        | 7 | 6      | 5      | 4      | 3 | 2 | 1      | 0      |

|--------|---|--------|--------|--------|---|---|--------|--------|

| R<br>W | R | PTFDD6 | PTFDD5 | PTFDD4 | R | R | PTFDD1 | PTFDD0 |

| Reset  | 0 | 0      | 0      | 0      | 0 | 0 | 0      | 0      |

Figure 6-36. Data Direction for Port F (PTFDD)<sup>1</sup>

<sup>1</sup> Bits 7, 3 and 2 are reserved bits that must always be written to 0.

### Table 6-27. PTFDD Register Field Descriptions

| Field              | Description                                                                                                                                                                     |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:4, 1:0<br>PTFDDn | <b>Data Direction for Port F Bits</b> — These read/write bits control the direction of port F pins and what is read for PTFD reads.                                             |

|                    | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port F bit n and PTFD reads return the contents of PTFDn.</li> </ol> |

#### Chapter 8 Internal Clock Generator (S08ICGV4)

#### Notes:

- 1. Port pins are software configurable with pullup device if input port.

- Pin contains software configurable pullup/pulldown device if IRQ is enabled (IRQPE = 1). Pulldown is enabled if rising edge detect is selected (IRQEDG = 1)

- 3. IRQ does not have a clamp diode to V<sub>DD</sub>. IRQ should not be driven above V<sub>DD</sub>.

- 4. Pin contains integrated pullup device.

- 5. PTD3, PTD2, and PTG4 contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

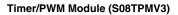

#### Figure 8-2. MC9S08AC16 Block Diagram Highlighting the ICG

MC9S08AC16 Series Data Sheet, Rev. 9

The TPM channels are programmable independently as input capture, output compare, or edge-aligned PWM channels. Alternately, the TPM can be configured to produce CPWM outputs on all channels. When the TPM is configured for CPWMs, the counter operates as an up/down counter; input capture, output compare, and EPWM functions are not practical.

If a channel is configured as input capture, an internal pullup device may be enabled for that channel. The details of how a module interacts with pin controls depends upon the chip implementation because the I/O pins and associated general purpose I/O controls are not part of the module. Refer to the discussion of the I/O port logic in a full-chip specification.

Because center-aligned PWMs are usually used to drive 3-phase AC-induction motors and brushless DC motors, they are typically used in sets of three or six channels.

# 10.4 Signal Description

Table 10-3 shows the user-accessible signals for the TPM. The number of channels may be varied from one to eight. When an external clock is included, it can be shared with the same pin as any TPM channel; however, it could be connected to a separate input pin. Refer to the I/O pin descriptions in full-chip specification for the specific chip implementation.

| Name                 | Function                                                              |

|----------------------|-----------------------------------------------------------------------|

| EXTCLK <sup>1</sup>  | External clock source which may be selected to drive the TPM counter. |

| TPMxCHn <sup>2</sup> | I/O pin associated with TPM channel n                                 |

| Table | 10-3. | Signal | Properties |

|-------|-------|--------|------------|

<sup>1</sup> When preset, this signal can share any channel pin; however depending upon full-chip implementation, this signal could be connected to a separate external pin.

<sup>2</sup> n=channel number (1 to 8)

Refer to documentation for the full-chip for details about reset states, port connections, and whether there is any pullup device on these pins.

TPM channel pins can be associated with general purpose I/O pins and have passive pullup devices which can be enabled with a control bit when the TPM or general purpose I/O controls have configured the associated pin as an input. When no TPM function is enabled to use a corresponding pin, the pin reverts to being controlled by general purpose I/O controls, including the port-data and data-direction registers. Immediately after reset, no TPM functions are enabled, so all associated pins revert to general purpose I/O control.

# 10.4.1 Detailed Signal Descriptions

This section describes each user-accessible pin signal in detail. Although Table 10-3 grouped all channel pins together, any TPM pin can be shared with the external clock source signal. Since I/O pin logic is not part of the TPM, refer to full-chip documentation for a specific derivative for more details about the interaction of TPM pin functions and general purpose I/O controls including port data, data direction, and pullup controls.

### 11.3.5.2 Stop Mode Operation

During all stop modes, clocks to the SCI module are halted.

In stop1 and stop2 modes, all SCI register data is lost and must be re-initialized upon recovery from these two stop modes. No SCI module registers are affected in stop3 mode.

The receive input active edge detect circuit is still active in stop3 mode, but not in stop2.. An active edge on the receive input brings the CPU out of stop3 mode if the interrupt is not masked (RXEDGIE = 1).

Note, because the clocks are halted, the SCI module will resume operation upon exit from stop (only in stop3 mode). Software should ensure stop mode is not entered while there is a character being transmitted out of or received into the SCI module.

### 11.3.5.3 Loop Mode

When LOOPS = 1, the RSRC bit in the same register chooses between loop mode (RSRC = 0) or single-wire mode (RSRC = 1). Loop mode is sometimes used to check software, independent of connections in the external system, to help isolate system problems. In this mode, the transmitter output is internally connected to the receiver input and the RxD pin is not used by the SCI, so it reverts to a general-purpose port I/O pin.

### 11.3.5.4 Single-Wire Operation

When LOOPS = 1, the RSRC bit in the same register chooses between loop mode (RSRC = 0) or single-wire mode (RSRC = 1). Single-wire mode is used to implement a half-duplex serial connection. The receiver is internally connected to the transmitter output and to the TxD pin. The RxD pin is not used and reverts to a general-purpose port I/O pin.

In single-wire mode, the TXDIR bit in SCIxC3 controls the direction of serial data on the TxD pin. When TXDIR = 0, the TxD pin is an input to the SCI receiver and the transmitter is temporarily disconnected from the TxD pin so an external device can send serial data to the receiver. When TXDIR = 1, the TxD pin is an output driven by the transmitter. In single-wire mode, the internal loop back connection from the transmitter to the receiver causes the receiver to receive characters that are sent out by the transmitter.

#### Chapter 12 Serial Peripheral Interface (S08SPIV3)

#### Notes:

- 1. Port pins are software configurable with pullup device if input port.

- Pin contains software configurable pullup/pulldown device if IRQ is enabled (IRQPE = 1). Pulldown is enabled if rising edge detect is selected (IRQEDG = 1)

- 3. IRQ does not have a clamp diode to  $V_{DD}$ . IRQ should not be driven above  $V_{DD}$ .

- 4. Pin contains integrated pullup device.

- 5. PTD3, PTD2, and PTG4 contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

#### Figure 12-1. MC9S08AC16 Block Diagram Highlighting the SPI

MC9S08AC16 Series Data Sheet, Rev. 9

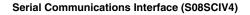

Inter-Integrated Circuit (S08IICV2)

Figure 13-2. IIC Functional Block Diagram

# 13.2 External Signal Description

This section describes each user-accessible pin signal.

### 13.2.1 SCL — Serial Clock Line

The bidirectional SCL is the serial clock line of the IIC system.

### 13.2.2 SDA — Serial Data Line

The bidirectional SDA is the serial data line of the IIC system.

## **13.3 Register Definition**

This section consists of the IIC register descriptions in address order.

Refer to the direct-page register summary in the memory chapter of this document for the absolute address assignments for all IIC registers. This section refers to registers and control bits only by their names. A

Chapter 14 Analog-to-Digital Converter (S08ADC10V1)

| ADCH  | Channel | Input             | Pin Control | ADCH  | Channel            | Input | Pin Control |

|-------|---------|-------------------|-------------|-------|--------------------|-------|-------------|

| 01111 | AD15    | V <sub>REFL</sub> | N/A         | 11111 | module<br>disabled | None  | N/A         |

### Table 14-1. ADC Channel Assignment (continued)

### NOTE

Selecting the internal bandgap channel requires BGBE =1 in SPMSC1 see Section 5.9.8, "System Power Management Status and Control 1 Register (SPMSC1)." For value of bandgap voltage reference see Section A.6, "DC Characteristics."

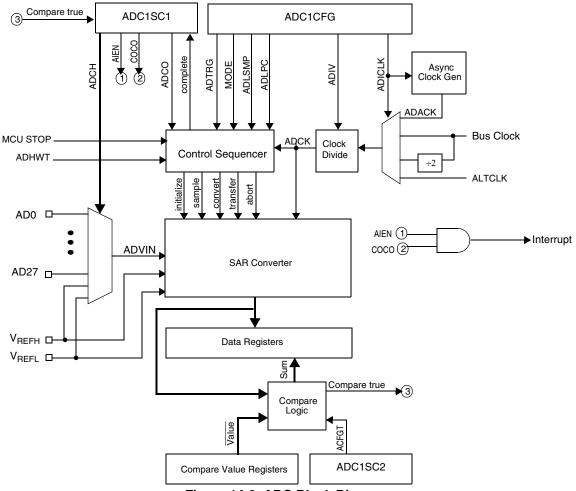

### 14.2.1 Alternate Clock

The ADC module is capable of performing conversions using the MCU bus clock, the bus clock divided by two, the local asynchronous clock (ADACK) within the module, or the alternate clock, ALTCLK. The alternate clock for the MC9S08AC16 Series MCU devices is the external reference clock (ICGERCLK) from the internal clock generator (ICG) module.

Because ICGERCLK is active only while an external clock source is enabled, the ICG must be configured for either FBE or FEE mode (CLKS1 = 1). ICGERCLK must run at a frequency such that the ADC conversion clock (ADCK) runs at a frequency within its specified range ( $f_{ADCK}$ ) after being divided down from the ALTCLK input as determined by the ADIV bits. For example, if the ADIV bits are set up to divide by four, then the minimum frequency for ALTCLK (ICGERCLK) is four times the minimum value for  $f_{ADCK}$  and the maximum frequency is four times the maximum value for  $f_{ADCK}$ . Because of the minimum frequency requirement, when an oscillator circuit is used it must be configured for high range operation (RANGE = 1).

ALTCLK is active while the MCU is in wait mode provided the conditions described above are met. This allows ALTCLK to be used as the conversion clock source for the ADC while the MCU is in wait mode.

ALTCLK cannot be used as the ADC conversion clock source while the MCU is in stop3.

### 14.2.2 Hardware Trigger

The ADC hardware trigger, ADHWT, is output from the real time interrupt (RTI) counter. The RTI counter can be clocked by either ICGERCLK or a nominal 1 kHz clock source within the RTI block. The 1-kHz clock source can be used with the MCU in run, wait, or stop3. With the ICG configured for either FBE or FEE mode, ICGERCLK can be used with the MCU in run or wait.

The period of the RTI is determined by the input clock frequency and the RTIS bits. When the ADC hardware trigger is enabled, a conversion is initiated upon an RTI counter overflow. The RTI counter is a free running counter that generates an overflow at the RTI rate determined by the RTIS bits.

### 14.2.2.1 Analog Pin Enables

The ADC on MC9S08AC16 Series contains only two analog pin enable registers, APCTL1 and APCTL2.

#### Analog-to-Digital Converter (S08ADC10V1)

Figure 14-2. ADC Block Diagram

# 14.3 External Signal Description

The ADC module supports up to 28 separate analog inputs. It also requires four supply/reference/ground connections.

| Name              | Function               |

|-------------------|------------------------|

| AD27–AD0          | Analog Channel inputs  |

| V <sub>REFH</sub> | High reference voltage |

| V <sub>REFL</sub> | Low reference voltage  |

| V <sub>DDAD</sub> | Analog power supply    |

| V <sub>SSAD</sub> | Analog ground          |

### **Table 14-2. Signal Properties**

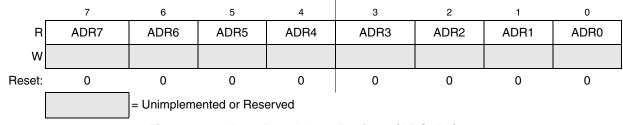

Figure 14-7. Data Result Low Register (ADC1RL)

## 14.4.5 Compare Value High Register (ADC1CVH)

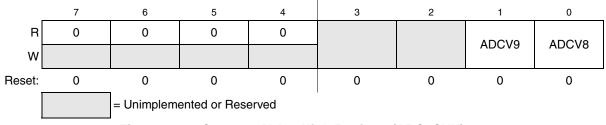

This register holds the upper two bits of the 10-bit compare value. These bits are compared to the upper two bits of the result following a conversion in 10-bit mode when the compare function is enabled. In 8-bit operation, ADC1CVH is not used during compare.

Figure 14-8. Compare Value High Register (ADC1CVH)

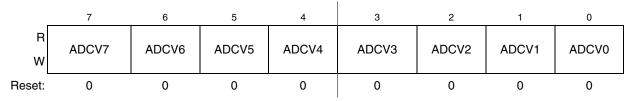

## 14.4.6 Compare Value Low Register (ADC1CVL)

This register holds the lower 8 bits of the 10-bit compare value, or all 8 bits of the 8-bit compare value. Bits ADCV7:ADCV0 are compared to the lower 8 bits of the result following a conversion in either 10-bit or 8-bit mode.

Figure 14-9. Compare Value Low Register(ADC1CVL)

## 14.4.7 Configuration Register (ADC1CFG)

ADC1CFG is used to select the mode of operation, clock source, clock divide, and configure for low power or long sample time.

Analog-to-Digital Converter (S08ADC10V1)

## 14.5.5 Automatic Compare Function

The compare function can be configured to check for either an upper limit or lower limit. After the input is sampled and converted, the result is added to the two's complement of the compare value (ADC1CVH and ADC1CVL). When comparing to an upper limit (ACFGT = 1), if the result is greater-than or equal-to the compare value, COCO is set. When comparing to a lower limit (ACFGT = 0), if the result is less than the compare value, COCO is set. The value generated by the addition of the conversion result and the two's complement of the compare value is transferred to ADC1RH and ADC1RL.

Upon completion of a conversion while the compare function is enabled, if the compare condition is not true, COCO is not set and no data is transferred to the result registers. An ADC interrupt is generated upon the setting of COCO if the ADC interrupt is enabled (AIEN = 1).

### NOTE

The compare function can be used to monitor the voltage on a channel while the MCU is in either wait or stop3 mode. The ADC interrupt will wake the MCU when the compare condition is met.

## 14.5.6 MCU Wait Mode Operation

The WAIT instruction puts the MCU in a lower power-consumption standby mode from which recovery is very fast because the clock sources remain active. If a conversion is in progress when the MCU enters wait mode, it continues until completion. Conversions can be initiated while the MCU is in wait mode by means of the hardware trigger or if continuous conversions are enabled.

The bus clock, bus clock divided by two, and ADACK are available as conversion clock sources while in wait mode. The use of ALTCLK as the conversion clock source in wait is dependent on the definition of ALTCLK for this MCU. Consult the module introduction for information on ALTCLK specific to this MCU.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from wait mode if the ADC interrupt is enabled (AIEN = 1).

## 14.5.7 MCU Stop3 Mode Operation

The STOP instruction is used to put the MCU in a low power-consumption standby mode during which most or all clock sources on the MCU are disabled.

### 14.5.7.1 Stop3 Mode With ADACK Disabled

If the asynchronous clock, ADACK, is not selected as the conversion clock, executing a STOP instruction aborts the current conversion and places the ADC in its idle state. The contents of ADC1RH and ADC1RL are unaffected by stop3 mode. After exiting from stop3 mode, a software or hardware trigger is required to resume conversions.

#### Development Support

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

# 15.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

#### Appendix A Electrical Characteristics and Timing Specifications

maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ).

| Rating                                                                                                                  | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                                          | V <sub>DD</sub>  | -0.3 to + 5.8                 | V    |

| Input voltage                                                                                                           | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1</sup> , <sup>2</sup> , <sup>3</sup> | I <sub>D</sub>   | ± 25                          | mA   |

| Maximum current into V <sub>DD</sub>                                                                                    | I <sub>DD</sub>  | 120                           | mA   |

| Storage temperature                                                                                                     | T <sub>stg</sub> | -55 to +150                   | °C   |

| Maximum junction temperature                                                                                            | Т <sub>Ј</sub>   | 150                           | °C   |

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

- $^2\,$  All functional non-supply pins are internally clamped to V\_{SS} and V\_{DD}

- <sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

### A.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or

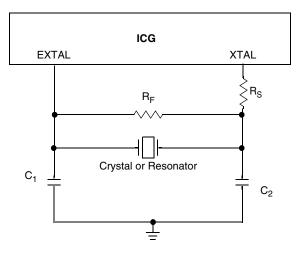

## A.9 Internal Clock Generation Module Characteristics

### Table A-10. ICG DC Electrical Specifications (Temperature Range = -40 to 125°C Ambient)

| Characteristic                                                                                                                                                         | Symbol                           | Min                   | Typ <sup>1</sup>          | Max | Unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|---------------------------|-----|----------|

| Load capacitors                                                                                                                                                        | C <sub>1</sub><br>C <sub>2</sub> | See Note <sup>2</sup> |                           |     |          |

| Feedback resistor<br>Low range (32k to 100 kHz)<br>High range (1M – 16 MHz)                                                                                            | R <sub>F</sub>                   |                       | 10<br>1                   |     | ΜΩ<br>ΜΩ |

| Series resistor<br>Low range<br>Low Gain (HGO = 0)<br>High Gain (HGO = 1)<br>High range<br>Low Gain (HGO = 0)<br>High Gain (HGO = 1)<br>$\geq 8$ MHz<br>4 MHz<br>1 MHz | R <sub>S</sub>                   |                       | 0<br>100<br>0<br>10<br>20 |     | kΩ       |

$^1$  Typical values are based on characterization data at V\_{DD} = 5.0V, 25 ^{\circ}C or is typical recommended value.

<sup>2</sup> See crystal or resonator manufacturer's recommendation.

DETAIL M PREFERED PIN 1 BACKSIDE IDENTIFIER

| VIFW | ROTATED | 90. | CW       |

|------|---------|-----|----------|

| •••  |         | 00  | <u> </u> |

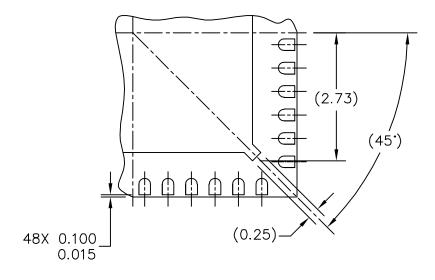

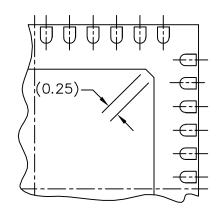

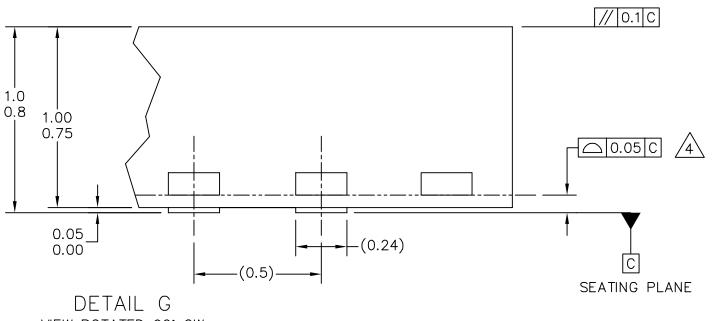

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.             | MECHANICA | L OUTLINE                     | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------------------|-----------|-------------------------------|------------------|-------------|

| TITLE: THERMALLY ENHANCED                                           | QUAD      | DOCUMENT NO                   | ): 98ARH99048A   | REV: F      |

| FLAT NON-LEADED PACKAGE (QFN)<br>48 TERMINAL, 0.5 PITCH (7 X 7 X 1) |           | CASE NUMBER: 1314-05 05 DEC 2 |                  | 05 DEC 2005 |

|                                                                     |           | STANDARD: JEDEC-MO-220 VKKD-2 |                  | 2           |

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION

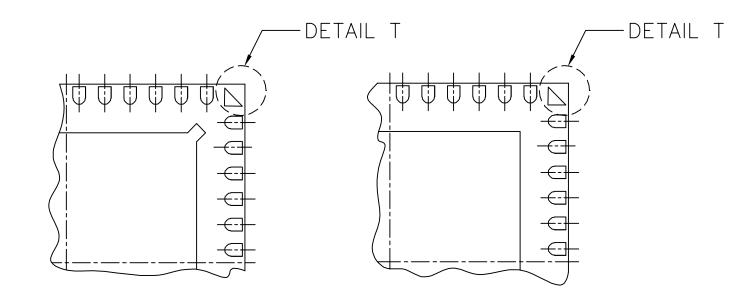

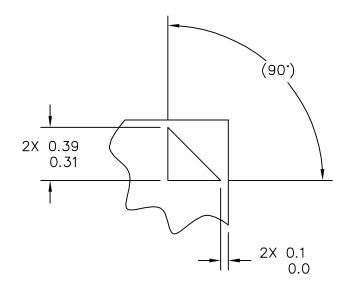

DETAIL T

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA  | L OUTLINE                      | PRINT VERSION NO  | T TO SCALE  |

|---------------------------------------------------------|------------|--------------------------------|-------------------|-------------|

| TITLE: THERMALLY ENHANCED                               | QUAD       | DOCUMENT NO                    | ): 98ARH99048A    | REV: F      |

|                                                         |            | CASE NUMBER: 1314-05 05 DEC 20 |                   | 05 DEC 2005 |

| 48 TERMINAL, 0.5 PITCH (7                               | 7 X 7 X 1) | STANDARD: JE                   | DEC-MO-220 VKKD-2 | 2           |

4.

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS IN MILLIMETERS.

DIMENSION DOES NOT INCLUDE MOLD FLASH. MAXIMUM MOLD FLASH 0.25.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE               | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|------------------------|------------------|-------------|

| TITLE:                                                  |           | DOCUMENT NO            | ): 98ASB42767B   | REV: A      |

| 42 LD PDIP                                              |           | CASE NUMBER: 858–01 24 |                  | 24 OCT 2005 |

|                                                         |           | STANDARD: NO           | N JEDEC          |             |