### NXP USA Inc. - MC9S08AC16CFJER Datasheet

#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I²C, SCI, SPI                                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | 32-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac16cfjer |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Parameter            | Cycles of FCLK | Time if FCLK = 200 kHz |

|----------------------|----------------|------------------------|

| Byte program         | 9              | 45 μs                  |

| Byte program (burst) | 4              | 20 μs <sup>1</sup>     |

| Page erase           | 4000           | 20 ms                  |

| Mass erase           | 20,000         | 100 ms                 |

Table 4-5. Program and Erase Times

<sup>1</sup> Excluding start/end overhead

## 4.4.3 Program and Erase Command Execution

The steps for executing any of the commands are listed below. The FCDIV register must be initialized and any error flags cleared before beginning command execution. The command execution steps are:

Write a data value to an address in the FLASH array. The address and data information from this write is latched into the FLASH interface. This write is a required first step in any command sequence. For erase and blank check commands, the value of the data is not important. For page erase commands, the address may be any address in the 512-byte page of FLASH to be erased. For mass erase and blank check commands, the address can be any address in the FLASH memory. Whole pages of 512 bytes are the smallest block of FLASH that may be erased. In the 60K version, there are two instances where the size of a block that is accessible to the user is less than 512 bytes: the first page following RAM, and the first page following the high page registers. These pages are overlapped by the RAM and high page registers respectively.

### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte which is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 2. Write the command code for the desired command to FCMD. The five valid commands are blank check (0x05), byte program (0x20), burst program (0x25), page erase (0x40), and mass erase (0x41). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag which must be cleared before starting a new command.

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the FLASH memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for

| SEC01:SEC00 | Description |

|-------------|-------------|

| 0:0         | secure      |

| 0:1         | secure      |

| 1:0         | unsecured   |

| 1:1         | secure      |

Table 4-9. Security States

SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH.

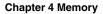

### 4.6.3 FLASH Configuration Register (FCNFG)

Bits 7 through 5 may be read or written at any time. Bits 4 through 0 always read 0 and cannot be written.

### Figure 4-7. FLASH Configuration Register (FCNFG)

| Table 4-10. | FCNFG | Register | Field | Descriptions |

|-------------|-------|----------|-------|--------------|

|-------------|-------|----------|-------|--------------|

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.5, "Security."</li> <li>0 Writes to 0xFFB0–0xFFB7 are interpreted as the start of a FLASH programming or erase command.</li> <li>1 Writes to NVBACKKEY (0xFFB0–0xFFB7) are interpreted as comparison key writes.</li> </ul> |

stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

### 5.5.2.1 IRQ Pin Configuration Options

The IRQ pin enable (IRQPE) control bit in IRQSC must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

The IRQ pin, when enabled, defaults to use an internal pull device (IRQPDD = 0), the device is a pull-up or pull-down depending on the polarity chosen. If the user desires to use an external pull-up or pull-down, the IRQPDD can be written to a 1 to turn off the internal device.

BIH and BIL instructions may be used to detect the level on the IRQ pin when the pin is configured to act as the IRQ input.

### NOTE

This pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$ . The voltage measured on the internally pulled up IRQ pin may be as low as  $V_{DD} - 0.7$  V. The internal gates connected to this pin are pulled all the way to  $V_{DD}$ .

### NOTE

When enabling the IRQ pin for use, the IRQF will be set, and should be cleared prior to enabling the interrupt. When configuring the pin for falling edge and level sensitivity in a 5V system, it is necessary to wait at least 6 cycles between clearing the flag and enabling the interrupt.

### 5.5.2.2 Edge and Level Sensitivity

The IRQMOD control bit reconfigures the detection logic so it detects edge events and pin levels. In the edge and level detection mode, the IRQF status flag becomes set when an edge is detected (when the IRQ pin changes from the deasserted to the asserted level), but the flag is continuously set (and cannot be cleared) as long as the IRQ pin remains at the asserted level.

# 5.5.3 Interrupt Vectors, Sources, and Local Masks

Table 5-2 provides a summary of all interrupt sources. Higher-priority sources are located toward the bottom of the table. The high-order byte of the address for the interrupt service routine is located at the first address in the vector address column, and the low-order byte of the address for the interrupt service routine is located at the next higher address.

When an interrupt condition occurs, an associated flag bit becomes set. If the associated local interrupt enable is 1, an interrupt request is sent to the CPU. Within the CPU, if the global interrupt mask (I bit in the CCR) is 0, the CPU will finish the current instruction, stack the PCL, PCH, X, A, and CCR CPU registers, set the I bit, and then fetch the interrupt vector for the highest priority pending interrupt. Processing then continues in the interrupt service routine.

| Vector<br>Priority | Vector<br>No. | Address<br>(High/Low)          | Vector Name         | Module            | Source                                    | Enable                       | Description                                                           |  |  |

|--------------------|---------------|--------------------------------|---------------------|-------------------|-------------------------------------------|------------------------------|-----------------------------------------------------------------------|--|--|

| Lower              | 29 –<br>31    | 0xFFC0/FFC1 –<br>0xFFC4/0xFFC5 |                     |                   | Unused vec<br>(available for us           |                              | L                                                                     |  |  |

| <b>≜</b>           | 28            | 0xFFC6/FFC7                    | Vtpm3ovf            | TPM3              | TOF                                       | TOIE                         | TPM3 overflow                                                         |  |  |

|                    | 27            | 0xFFC8/FFC9                    | Vtpm3ch1            | TPM3              | CH1F                                      | CH1IE                        | TPM3 channel 1                                                        |  |  |

|                    | 26            | 0xFFCA/FFCB                    | Vtpm3ch0            | TPM3              | CH0F                                      | CH0IF                        | TPM3 channel 0                                                        |  |  |

|                    | 25            | 0xFFCC/FFCD                    | Vrti                | System<br>control | RTIF                                      | RTIE                         | Real-time interrup                                                    |  |  |

|                    | 24            | 0xFFCE/FFCF                    | Viic1               | IIC1              | licif                                     | IICIE                        | IIC1                                                                  |  |  |

|                    | 23            | 0xFFD0/FFD1                    | Vadc1               | ADC1              | COCO                                      | AIEN                         | ADC1                                                                  |  |  |

|                    | 22            | 0xFFD2/FFD3                    | Vkeyboard 1         | KBI               | KBF                                       | KBIE                         | KBI pins                                                              |  |  |

|                    | 21            | 0xFFD4/FFD5                    | Vsci2tx             | SCI2              | TDRE<br>TC                                | TIE<br>TCIE                  | SCI2 transmit                                                         |  |  |

|                    | 20            | 0xFFD6/FFD7                    | Vsci2rx             | SCI2              | IDLE<br>RDRF                              | ILIE<br>RIE                  | SCI2 receive                                                          |  |  |

|                    | 19            | 0xFFD8/FFD9                    | Vsci2err            | SCI2              | OR<br>NF<br>FE<br>PF                      | ORIE<br>NFIE<br>FEIE<br>PFIE | SCI2 error                                                            |  |  |

|                    | 18            | 0xFFDA/FFDB                    | Vsci1tx             | SCI1              | TDRE<br>TC                                | TIE<br>TCIE                  | SCI1 transmit                                                         |  |  |

|                    | 17            | 0xFFDC/FFDD                    | Vsci1rx             | SCI1              | IDLE<br>RDRF                              | ILIE<br>RIE                  | SCI1 receive                                                          |  |  |

|                    | 16            | 0xFFDE/FFDF                    | Vsci1err            | SCI1              | OR<br>NF<br>FE<br>PF                      | ORIE<br>NFIE<br>FEIE<br>PFIE | SCI1 error                                                            |  |  |

|                    | 15            | 0xFFE0/FFE1                    | Vspi1               | SPI1              | SPIF<br>MODF<br>SPTEF                     | SPIE<br>SPIE<br>SPTIE        | SPI1                                                                  |  |  |

|                    | 14            | 0xFFE2/FFE3                    | Vtpm2ovf            | TPM2              | TOF                                       | TOIE                         | TPM2 overflow                                                         |  |  |

|                    | 13            | 0xFFE4/FFE5                    | Vtpm2ch1            | TPM2              | CH1F                                      | CH1IE                        | TPM2 channel 1                                                        |  |  |

|                    | 12            | 0xFFE6/FFE7                    | Vtpm2ch0            | TPM2              | CH0F                                      | CH0IE                        | TPM2 channel 0                                                        |  |  |

|                    | 11            | 0xFFE8/FFE9                    | Vtpm1ovf            | TPM1              | TOF                                       | TOIE                         | TPM1 overflow                                                         |  |  |

|                    | 10            | 0xFFEA/FFEB                    | Unused vector space |                   |                                           |                              |                                                                       |  |  |

|                    | 9             | 0xFFEC/FFED                    |                     |                   | Unused vec                                | tor space                    |                                                                       |  |  |

|                    | 8             | 0xFFEE/FFEF                    | Vtpm1ch3            | TPM1              | CH3F                                      | CH3IE                        | TPM1 channel 3                                                        |  |  |

|                    | 7             | 0xFFF0/FFF1                    | Vtpm1ch2            | TPM1              | CH2F                                      | CH2IE                        | TPM1 channel 2                                                        |  |  |

|                    | 6             | 0xFFF2/FFF3                    | Vtpm1ch1            | TPM1              | CH1F                                      | CH1IE                        | TPM1 channel 1                                                        |  |  |

|                    | 5             | 0xFFF4/FFF5                    | Vtpm1ch0            | TPM1              | CH0F                                      | CH0IE                        | TPM1 channel 0                                                        |  |  |

|                    | 4             | 0xFFF6/FFF7                    | Vicg                | ICG               | ICGIF<br>(LOLS/LOCS)                      | LOLRE/LOCRE                  | ICG                                                                   |  |  |

|                    | 3             | 0xFFF8/FFF9                    | Vlvd                | System<br>control | LVDF                                      | LVDIE                        | Low-voltage detec                                                     |  |  |

|                    | 2             | 0xFFFA/FFFB                    | Virq                | IRQ               | IRQF                                      | IRQIE                        | IRQ pin                                                               |  |  |

| ¥                  | 1             | 0xFFFC/FFFD                    | Vswi                | Core              | SWI<br>Instruction                        | —                            | Software interrup                                                     |  |  |

| Higher             | 0             | 0xFFFE/FFFF                    | Vreset              | System<br>control | COP<br>LVD<br>RESET pin<br>Illegal opcode | COPE<br>LVDRE<br>—<br>—      | Watchdog timer<br>Low-voltage detec<br>External pin<br>Illegal opcode |  |  |

#### Table 5-2. Vector Summary

# 5.6 Low-Voltage Detect (LVD) System

The MC9S08AC16 Series includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and an LVD circuit with a user selectable trip voltage, either high ( $V_{LVDH}$ ) or low ( $V_{LVDL}$ ). The LVD circuit is enabled when LVDE in SPMSC1 is high and the trip voltage is selected by LVDV in SPMSC2. The LVD is disabled upon entering any of the stop modes unless the LVDSE bit is set. If LVDSE and LVDE are both set, then the MCU cannot enter stop2, and the current consumption in stop3 with the LVD enabled will be greater.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the  $V_{POR}$  level, the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the chip in reset until the supply has risen above the  $V_{LVDL}$  level. Both the POR bit and the LVD bit in SRS are set following a POR.

### 5.6.2 LVD Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the level determined by LVDV. The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 LVD Interrupt Operation

When a low voltage condition is detected and the LVD circuit is configured for interrupt operation (LVDE set, LVDIE set, and LVDRE clear), then LVDF will be set and an LVD interrupt will occur.

### 5.6.4 Low-Voltage Warning (LVW)

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching, but is still above, the LVD voltage. The LVW does not have an interrupt associated with it. There are two user selectable trip voltages for the LVW, one high ( $V_{LVWH}$ ) and one low ( $V_{LVWL}$ ). The trip voltage is selected by LVWV in SPMSC2. Setting the LVW trip voltage equal to the LVD trip voltage is not recommended. Typical use of the LVW would be to select  $V_{LVWH}$  and  $V_{LVDL}$ .

# 5.7 Real-Time Interrupt (RTI)

The real-time interrupt function can be used to generate periodic interrupts. The RTI can accept two sources of clocks, the 1-kHz internal clock or an external clock if available. The 1-kHz internal clock source is completely independent of any bus clock source and is used only by the RTI module and, on some MCUs, the COP watchdog. To use an external clock source, it must be available and active. The RTICLKS bit in SRTISC is used to select the RTI clock source.

Chapter 5 Resets, Interrupts, and System Configuration

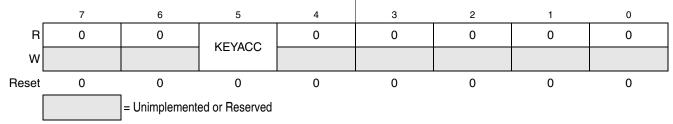

# 5.9.4 System Options Register (SOPT)

This register may be read at any time. Bits 3 and 2 are unimplemented and always read 0. This is a write-once register so only the first write after reset is honored. Any subsequent attempt to write to SOPT (intentionally or unintentionally) is ignored to avoid accidental changes to these sensitive settings. SOPT should be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

#### Figure 5-5. System Options Register (SOPT)

#### Table 5-6. SOPT Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COPE  | <ul> <li>COP Watchdog Enable — This write-once bit defaults to 1 after reset.</li> <li>0 COP watchdog timer disabled.</li> <li>1 COP watchdog timer enabled (force reset on timeout).</li> </ul>                                                                                         |

| 6<br>COPT  | <ul> <li>COP Watchdog Timeout — This write-once bit defaults to 1 after reset.</li> <li>0 Short timeout period selected.</li> <li>1 Long timeout period selected.</li> </ul>                                                                                                             |

| 5<br>STOPE | <ul> <li>Stop Mode Enable — This write-once bit defaults to 0 after reset, which disables stop mode. If stop mode is disabled and a user program attempts to execute a STOP instruction, an illegal opcode reset is forced.</li> <li>0 Stop mode disabled.1Stop mode enabled.</li> </ul> |

### 6.3.4 Port D

| Port D |          | Bit 7 | 6 | 5 | 4 | 3                         | 2                         | 1              | Bit 0          |

|--------|----------|-------|---|---|---|---------------------------|---------------------------|----------------|----------------|

|        | MCU Pin: | R     | R | R | R | PTD3/<br>AD1P11/<br>KBIP6 | PTD2/<br>AD1P10/<br>KBIP5 | PTD1/<br>AD1P9 | PTD0/<br>AD1P8 |

Figure 6-5. Port D Pin Names

Port D pins are general-purpose I/O pins. Parallel I/O function is controlled by the port D data (PTDD) and data direction (PTDDD) registers which are located in page zero register space. The pin control registers, pullup enable (PTDPE), slew rate control (PTDSE), and drive strength select (PTDDS) are located in the high page registers. Refer to Section 6.4, "Parallel I/O Control" for more information about general-purpose I/O control and Section 6.5, "Pin Control" for more information about pin control.

Port D general-purpose I/O are shared with the ADC and KBI. When any of these shared functions is enabled, the direction, input or output, is controlled by the shared function and not by the data direction register of the parallel I/O port. When a pin is shared with both the ADC and a digital peripheral function, the ADC has higher priority. For example, in the case that both the ADC and the KBI are configured to use PTD7 then the pin is controlled by the ADC module.

Refer to Chapter 10, "Timer/PWM (S08TPMV3)" for more information about using port D pins as TPM external clock inputs.

Refer to Chapter 14, "Analog-to-Digital Converter (S08ADC10V1)" for more information about using port D pins as analog inputs.

Refer to Chapter 9, "Keyboard Interrupt (S08KBIV1)" for more information about using port D pins as keyboard inputs.

### 6.3.5 Port E

Port E

|     |      | Bit 7 | 6 | 5 | 4 | 3                | 2 | 1 | Bit 0 |

|-----|------|-------|---|---|---|------------------|---|---|-------|

| MCU | Pin: |       |   |   |   | PTE3/<br>TPM1CH1 |   |   |       |

|     |      |       |   |   |   |                  |   |   |       |

Figure 6-6. Port E Pin Names

Port E pins are general-purpose I/O pins. Parallel I/O function is controlled by the port E data (PTED) and data direction (PTEDD) registers which are located in page zero register space. The pin control registers, pullup enable (PTEPE), slew rate control (PTESE), and drive strength select (PTEDS) are located in the high page registers. Refer to Section 6.4, "Parallel I/O Control" for more information about general-purpose I/O control and Section 6.5, "Pin Control" for more information about pin control.

Port E general-purpose I/O is shared with SCI1, SPI, and TPM1 timer channels. When any of these shared functions is enabled, the direction, input or output, is controlled by the shared function and not by the data direction register of the parallel I/O port. Also, for pins which are configured as outputs by the shared function, the output data is controlled by the shared function and not by the port data register.

**Chapter 6 Parallel Input/Output**

Refer to Chapter 11, "Serial Communications Interface (S08SCIV4)" for more information about using port E pins as SCI pins.

Refer to Chapter 12, "Serial Peripheral Interface (S08SPIV3)" for more information about using port E pins as SPI pins.

Refer to Chapter 10, "Timer/PWM (S08TPMV3)" for more information about using port E pins as TPM channel pins.

### 6.3.6 Port F

Port F

|                              | Bit 7 | 6    | 5                | 4                | 3 | 2 | 1                | Bit 0            |

|------------------------------|-------|------|------------------|------------------|---|---|------------------|------------------|

| MCU Pin:                     | R     | PTF6 | PTF5/<br>TPM2CH1 | PTF4/<br>TPM2CH0 | R | R | PTF1/<br>TPM1CH3 | PTF0/<br>TPM1CH2 |

| Figure 6-7. Port F Pin Names |       |      |                  |                  |   |   |                  |                  |

Port F pins are general-purpose I/O pins. Parallel I/O function is controlled by the port F data (PTFD) and data direction (PTFDD) registers which are located in page zero register space. The pin control registers, pullup enable (PTFPE), slew rate control (PTFSE), and drive strength select (PTFDS) are located in the high page registers. Refer to Section 6.4, "Parallel I/O Control" for more information about general-purpose I/O control and Section 6.5, "Pin Control" for more information about pin control.

Port F general-purpose I/O is shared with TPM1 and TPM2 timer channels. When any of these shared functions is enabled, the direction, input or output, is controlled by the shared function and not by the data direction register of the parallel I/O port. Also, for pins which are configured as outputs by the shared function, the output data is controlled by the shared function and not by the port data register.

Refer to Chapter 10, "Timer/PWM (S08TPMV3)" for more information about using port F pins as TPM channel pins.

# 6.3.7 Port G

| Port G   | Bit 7 | 6 | 5 | 4              | 3 | 2 | 1 | Bit 0 |

|----------|-------|---|---|----------------|---|---|---|-------|

| MCU Pin: | 0     |   |   | PTG4/<br>KBIP4 |   |   |   |       |

### Figure 6-8. Port G Pin Names

Port G pins are general-purpose I/O pins. Parallel I/O function is controlled by the port G data (PTGD) and data direction (PTGDD) registers which are located in page zero register space. The pin control registers, pullup enable (PTGPE), slew rate control (PTGSE), and drive strength select (PTGDS) are located in the high page registers. Refer to Section 6.4, "Parallel I/O Control" for more information about general-purpose I/O control and Section 6.5, "Pin Control" for more information about pin control.

Port G general-purpose I/O is shared with KBI, XTAL, and EXTAL. When a pin is enabled as a KBI input, the pin functions as an input regardless of the state of the associated PTG data direction register bit. When the external oscillator is enabled, PTG5 and PTG6 function as oscillator pins. In this case the associated parallel I/O and pin control registers have no control of the pins.

#### MC9S08AC16 Series Data Sheet, Rev. 9

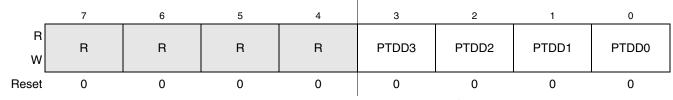

# 6.7.7 Port D I/O Registers (PTDD and PTDDD)

Port D parallel I/O function is controlled by the registers listed below.

### Figure 6-25. Port D Data Register (PTDD)<sup>1</sup>

<sup>1</sup> Bits 7 through 4 are reserved bits that must always be written to 0.

| Table 0-10. FIDD negister Tield Descriptions | Table 6-16. | PTDD Register Field Descriptions |

|----------------------------------------------|-------------|----------------------------------|

|----------------------------------------------|-------------|----------------------------------|

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTDD[3:0] | Port D Data Register Bits — For port D pins that are inputs, reads return the logic level on the pin. For port D pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port D pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTDD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

|        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

| R<br>W | R | R | R | R | PTDDD3 | PTDDD2 | PTDDD1 | PTDDD0 |

| Reset  | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

Figure 6-26. Data Direction for Port D (PTDDD)<sup>1</sup>

<sup>1</sup> Bits 7 through 4 are reserved bits that must always be written to 0.

#### Table 6-17. PTDDD Register Field Descriptions

| Field             | Description                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTDDD[3:0] | <b>Data Direction for Port D Bits</b> — These read/write bits control the direction of port D pins and what is read for PTDD reads.                                              |

|                   | <ul><li>0 Input (output driver disabled) and reads return the pin value.</li><li>1 Output driver enabled for port D bit n and PTDD reads return the contents of PTDDn.</li></ul> |

| Field  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>V | <ul> <li>Two's Complement Overflow Flag — The CPU sets the overflow flag when a two's complement overflow occurs.</li> <li>The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.</li> <li>No overflow</li> <li>1 Overflow</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4<br>H | <ul> <li>Half-Carry Flag — The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C condition code bits to automatically add a correction value to the result from a previous ADD or ADC on BCD operands to correct the result to a valid BCD value.</li> <li>No carry between bits 3 and 4</li> <li>Carry between bits 3 and 4</li> </ul>                                                                                |

| 3      | Interrupt Mask Bit — When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the first instruction of the interrupt service routine is executed.<br>Interrupts are not recognized at the instruction boundary after any instruction that clears I (CLI or TAP). This ensures that the next instruction after a CLI or TAP will always be executed without the possibility of an intervening interrupt, provided I was set.<br>0 Interrupts disabled |

| 2<br>N | <ul> <li>Negative Flag — The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result. Simply loading or storing an 8-bit or 16-bit value causes N to be set if the most significant bit of the loaded or stored value was 1.</li> <li>0 Non-negative result</li> <li>1 Negative result</li> </ul>                                                                                                                                                                                                                                                                     |

| 1<br>Z | <ul> <li>Zero Flag — The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of 0x00 or 0x0000. Simply loading or storing an 8-bit or 16-bit value causes Z to be set if the loaded or stored value was all 0s.</li> <li>0 Non-zero result</li> <li>1 Zero result</li> </ul>                                                                                                                                                                                                                                                                                                                                |

| 0<br>C | <ul> <li>Carry/Borrow Flag — The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.</li> <li>0 No carry out of bit 7</li> <li>1 Carry out of bit 7</li> </ul>                                                                                                                                                                                                                                                                               |

### Table 7-1. CCR Register Field Descriptions

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, all memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte linear address space so a 16-bit binary address can uniquely identify any memory location. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location

Chapter 7 Central Processor Unit (S08CPUV2)

## 7.4.3 Wait Mode Operation

The WAIT instruction enables interrupts by clearing the I bit in the CCR. It then halts the clocks to the CPU to reduce overall power consumption while the CPU is waiting for the interrupt or reset event that will wake the CPU from wait mode. When an interrupt or reset event occurs, the CPU clocks will resume and the interrupt or reset event will be processed normally.

If a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in wait mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in wait mode.

# 7.4.4 Stop Mode Operation

Usually, all system clocks, including the crystal oscillator (when used), are halted during stop mode to minimize power consumption. In such systems, external circuitry is needed to control the time spent in stop mode and to issue a signal to wake up the target MCU when it is time to resume processing. Unlike the earlier M68HC05 and M68HC08 MCUs, the HCS08 can be configured to keep a minimum set of clocks running in stop mode. This optionally allows an internal periodic signal to wake the target MCU from stop mode.

When a host debug system is connected to the background debug pin (BKGD) and the ENBDM control bit has been set by a serial command through the background interface (or because the MCU was reset into active background mode), the oscillator is forced to remain active when the MCU enters stop mode. In this case, if a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in stop mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in stop mode.

Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation chapter for more details.

### 7.4.5 BGND Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

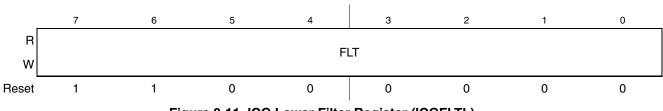

Figure 8-11. ICG Lower Filter Register (ICGFLTL)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>FLT | <b>Filter Value</b> — The FLT bits indicate the current filter value, which controls the DCO frequency. The FLT bits are read only except when the CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. The filter registers show the filter value (FLT). |

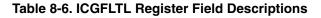

# 8.3.6 ICG Trim Register (ICGTRM)

U = Unaffected by MCU reset

### Figure 8-12. ICG Trim Register (ICGTRM)

### Table 8-7. ICGTRM Register Field Descriptions

| Field | Description                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------|

| 7     | ICG Trim Setting — The TRIM bits control the internal reference generator frequency. They allow a $\pm 25\%$         |

| TRIM  | adjustment of the nominal (POR) period. The bit's effect on period is binary weighted (i.e., bit 1 will adjust twice |

|       | as much as changing bit 0). Increasing the binary value in TRIM will increase the period and decreasing the value    |

|       | will decrease the period.                                                                                            |

# 8.4 Functional Description

This section provides a functional description of each of the five operating modes of the ICG. Also discussed are the loss of clock and loss of lock errors and requirements for entry into each mode. The ICG is very flexible, and in some configurations, it is possible to exceed certain clock specifications. When using the FLL, configure the ICG so that the frequency of ICGDCLK does not exceed its maximum value to ensure proper MCU operation.

Internal Clock Generator (S08ICGV4)

#### Table 8-12. MFD and RFD Decode Table

| 101 | 14 | 101 | ÷32  |

|-----|----|-----|------|

| 110 | 16 | 110 | ÷64  |

| 111 | 18 | 111 | ÷128 |

### 8.5.2 Example #1: External Crystal = 32 kHz, Bus Frequency = 4.19 MHz

In this example, the FLL will be used (in FEE mode) to multiply the external 32 kHz oscillator up to 8.38 MHz to achieve 4.19 MHz bus frequency.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately 8 MHz on ICGOUT, which corresponds to a 4 MHz bus frequency ( $f_{Bus}$ ).

The clock scheme will be FLL engaged, external (FEE). So

Solving for N / R gives:

| N / R = 8.38 MHz /(32 kHz * 64) = 4 ; we can choose N = 4 and R =1 | Eqn. 8-2 |

|--------------------------------------------------------------------|----------|

|--------------------------------------------------------------------|----------|

The values needed in each register to set up the desired operation are:

### ICGC1 = \$38 (%00111000)

| Bit 7    | HGO     | 0  | Configures oscillator for low power                                      |

|----------|---------|----|--------------------------------------------------------------------------|

| Bit 6    | RANGE   | 0  | Configures oscillator for low-frequency range; FLL prescale factor is 64 |

| Bit 5    | REFS    | 1  | Oscillator using crystal or resonator is requested                       |

| Bits 4:3 | CLKS    | 11 | FLL engaged, external reference clock mode                               |

| Bit 2    | OSCSTEN | 0  | Oscillator disabled                                                      |

| Bit 1    | LOCD    | 0  | Loss-of-clock detection enabled                                          |

| Bit 0    |         | 0  | Unimplemented or reserved, always reads zero                             |

### ICGC2 = \$00 (%0000000)

| Bit 7    | LOLRE | 0   | Generates an interrupt request on loss of lock  |

|----------|-------|-----|-------------------------------------------------|

| Bits 6:4 | MFD   | 000 | Sets the MFD multiplication factor to 4         |

| Bit 3    | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bits 2:0 | RFD   | 000 | Sets the RFD division factor to ÷1              |

### ICGS1 = \$xx

This is read only except for clearing interrupt flag

#### ICGS2 = xx

This is read only; should read DCOS = 1 before performing any time critical tasks

### ICGFLTLU/L = \$xx

Only needed in self-clocked mode; FLT will be adjusted by loop to give 8.38 MHz DCO clock Bits 15:12 unused 0000

# ICGTRM = \$xx

Bit 7:0 TRIM

Only need to write when trimming internal oscillator; done in separate operation (see example #4)

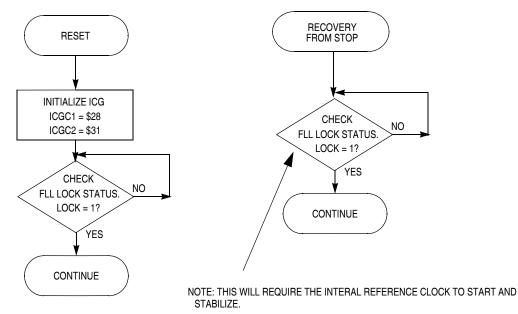

Figure 8-16. ICG Initialization and Stop Recovery for Example #3

#### Analog-to-Digital Converter (S08ADC10V1)

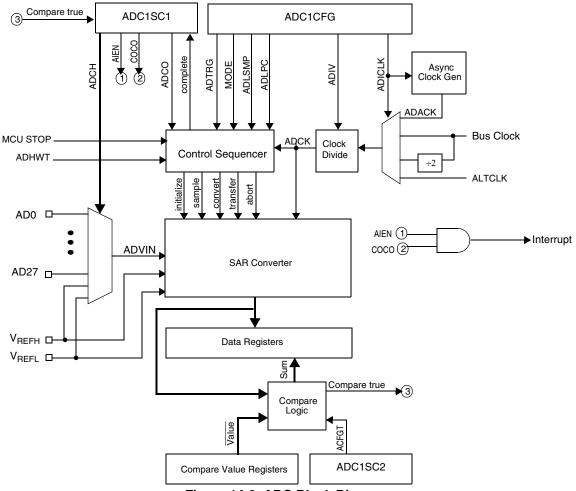

Figure 14-2. ADC Block Diagram

# 14.3 External Signal Description

The ADC module supports up to 28 separate analog inputs. It also requires four supply/reference/ground connections.

| Name              | Function               |  |  |

|-------------------|------------------------|--|--|

| AD27–AD0          | Analog Channel inputs  |  |  |

| V <sub>REFH</sub> | High reference voltage |  |  |

| V <sub>REFL</sub> | Low reference voltage  |  |  |

| V <sub>DDAD</sub> | Analog power supply    |  |  |

| V <sub>SSAD</sub> | Analog ground          |  |  |

#### **Table 14-2. Signal Properties**

Development Support

# 15.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 15-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 15-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

Appendix A Electrical Characteristics and Timing Specifications

# A.5 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model      | Description                 | Symbol | Value | Unit |

|------------|-----------------------------|--------|-------|------|

|            | Series Resistance           | R1     | 1500  | Ω    |

| Human Body | Storage Capacitance         | С      | 100   | pF   |

|            | Number of Pulse per pin     | -      | 3     |      |

|            | Series Resistance           | R1     | 0     | Ω    |

| Machine    | Storage Capacitance         | С      | 200   | pF   |

|            | Number of Pulse per pin     | -      | 3     |      |

| Latch-up   | Minimum input voltage limit |        | - 2.5 | V    |

| μαιση-υρ   | Maximum input voltage limit |        | 7.5   | V    |

Table A-4. ESD and Latch-up Test Conditions

Table A-5. ESD and Latch-Up Protection Characteristics

| Num | С | Rating                                     | Symbol           | Min       | Max | Unit |

|-----|---|--------------------------------------------|------------------|-----------|-----|------|

| 1   | С | Human Body Model (HBM)                     | V <sub>HBM</sub> | $\pm2000$ | _   | V    |

| 2   | С | Machine Model (MM)                         | V <sub>MM</sub>  | ± 200     | -   | V    |

| 3   | С | Charge Device Model (CDM)                  | V <sub>CDM</sub> | ± 500     | _   | V    |

| 4   | С | Latch-up Current at T <sub>A</sub> = 125°C | I <sub>LAT</sub> | ± 100     | _   | mA   |

Appendix A Electrical Characteristics and Timing Specifications

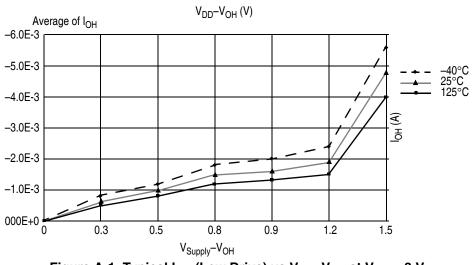

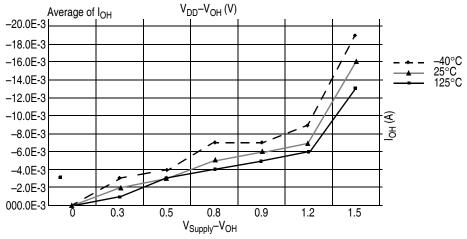

Figure A-2. Typical I<sub>OH</sub> (High Drive) vs  $V_{DD}$ -V<sub>OH</sub> at  $V_{DD}$  = 3 V

Appendix A Electrical Characteristics and Timing Specifications

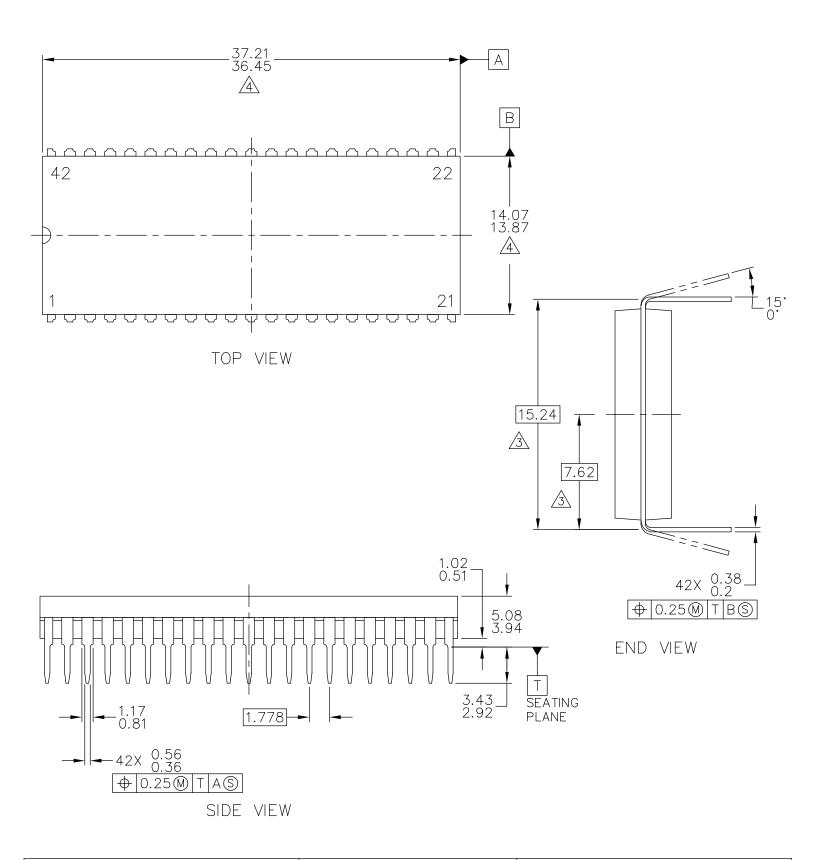

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NOT TO SCALE |  |  |  |

|---------------------------------------------------------|--------------------|----------------------------|--|--|--|

| TITLE:                                                  | DOCUMENT N         | DOCUMENT NO: 98ASB42767B   |  |  |  |

| 42 LD PDIP                                              | CASE NUMBE         | CASE NUMBER: 858-01        |  |  |  |

|                                                         | STANDARD: N        | STANDARD: NON-JEDEC        |  |  |  |