Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 32                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Through Hole                                               |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | 42-PDIP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08ac16mbe |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

| Introduction19                                           |

|----------------------------------------------------------|

| Pins and Connections25                                   |

| Modes of Operation                                       |

| Memory                                                   |

| Resets, Interrupts, and System Configuration63           |

| Parallel Input/Output81                                  |

| Central Processor Unit (S08CPUV2)107                     |

| Internal Clock Generator (S08ICGV4)127                   |

| Keyboard Interrupt (S08KBIV1)153                         |

| Timer/PWM (S08TPMV3)159                                  |

| Serial Communications Interface (S08SCIV4)189            |

| Serial Peripheral Interface (S08SPIV3)209                |

| Inter-Integrated Circuit (S08IICV2)                      |

| Analog-to-Digital Converter (S08ADC10V1)243              |

| Development Support271                                   |

| Electrical Characteristics and Timing Specifications 293 |

| Ordering Information and Mechanical Drawings             |

|                                                          |

Chapter 1 Introduction

Table 1-2 lists the functional versions of the on-chip modules.

| Table 1-2. Versions of On-Chip Modules | Table 1-2. | Versions | of On-Chip | Modules |

|----------------------------------------|------------|----------|------------|---------|

|----------------------------------------|------------|----------|------------|---------|

| Module                          | Version |   |

|---------------------------------|---------|---|

| Analog-to-Digital Converter     | (ADC)   | 1 |

| Internal Clock Generator        | (ICG)   | 4 |

| Inter-Integrated Circuit        | (IIC)   | 2 |

| Keyboard Interrupt              | (KBI)   | 1 |

| Serial Communications Interface | (SCI)   | 4 |

| Serial Peripheral Interface     | (SPI)   | 3 |

| Timer Pulse-Width Modulator     | (TPM)   | 3 |

| Central Processing Unit         | (CPU)   | 2 |

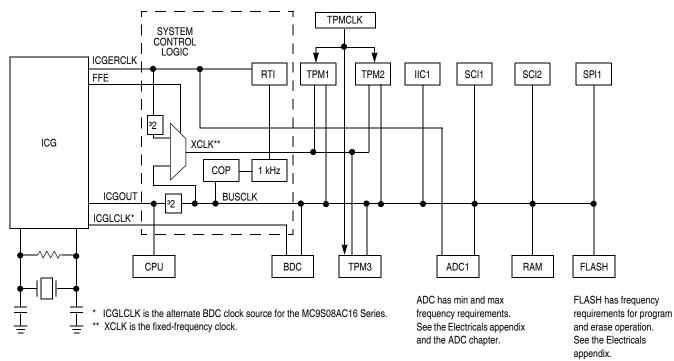

# 1.3 System Clock Distribution

Figure 1-2. System Clock Distribution Diagram

Some of the modules inside the MCU have clock source choices. Figure 1-2 shows a simplified clock connection diagram. The ICG supplies the clock sources:

- ICGOUT is an output of the ICG module. It is one of the following:

- The external crystal oscillator

- An external clock source

- The output of the digitally-controlled oscillator (DCO) in the frequency-locked loop sub-module

**Chapter 2 Pins and Connections**

# 2.3 Recommended System Connections

Figure 2-5 shows pin connections that are common to almost all MC9S08AC16 Series application systems.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FCBEF   | <ul> <li>FLASH Command Buffer Empty Flag — The FCBEF bit is used to launch commands. It also indicates that the command buffer is empty so that a new command sequence can be executed when performing burst programming. The FCBEF bit is cleared by writing a one to it or when a burst program command is transferred to the array for programming. Only burst program commands can be buffered.</li> <li>0 Command buffer is full (not ready for additional commands).</li> <li>1 A new burst program command may be written to the command buffer.</li> </ul>                                                     |

| 6<br>FCCF    | <ul> <li>FLASH Command Complete Flag — FCCF is set automatically when the command buffer is empty and no command is being processed. FCCF is cleared automatically when a new command is started (by writing 1 to FCBEF to register a command). Writing to FCCF has no meaning or effect.</li> <li>0 Command in progress</li> <li>1 All commands complete</li> </ul>                                                                                                                                                                                                                                                   |

| 5<br>FPVIOL  | <ul> <li>Protection Violation Flag — FPVIOL is set automatically when FCBEF is cleared to register a command that attempts to erase or program a location in a protected block (the erroneous command is ignored). FPVIOL is cleared by writing a 1 to FPVIOL.</li> <li>0 No protection violation.</li> <li>1 An attempt was made to erase or program a protected location.</li> </ul>                                                                                                                                                                                                                                 |

| 4<br>FACCERR | <ul> <li>Access Error Flag — FACCERR is set automatically when the proper command sequence is not obeyed exactly (the erroneous command is ignored), if a program or erase operation is attempted before the FCDIV register has been initialized, or if the MCU enters stop while a command was in progress. For a more detailed discussion of the exact actions that are considered access errors, see Section 4.4.5, "Access Errors." FACCERR is cleared by writing a 1 to FACCERR. Writing a 0 to FACCERR has no meaning or effect.</li> <li>0 No access error.</li> <li>1 An access error has occurred.</li> </ul> |

| 2<br>FBLANK  | <ul> <li>FLASH Verified as All Blank (erased) Flag — FBLANK is set automatically at the conclusion of a blank check command if the entire FLASH array was verified to be erased. FBLANK is cleared by clearing FCBEF to write a new valid command. Writing to FBLANK has no meaning or effect.</li> <li>O After a blank check command is completed and FCCF = 1, FBLANK = 0 indicates the FLASH array is not completely erased.</li> <li>1 After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the FLASH array is completely erased (all 0xFF).</li> </ul>                                     |

## 4.6.6 FLASH Command Register (FCMD)

Only five command codes are recognized in normal user modes as shown in Table 4-14. Refer to Section 4.4.3, "Program and Erase Command Execution" for a detailed discussion of FLASH programming and erase operations.

| _     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| R     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| W     | FCMD7 | FCMD6 | FCMD5 | FCMD4 | FCMD3 | FCMD2 | FCMD1 | FCMD0 |

| Reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 4-10. FLASH Command Register (FCMD)

# Chapter 5 Resets, Interrupts, and System Configuration

# 5.1 Introduction

This chapter discusses basic reset and interrupt mechanisms and the various sources of reset and interrupts in the MC9S08AC16 Series. Some interrupt sources from peripheral modules are discussed in greater detail within other chapters of this data manual. This chapter gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer operating properly (COP) watchdog and real-time interrupt (RTI), are not part of on-chip peripheral systems with their own sections but are part of the system control logic.

# 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation:

- Power-on detection (POR)

- Low voltage detection (LVD) with enable

- External RESET pin

- COP watchdog with enable and two timeout choices

- Illegal opcode

- Illegal address

- Serial command from a background debug host

- Reset status register (SRS) to indicate source of most recent reset

- Separate interrupt vectors for each module (reduces polling overhead) (see Table 5-11)

# 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is loaded from the reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose high-impedance inputs with pullup devices disabled. The I bit in the condition code register (CCR) is set to block maskable interrupts so the user program has a chance to initialize the stack pointer (SP) and system control settings. SP is forced to 0x00FF at reset.

The following sources of reset are available on the MC9S08AC16 Series:

- Power-on reset (POR)

- Low-voltage detect (LVD)

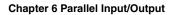

# 6.7.7 Port D I/O Registers (PTDD and PTDDD)

Port D parallel I/O function is controlled by the registers listed below.

#### Figure 6-25. Port D Data Register (PTDD)<sup>1</sup>

<sup>1</sup> Bits 7 through 4 are reserved bits that must always be written to 0.

| Table 0-10. FIDD negister Tield Descriptions | Table 6-16. | PTDD Register Field Descriptions |

|----------------------------------------------|-------------|----------------------------------|

|----------------------------------------------|-------------|----------------------------------|

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTDD[3:0] | Port D Data Register Bits — For port D pins that are inputs, reads return the logic level on the pin. For port D pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port D pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTDD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

|        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

| R<br>W | R | R | R | R | PTDDD3 | PTDDD2 | PTDDD1 | PTDDD0 |

| Reset  | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

Figure 6-26. Data Direction for Port D (PTDDD)<sup>1</sup>

<sup>1</sup> Bits 7 through 4 are reserved bits that must always be written to 0.

#### Table 6-17. PTDDD Register Field Descriptions

| Field             | Description                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTDDD[3:0] | <b>Data Direction for Port D Bits</b> — These read/write bits control the direction of port D pins and what is read for PTDD reads.                                              |

|                   | <ul><li>0 Input (output driver disabled) and reads return the pin value.</li><li>1 Output driver enabled for port D bit n and PTDD reads return the contents of PTDDn.</li></ul> |

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1*.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

## 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

#### MC9S08AC16 Series Data Sheet, Rev. 9

Chapter 7 Central Processor Unit (S08CPUV2)

## 7.4.3 Wait Mode Operation

The WAIT instruction enables interrupts by clearing the I bit in the CCR. It then halts the clocks to the CPU to reduce overall power consumption while the CPU is waiting for the interrupt or reset event that will wake the CPU from wait mode. When an interrupt or reset event occurs, the CPU clocks will resume and the interrupt or reset event will be processed normally.

If a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in wait mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in wait mode.

# 7.4.4 Stop Mode Operation

Usually, all system clocks, including the crystal oscillator (when used), are halted during stop mode to minimize power consumption. In such systems, external circuitry is needed to control the time spent in stop mode and to issue a signal to wake up the target MCU when it is time to resume processing. Unlike the earlier M68HC05 and M68HC08 MCUs, the HCS08 can be configured to keep a minimum set of clocks running in stop mode. This optionally allows an internal periodic signal to wake the target MCU from stop mode.

When a host debug system is connected to the background debug pin (BKGD) and the ENBDM control bit has been set by a serial command through the background interface (or because the MCU was reset into active background mode), the oscillator is forced to remain active when the MCU enters stop mode. In this case, if a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in stop mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in stop mode.

Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation chapter for more details.

## 7.4.5 BGND Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

# 7.5 HCS08 Instruction Set Summary

Table 7-2 provides a summary of the HCS08 instruction set in all possible addressing modes. The table shows operand construction, execution time in internal bus clock cycles, and cycle-by-cycle details for each addressing mode variation of each instruction.

| Source<br>Form                                                                                                            | Operation                                                                               | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                    | Affect<br>on CCR      |                        |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|-----------------------|------------------------|

|                                                                                                                           |                                                                                         | PA                                                  |                                                                                  | ΰ                               | Dotano                                                   | <b>V</b> 1 1 <b>H</b> | INZC                   |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP           | Add with Carry<br>A $\leftarrow$ (A) + (M) + (C)                                        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A9 ii<br>B9 dd<br>C9 hh 11<br>D9 ee ff<br>E9 ff<br>F9<br>9E D9 ee ff<br>9E E9 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rpp<br>rfp<br>prpp<br>prpp   | \$1 1\$               | -\$\$\$                |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP | Add without Carry<br>A ← (A) + (M)                                                      | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AB ii<br>BB dd<br>CB hh 11<br>DB ee ff<br>EB ff<br>FB<br>9E DB ee ff<br>9E EB ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>prpp<br>prpp<br>prpp  | \$1 1\$               | -\$\$\$                |

| AIS #opr8i                                                                                                                | Add Immediate Value (Signed) to<br>Stack Pointer<br>SP $\leftarrow$ (SP) + (M)          | IMM                                                 | A7 ii                                                                            | 2                               | qq                                                       | - 1 1 -               |                        |

| AIX #opr8i                                                                                                                | Add Immediate Value (Signed) to<br>Index Register (H:X)<br>H:X $\leftarrow$ (H:X) + (M) | IMM                                                 | AF ii                                                                            | 2                               | qq                                                       | -11-                  |                        |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP           | Logical AND<br>A ← (A) & (M)                                                            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A4 ii<br>B4 dd<br>C4 hh ll<br>D4 ee ff<br>E4 ff<br>F4<br>9E D4 ee ff<br>9E E4 ff | 2 3 4 4 3 3 5 4                 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | 011-                  | - \$ \$ -              |

| ASL <i>opr8a</i><br>ASLA<br>ASLX<br>ASL <i>oprx8</i> ,X<br>ASL ,X<br>ASL <i>oprx8</i> ,SP                                 | Arithmetic Shift Left                                                                   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp                    | \$11-                 | $ \ddagger$ $\ddagger$ |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                                        | Arithmetic Shift Right                                                                  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37 dd<br>47<br>57<br>67 ff<br>77<br>9E 67 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp               | \$11-                 | - 1 1 1                |

Table 7-2. . Instruction Set Summary (Sheet 1 of 9)

## 11.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Active edge on receive pin

- Break detect supporting LIN

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

- Optional 13-bit break character generation / 11-bit break character detection

- Selectable transmitter output polarity

## 11.1.2 Modes of Operation

See Section 11.3, "Functional Description," For details concerning SCI operation in these modes:

- 8- and 9-bit data modes

- Stop mode operation

- Loop mode

- Single-wire mode

#### Serial Communications Interface (S08SCIV4)

status flag is set. If RDRF was already set indicating the receive data register (buffer) was already full, the overrun (OR) status flag is set and the new data is lost. Because the SCI receiver is double-buffered, the program has one full character time after RDRF is set before the data in the receive data buffer must be read to avoid a receiver overrun.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCIxD. The RDRF flag is cleared automatically by a 2-step sequence which is normally satisfied in the course of the user's program that handles receive data. Refer to Section 11.3.4, "Interrupts and Status Flags" for more details about flag clearing.

## 11.3.3.1 Data Sampling Technique

The SCI receiver uses a 16× baud rate clock for sampling. The receiver starts by taking logic level samples at 16 times the baud rate to search for a falling edge on the RxD serial data input pin. A falling edge is defined as a logic 0 sample after three consecutive logic 1 samples. The 16× baud rate clock is used to divide the bit time into 16 segments labeled RT1 through RT16. When a falling edge is located, three more samples are taken at RT3, RT5, and RT7 to make sure this was a real start bit and not merely noise. If at least two of these three samples are 0, the receiver assumes it is synchronized to a receive character.

The receiver then samples each bit time, including the start and stop bits, at RT8, RT9, and RT10 to determine the logic level for that bit. The logic level is interpreted to be that of the majority of the samples taken during the bit time. In the case of the start bit, the bit is assumed to be 0 if at least two of the samples at RT3, RT5, and RT7 are 0 even if one or all of the samples taken at RT8, RT9, and RT10 are 1s. If any sample in any bit time (including the start and stop bits) in a character frame fails to agree with the logic level for that bit, the noise flag (NF) will be set when the received character is transferred to the receive data buffer.

The falling edge detection logic continuously looks for falling edges, and if an edge is detected, the sample clock is resynchronized to bit times. This improves the reliability of the receiver in the presence of noise or mismatched baud rates. It does not improve worst case analysis because some characters do not have any extra falling edges anywhere in the character frame.

In the case of a framing error, provided the received character was not a break character, the sampling logic that searches for a falling edge is filled with three logic 1 samples so that a new start bit can be detected almost immediately.

In the case of a framing error, the receiver is inhibited from receiving any new characters until the framing error flag is cleared. The receive shift register continues to function, but a complete character cannot transfer to the receive data buffer if FE is still set.

## 11.3.3.2 Receiver Wakeup Operation

Receiver wakeup is a hardware mechanism that allows an SCI receiver to ignore the characters in a message that is intended for a different SCI receiver. In such a system, all receivers evaluate the first character(s) of each message, and as soon as they determine the message is intended for a different receiver, they write logic 1 to the receiver wake up (RWU) control bit in SCIxC2. When RWU bit is set, the status flags associated with the receiver (with the exception of the idle bit, IDLE, when RWUID bit is set) are inhibited from setting, thus eliminating the software overhead for handling the unimportant

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SDA Hold<br>(Stop)<br>Value |

|--------------|----------------|-------------------|------------------------------|-----------------------------|

| 00           | 20             | 7                 | 6                            | 11                          |

| 01           | 22             | 7                 | 7                            | 12                          |

| 02           | 24             | 8                 | 8                            | 13                          |

| 03           | 26             | 8                 | 9                            | 14                          |

| 04           | 28             | 9                 | 10                           | 15                          |

| 05           | 30             | 9                 | 11                           | 16                          |

| 06           | 34             | 10                | 13                           | 18                          |

| 07           | 40             | 10                | 16                           | 21                          |

| 08           | 28             | 7                 | 10                           | 15                          |

| 09           | 32             | 7                 | 12                           | 17                          |

| 0A           | 36             | 9                 | 14                           | 19                          |

| 0B           | 40             | 9                 | 16                           | 21                          |

| 0C           | 44             | 11                | 18                           | 23                          |

| 0D           | 48             | 11                | 20                           | 25                          |

| 0E           | 56             | 13                | 24                           | 29                          |

| 0F           | 68             | 13                | 30                           | 35                          |

| 10           | 48             | 9                 | 18                           | 25                          |

| 11           | 56             | 9                 | 22                           | 29                          |

| 12           | 64             | 13                | 26                           | 33                          |

| 13           | 72             | 13                | 30                           | 37                          |

| 14           | 80             | 17                | 34                           | 41                          |

| 15           | 88             | 17                | 38                           | 45                          |

| 16           | 104            | 21                | 46                           | 53                          |

| 17           | 128            | 21                | 58                           | 65                          |

| 18           | 80             | 9                 | 38                           | 41                          |

| 19           | 96             | 9                 | 46                           | 49                          |

| 1A           | 112            | 17                | 54                           | 57                          |

| 1B           | 128            | 17                | 62                           | 65                          |

| 1C           | 144            | 25                | 70                           | 73                          |

| 1D           | 160            | 25                | 78                           | 81                          |

| 1E           | 192            | 33                | 94                           | 97                          |

| 1F           | 240            | 33                | 118                          | 121                         |

#### Table 13-4. IIC Divider and Hold Values

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SCL Hold<br>(Stop)<br>Value |  |

|--------------|----------------|-------------------|------------------------------|-----------------------------|--|

| 20           | 160            | 17                | 78                           | 81                          |  |

| 21           | 192            | 17                | 94                           | 97                          |  |

| 22           | 224            | 33                | 110                          | 113                         |  |

| 23           | 256            | 33                | 126                          | 129                         |  |

| 24           | 288            | 49                | 142                          | 145                         |  |

| 25           | 320            | 49                | 158                          | 161                         |  |

| 26           | 384            | 65                | 190                          | 193                         |  |

| 27           | 480            | 65                | 238                          | 241                         |  |

| 28           | 320            | 33                | 158                          | 161                         |  |

| 29           | 384            | 33                | 190                          | 193                         |  |

| 2A           | 448            | 65                | 222                          | 225                         |  |

| 2B           | 512            | 65                | 254                          | 257                         |  |

| 2C           | 576            | 97                | 286                          | 289                         |  |

| 2D           | 640            | 97                | 318                          | 321                         |  |

| 2E           | 768            | 129               | 382                          | 385                         |  |

| 2F           | 960            | 129               | 478                          | 481                         |  |

| 30           | 640            | 65                | 318                          | 321                         |  |

| 31           | 768            | 65                | 382                          | 385                         |  |

| 32           | 896            | 129               | 446                          | 449                         |  |

| 33           | 1024           | 129               | 510                          | 513                         |  |

| 34           | 1152           | 193               | 574                          | 577                         |  |

| 35           | 1280           | 193               | 638                          | 641                         |  |

| 36           | 1536           | 257               | 766                          | 769                         |  |

| 37           | 1920           | 257               | 958                          | 961                         |  |

| 38           | 1280           | 129               | 638                          | 641                         |  |

| 39           | 1536           | 129               | 766                          | 769                         |  |

| 3A           | 1792           | 257               | 894                          | 897                         |  |

| 3B           | 2048           | 257               | 1022                         | 1025                        |  |

| 3C           | 2304           | 385               | 1150                         | 1153                        |  |

| 3D           | 2560           | 385               | 1278                         | 1281                        |  |

| 3E           | 3072           | 513               | 1534                         | 1537                        |  |

| 3F           | 3840           | 513               | 1918                         | 1921                        |  |

Inter-Integrated Circuit (S08IICV2)

| Field | Description                                                                                                                                                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data</b> — In master transmit mode, when data is written to the IIC1D, a data transfer is initiated. The most significant bit is sent first. In master receive mode, reading this register initiates receiving of the next byte of data. |

### NOTE

When transitioning out of master receive mode, the IIC mode should be switched before reading the IIC1D register to prevent an inadvertent initiation of a master receive data transfer.

In slave mode, the same functions are available after an address match has occurred.

The TX bit in IIC1C must correctly reflect the desired direction of transfer in master and slave modes for the transmission to begin. For instance, if the IIC is configured for master transmit but a master receive is desired, reading the IIC1D does not initiate the receive.

Reading the IIC1D returns the last byte received while the IIC is configured in master receive or slave receive modes. The IIC1D does not reflect every byte transmitted on the IIC bus, nor can software verify that a byte has been written to the IIC1D correctly by reading it back.

In master transmit mode, the first byte of data written to IIC1D following assertion of MST is used for the address transfer and should comprise of the calling address (in bit 7 to bit 1) concatenated with the required  $R/\overline{W}$  bit (in position bit 0).

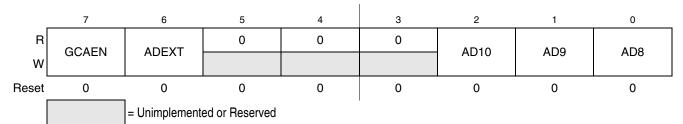

# 13.3.6 IIC Control Register 2 (IIC1C2)

#### Figure 13-8. IIC Control Register (IIC1C2)

#### Table 13-8. IIC1C2 Field Descriptions

| Field           | Description                                                                                                                                                                                     |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>GCAEN      | <ul> <li>General Call Address Enable. The GCAEN bit enables or disables general call address.</li> <li>0 General call address is disabled</li> <li>1 General call address is enabled</li> </ul> |  |  |

| 6<br>ADEXT      | <ul> <li>Address Extension. The ADEXT bit controls the number of bits used for the slave address.</li> <li>0 7-bit address scheme</li> <li>1 10-bit address scheme</li> </ul>                   |  |  |

| 2–0<br>AD[10:8] | Slave Address. The AD[10:8] field contains the upper three bits of the slave address in the 10-bit address scheme. This field is only valid when the ADEXT bit is set.                          |  |  |

#### MC9S08AC16 Series Data Sheet, Rev. 9

Inter-Integrated Circuit (S08IICV2)

## 13.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the start signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a  $R/\overline{W}$  bit. The  $R/\overline{W}$  bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master responds by sending back an acknowledge bit. This is done by pulling the SDA low at the ninth clock (see Figure 13-9).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC reverts to slave mode and operates correctly even if it is being addressed by another master.

## 13.4.1.3 Data Transfer

Before successful slave addressing is achieved, the data transfer can proceed byte-by-byte in a direction specified by the  $R/\overline{W}$  bit sent by the calling master.

All transfers that come after an address cycle are referred to as data transfers, even if they carry sub-address information for the slave device

Each data byte is 8 bits long. Data may be changed only while SCL is low and must be held stable while SCL is high as shown in Figure 13-9. There is one clock pulse on SCL for each data bit, the msb being transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one complete data transfer needs nine clock pulses.

If the slave receiver does not acknowledge the master in the ninth bit time, the SDA line must be left high by the slave. The master interprets the failed acknowledge as an unsuccessful data transfer.

If the master receiver does not acknowledge the slave transmitter after a data byte transmission, the slave interprets this as an end of data transfer and releases the SDA line.

In either case, the data transfer is aborted and the master does one of two things:

- Relinquishes the bus by generating a stop signal.

- Commences a new calling by generating a repeated start signal.

## 13.4.1.4 Stop Signal

The master can terminate the communication by generating a stop signal to free the bus. However, the master may generate a start signal followed by a calling command without generating a stop signal first. This is called repeated start. A stop signal is defined as a low-to-high transition of SDA while SCL at logical 1 (see Figure 13-9).

The master can generate a stop even if the slave has generated an acknowledge at which point the slave must release the bus.

# 13.7 Initialization/Application Information

| 1        | ***                                                                            | Module Initialization (Slave)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1.       | Write: I                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|          |                                                                                | enable or disable general call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| _        |                                                                                | select 10-bit or 7-bit addressing mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 2.       | Write: I                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|          |                                                                                | set the slave address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 3.       | Write: I                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|          |                                                                                | enable IIC and interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|          |                                                                                | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 5.       | Initializ                                                                      | ze RAM variables used to achieve the routine shown in Figure 13-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|          |                                                                                | Module Initialization (Master)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 1.       | Write: I                                                                       | Write: IICF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|          | - to se                                                                        | et the IIC baud rate (example provided in this chapter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 2.       | Write: I                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|          |                                                                                | nable IIC and interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|          | - to e                                                                         | enable IIC and interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 3.       |                                                                                | enable IIC and interrupts<br>ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 3.<br>4. | Initializ                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 4.       | Initializ                                                                      | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>ze RAM variables used to achieve the routine shown in Figure 13-12                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|          | Initializ<br>Initializ<br>Write: I                                             | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>ze RAM variables used to achieve the routine shown in Figure 13-12                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I                                             | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>ze RAM variables used to achieve the routine shown in Figure 13-12<br>IICC1                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I                                             | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>ze RAM variables used to achieve the routine shown in Figure 13-12<br>IICC1                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I                                             | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>ze RAM variables used to achieve the routine shown in Figure 13-12<br>IICC1<br>enable TX<br>Register Model                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en                                  | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>ze RAM variables used to achieve the routine shown in Figure 13-12<br>IICC1<br>enable TX<br>Register Model<br>AD[7:1] 0                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en                                  | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data         ze RAM variables used to achieve the routine shown in Figure 13-12         IICC1         enable TX         Register Model $AD[7:1]$ 0         When addressed as a slave (in slave mode), the module responds to this addressed                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en<br>IICA                          | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data         ze RAM variables used to achieve the routine shown in Figure 13-12         IICC1         enable TX         Register Model $AD[7:1]$ 0         When addressed as a slave (in slave mode), the module responds to this addressed                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en<br>IICA                          | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>ze RAM variables used to achieve the routine shown in Figure 13-12<br>IICC1<br>enable TX<br>Register Model<br>                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en<br>IICA<br>IICF                  | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data<br>ze RAM variables used to achieve the routine shown in Figure 13-12<br>IICC1<br>enable TX<br>Register Model<br>AD[7:1] 0<br>When addressed as a slave (in slave mode), the module responds to this address<br>MULT ICR<br>Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))<br>IICEN IICIE MST TX TXAK RSTA 0 0<br>Module configuration                                                                                                                                                              |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en<br>IICA<br>IICF                  | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data         ze RAM variables used to achieve the routine shown in Figure 13-12         IICC1         enable TX         Register Model                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en<br>IICA<br>IICF<br>IICC1<br>IICS | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data         ze RAM variables used to achieve the routine shown in Figure 13-12         IICC1         enable TX         Register Model $AD[7:1]$ 0         When addressed as a slave (in slave mode), the module responds to this address         MULT       ICR         Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER)))         IICEN       IICIE         Module configuration         TCF       IAAS         BUSY       ARBL       0         SRW       IICIF         RAS       BUSY       ARBL       0 |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en<br>IICA<br>IICF<br>IICC1         | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data         ze RAM variables used to achieve the routine shown in Figure 13-12         IICC1         enable TX         Register Model $\Delta D[7:1]$ 0         When addressed as a slave (in slave mode), the module responds to this address $MULT$ ICR         Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))         IICEN       IICIE         Module configuration         TCF       IAAS         BUSY       ARBL         0       SRW         IICIF       RXAK                                     |  |  |  |  |  |

| 4.       | Initializ<br>Initializ<br>Write: I<br>— to en<br>IICA<br>IICF<br>IICC1<br>IICS | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data         ze RAM variables used to achieve the routine shown in Figure 13-12         IICC1         enable TX         Register Model $AD[7:1]$ 0         When addressed as a slave (in slave mode), the module responds to this address         MULT       ICR         Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER)))         IICEN       IICIE         MOULT       TX         TX       TXAK         Register Model                                                                                   |  |  |  |  |  |

Figure 13-11. IIC Module Quick Start

MC9S08AC16 Series Data Sheet, Rev. 9

#### Analog-to-Digital Converter (S08ADC10V1)

- Average the result by converting the analog input many times in succession and dividing the sum of the results. Four samples are required to eliminate the effect of a 1LSB, one-time error.

- Reduce the effect of synchronous noise by operating off the asynchronous clock (ADACK) and averaging. Noise that is synchronous to ADCK cannot be averaged out.

## 14.7.2.4 Code Width and Quantization Error

The ADC quantizes the ideal straight-line transfer function into 1024 steps (in 10-bit mode). Each step ideally has the same height (1 code) and width. The width is defined as the delta between the transition points to one code and the next. The ideal code width for an N bit converter (in this case N can be 8 or 10), defined as 1LSB, is:

#### $1LSB = (V_{REFH} - V_{REFL}) / 2^{N}$ Eqn. 14-2

There is an inherent quantization error due to the digitization of the result. For 8-bit or 10-bit conversions the code will transition when the voltage is at the midpoint between the points where the straight line transfer function is exactly represented by the actual transfer function. Therefore, the quantization error will be  $\pm 1/2$ LSB in 8- or 10-bit mode. As a consequence, however, the code width of the first (\$000) conversion is only 1/2LSB and the code width of the last (\$FF or \$3FF) is 1.5LSB.

## 14.7.2.5 Linearity Errors

The ADC may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the system should be aware of them because they affect overall accuracy. These errors are:

- Zero-scale error (E<sub>ZS</sub>) (sometimes called offset) This error is defined as the difference between the actual code width of the first conversion and the ideal code width (1/2LSB). Note, if the first conversion is \$001, then the difference between the actual \$001 code width and its ideal (1LSB) is used.

- Full-scale error  $(E_{FS})$  This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5LSB). Note, if the last conversion is \$3FE, then the difference between the actual \$3FE code width and its ideal (1LSB) is used.

- Differential non-linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral non-linearity (INL) This error is defined as the highest-value the (absolute value of the) running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total unadjusted error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function, and therefore includes all forms of error.

## 14.7.2.6 Code Jitter, Non-Monotonicity and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the

Development Support

# 15.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 15-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

## **Coding Structure Nomenclature**

This nomenclature is used in Table 15-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

Development Support

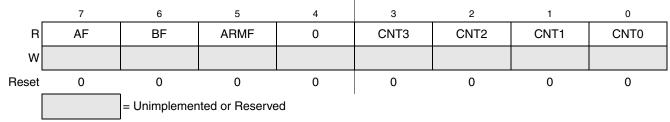

# 15.4.3.9 Debug Status Register (DBGS)

This is a read-only status register.

#### Figure 15-9. Debug Status Register (DBGS)

#### Table 15-6. DBGS Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>AF         | <ul> <li>Trigger Match A Flag — AF is cleared at the start of a debug run and indicates whether a trigger match A condition was met since arming.</li> <li>0 Comparator A has not matched</li> <li>1 Comparator A match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 6<br>BF         | <ul> <li>Trigger Match B Flag — BF is cleared at the start of a debug run and indicates whether a trigger match B condition was met since arming.</li> <li>0 Comparator B has not matched</li> <li>1 Comparator B match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 5<br>ARMF       | <ul> <li>Arm Flag — While DBGEN = 1, this status bit is a read-only image of ARM in DBGC. This bit is set by writing 1 to the ARM control bit in DBGC (while DBGEN = 1) and is automatically cleared at the end of a debug run. A debug run is completed when the FIFO is full (begin trace) or when a trigger event is detected (end trace). A debug run can also be ended manually by writing 0 to ARM or DBGEN in DBGC.</li> <li>0 Debugger not armed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                                             |  |  |  |  |

| 3:0<br>CNT[3:0] | FIFO Valid Count — These bits are cleared at the start of a debug run and indicate the number of words of valid data in the FIFO at the end of a debug run. The value in CNT does not decrement as data is read out of the FIFO. The external debug host is responsible for keeping track of the count as information is read out of the FIFO. 0000 Number of valid words in FIFO = No valid data 0001 Number of valid words in FIFO = 1 0010 Number of valid words in FIFO = 2 0011 Number of valid words in FIFO = 3 0100 Number of valid words in FIFO = 4 0101 Number of valid words in FIFO = 5 0110 Number of valid words in FIFO = 6 0111 Number of valid words in FIFO = 7 1000 Number of valid words in FIFO = 8 |  |  |  |  |

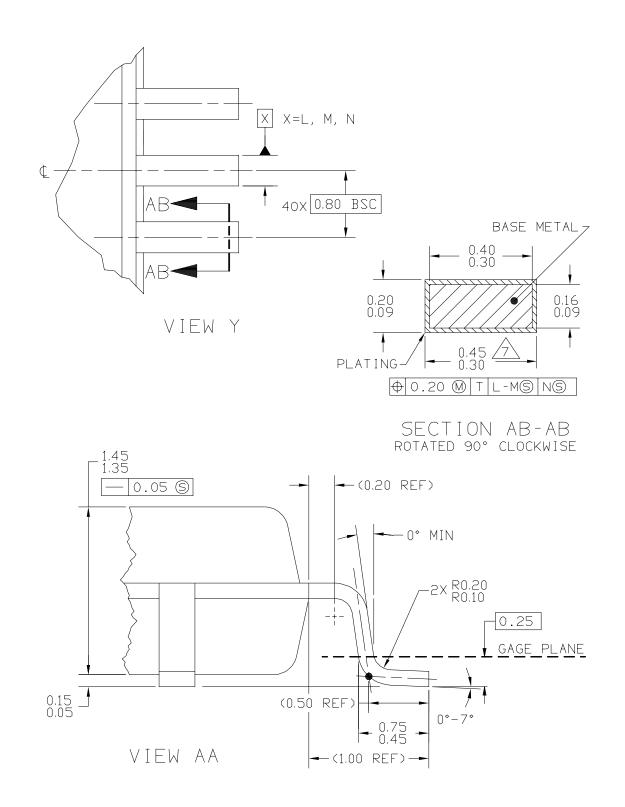

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.    |              | L OUTLINE            | PRINT VERSION NOT TO SCALE |             |

|------------------------------------------------------------|--------------|----------------------|----------------------------|-------------|

| TITLE:<br>44 LD LQFP,<br>10 X 10 PKG, 0.8 PITCH, 1.4 THICK |              | DOCUMENT NE          | : 98ASS23225W              | RE∨: D      |

|                                                            |              | CASE NUMBER: 824D-02 |                            | 26 FEB 2007 |

|                                                            | STANDARD: JE | DEC MS-026 BCB       |                            |             |