Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 38                                                         |

| Program Memory Size        | 8KB (8K x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 768 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 8x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                       |

| Supplier Device Package    | 48-QFN-EP (7x7)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08ac8cfde |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **MC9S08AC16 Series Features**

### MC9S08AC16 Series Devices

- Consumer & Industrial

- MC9S08AC16

- MC9S08AC8

- Automotive

- MC9S08AW16A

- MC9S08AW8A

### 8-Bit HCS08 Central Processor Unit (CPU)

- 40-MHz HCS08 CPU (central processor unit)

- 20-MHz internal bus frequency

- HC08 instruction set with added BGND instruction

- Background debugging system

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints in on-chip debug module)

- Debug module containing two comparators and nine trigger modes. Eight deep FIFO for storing change-of-flow addresses and event-only data. Debug module supports both tag and force breakpoints.

- Support for up to 32 interrupt/reset sources

### **Memory Options**

- Up to 16 KB of on-chip in-circuit programmable FLASH memory with block protection and security options

- Up to 1 KB of on-chip RAM

### **Clock Source Options**

Clock source options include crystal, resonator, external clock, or internally generated clock with precision NVM trimming

### **System Protection**

- Optional computer operating properly (COP) reset with option to run from independent internal clock source or bus clock

- Low-voltage detection with reset or interrupt

- Illegal opcode detection with reset

- Illegal address detection with reset

### **Power-Saving Modes**

Wait plus two stops

### Peripherals

- ADC 8-channel, 10-bit analog-to-digital converter with automatic compare function

- **SCI** Two serial communications interface modules with optional 13-bit break

- SPI Serial peripheral interface module

- IIC Inter-integrated circuit bus module to operate at up to 100 kbps with maximum bus loading; capable of higher baud rates with reduced loading

- **Timers** Three 16-bit timer/pulse-width modulator (TPM) modules — Two 2-channel and one 4-channel; each has selectable input capture, output compare, and edge-aligned PWM capability on each channel. Each timer module may be configured for buffered, centered PWM (CPWM) on all channels

- **KBI** 7-pin keyboard interrupt module

### Input/Output

- Up to 38 general-purpose input/output (I/O) pins

- Software selectable pullups on ports when used as inputs

- Software selectable slew rate control on ports when used as outputs

- Software selectable drive strength on ports when used as outputs

- Master reset pin and power-on reset (POR)

- Internal pullup on RESET, IRQ, and BKGD/MS pins to reduce customer system cost

### **Package Options**

- 48-pin quad flat no-lead package (QFN)

- 44-pin low-profile quad flat package (LQFP)

- 42-pin shrink dual-in-line package (SDIP)

- 32-pin low-profile quad flat package (LQFP)

# MC9S08AC16 Series Data Sheet

Covers MC9S08AC16 MC9S08AC8 MC9S08AW16A MC9S08AW8A

> MC9S08AC16 Rev. 9 8/2011

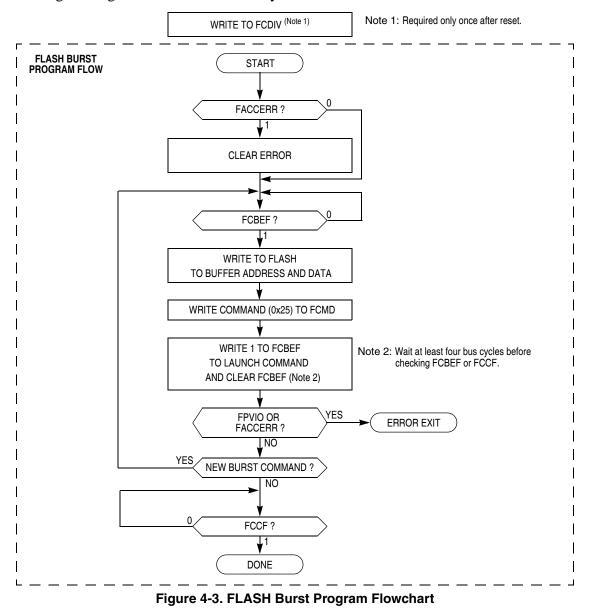

• The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst program time provided that the conditions above are met. In the case the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

**Chapter 6 Parallel Input/Output**

Refer to Chapter 11, "Serial Communications Interface (S08SCIV4)" for more information about using port E pins as SCI pins.

Refer to Chapter 12, "Serial Peripheral Interface (S08SPIV3)" for more information about using port E pins as SPI pins.

Refer to Chapter 10, "Timer/PWM (S08TPMV3)" for more information about using port E pins as TPM channel pins.

# 6.3.6 Port F

Port F

|                              | Bit 7 | 6    | 5                | 4                | 3 | 2 | 1                | Bit 0            |

|------------------------------|-------|------|------------------|------------------|---|---|------------------|------------------|

| MCU Pin:                     | R     | PTF6 | PTF5/<br>TPM2CH1 | PTF4/<br>TPM2CH0 | R | R | PTF1/<br>TPM1CH3 | PTF0/<br>TPM1CH2 |

| Figure 6-7. Port F Pin Names |       |      |                  |                  |   |   |                  |                  |

Port F pins are general-purpose I/O pins. Parallel I/O function is controlled by the port F data (PTFD) and data direction (PTFDD) registers which are located in page zero register space. The pin control registers, pullup enable (PTFPE), slew rate control (PTFSE), and drive strength select (PTFDS) are located in the high page registers. Refer to Section 6.4, "Parallel I/O Control" for more information about general-purpose I/O control and Section 6.5, "Pin Control" for more information about pin control.

Port F general-purpose I/O is shared with TPM1 and TPM2 timer channels. When any of these shared functions is enabled, the direction, input or output, is controlled by the shared function and not by the data direction register of the parallel I/O port. Also, for pins which are configured as outputs by the shared function, the output data is controlled by the shared function and not by the port data register.

Refer to Chapter 10, "Timer/PWM (S08TPMV3)" for more information about using port F pins as TPM channel pins.

# 6.3.7 Port G

| Port G   | Bit 7 | 6 | 5 | 4              | 3 | 2 | 1 | Bit 0 |

|----------|-------|---|---|----------------|---|---|---|-------|

| MCU Pin: | 0     |   |   | PTG4/<br>KBIP4 |   |   |   |       |

### Figure 6-8. Port G Pin Names

Port G pins are general-purpose I/O pins. Parallel I/O function is controlled by the port G data (PTGD) and data direction (PTGDD) registers which are located in page zero register space. The pin control registers, pullup enable (PTGPE), slew rate control (PTGSE), and drive strength select (PTGDS) are located in the high page registers. Refer to Section 6.4, "Parallel I/O Control" for more information about general-purpose I/O control and Section 6.5, "Pin Control" for more information about pin control.

Port G general-purpose I/O is shared with KBI, XTAL, and EXTAL. When a pin is enabled as a KBI input, the pin functions as an input regardless of the state of the associated PTG data direction register bit. When the external oscillator is enabled, PTG5 and PTG6 function as oscillator pins. In this case the associated parallel I/O and pin control registers have no control of the pins.

Chapter 6 Parallel Input/Output

|       | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     | 0 | PTGSE6 | PTGSE5 | PTGSE4 | PTGSE3 | PTGSE2 | PTGSE1 | PTGSE0 |

| w     |   | FIGSED | FIGSES | F163E4 | FIGSES | FIGSEZ | FIGSET | FIGSED |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-43. Output Slew Rate Control Enable for Port G Bits (PTGSE)

### Table 6-34. PTGSE Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTGSE[6:0] | <ul> <li>Output Slew Rate Control Enable for Port G Bits— Each of these control bits determine whether output slew rate control is enabled for the associated PTG pin. For port G pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port G bit n.</li> <li>Output slew rate control enabled for port G bit n.</li> </ul> |

|       | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     | 0 | PTGDS6 | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| w     |   | FIGD30 | FIGDS5 | FIGD34 | FIGD33 | FIGD52 | FIGDST | FIGDSU |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-44. Output Drive Strength Selection for Port G (PTGDS)

### Table 6-35. PTGDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGDS[6:0] | <ul> <li>Output Drive Strength Selection for Port G Bits — Each of these control bits selects between low and high output drive for the associated PTG pin.</li> <li>0 Low output drive enabled for port G bit n.</li> <li>1 High output drive enabled for port G bit n.</li> </ul> |

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1*.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

# 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

Chapter 7 Central Processor Unit (S08CPUV2)

# 7.3.6.1 Indexed, No Offset (IX)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair as the address of the operand needed to complete the instruction.

# 7.3.6.2 Indexed, No Offset with Post Increment (IX+)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair as the address of the operand needed to complete the instruction. The index register pair is then incremented (H:X = H:X + 0x0001) after the operand has been fetched. This addressing mode is only used for MOV and CBEQ instructions.

## 7.3.6.3 Indexed, 8-Bit Offset (IX1)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction.

## 7.3.6.4 Indexed, 8-Bit Offset with Post Increment (IX1+)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction. The index register pair is then incremented (H:X = H:X + 0x0001) after the operand has been fetched. This addressing mode is used only for the CBEQ instruction.

### 7.3.6.5 Indexed, 16-Bit Offset (IX2)

This variation of indexed addressing uses the 16-bit value in the H:X index register pair plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

## 7.3.6.6 SP-Relative, 8-Bit Offset (SP1)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus an unsigned 8-bit offset included in the instruction as the address of the operand needed to complete the instruction.

## 7.3.6.7 SP-Relative, 16-Bit Offset (SP2)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

# 7.4 Special Operations

The CPU performs a few special operations that are similar to instructions but do not have opcodes like other CPU instructions. In addition, a few instructions such as STOP and WAIT directly affect other MCU circuitry. This section provides additional information about these operations.

# 7.5 HCS08 Instruction Set Summary

Table 7-2 provides a summary of the HCS08 instruction set in all possible addressing modes. The table shows operand construction, execution time in internal bus clock cycles, and cycle-by-cycle details for each addressing mode variation of each instruction.

| Source<br>Form                                                                                                            | Operation                                                                               | A po            |                                                                                  | Cycles                          | Cyc-by-Cyc<br>Details                                    | Affect<br>on CCR      |                        |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|-----------------------|------------------------|

|                                                                                                                           |                                                                                         | PA<br>Ad                                            |                                                                                  | ΰ                               | Dotano                                                   | <b>V</b> 1 1 <b>H</b> | INZC                   |

| ADC #opr8i<br>ADC opr8a<br>ADC opr16a<br>ADC oprx16,X<br>ADC oprx8,X<br>ADC ,X<br>ADC oprx16,SP<br>ADC oprx8,SP           | Add with Carry<br>A $\leftarrow$ (A) + (M) + (C)                                        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A9 ii<br>B9 dd<br>C9 hh 11<br>D9 ee ff<br>E9 ff<br>F9<br>9E D9 ee ff<br>9E E9 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rpp<br>rfp<br>prpp<br>prpp   | \$1 1\$               | -\$\$\$                |

| ADD #opr8i<br>ADD opr8a<br>ADD opr16a<br>ADD oprx16,X<br>ADD oprx8,X<br>ADD ,X<br>ADD ,X<br>ADD oprx16,SP<br>ADD oprx8,SP | Add without Carry<br>A ← (A) + (M)                                                      | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | AB ii<br>BB dd<br>CB hh 11<br>DB ee ff<br>EB ff<br>FB<br>9E DB ee ff<br>9E EB ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rfp<br>prpp<br>prpp<br>prpp  | \$1 1\$               | -\$\$\$                |

| AIS #opr8i                                                                                                                | Add Immediate Value (Signed) to<br>Stack Pointer<br>SP $\leftarrow$ (SP) + (M)          | IMM                                                 | A7 ii                                                                            | 2                               | qq                                                       | - 1 1 -               |                        |

| AIX #opr8i                                                                                                                | Add Immediate Value (Signed) to<br>Index Register (H:X)<br>H:X $\leftarrow$ (H:X) + (M) | IMM                                                 | AF ii                                                                            | 2                               | qq                                                       | -11-                  |                        |

| AND #opr8i<br>AND opr8a<br>AND opr16a<br>AND oprx16,X<br>AND oprx8,X<br>AND ,X<br>AND oprx16,SP<br>AND oprx8,SP           | Logical AND<br>A ← (A) & (M)                                                            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A4 ii<br>B4 dd<br>C4 hh ll<br>D4 ee ff<br>E4 ff<br>F4<br>9E D4 ee ff<br>9E E4 ff | 2 3 4 4 3 3 5 4                 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | 011-                  | - \$ \$ -              |

| ASL <i>opr8a</i><br>ASLA<br>ASLX<br>ASL <i>oprx8</i> ,X<br>ASL ,X<br>ASL <i>oprx8</i> ,SP                                 | Arithmetic Shift Left                                                                   | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38 dd<br>48<br>58<br>68 ff<br>78<br>9E 68 ff                                     | 5<br>1<br>5<br>4<br>6           | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwpp                    | \$11-                 | $ \ddagger$ $\ddagger$ |

| ASR opr8a<br>ASRA<br>ASRX<br>ASR oprx8,X<br>ASR ,X<br>ASR oprx8,SP                                                        | Arithmetic Shift Right                                                                  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 37 dd<br>47<br>57<br>67 ff<br>77<br>9E 67 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp               | \$11-                 | - 1 1 1                |

Table 7-2. . Instruction Set Summary (Sheet 1 of 9)

#### Chapter 8 Internal Clock Generator (S08ICGV4)

#### Notes:

- 1. Port pins are software configurable with pullup device if input port.

- Pin contains software configurable pullup/pulldown device if IRQ is enabled (IRQPE = 1). Pulldown is enabled if rising edge detect is selected (IRQEDG = 1)

- 3. IRQ does not have a clamp diode to V<sub>DD</sub>. IRQ should not be driven above V<sub>DD</sub>.

- 4. Pin contains integrated pullup device.

- 5. PTD3, PTD2, and PTG4 contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

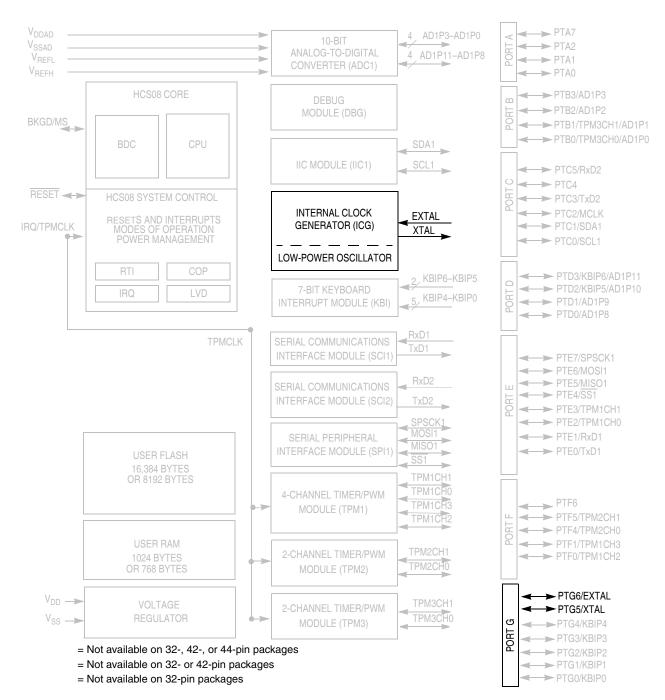

#### Figure 8-2. MC9S08AC16 Block Diagram Highlighting the ICG

# Chapter 9 Keyboard Interrupt (S08KBIV1)

# 9.1 Introduction

The MC9S08AC16 Series has one KBI module with seven keyboard interrupt inputs that are shared with port D and port G pins. See Chapter 2, "Pins and Connections," for more information about the logic and hardware aspects of these pins.

### NOTE

Bit 7 of KBISC and KBIPE is reserved and reads 0. Neglect the correlative information in Section 9.4.1, "KBI Status and Control Register (KBISC)," and Section 9.4.2, "KBI Pin Enable Register (KBIPE)."

# 9.2 Keyboard Pin Sharing

The KBI input KBIP6 shares a common pin with PTD3 and AD11, and KBI input KBIP5 shares a common pin with PTD2 and AD10.

The KBI inputs KBIP4–KBIP0 are shared on common pins with PTG4–PTG0.

KBIP3–KBIP0 are always falling-edge/low-level sensitive. KBIP6–KBIP4 can be configured for rising-edge/high-level or for falling-edge/low-level sensitivity. When any of the inputs KBIP6–KBIP0 are enabled and configured to detect rising edges/high levels, and the pin pullup is enabled through the corresponding port pullup enable bit for that pin, a pulldown resistor rather than a pullup resistor is enabled on the pin.

# 9.3 Features

The keyboard interrupt (KBI) module features include:

- Four falling edge/low level sensitive

- Three falling edge/low level or rising edge/high level sensitive

- Choice of edge-only or edge-and-level sensitivity

- Common interrupt flag and interrupt enable control

- Capable of waking up the MCU from stop3, stop2, or wait mode

Chapter 11 Serial Communications Interface (S08SCIV4)

#### Notes:

- 1. Port pins are software configurable with pullup device if input port.

- Pin contains software configurable pullup/pulldown device if IRQ is enabled (IRQPE = 1). Pulldown is enabled if rising edge detect is selected (IRQEDG = 1)

- 3. IRQ does not have a clamp diode to  $V_{DD}$ . IRQ should not be driven above  $V_{DD}$ .

- 4. Pin contains integrated pullup device.

- 5. PTD3, PTD2, and PTG4 contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

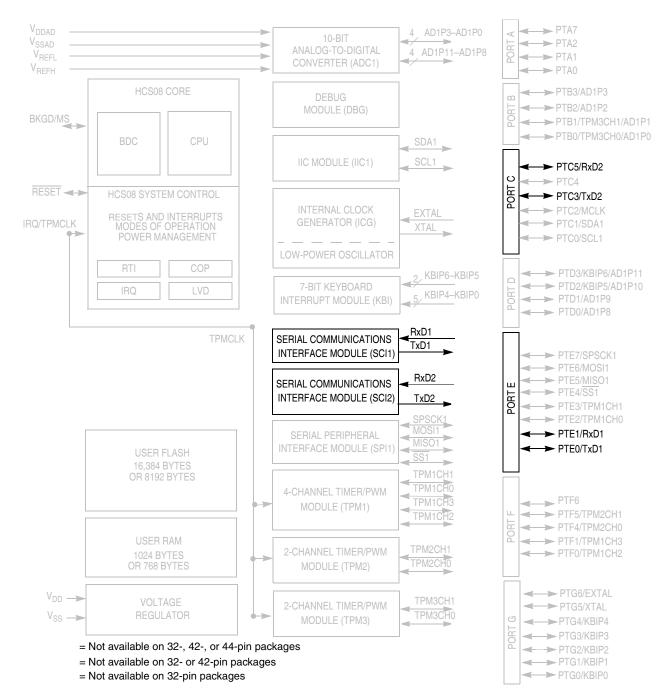

### Figure 11-1. MC9S08AC16 Block Diagram Highlighting the SCI

### Table 11-5. SCIxS1 Field Descriptions (continued)

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>FE | <ul> <li>Framing Error Flag — FE is set at the same time as RDRF when the receiver detects a logic 0 where the stop bit was expected. This suggests the receiver was not properly aligned to a character frame. To clear FE, read SCIxS1 with FE = 1 and then read the SCI data register (SCIxD).</li> <li>0 No framing error detected. This does not guarantee the framing is correct.</li> <li>1 Framing error.</li> </ul> |

| 0<br>PF | <ul> <li>Parity Error Flag — PF is set at the same time as RDRF when parity is enabled (PE = 1) and the parity bit in the received character does not agree with the expected parity value. To clear PF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No parity error.</li> <li>1 Parity error.</li> </ul>                                                                                            |

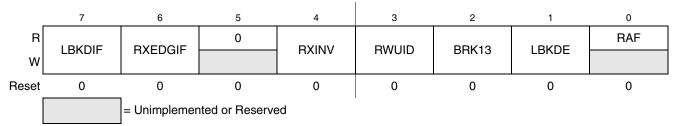

# 11.2.5 SCI Status Register 2 (SCIxS2)

This register has one read-only status flag.

### Figure 11-9. SCI Status Register 2 (SCIxS2)

#### Table 11-6. SCIxS2 Field Descriptions

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LBKDIF             | LIN Break Detect Interrupt Flag — LBKDIF is set when the LIN break detect circuitry is enabled and a LIN break character is detected. LBKDIF is cleared by writing a "1" to it.<br>0 No LIN break character has been detected.<br>1 LIN break character has been detected.                                                                                                           |

| 6<br>RXEDGIF            | <ul> <li>RxD Pin Active Edge Interrupt Flag — RXEDGIF is set when an active edge (falling if RXINV = 0, rising if RXINV=1) on the RxD pin occurs. RXEDGIF is cleared by writing a "1" to it.</li> <li>0 No active edge on the receive pin has occurred.</li> <li>1 An active edge on the receive pin has occurred.</li> </ul>                                                        |

| 4<br>RXINV <sup>1</sup> | <ul> <li>Receive Data Inversion — Setting this bit reverses the polarity of the received data input.</li> <li>0 Receive data not inverted</li> <li>1 Receive data inverted</li> </ul>                                                                                                                                                                                                |

| 3<br>RWUID              | <ul> <li>Receive Wake Up Idle Detect— RWUID controls whether the idle character that wakes up the receiver sets the IDLE bit.</li> <li>0 During receive standby state (RWU = 1), the IDLE bit does not get set upon detection of an idle character.</li> <li>1 During receive standby state (RWU = 1), the IDLE bit gets set upon detection of an idle character.</li> </ul>         |

| 2<br>BRK13              | <ul> <li>Break Character Generation Length — BRK13 is used to select a longer transmitted break character length.</li> <li>Detection of a framing error is not affected by the state of this bit.</li> <li>0 Break character is transmitted with length of 10 bit times (11 if M = 1)</li> <li>1 Break character is transmitted with length of 13 bit times (14 if M = 1)</li> </ul> |

### 12.1.1 Features

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

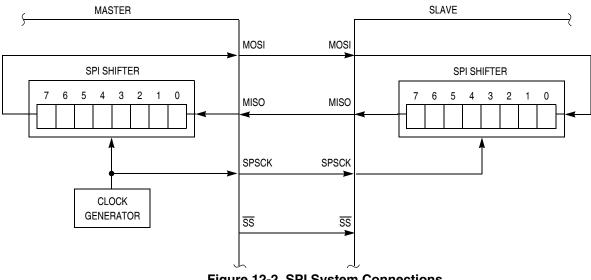

### 12.1.2 Block Diagrams

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

### 12.1.2.1 SPI System Block Diagram

Figure 12-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI pin) to the slave while simultaneously shifting data in (on the MISO pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS}$  pin). In this system, the master device has configured its  $\overline{SS}$  pin as an optional slave select output.

Figure 12-2. SPI System Connections

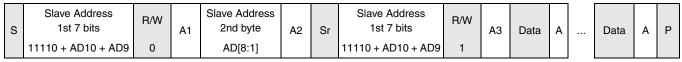

After a repeated start condition (Sr), all other slave devices also compare the first seven bits of the first byte of the slave address with their own addresses and test the eighth  $(R/\overline{W})$  bit. However, none of them are addressed because  $R/\overline{W} = 1$  (for 10-bit devices) or the 11110XX slave address (for 7-bit devices) does not match.

Table 13-10. Master-Receiver Addresses a Slave-Transmitter with a 10-bit Address

After the master-receiver has sent the first byte of the 10-bit address, the slave-transmitter sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

# 13.4.3 General Call Address

General calls can be requested in 7-bit address or 10-bit address. If the GCAEN bit is set, the IIC matches the general call address as well as its own slave address. When the IIC responds to a general call, it acts as a slave-receiver and the IAAS bit is set after the address cycle. Software must read the IICD register after the first byte transfer to determine whether the address matches is its own slave address or a general call. If the value is 00, the match is a general call. If the GCAEN bit is clear, the IIC ignores any data supplied from a general call address by not issuing an acknowledgement.

# 13.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

# 13.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 13-11 occur, provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a 1 to it in the interrupt routine. You can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | IICIF | IICIE        |

| Match of received calling address | IAAS   | IICIF | IICIE        |

| Arbitration Lost                  | ARBL   | IICIF | IICIE        |

Table 13-11. Interrupt Summary

## 13.6.1 Byte Transfer Interrupt

The TCF (transfer complete flag) bit is set at the falling edge of the ninth clock to indicate the completion of byte transfer.

Inter-Integrated Circuit (S08IICV2)

# 13.6.2 Address Detect Interrupt

When the calling address matches the programmed slave address (IIC address register) or when the GCAEN bit is set and a general call is received, the IAAS bit in the status register is set. The CPU is interrupted, provided the IICIE is set. The CPU must check the SRW bit and set its Tx mode accordingly.

# 13.6.3 Arbitration Lost Interrupt

The IIC is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, the relative priority of the contending masters is determined by a data arbitration procedure. The IIC module asserts this interrupt when it loses the data arbitration process and the ARBL bit in the status register is set.

Arbitration is lost in the following circumstances:

- SDA sampled as a low when the master drives a high during an address or data transmit cycle.

- SDA sampled as a low when the master drives a high during the acknowledge bit of a data receive cycle.

- A start cycle is attempted when the bus is busy.

- A repeated start cycle is requested in slave mode.

- A stop condition is detected when the master did not request it.

This bit must be cleared by software writing a 1 to it.

#### Analog-to-Digital Converter (S08ADC10V1)

In cases where separate power supplies are used for analog and digital power, the ground connection between these supplies must be at the  $V_{SSAD}$  pin. This should be the only ground connection between these supplies if possible. The  $V_{SSAD}$  pin makes a good single point ground location.

### 14.7.1.2 Analog Reference Pins

In addition to the analog supplies, the ADC module has connections for two reference voltage inputs. The high reference is  $V_{REFH}$ , which may be shared on the same pin as  $V_{DDAD}$  on some devices. The low reference is  $V_{REFL}$ , which may be shared on the same pin as  $V_{SSAD}$  on some devices.

When available on a separate pin,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ). When available on a separate pin,  $V_{REFL}$  must be connected to the same voltage potential as  $V_{SSAD}$ . Both  $V_{REFH}$  and  $V_{REFL}$  must be routed carefully for maximum noise immunity and bypass capacitors placed as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the  $V_{REFH}$  and  $V_{REFL}$  loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between  $V_{REFH}$  and  $V_{REFL}$  and must be placed as near as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

### 14.7.1.3 Analog Input Pins

The external analog inputs are typically shared with digital I/O pins on MCU devices. The pin I/O control is disabled by setting the appropriate control bit in one of the pin control registers. Conversions can be performed on inputs without the associated pin control register bit set. It is recommended that the pin control register bit always be set when using a pin as an analog input. This avoids problems with contention because the output buffer will be in its high impedance state and the pullup is disabled. Also, the input buffer draws dc current when its input is not at either  $V_{DD}$  or  $V_{SS}$ . Setting the pin control register bits for all pins used as analog inputs should be done to achieve lowest operating current.

Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. Use of 0.01  $\mu$ F capacitors with good high-frequency characteristics is sufficient. These capacitors are not necessary in all cases, but when used they must be placed as near as possible to the package pins and be referenced to V<sub>SSA</sub>.

For proper conversion, the input voltage must fall between  $V_{REFH}$  and  $V_{REFL}$ . If the input is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to \$3FF (full scale 10-bit representation) or \$FF (full scale 8-bit representation). If the input is equal to or less than  $V_{REFL}$ , the converter circuit converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions. There will be a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. The input is sampled for 3.5 cycles of the ADCK source when ADLSMP is low, or 23.5 cycles when ADLSMP is high.

For minimal loss of accuracy due to current injection, pins adjacent to the analog input pins should not be transitioning during conversions.

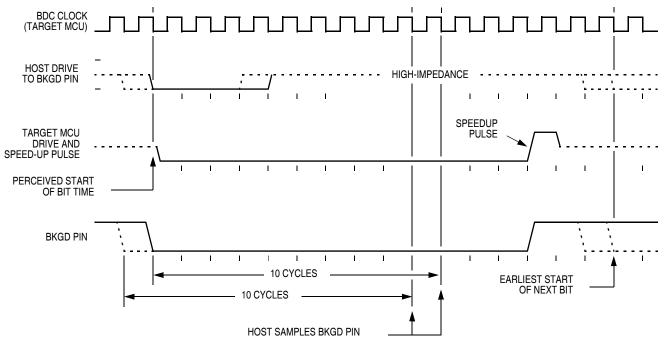

#### **Development Support**

Figure 15-4 shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit level about 10 cycles after starting the bit time.

Figure 15-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

Development Support

A-Only — Trigger when the address matches the value in comparator A

A OR B — Trigger when the address matches either the value in comparator A or the value in comparator B

A Then B — Trigger when the address matches the value in comparator B but only after the address for another cycle matched the value in comparator A. There can be any number of cycles after the A match and before the B match.

A AND B Data (Full Mode) — This is called a full mode because address, data, and R/W (optionally) must match within the same bus cycle to cause a trigger event. Comparator A checks address, the low byte of comparator B checks data, and R/W is checked against RWA if RWAEN = 1. The high-order half of comparator B is not used.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

A AND NOT B Data (Full Mode) — Address must match comparator A, data must not match the low half of comparator B, and R/W must match RWA if RWAEN = 1. All three conditions must be met within the same bus cycle to cause a trigger.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**Event-Only B** (Store Data) — Trigger events occur each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

A Then Event-Only B (Store Data) — After the address has matched the value in comparator A, a trigger event occurs each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

**Inside Range (** $A \le Address \le B$ **)** — A trigger occurs when the address is greater than or equal to the value in comparator A and less than or equal to the value in comparator B at the same time.

**Outside Range** (Address < A or Address > B) — A trigger occurs when the address is either less than the value in comparator A or greater than the value in comparator B.

Development Support

# 15.4.1.1 BDC Status and Control Register (BDCSCR)

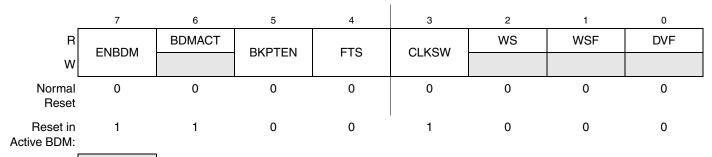

This register can be read or written by serial BDC commands (READ\_STATUS and WRITE\_CONTROL) but is not accessible to user programs because it is not located in the normal memory map of the MCU.

= Unimplemented or Reserved

### Figure 15-5. BDC Status and Control Register (BDCSCR)

### Table 15-2. BDCSCR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDM  | <ul> <li>Enable BDM (Permit Active Background Mode) — Typically, this bit is written to 1 by the debug host shortly after the beginning of a debug session or whenever the debug host resets the target and remains 1 until a normal reset clears it.</li> <li>0 BDM cannot be made active (non-intrusive commands still allowed)</li> <li>1 BDM can be made active to allow active background mode commands</li> </ul>                                                                                                                                                                                                                                                |

| 6<br>BDMACT | Background Mode Active Status — This is a read-only status bit.0 BDM not active (user application program running)1 BDM active and waiting for serial commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>BKPTEN | <ul> <li>BDC Breakpoint Enable — If this bit is clear, the BDC breakpoint is disabled and the FTS (force tag select) control bit and BDCBKPT match register are ignored.</li> <li>0 BDC breakpoint disabled</li> <li>1 BDC breakpoint enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4<br>FTS    | <ul> <li>Force/Tag Select — When FTS = 1, a breakpoint is requested whenever the CPU address bus matches the BDCBKPT match register. When FTS = 0, a match between the CPU address bus and the BDCBKPT register causes the fetched opcode to be tagged. If this tagged opcode ever reaches the end of the instruction queue, the CPU enters active background mode rather than executing the tagged opcode.</li> <li>0 Tag opcode at breakpoint address and enter active background mode if CPU attempts to execute that instruction</li> <li>1 Breakpoint match forces active background mode at next instruction boundary (address need not be an opcode)</li> </ul> |

| 3<br>CLKSW  | Select Source for BDC Communications Clock — CLKSW defaults to 0, which selects the alternate BDC clock source.         0       Alternate BDC clock source         1       MCU bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

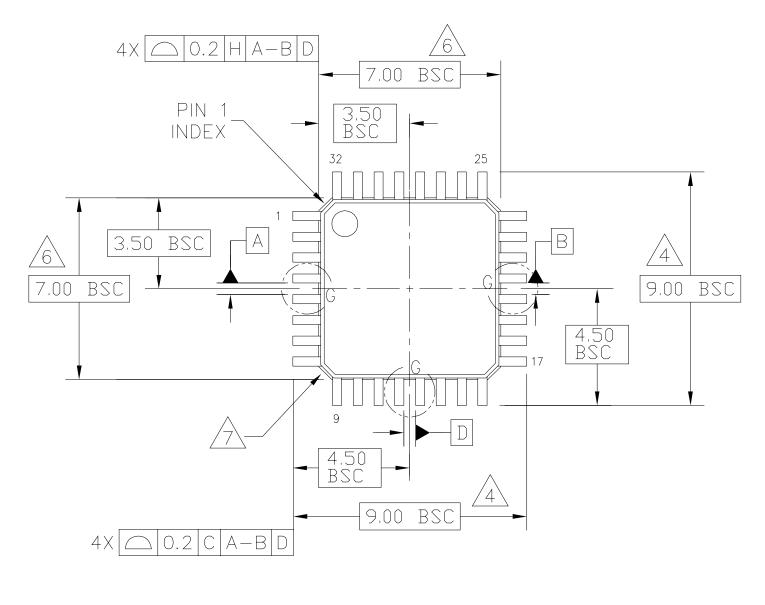

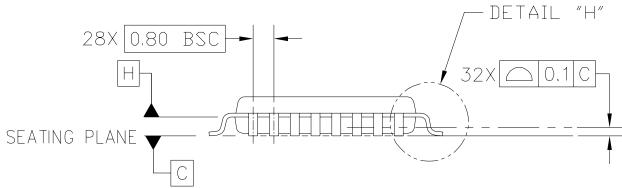

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED.               | MECHANICAL OUTLINE |                            | PRINT VERSION NOT TO SCALE |             |

|-----------------------------------------------------------------------|--------------------|----------------------------|----------------------------|-------------|

| TITLE:                                                                |                    | DOCUMENT NO: 98ASH70029A   |                            | RE∨: D      |

| LOW PROFILE QUAD FLAT PACK (LQFP)<br>32 LEAD, 0.8 PITCH (7 X 7 X 1.4) |                    | CASE NUMBER: 873A-03       |                            | 19 MAY 2005 |

|                                                                       |                    | STANDARD: JEDEC MS-026 BBA |                            |             |