Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 34                                                                    |

| Program Memory Size        | 8KB (8K × 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 768 × 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | 44-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac8cfge |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9S08AC16 MC9S08AC8 MC9S08AW16A MC9S08AW8A

Data Sheet

HCS08 Microcontrollers

MC9S08AC16 Rev. 9 8/2011

freescale.com

**Chapter 1 Introduction**

# Chapter 4 Memory

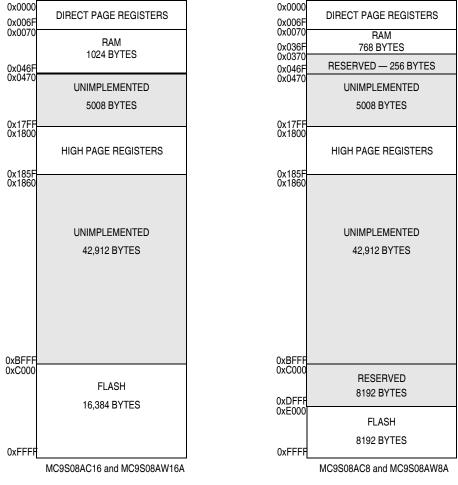

# 4.1 MC9S08AC16 Series Memory Map

Figure 4-1 shows the memory maps for the MC9S08AC16 Series MCUs. On-chip memory in the MC9S08AC16 Series of MCU consists of RAM, FLASH program memory for nonvolatile data storage, plus I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (0x0000 through 0x006F)

- High-page registers (0x1800 through 0x185F)

- Nonvolatile registers (0xFFB0 through 0xFFBF)

**Chapter 4 Memory**

### 4.1.1 Reset and Interrupt Vector Assignments

Figure 4-1 shows address assignments for reset and interrupt vectors. The vector names shown in this table are the labels used in the Freescale-provided equate file for the MC9S08AC16 Series. For more details about resets, interrupts, interrupt priority, and local interrupt mask controls, refer to Chapter 5, "Resets, Interrupts, and System Configuration."

| Address (High/Low)              | Vector                                           | Vector Name |  |  |

|---------------------------------|--------------------------------------------------|-------------|--|--|

| 0xFFC0:FFC1 through 0xFFC4:FFC5 | Unused Vector Space (available for user program) | _           |  |  |

| 0xFFC6:FFC7                     | TPM3 overflow                                    | Vtpm3ovf    |  |  |

| 0xFFC8:FFC9                     | TPM3 channel 1                                   | Vtpm3ch1    |  |  |

| 0xFFCA:FFCB                     | TPM3 channel 0                                   | Vtpm3ch0    |  |  |

| 0xFFCC:FFCD                     | RTI                                              | Vrti        |  |  |

| 0xFFCE:FFCF                     | IIC1                                             | Viic1       |  |  |

| 0xFFD0:FFD1                     | ADC1 Conversion                                  | Vadc1       |  |  |

| 0xFFD2:FFD3                     | KBI                                              | Vkeyboard1  |  |  |

| 0xFFD4:FFD5                     | SCI2 Transmit                                    | Vsci2tx     |  |  |

| 0xFFD6:FFD7                     | SCI2 Receive                                     | Vsci2rx     |  |  |

| 0xFFD8:FFD9                     | SCI2 Error                                       | Vsci2err    |  |  |

| 0xFFDA:FFDB                     | SCI1 Transmit                                    | Vsci1tx     |  |  |

| 0xFFDC:FFDD                     | SCI1 Receive                                     | Vsci1rx     |  |  |

| 0xFFDE:FFDF                     | SCI1 Error                                       | Vsci1err    |  |  |

| 0xFFE0:FFE1                     | SPI1                                             | Vspi1       |  |  |

| 0xFFE2:FFE3                     | TPM2 Overflow                                    | Vtpm2ovf    |  |  |

| 0xFFE4:FFE5                     | TPM2 Channel 1                                   | Vtpm2ch1    |  |  |

| 0xFFE6:FFE7                     | TPM2 Channel 0                                   | Vtpm2ch0    |  |  |

| 0xFFE8:FFE9                     | TPM1 Overflow                                    | Vtpm1ovf    |  |  |

| 0xFFEA:FFEB                     | Unused                                           | —           |  |  |

| 0xFFEC:FFED                     | Unused                                           | —           |  |  |

| 0xFFEE:FFEF                     | TPM1 Channel 3                                   | Vtpm1ch3    |  |  |

| 0xFFF0:FFF1                     | TPM1 Channel 2                                   | Vtpm1ch2    |  |  |

| 0xFFF2:FFF3                     | TPM1 Channel 1                                   | Vtpm1ch1    |  |  |

| 0xFFF4:FFF5                     | TPM1 Channel 0                                   | Vtpm1ch0    |  |  |

| 0xFFF6:FFF7                     | ICG                                              | Vicg        |  |  |

| 0xFFF8:FFF9                     | Low Voltage Detect                               | Vlvd        |  |  |

| 0xFFFA:FFFB                     | IRQ                                              | Virq        |  |  |

| 0xFFFC:FFFD                     | SWI                                              | Vswi        |  |  |

| 0xFFFE:FFFF                     | Reset                                            | Vreset      |  |  |

Table 4-1. Reset and Interrupt Vectors

#### Chapter 4 Memory

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.5, "Security" for a detailed description of the security feature.

# 4.4 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I,* Freescale Semiconductor document order number HCS08RMv1/D.

### 4.4.1 Features

Features of the FLASH memory include:

- FLASH Size

- MC9S08AC16 and MC9S08AW16A— 16,384 bytes (32 pages of 512 bytes each)

- MC9S08AC8 and MC9S08AW8A— 8192 bytes (16 pages of 512 bytes each)

- Single power supply program and erase

- Command interface for fast program and erase operation

- Up to 100,000 program/erase cycles at typical voltage and temperature

- Flexible block protection

- Security feature for FLASH and RAM

- Auto power-down for low-frequency read accesses

### 4.4.2 Program and Erase Times

Before any program or erase command can be accepted, the FLASH clock divider register (FCDIV) must be written to set the internal clock for the FLASH module to a frequency ( $f_{FCLK}$ ) between 150 kHz and 200 kHz (see Section 4.6.1, "FLASH Clock Divider Register (FCDIV)"). This register can be written only once, so normally this write is done during reset initialization. FCDIV cannot be written if the access error flag, FACCERR in FSTAT, is set. The user must ensure that FACCERR is not set before writing to the FCDIV register. One period of the resulting clock ( $1/f_{FCLK}$ ) is used by the command processor to time program and erase pulses. An integer number of these timing pulses are used by the command processor to complete a program or erase command.

Table 4-5 shows program and erase times. The bus clock frequency and FCDIV determine the frequency of FCLK ( $f_{FCLK}$ ). The time for one cycle of FCLK is  $t_{FCLK} = 1/f_{FCLK}$ . The times are shown as a number of cycles of FCLK and as an absolute time for the case where  $t_{FCLK} = 5 \ \mu s$ . Program and erase times shown include overhead for the command state machine and enabling and disabling of program and erase voltages.

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1*.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

### 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

Internal Clock Generator (S08ICGV4)

# 8.3.4 ICG Status Register 2 (ICGS2)

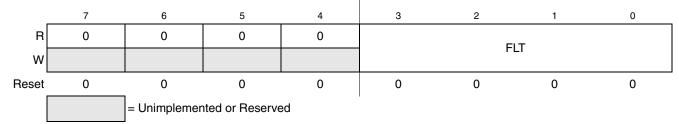

#### Figure 8-9. ICG Status Register 2 (ICGS2)

#### Table 8-4. ICGS2 Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>DCOS | <ul> <li>DCO Clock Stable — The DCOS bit is set when the DCO clock (ICG2DCLK) is stable, meaning the count error has not changed by more than n<sub>unlock</sub> for two consecutive samples and the DCO clock is not static. This bit is used when exiting off state if CLKS = X1 to determine when to switch to the requested clock mode. It is also used in self-clocked mode to determine when to start monitoring the DCO clock. This bit is cleared upon entering the off state.</li> <li>0 DCO clock is unstable.</li> <li>1 DCO clock is stable.</li> </ul> |

# 8.3.5 ICG Filter Registers (ICGFLTU, ICGFLTL)

#### Figure 8-10. ICG Upper Filter Register (ICGFLTU)

#### Table 8-5. ICGFLTU Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLT   | <b>Filter Value</b> — The FLT bits indicate the current filter value, which controls the DCO frequency. The FLT bits are read only except when the CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. |

#### Internal Clock Generator (S08ICGV4)

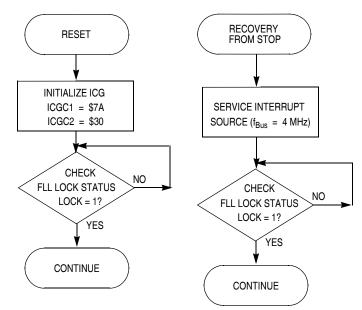

Figure 8-15. ICG Initialization and Stop Recovery for Example #2

### ICGTRM = \$xx

Bit 7:0 TRIM

Only need to write when trimming internal oscillator; done in separate operation (see example #4)

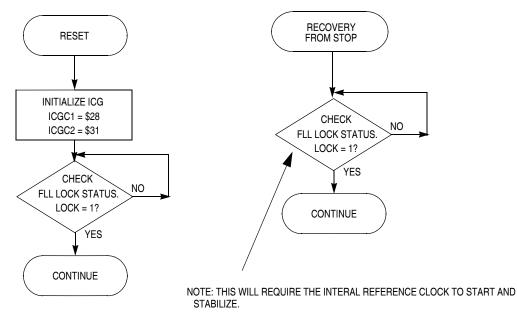

Figure 8-16. ICG Initialization and Stop Recovery for Example #3

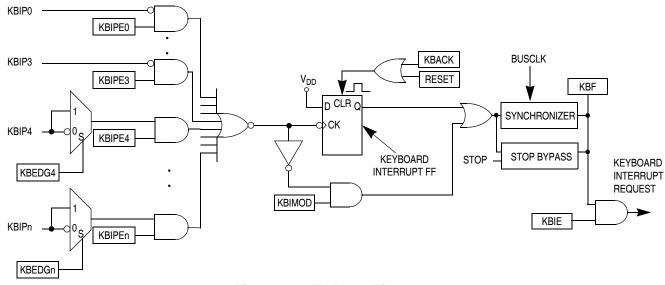

### 9.3.1 KBI Block Diagram

Figure 9-2 shows the block diagram for a KBI module.

Figure 9-2. KBI Block Diagram

## 9.4 Register Definition

This section provides information about all registers and control bits associated with the KBI module.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all KBI registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Timer/PWM Module (S08TPMV3)

| CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                  | Configuration                                 |

|-------|-----------|-------------|-----------------------|-----------------------------------------------|

| 0     | 00        | 01          | Input capture         | Capture on rising edge only                   |

|       |           | 10          |                       | Capture on falling edge only                  |

|       |           | 11          |                       | Capture on rising or falling edge             |

|       | 01        | 00          | Output compare        | Software compare only                         |

|       |           | 01          |                       | Toggle output on compare                      |

|       |           | 10          |                       | Clear output on compare                       |

|       |           | 11          |                       | Set output on compare                         |

|       | 1X        | 10          | Edge-aligned<br>PWM   | High-true pulses (clear output on compare)    |

|       |           | X1          |                       | Low-true pulses (set output on compare)       |

| 1     | XX        | 10          | Center-aligned<br>PWM | High-true pulses (clear output on compare-up) |

|       |           | X1          |                       | Low-true pulses (set output on compare-up)    |

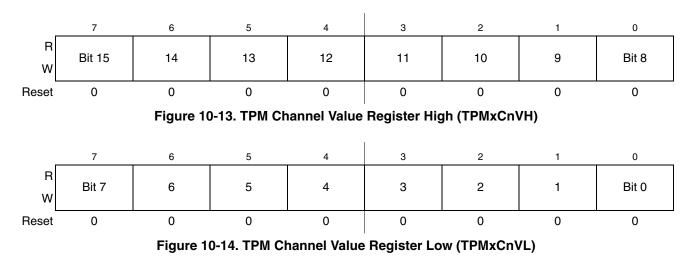

### 10.5.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)

These read/write registers contain the captured TPM counter value of the input capture function or the output compare value for the output compare or PWM functions. The channel registers are cleared by reset.

In input capture mode, reading either byte (TPMxCnVH or TPMxCnVL) latches the contents of both bytes into a buffer where they remain latched until the other half is read. This latching mechanism also resets

### 13.4.1.5 Repeated Start Signal

As shown in Figure 13-9, a repeated start signal is a start signal generated without first generating a stop signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in different mode (transmit/receive mode) without releasing the bus.

### 13.4.1.6 Arbitration Procedure

The IIC bus is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock, for which the low period is equal to the longest clock low period and the high is equal to the shortest one among the masters. The relative priority of the contending masters is determined by a data arbitration procedure, a bus master loses arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately switch over to slave receive mode and stop driving SDA output. In this case, the transition from master to slave mode does not generate a stop condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

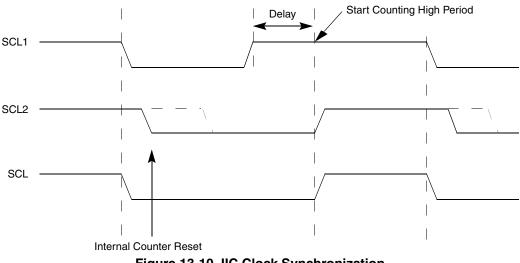

### 13.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 13-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

Figure 13-10. IIC Clock Synchronization

Inter-Integrated Circuit (S08IICV2)

### 13.6.2 Address Detect Interrupt

When the calling address matches the programmed slave address (IIC address register) or when the GCAEN bit is set and a general call is received, the IAAS bit in the status register is set. The CPU is interrupted, provided the IICIE is set. The CPU must check the SRW bit and set its Tx mode accordingly.

### 13.6.3 Arbitration Lost Interrupt

The IIC is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, the relative priority of the contending masters is determined by a data arbitration procedure. The IIC module asserts this interrupt when it loses the data arbitration process and the ARBL bit in the status register is set.

Arbitration is lost in the following circumstances:

- SDA sampled as a low when the master drives a high during an address or data transmit cycle.

- SDA sampled as a low when the master drives a high during the acknowledge bit of a data receive cycle.

- A start cycle is attempted when the bus is busy.

- A repeated start cycle is requested in slave mode.

- A stop condition is detected when the master did not request it.

This bit must be cleared by software writing a 1 to it.

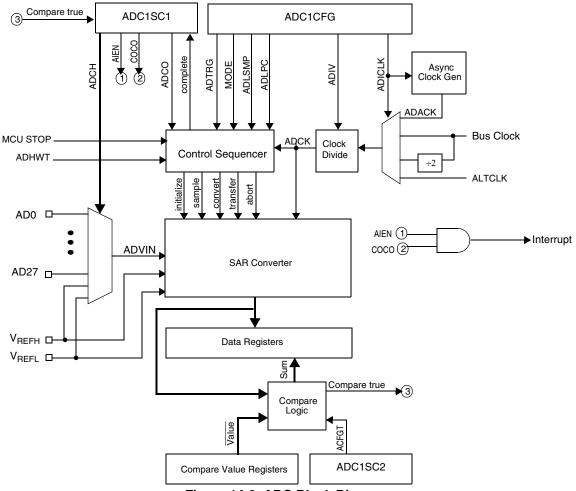

#### Analog-to-Digital Converter (S08ADC10V1)

Figure 14-2. ADC Block Diagram

# 14.3 External Signal Description

The ADC module supports up to 28 separate analog inputs. It also requires four supply/reference/ground connections.

| Name              | Function               |

|-------------------|------------------------|

| AD27–AD0          | Analog Channel inputs  |

| V <sub>REFH</sub> | High reference voltage |

| V <sub>REFL</sub> | Low reference voltage  |

| V <sub>DDAD</sub> | Analog power supply    |

| V <sub>SSAD</sub> | Analog ground          |

#### **Table 14-2. Signal Properties**

Analog-to-Digital Converter (S08ADC10V1)

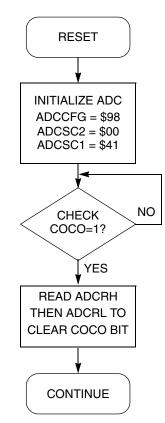

Figure 14-14. Initialization Flowchart for Example

# 14.7 Application Information

This section contains information for using the ADC module in applications. The ADC has been designed to be integrated into a microcontroller for use in embedded control applications requiring an A/D converter.

### 14.7.1 External Pins and Routing

The following sections discuss the external pins associated with the ADC module and how they should be used for best results.

### 14.7.1.1 Analog Supply Pins

The ADC module has analog power and ground supplies ( $V_{DDAD}$  and  $V_{SSAD}$ ) which are available as separate pins on some devices. On other devices,  $V_{SSAD}$  is shared on the same pin as the MCU digital  $V_{SS}$ , and on others, both  $V_{SSAD}$  and  $V_{DDAD}$  are shared with the MCU digital supply pins. In these cases, there are separate pads for the analog supplies which are bonded to the same pin as the corresponding digital supply so that some degree of isolation between the supplies is maintained.

When available on a separate pin, both  $V_{DDAD}$  and  $V_{SSAD}$  must be connected to the same voltage potential as their corresponding MCU digital supply ( $V_{DD}$  and  $V_{SS}$ ) and must be routed carefully for maximum noise immunity and bypass capacitors placed as near as possible to the package.

### 14.7.2 Sources of Error

Several sources of error exist for A/D conversions. These are discussed in the following sections.

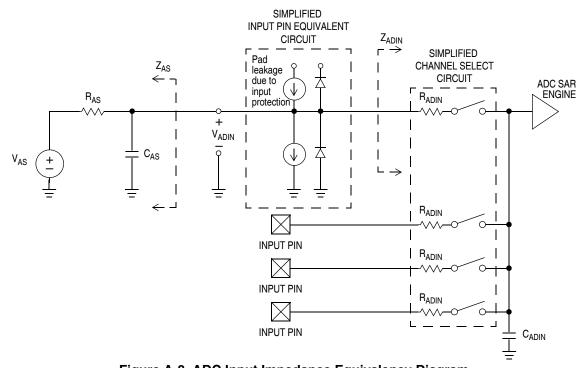

### 14.7.2.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately  $7k\Omega$  and input capacitance of approximately 5.5 pF, sampling to within 1/4LSB (at 10-bit resolution) can be achieved within the minimum sample window (3.5 cycles @ 8 MHz maximum ADCK frequency) provided the resistance of the external analog source ( $R_{AS}$ ) is kept below 5 k $\Omega$ .

Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

### 14.7.2.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{DDAD} / (2^{N*}I_{LEAK})$  for less than 1/4LSB leakage error (N = 8 in 8-bit mode or 10 in 10-bit mode).

### 14.7.2.3 Noise-Induced Errors

System noise which occurs during the sample or conversion process can affect the accuracy of the conversion. The ADC accuracy numbers are guaranteed as specified only if the following conditions are met:

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>REFH</sub> to V<sub>REFL</sub>.

- There is a 0.1  $\mu$ F low-ESR capacitor from V<sub>DDAD</sub> to V<sub>SSAD</sub>.

- If inductive isolation is used from the primary supply, an additional 1  $\mu$ F capacitor is placed from V<sub>DDAD</sub> to V<sub>SSAD</sub>.

- $V_{SSAD}$  (and  $V_{REFL}$ , if connected) is connected to  $V_{SS}$  at a quiet point in the ground plane.

- Operate the MCU in wait or stop3 mode before initiating (hardware triggered conversions) or immediately after initiating (hardware or software triggered conversions) the ADC conversion.

- For software triggered conversions, immediately follow the write to the ADC1SC1 with a WAIT instruction or STOP instruction.

- For stop3 mode operation, select ADACK as the clock source. Operation in stop3 reduces V<sub>DD</sub> noise but increases effective conversion time due to stop recovery.

- There is no I/O switching, input or output, on the MCU during the conversion.

There are some situations where external system activity causes radiated or conducted noise emissions or excessive  $V_{DD}$  noise is coupled into the ADC. In these situations, or when the MCU cannot be placed in wait or stop3 or I/O activity cannot be halted, these recommended actions may reduce the effect of noise on the accuracy:

• Place a 0.01  $\mu$ F capacitor (C<sub>AS</sub>) on the selected input channel to V<sub>REFL</sub> or V<sub>SSAD</sub> (this will improve noise issues but will affect sample rate based on the external analog source resistance).

Appendix A Electrical Characteristics and Timing Specifications

Figure A-8. ADC Input Impedance Equivalency Diagram

| Characteristic                                        | Conditions                | с                    | Symb              | Min  | Typ <sup>1</sup> | Max | Unit   |

|-------------------------------------------------------|---------------------------|----------------------|-------------------|------|------------------|-----|--------|

| Supply current<br>ADLPC = 1<br>ADLSMP = 1<br>ADCO = 1 |                           | Т                    | I <sub>DDAD</sub> | _    | 133              |     | μA     |

| Supply current<br>ADLPC = 1<br>ADLSMP = 0<br>ADCO = 1 |                           | Т                    | I <sub>DDAD</sub> | _    | 218              | _   | μΑ     |

| Supply current<br>ADLPC = 0<br>ADLSMP = 1<br>ADCO = 1 |                           | Т                    | I <sub>DDAD</sub> |      | 327              | _   | μA     |

| Supply current                                        |                           | Т                    | I <sub>DDAD</sub> | —    | 582              | -   | μA     |

| ADLPC = 0<br>ADLSMP = 0<br>ADCO = 1                   | $V_{DDAD} \le 5.5 V$      | Р                    |                   | _    | _                | 1   | mA     |

| ADC asynchronous clock source                         | High speed (ADLPC = 0)    | P <sup>f</sup> ADACK | 2                 | 3.3  | 5                | MHz |        |

| $t_{ADACK} = 1/f_{ADACK}$                             | Low power (ADLPC = 1)     |                      |                   | 1.25 | 2                | 3.3 |        |

| Conversion time                                       | Short sample (ADLSMP = 0) | Р                    | t <sub>ADC</sub>  | —    | 20               | —   | ADCK   |

| (Including sample time)                               | Long sample (ADLSMP = 1)  |                      |                   | _    | 40               | _   | cycles |

Appendix B Ordering Information and Mechanical Drawings

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

MC9S08AC16 Rev. 9, 8/2011 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2007-2011. All rights reserved.