Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HC11                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 3MHz                                                        |

| Connectivity               | SCI, SPI                                                    |

| Peripherals                | POR, WDT                                                    |

| Number of I/O              | 30                                                          |

| Program Memory Size        | -                                                           |

| Program Memory Type        | ROMIess                                                     |

| EEPROM Size                | 512 x 8                                                     |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                   |

| Data Converters            | A/D 8x8b                                                    |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 68-LCC (J-Lead)                                             |

| Supplier Device Package    | 68-PLCC (24.21x24.21)                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68l11f1cfne3 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **TABLE OF CONTENTS**

Paragraph

Title

Page

### **SECTION 1INTRODUCTION**

| 1.1 | Features |  | 1- <sup>-</sup> | 1 |

|-----|----------|--|-----------------|---|

|-----|----------|--|-----------------|---|

### **SECTION 2 PIN DESCRIPTIONS**

| 2.1    | $V_{\mbox{\scriptsize DD}}$ and $V_{\mbox{\scriptsize SS}}$ | 2-2 |

|--------|-------------------------------------------------------------|-----|

| 2.2    | Reset (RESET)                                               |     |

| 2.3    | E-Clock Output (E)                                          |     |

| 2.4    | Crystal Driver and External Clock Input (XTAL, EXTAL)       | 2-3 |

| 2.5    | Four Times E-Clock Frequency Output (4XOUT)                 | 2-5 |

| 2.6    | Interrupt Request (IRQ)                                     | 2-5 |

| 2.7    | Non-Maskable Interrupt (XIRQ)                               | 2-5 |

| 2.8    | MODA and MODB (MODA/LIR and MODB/V <sub>STBY</sub> )        | 2-6 |

| 2.9    | V <sub>RH</sub> and V <sub>RL</sub>                         | 2-6 |

| 2.10   | R/W                                                         |     |

| 2.11   | Port Signals                                                | 2-6 |

| 2.11.1 | Port A                                                      | 2-7 |

| 2.11.2 | Port B                                                      | 2-8 |

| 2.11.3 | Port C                                                      | 2-8 |

| 2.11.4 | Port D                                                      | 2-8 |

| 2.11.5 | Port E                                                      | 2-9 |

| 2.11.6 | Port F                                                      | 2-9 |

| 2.11.7 | Port G                                                      | 2-9 |

### **SECTION 3 CENTRAL PROCESSING UNIT**

| 3.1     | CPU Registers                 |  |

|---------|-------------------------------|--|

| 3.1.1   | Accumulators A, B, and D      |  |

| 3.1.2   | Index Register X (IX)         |  |

| 3.1.3   | Index Register Y (IY)         |  |

| 3.1.4   | Stack Pointer (SP)            |  |

| 3.1.5   | Program Counter (PC)          |  |

| 3.1.6   | Condition Code Register (CCR) |  |

| 3.1.6.1 | Carry/Borrow (C)              |  |

| 3.1.6.2 | Overflow (V)                  |  |

| 3.1.6.3 | Zero (Z)                      |  |

| 3.1.6.4 | Negative (N)                  |  |

| 3.1.6.5 | Interrupt Mask (I)            |  |

| 3.1.6.6 | Half Carry (H)                |  |

| 3.1.6.7 | X Interrupt Mask (X)          |  |

| 3.1.6.8 | Stop Disable (S)              |  |

Semiconductor, Inc.

Freescale

# TABLE OF CONTENTS (Continued) Title

# Paragraph

Page

| 3.2   | Data Types      |  |

|-------|-----------------|--|

| 3.3   |                 |  |

| 3.4   |                 |  |

| 3.4.1 | Immediate       |  |

| 3.4.2 | Direct          |  |

| 3.4.3 | Extended        |  |

| 3.4.4 | Indexed         |  |

| 3.4.5 | Inherent        |  |

| 3.4.6 | Relative        |  |

| 3.5   | Instruction Set |  |

|       |                 |  |

# SECTION 40PERATING MODES AND ON-CHIP MEMORY

| 4.1     | Operating Modes                             | 4-1  |

|---------|---------------------------------------------|------|

| 4.1.1   | Single-Chip Operating Mode                  | 4-1  |

| 4.1.2   | Expanded Operating Mode                     |      |

| 4.1.3   | Special Test Mode                           |      |

| 4.1.4   | Special Bootstrap Mode                      |      |

| 4.2     | On-Chip Memory                              |      |

| 4.2.1   | Mapping Allocations                         | 4-2  |

| 4.2.2   | Memory Map                                  | 4-3  |

| 4.2.2.1 | RAM                                         | 4-3  |

| 4.2.2.2 | Bootloader ROM                              | 4-4  |

| 4.2.2.3 | EEPROM                                      | 4-4  |

| 4.2.3   | Registers                                   | 4-4  |

| 4.3     | System Initialization                       | 4-6  |

| 4.3.1   | Mode Selection                              | 4-7  |

| 4.3.1.1 | HPRIO Register                              | 4-8  |

| 4.3.2   | Initialization                              | 4-9  |

| 4.3.2.1 | CONFIG Register                             | 4-9  |

| 4.3.2.2 | INIT Register                               | 4-10 |

| 4.3.2.3 | OPTION Register                             | 4-11 |

| 4.3.2.4 | OPT2 Register                               | 4-12 |

| 4.3.2.5 | Block Protect Register (BPROT)              | 4-13 |

| 4.4     | EEPROM and CONFIG Register                  | 4-14 |

| 4.4.1   | EEPROM                                      | 4-14 |

| 4.4.1.1 | EEPROM Programming                          | 4-14 |

| 4.4.1.2 | EEPROM Bulk Erase                           | 4-15 |

| 4.4.1.3 | EEPROM Row Erase                            | 4-15 |

| 4.4.1.4 | EEPROM Byte Erase                           | 4-16 |

| 4.4.2   | PPROG EEPROM Programming Control Register . | 4-16 |

| 4.4.3   | CONFIG Register Programming                 | 4-17 |

TECHNICAL DATA

### TABLE OF CONTENTS (Continued) Title

Paragraph

Page

### **SECTION 9 TIMING SYSTEM**

| 9.1    | Timer Structure                                 | 9-3  |

|--------|-------------------------------------------------|------|

| 9.2    | Input Capture                                   | 9-5  |

| 9.2.1  | Timer Control Register 2                        | 9-5  |

| 9.2.2  | Timer Input Capture Registers                   | 9-6  |

| 9.2.3  | Timer Input Capture 4/Output Compare 5 Register | 9-6  |

| 9.3    | Output Compare                                  | 9-6  |

| 9.3.1  | Timer Output Compare Registers                  | 9-7  |

| 9.3.2  | Timer Compare Force Register                    | 9-8  |

| 9.3.3  | Output Compare Mask Registers                   | 9-8  |

| 9.3.4  | Output Compare Data Register                    | 9-9  |

| 9.3.5  | Timer Counter Register                          | 9-9  |

| 9.3.6  | Timer Control Register 1                        | 9-9  |

| 9.3.7  | Timer Interrupt Mask Register 1                 | 9-10 |

| 9.3.8  | Timer Interrupt Flag Register 1                 | 9-11 |

| 9.3.9  | Timer Interrupt Mask Register 2                 | 9-11 |

| 9.3.10 | Timer Interrupt Flag Register 2                 | 9-12 |

| 9.4    | Real-Time Interrupt                             | 9-12 |

| 9.4.1  | Timer Interrupt Mask Register 2                 | 9-13 |

| 9.4.2  | Timer Interrupt Flag Register 2                 | 9-14 |

| 9.4.3  | Pulse Accumulator Control Register              | 9-14 |

| 9.5    | Computer Operating Properly Watchdog Function   | 9-15 |

| 9.6    | Pulse Accumulator                               | 9-15 |

| 9.6.1  | Pulse Accumulator Control Register              | 9-16 |

| 9.6.2  | Pulse Accumulator Count Register                | 9-17 |

| 9.6.3  | Pulse Accumulator Status and Interrupt Bits     | 9-18 |

|        |                                                 |      |

# SECTION 10 ANALOG-TO-DIGITAL CONVERTER

| 10.1   | Overview                                |  |

|--------|-----------------------------------------|--|

| 10.1.1 | Multiplexer                             |  |

| 10.1.2 | Analog Converter                        |  |

| 10.1.3 | Digital Control                         |  |

| 10.1.4 | Result Registers                        |  |

| 10.1.5 | A/D Converter Clocks                    |  |

| 10.1.6 | Conversion Sequence                     |  |

| 10.2   | A/D Converter Power-Up and Clock Select |  |

| 10.3   | Conversion Process                      |  |

| 10.4   | Channel Assignments                     |  |

| 10.5   | Single-Channel Operation                |  |

| 10.6   | Multiple-Channel Operation              |  |

### TABLE OF CONTENTS (Continued) Title

## Paragraph

Page

| 10.7 | Operation in STOP and WAIT Modes |  |

|------|----------------------------------|--|

| 10.8 | A/D Control/Status Registers     |  |

| 10.9 | A/D Converter Result Registers   |  |

# **APPENDIX A ELECTRICAL CHARACTERISTICS**

# APPENDIX BMECHANICAL DATA AND ORDERING INFORMATION

| B.1 | Pin Assignments      | B-1 |

|-----|----------------------|-----|

|     | Package Dimensions   |     |

|     | Ordering Information |     |

# APPENDIX CDEVELOPMENT SUPPORT

| C.1 | MC68HC11F1 Development Tools                                 | C-1 |

|-----|--------------------------------------------------------------|-----|

| C.2 | MC68HC11EVS — Evaluation System                              | C-1 |

| C.3 | M68MMDS11 — Modular Development System for M68HC11 Devices . | C-1 |

# LIST OF ILLUSTRATIONS (Continued) Title

# Figure

Page

| A-11 | SPI Master Timing (CPHA = 1)     | A-15 |

|------|----------------------------------|------|

|      | SPI Slave Timing (CPHA = 0)      |      |

|      | SPI Slave Timing (CPHA = 1)      |      |

|      | MC68HC11F1 68-Pin PLCC           |      |

| B-2  | MC68HC11F1 80-Pin Quad Flat Pack | B-2  |

TECHNICAL DATA

# **SECTION 1INTRODUCTION**

The MC68HC11F1 high-performance microcontroller unit (MCU) is an enhanced derivative of the M68HC11 family of microcontrollers and includes many advanced features. This MCU, with a nonmultiplexed expanded bus, is characterized by high speed and low power consumption. The fully static design allows operation at frequencies from 4 MHz to dc.

# 1.1 Features

- M68HC11 Central Processing Unit (CPU)

- Power Saving STOP and WAIT Modes

- 512 Bytes Electrically Erasable Programmable Read-Only Memory (EEPROM)

- 1024 Bytes RAM, Data Retained During Standby

- Nonmultiplexed Address and Data Buses

- Enhanced 16-Bit Timer

- Three Input Capture (IC) Channels

- Four Output Compare (OC) Channels

- One Additional Channel, Selectable as Fourth IC or Fifth OC

- 8-Bit Pulse Accumulator

- Real-Time Interrupt Circuit

- Computer Operating Properly (COP) Watchdog

- Enhanced Asynchronous Nonreturn to Zero (NRZ) Serial Communications Interface (SCI)

- Enhanced Synchronous Serial Peripheral Interface (SPI)

- Eight-Channel 8-Bit Analog-to-Digital (A/D) Converter

- Four Chip-Select Signal Outputs with Programmable Clock Stretching

Two I/O Chip Selects

- Two I/O Chip Selects

- One Program Chip Select

- One General-Purpose Chip Select

- Available in 68-Pin Plastic Leaded Chip Carrier (PLCC) and 80-Pin Plastic Quad Flat Pack (QFP)

TECHNICAL DATA

INTRODUCTION

## 2.2 Reset (RESET)

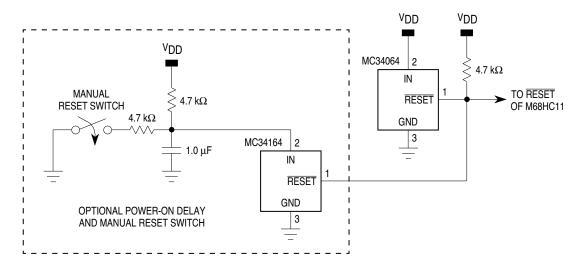

An active low bidirectional control signal, RESET, acts as an input to initialize the MCU to a known start-up state. It also acts as an open-drain output to indicate that an internal failure has been detected in either the clock monitor or COP watchdog circuit. The CPU distinguishes between internal and external reset conditions by sensing whether the reset pin rises to a logic one in less than two E-clock cycles after a reset has occurred. It is not advisable to connect an external resistor-capacitor (RC) power-up delay circuit to the reset pin of M68HC11 devices because the circuit charge time constant can cause the device to misinterpret the type of reset that occurred. Refer to **SECTION 5 RESETS AND INTERRUPTS** for further information.

**Figure 2-3** illustrates a reset circuit that uses an external switch. Other circuits can be used, however, it is important to incorporate a low voltage interrupt (LVI) circuit to prevent operation at insufficient voltage levels which could result in erratic behavior or corruption of RAM.

Figure 2-3 External Reset Circuit

# 2.3 E-Clock Output (E)

E is the output connection for the internally generated E clock. The signal from E is used as a timing reference. The frequency of the E-clock output is one fourth that of the input frequency at the EXTAL pin. When E-clock output is low, an internal process is taking place. When it is high, data is being accessed. All clocks, including the E clock, are halted when the MCU is in STOP mode. The E clock can be turned off in single-chip modes to reduce the effects of radio frequency interference (RFI). Refer to **SECTION 9 TIMING SYSTEM**.

# 2.4 Crystal Driver and External Clock Input (XTAL, EXTAL)

These two pins provide the interface for either a crystal or a CMOS-compatible clock to control the internal clock generator circuitry. Either a crystal oscillator or a CMOS compatible clock can be used. The resulting E-clock rate is the input frequency divided by four.

**PIN DESCRIPTIONS**

# 3.1.6.3 Zero (Z)

The Z bit is set if the result of an arithmetic, logic, or data manipulation operation is zero. Otherwise, the Z bit is cleared. Compare instructions do an internal implied sub-traction and the condition codes, including Z, reflect the results of that subtraction. A few operations (INX, DEX, INY, and DEY) affect the Z bit and no other condition flags. For these operations, only = and - conditions can be determined.

# 3.1.6.4 Negative (N)

The N bit is set if the result of an arithmetic, logic, or data manipulation operation is negative (MSB = 1). Otherwise, the N bit is cleared. A result is said to be negative if its most significant bit (MSB) is a one. A quick way to test whether the contents of a memory location has the MSB set is to load it into an accumulator and then check the status of the N bit.

# 3.1.6.5 Interrupt Mask (I)

The interrupt request (IRQ) mask (I bit) is a global mask that disables all maskable interrupt sources. While the I bit is set, interrupts can become pending, but the operation of the CPU continues uninterrupted until the I bit is cleared. After any reset, the I bit is set by default and can only be cleared by a software instruction. When an interrupt is recognized, the I bit is set after the registers are stacked, but before the interrupt vector is fetched. After the interrupt has been serviced, a return from interrupt instruction is normally executed, restoring the registers to the values that were present before the interrupt occurred. Normally, the I bit is zero after a return from interrupt is executed. Although the I bit can be cleared within an interrupt service routine, "nesting" interrupts in this way should only be done when there is a clear understanding of latency and of the arbitration mechanism. Refer to **SECTION 5 RESETS AND INTERRUPTS**.

# 3.1.6.6 Half Carry (H)

The H bit is set when a carry occurs between bits 3 and 4 of the arithmetic logic unit during an ADD, ABA, or ADC instruction. Otherwise, the H bit is cleared. Half carry is used during BCD operations.

### 3.1.6.7 X Interrupt Mask (X)

The  $\overline{XIRQ}$  mask (X) bit disables interrupts from the  $\overline{XIRQ}$  pin. After any reset, X is set by default and must be cleared by a software instruction. When an  $\overline{XIRQ}$  interrupt is recognized, the X and I bits are set after the registers are stacked, but before the interrupt vector is fetched. After the interrupt has been serviced, an RTI instruction is normally executed, causing the registers to be restored to the values that were present before the interrupt occurred. The X interrupt mask bit is set only by hardware (RESET or  $\overline{XIRQ}$  acknowledge). X is cleared only by program instruction (TAP, where the associated bit of A is zero; or RTI, where bit 6 of the value loaded into the CCR from the stack has been cleared). There is no hardware action for clearing X.

MC68HC11F1 TECHNICAL DATA

A normal mode is selected when MODB is logic one during reset. One of three reset vectors is fetched from address \$FFFA-\$FFFF, and program execution begins from the address indicated by this vector. If MODB is logic zero during reset, the special mode reset vector is fetched from addresses \$BFFA-\$BFFF and software has access to special test features. Refer to **SECTION 5 RESETS AND INTERRUPTS** for information regarding reset vectors.

### 4.3.1.1 HPRIO Register

Bits in the HPRIO register select the highest priority interrupt level, select whether bootstrap ROM is present, and control visibility of internal reads by the CPU. After reset, MDA and SMOD select the operating mode.

| HPRIO  | — Highe | st Priority | / I-Bit Inte | errupt an | d Miscell | aneous |       |       | \$103C       |

|--------|---------|-------------|--------------|-----------|-----------|--------|-------|-------|--------------|

|        | Bit 7   | 6           | 5            | 4         | 3         | 2      | 1     | Bit 0 |              |

|        | RBOOT*  | SMOD*       | MDA*         | IRV       | PSEL3     | PSEL2  | PSEL1 | PSEL0 | ]            |

| RESET: | 0       | 0           | 0            | 0         | 0         | 1      | 1     | 0     | Single Chip  |

|        | 0       | 0           | 1            | 0         | 0         | 1      | 1     | 0     | Expanded     |

|        | 1       | 1           | 0            | 1         | 0         | 1      | 1     | 0     | Bootstrap    |

|        | 0       | 1           | 1            | 1         | 0         | 1      | 1     | 0     | Special Test |

\*Reset states of RBOOT, SMOD, and MDA bits depend on hardware mode selection. Refer to Table 4-3.

### RBOOT — Read Bootstrap ROM

Set to one out of reset in bootstrap mode. Valid while in special modes only. Can be read anytime. Can only be written in special modes.

- 0 = Bootloader ROM disabled and not in map

- 1 = Bootloader ROM enabled and in map at \$BF00-\$BFFF

### SMOD and MDA — Special Mode Select and Mode Select A

The initial value of SMOD is the inverse of the logic level present on the MODB pin at the rising edge of reset. The initial value of MDA equals the logic level present on the MODA pin at the rising edge of reset. These two bits can be read at any time. They can be written at any time in special modes. Neither bit can be written is normal modes. SMOD cannot be set once it has been cleared. Refer to **Table 4-3**.

### IRV — Internal Read Visibility

IRV can be written at any time in special modes (SMOD = 1). In normal modes (SMOD = 0) IRV can be written only once. In expanded and test modes, IRV determines whether internal read visibility is on or off. In single-chip and bootstrap modes, IRV has no meaning or effect.

0 = No internal read visibility on external bus

1 = Data from internal reads is driven out the external data bus.

PSEL[3:0] — Priority Select Bits [3:0]

Refer to 5.3.1 Highest Priority Interrupt and Miscellaneous Register.

For More Information On This Product, Go to: www.freescale.com

Semiconductor, Inc.

reescale

|               | Bit 7                                | 6                    | 5                      | 4                    | 3              | 2            | 1                       | Bit 0                 |

|---------------|--------------------------------------|----------------------|------------------------|----------------------|----------------|--------------|-------------------------|-----------------------|

|               | IO1EN                                | IO1PL                | IO2EN                  | IO2PL                | GCSPR          | PCSEN*       | PSIZA                   | PSIZB                 |

| RESET:        | 0                                    | 0                    | 0                      | 0                    | 0              |              | 0                       | 0                     |

| *PCSEI        | N is set out c                       | of reset in e        | xpanded mo             | odes and c           | leared in sing | gle-chip moo | des.                    |                       |

| 0 :           | - I/O Chip<br>= CSIO1 i<br>= CSIO1 i | is disable           | ed and po              | ort G bit            | •              | eral-purpo   | ose I/O.                |                       |

| 0 :           | - I/O Chip<br>= CSIO1                | active lo            | W                      | Select               |                |              |                         |                       |

| 0 :           | - I/O Chip<br>= CSIO2 i<br>= CSIO2 i | is disable           | ed and po              | ort G bit            |                | eral-purpo   | ose I/O.                |                       |

| 0 :           | - I/O Chip<br>= CSIO2                | active lo            | W                      | Select               |                |              |                         |                       |

| 0 :           | •                                    | n chip se            | elect has              | priority of          | over gene      |              | ose chip s<br>am chip s |                       |

| This t<br>0 : |                                      | ut of res<br>G disab | et in exp<br>led and p | anded m<br>port G bi | t 7 availal    | ole as ge    | neral-purp              | chip mode<br>pose I/O |

|               | SIZB — I                             | -<br>rogram          | Chip Se                | lect Size            | e (A or B)     |              |                         |                       |

| PSIZA, P      |                                      |                      | •                      |                      | . ,            |              |                         |                       |

| PSIZA | PSIZB | Size (Bytes) | Address Range |

|-------|-------|--------------|---------------|

| 0     | 0     | 64 K         | \$0000-\$FFFF |

| 0     | 1     | 32 K         | \$8000-\$FFFF |

| 1     | 0     | 16 K         | \$C000-\$FFFF |

| 1     | 1     | 8 K          | \$E000-\$FFFF |

CSGADR — General-Purpose Chip Select Address Register

\$105E

|        | Bit 7 | 6    | 5    | 4    | 3    | 2    | 1 | Bit 0 |

|--------|-------|------|------|------|------|------|---|-------|

|        | GA15  | GA14 | GA13 | GA12 | GA11 | GA10 | — | —     |

| RESET: | 0     | 0    | 0    | 0    | 0    | 0    | 0 | 0     |

### GA[15:10] — General-Purpose Chip Select Base Address

GA[15:10] correspond to MCU address bits ADDR[15:10] and select the starting address of the general-purpose chip select's address range. Which bits are valid depends upon the size selected by GSIZA-GSIZC in CSGSIZ register. Refer to the following table and to Figure 4-4.

### **OPERATING MODES AND ON-CHIP MEMORY**

**TECHNICAL DATA**

For More Information On This Product, Go to: www.freescale.com

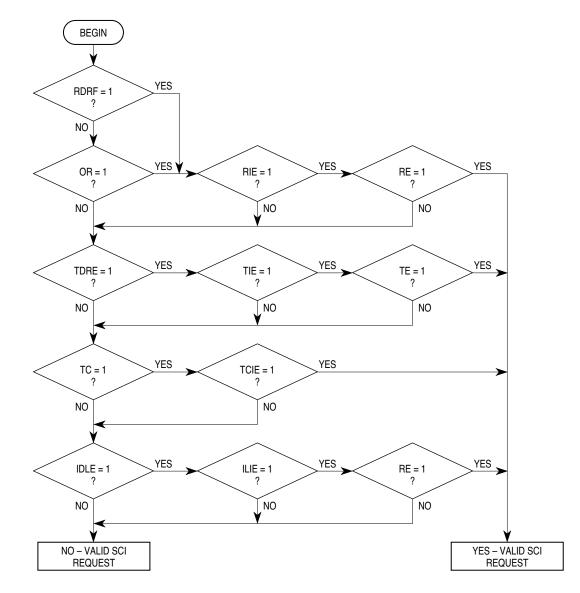

Figure 5-5 Interrupt Source Resolution Within SCI

# 5.5 Low Power Operation

Both STOP and WAIT suspend CPU operation until a reset or interrupt occurs. The WAIT condition suspends processing and reduces power consumption to an intermediate level. The STOP condition turns off all on-chip clocks and reduces power consumption to an absolute minimum while retaining the contents of all 1024 bytes of RAM.

**RESETS AND INTERRUPTS**

# 5.5.1 WAIT

The WAI opcode places the MCU in the WAIT condition, during which the CPU registers are stacked and CPU processing is suspended until a qualified interrupt is detected. The interrupt can be an external  $\overline{IRQ}$ , an  $\overline{XIRQ}$ , or any of the internally generated interrupts, such as the timer or serial interrupts. The on-chip crystal oscillator remains active throughout the WAIT standby period.

The reduction of power in the WAIT condition depends on how many internal clock signals driving on-chip peripheral functions can be shut down. The CPU is always shut down during WAIT. While in the wait state, the address/data bus repeatedly runs read cycles to the address where the CCR contents were stacked. Ensuring that the stack contents are placed in internal RAM will further reduce power consumption. The MCU leaves the wait state when it senses any interrupt that has not been masked.

The free-running timer system is shut down only if the I bit is set to one and the COP system is disabled by NOCOP being set to one. Several other systems can also be in a reduced power consumption state depending on the state of software-controlled configuration control bits. Power consumption by the analog-to-digital (A/D) converter is not affected significantly by the WAIT condition. However, the A/D converter current can be eliminated by writing the ADPU bit to zero. The SPI system is enabled or disabled by the SPE control bit. The SCI transmitter is enabled or disabled by the TE bit, and the SCI receiver is enabled or disabled by the RE bit. Therefore the power consumption in WAIT is dependent on the particular application.

# 5.5.2 STOP

**TECHNICAL DATA**

Executing the STOP instruction while the S bit in the CCR is equal to zero places the MCU in the STOP condition. If the S bit is not zero, the STOP opcode is treated as a no-op (NOP). The STOP condition offers minimum power consumption because all clocks, including the crystal oscillator, are stopped while in this mode. To exit STOP and resume normal processing, a logic low level must be applied to one of the external interrupts (IRQ or XIRQ) or to the RESET pin. A pending edge-triggered IRQ can also bring the CPU out of STOP.

Because all clocks are stopped in this mode, all internal peripheral functions also stop. The data in the internal RAM is retained as long as  $V_{DD}$  power is maintained. The CPU state and I/O pin levels are static and are unchanged by STOP. Therefore, when an interrupt restarts the system, the MCU resumes processing as if there were no interruption. If reset is used to restart the system a normal reset sequence results where all I/O pins and functions are also restored to their initial states.

To use the  $\overline{IRQ}$  pin as a means of recovering from STOP, the I bit in the CCR must be clear ( $\overline{IRQ}$  not masked). The  $\overline{XIRQ}$  pin can be used to wake up the MCU from STOP regardless of the state of the X bit in the CCR, although the recovery sequence depends on the state of the X bit. If X is set to zero ( $\overline{XIRQ}$  not masked), the MCU starts up, beginning with the stacking sequence leading to normal service of the  $\overline{XIRQ}$  request. If X is set to one ( $\overline{XIRQ}$  masked or inhibited), then processing continues with the instruction that immediately follows the STOP instruction, and no  $\overline{XIRQ}$  interrupt service is requested or pending.

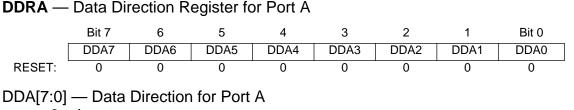

0 = Input

1 = Output

### NOTE

To enable PA3 as fourth input capture, set the I4/O5 bit in the PACTL register. Otherwise, PA3 is configured as a fifth output compare out of reset, with bit I4/O5 being cleared. If the DDA3 bit is set (configuring PA3 as an output), and IC4 is enabled, writes to PA3 cause edges on the pin to result in input captures. Writing to TI4/O5 has no effect when the TI4/O5 register is acting as IC4. PA7 drives the pulse accumulator input but also can be configured for general-purpose I/O, or output compare. Note that even when PA7 is configured as an output, the pin still drives the pulse accumulator input.

### 6.2 Port B

Reset state is mode dependent. In single-chip or bootstrap modes, port B pins are general-purpose outputs. In expanded and test modes, port B pins are high-order address outputs and PORTB is not in the memory map.

| PORTB | - Port | B Data |

|-------|--------|--------|

|-------|--------|--------|

Bit 7 6 5 4 3 2 1 Bit 0 PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0 S. Chip or PB7 PB6 PB5 PB4 PB3 PB2 PB1 PB0 Boot: RESET: 0 0 0 0 0 0 0 0 Expan. or ADDR13 ADDR12 ADDR11 ADDR15 ADDR14 ADDR10 ADDR9 ADDR8 Test:

# 6.3 Port C

Reset state is mode dependent. In single-chip and bootstrap modes, port C pins are high-impedance inputs. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. In expanded or test modes, port C pins are data bus inputs/outputs and PORTC is not in the memory map. The R/W signal is used to control the direction of data transfers.

The CWOM control bit in the OPT2 register disables port C's P-channel output drivers. Because the N-channel driver is not affected by CWOM, setting CWOM causes port C to become an open-drain-type output port suitable for wired-OR operation. In wired-OR mode, (PORTC bits are at logic level zero), pins are actively driven low by the Nchannel driver. When a port C bit is at logic level one, the associated pin is in a high-

| P | AR | AL | LEL | INP | UT/   | OU | TP | UΤ |

|---|----|----|-----|-----|-------|----|----|----|

|   |    |    |     |     | • • • |    |    |    |

MC68HC11F1 TECHNICAL DATA

\$1004

Semiconductor, Inc

0

eescal

# Freescale Semiconductor, Inc.

R8 — Receive Data Bit 8

If M bit is set, R8 stores the ninth bit in the receive data character.

T8 — Transmit Data Bit 8

If M bit is set, T8 stores the ninth bit in the transmit data character.

- M Mode (Select Character Format)

- 0 = Start bit, 8 data bits, 1 stop bit

- 1 = Start bit, 9 data bits, 1 stop bit

- WAKE Wakeup by Address Mark/Idle

- 0 = Wakeup by IDLE line recognition

- 1 = Wakeup by address mark (most significant data bit set)

# 7.6.3 Serial Communications Control Register 2

The SCCR2 register provides the control bits that enable or disable individual SCI functions.

# SCCR2 — SCI Control Register 2

### Bit 7 6 5 4 3 2 Bit 0 1 RE TIE TCIE RIE ILIE TE RWU SBK RESET: 0 0 0 0 0 0 0 0

# TIE — Transmit Interrupt Enable

0 = TDRE interrupts disabled

1 = SCI interrupt requested when TDRE status flag is set

# TCIE — Transmit Complete Interrupt Enable

- 0 = TC interrupts disabled

- 1 = SCI interrupt requested when TC status flag is set

- RIE Receiver Interrupt Enable

- 0 = RDRF and OR interrupts disabled

- 1 = SCI interrupt requested when RDRF flag or the OR status flag is set

# ILIE — Idle-Line Interrupt Enable

- 0 = IDLE interrupts disabled

- 1 = SCI interrupt requested when IDLE status flag is set

# TE — Transmitter Enable

When TE goes from zero to one, one unit of idle character time (logic one) is queued as a preamble.

- 0 = Transmitter disabled

- 1 = Transmitter enabled

- RE Receiver Enable

- 0 = Receiver disabled

- 1 = Receiver enabled

TDRE and TC flags are normally set when the transmitter is first enabled (TE set to one). The TDRE flag indicates there is room in the transmit queue to store another data character in the TDR. The TIE bit is the local interrupt mask for TDRE. When TIE is zero, TDRE must be polled. When TIE and TDRE are one, an interrupt is requested.

The TC flag indicates the transmitter has completed the queue. The TCIE bit is the local interrupt mask for TC. When TCIE is zero, TC must be polled; when TCIE is one and TC is one, an interrupt is requested.

Writing a zero to TE requests that the transmitter stop when it can. The transmitter completes any transmission in progress before actually shutting down. Only an MCU reset can cause the transmitter to stop and shut down immediately. If TE is written to zero when the transmitter is already idle, the pin reverts to its general-purpose I/O function (synchronized to the bit-rate clock). If anything is being transmitted when TE is written to zero, that character is completed before the pin reverts to general-purpose I/O, but any other characters waiting in the transmit queue are lost. The TC and TDRE flags are set at the completion of this last character, even though TE has been disabled.

# 7.7.1 Receiver Flags

The SCI receiver has five status flags, three of which can generate interrupt requests. The status flags are set by the SCI logic in response to specific conditions in the receiver. These flags can be read (polled) at any time by software. Refer to Figure 7–4, which shows SCI interrupt arbitration.

When an overrun takes place, the new character is lost, and the character that was in its way in the parallel RDR is undisturbed. RDRF is set when a character has been received and transferred into the parallel RDR. The OR flag is set instead of RDRF if overrun occurs. A new character is ready to be transferred into RDR before a previous character is read from RDR.

The NF and FE flags provide additional information about the character in the RDR, but do not generate interrupt requests.

The last receiver status flag and interrupt source come from the IDLE flag. The RxD line is idle if it has constantly been at logic one for a full character time. The IDLE flag is set only after the RxD line has been busy and becomes idle, which prevents repeated interrupts for the whole time RxD remains idle.

|        |        |    | -  | -  |    |    |   |       |             |

|--------|--------|----|----|----|----|----|---|-------|-------------|

| \$1016 | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 | TOC1 (High) |

| \$1017 | Bit 7  | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 | TOC1 (Low)  |

| \$1018 | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 | TOC2 (High) |

| \$1019 | Bit 7  | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 | TOC2 (Low)  |

| \$101A | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 | TOC3 (High) |

| \$101B | Bit 7  | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 | TOC3 (Low)  |

| \$101C | Bit 15 | 14 | 13 | 12 | 11 | 10 | 9 | Bit 8 | TOC4 (High) |

| \$101D | Bit 7  | 6  | 5  | 4  | 3  | 2  | 1 | Bit 0 | TOC4 (Low)  |

### TOC1-TOC4 — Timer Output Compare

All TOCx register pairs reset to ones (\$FFFF).

### 9.3.2 Timer Compare Force Register

The CFORC register allows forced early compares. FOC[1:5] correspond to the five output compares. These bits are set for each output compare that is to be forced. The action taken as a result of a forced compare is the same as if there were a match between the OCx register and the free-running counter, except that the corresponding interrupt status flag bits are not set. The forced channels trigger their programmed pin actions to occur at the next timer count transition after the write to CFORC.

The CFORC bits should not be used on an output compare function that is programmed to toggle its output on a successful compare because a normal compare that occurs immediately before or after the force can result in an undesirable operation.

### **CFORC** — Timer Compare Force

|        | Bit 7 | 6    | 5    | 4    | 3    | 2 | 1 | Bit 0 |

|--------|-------|------|------|------|------|---|---|-------|

|        | FOC1  | FOC2 | FOC3 | FOC4 | FOC5 | — | — | —     |

| RESET: | 0     | 0    | 0    | 0    | 0    | 0 | 0 | 0     |

FOC[1:5] — Force Output Comparison

When the FOC bit associated with an output compare circuit is set, the output compare circuit immediately performs the action it is programmed to do when an output match occurs.

- 0 = Not affected

- 1 = Output x action occurs

Bits [2:0] - Not implemented

Always read zero

### 9.3.3 Output Compare Mask Registers

Use OC1M with OC1 to specify the bits of port A that are affected by a successful OC1 compare. The bits of the OC1M register correspond to PA[7:3].

# \$1016-\$101D

\$100B

PEDGE — Pulse Accumulator Edge Control Refer to **9.6 Pulse Accumulator**.

- Bit 3 Not implemented Always reads zero

- I4/O5 Input Capture 4/Output Compare Refer to **9.6 Pulse Accumulator**.

# RTR[1:0] — RTI Interrupt Rate Select

These two bits determine the rate at which the RTI system requests interrupts. The RTI system is driven by an E divided by 2<sup>13</sup> rate clock that is compensated so it is independent of the timer prescaler. These two control bits select an additional division factor. Refer to **Table 9-5**.

# 9.5 Computer Operating Properly Watchdog Function

The clocking chain for the COP function, tapped off of the main timer divider chain, is only superficially related to the main timer system. The CR[1:0] bits in the OPTION register and the NOCOP bit in the CONFIG register determine the status of the COP function. One additional register, COPRST, is used to arm and clear the COP watch-dog reset system. Refer to **SECTION 5 RESETS AND INTERRUPTS** for a more detailed discussion of the COP function.

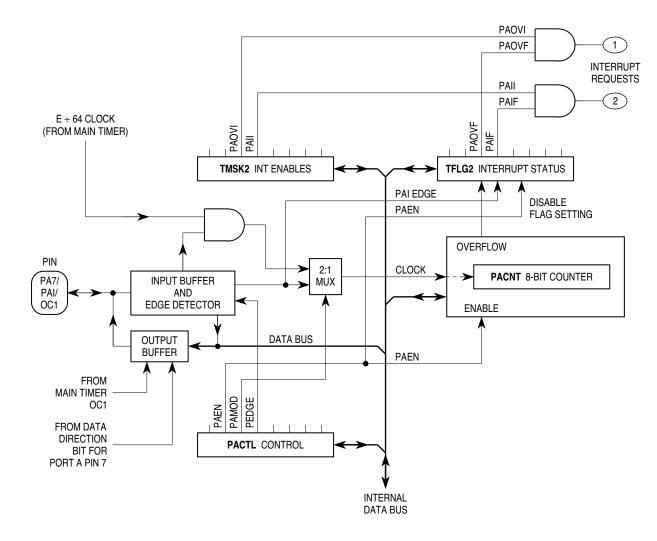

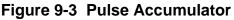

### 9.6 Pulse Accumulator

The MC68HC11F1 MCUs have an 8-bit counter that can be configured to operate either as a simple event counter, or for gated time accumulation, depending on the state of the PAMOD bit in the PACTL register. Refer to the pulse accumulator block diagram, **Figure 9-3**.

In the event counting mode, the 8-bit counter is incremented by pulses on an external pin (PAI). The maximum clocking rate for the external event counting mode is the E clock divided by two. In gated time accumulation mode, a free-running E-clock  $\div$  64 signal drives the 8-bit counter, but only while the external PAI pin is activated. Refer to **Table 9-6**. The pulse accumulator counter can be read or written at any time.

| Table 9-5 Pulse Accumulator | Timing |

|-----------------------------|--------|

|-----------------------------|--------|

| Crystal Frequency<br>(4*E) | E Clock<br>(E) | Cycle Time<br>(1/E) | 2 <sup>6</sup> /E<br>(64/E) | PACNT Overflow<br>(16384/E) |

|----------------------------|----------------|---------------------|-----------------------------|-----------------------------|

| 4.0 MHz                    | 1.0 MHz        | 1000 ns             | 64 μs                       | 16.384 ms                   |

| 8.0 MHz                    | 2.0 MHz        | 500 ns              | 32 µs                       | 8.192 ms                    |

| 12.0 MHz                   | 3.0 MHz        | 333 ns              | 21.33 μs                    | 5.461 ms                    |

| 16.0 MHz                   | 4.0 MHz        | 250 ns              | 16.0 μs                     | 4.096 ms                    |

Pulse accumulator control bits are also located within two timer registers, TMSK2 and TFLG2, as described in the following paragraphs.

### 9.6.1 Pulse Accumulator Control Register

Four of this register's bits control an 8-bit pulse accumulator system. Another bit enables either the OC5 function or the IC4 function, while two other bits select the rate for the real-time interrupt system.

TIMING SYSTEM

MC68HC11F1 TECHNICAL DATA

# Freescale Semiconductor, Inc.

### **10.4 Channel Assignments**

The multiplexer allows the A/D converter to select one of sixteen analog signals. Eight of these channels correspond to port E input lines, four of the channels are internal reference points or test functions, and four channels are reserved. Refer to **Table 10-1**.

| Channel<br>Number | Channel<br>Signal     | Result in ADRx if<br>MULT = 1 |

|-------------------|-----------------------|-------------------------------|

| 1                 | AN0                   | ADR1                          |

| 2                 | AN1                   | ADR2                          |

| 3                 | AN2                   | ADR3                          |

| 4                 | AN3                   | ADR4                          |

| 5                 | AN4                   | ADR1                          |

| 6                 | AN5                   | ADR2                          |

| 7                 | AN6                   | ADR3                          |

| 8                 | AN7                   | ADR4                          |

| 9                 | Reserved              | —                             |

| 10                | Reserved              | —                             |

| 11                | Reserved              | —                             |

| 12                | Reserved              | —                             |

| 13                | V <sub>RH</sub> *     | ADR1                          |

| 14                | V <sub>RL</sub> *     | ADR2                          |

| 15                | (V <sub>RH</sub> )/2* | ADR3                          |

| 16                | Reserved*             | ADR4                          |

Table 10-1 A/D Converter Channel Assignments

\*Used for factory testing

### **10.5 Single-Channel Operation**

There are two types of single-channel operation. When SCAN = 0, the first type, the single selected channel is converted four consecutive times. The first result is stored in A/D result register 1 (ADR1), and the fourth result is stored in ADR4. After the fourth conversion is complete, all conversion activity is halted until a new conversion command is written to the ADCTL register. In the second type of single-channel operation, SCAN = 1, conversions continue to be performed on the selected channel with the fifth conversion being stored in register ADR1 (overwriting the first conversion result), the sixth conversion overwriting ADR2, and so on.

# **10.6 Multiple-Channel Operation**

There are two types of multiple-channel operation. When SCAN = 0, the first type, a selected group of four channels is converted one time each. The first result is stored in A/D result register 1 (ADR1), and the fourth result is stored in ADR4. After the fourth conversion is complete, all conversion activity is halted until a new conversion command is written to the ADCTL register. In the second type of multiple-channel operation, SCAN = 1, conversions continue to be performed on the selected group of channels with the fifth conversion being stored in register ADR1 (replacing the earlier conversion result for the first channel in the group), the sixth conversion overwriting ADR2, and so on.

MC68HC11F1 TECHNICAL DATA

For More Information On This Product, Go to: www.freescale.com

### **Table A-3 DC Electrical Characteristics**

| Charac                                                                                                            | teristic                                                                         | Symbol                             | Min                                            | Max                                            | Unit           |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------|------------------------------------------------|------------------------------------------------|----------------|

| Output Voltage (Note 1)<br>All Outputs Exce<br>I <sub>Load</sub> = ± 10.0 μA                                      | All Outputs except XTAL ept XTAL, RESET, and MODA                                | V <sub>OL</sub><br>V <sub>OH</sub> | V <sub>DD</sub> – 0.1                          | 0.1                                            | V<br>V         |

| Output High Voltage (Note 1)<br>All Outputs Exce<br>$I_{Load} = -0.8 \text{ mA}, V_{DD} = 4.$                     | ept XTAL, RESET, and MODA<br>5 V                                                 | V <sub>OH</sub>                    | V <sub>DD</sub> – 0.8                          | _                                              | V              |

| Output Low Voltage<br>I <sub>Load</sub> = 1.6 mA                                                                  | All Outputs Except XTAL                                                          | V <sub>OL</sub>                    | _                                              | 0.4                                            | V              |

| Input High Voltage                                                                                                | All Inputs Except RESET<br>RESET                                                 | V <sub>IH</sub>                    | 0.7 x V <sub>DD</sub><br>0.8 x V <sub>DD</sub> | V <sub>DD</sub> + 0.3<br>V <sub>DD</sub> + 0.3 | V<br>V         |

| Input Low Voltage                                                                                                 | All Inputs                                                                       | V <sub>IL</sub>                    | V <sub>SS</sub> -0.3                           | 0.2 x V <sub>DD</sub>                          | V              |

| I/O Ports, Three-State Leakage $V_{in} = V_{IH}$ or $V_{IL}$                                                      | Ports A, B, C, D, F, G<br>MODA/LIR, RESET                                        | I <sub>OZ</sub>                    | _                                              | ±10                                            | μA             |

| Input Leakage Current (Note 2)<br>$V_{in} = V_{DD} \text{ or } V_{SS}$ IR<br>$V_{in} = V_{DD} \text{ or } V_{SS}$ | Q, XIRQ on standard devices<br>MODB/V <sub>STBY</sub> ,<br>XIRQ on EPROM devices | l <sub>in</sub>                    | _                                              | ±1<br>±10                                      | μA<br>μA       |

| Input Current with Pull-Up Resist $V_{in} = V_{IL}$                                                               | stors<br>Ports B, F, and G                                                       | l <sub>ipr</sub>                   | 100                                            | 500                                            | μA             |

| RAM Standby Voltage                                                                                               | Power down                                                                       | V <sub>SB</sub>                    | 4.0                                            | V <sub>DD</sub>                                | V              |

| RAM Standby Current                                                                                               | Power down                                                                       | I <sub>SB</sub>                    | —                                              | 20                                             | μA             |

| Input Capacitance<br>Ports A, B, C                                                                                | PE[7:0], IRQ, XIRQ, EXTAL<br>, D, F, G, MODA/LIR, RESET                          | C <sub>in</sub>                    | _                                              | 8<br>12                                        | pF<br>pF       |

| Output Load Capacitance                                                                                           | All Outputs Except PD[4:1],<br>4XOUT, XTAL, MODA/LIR<br>PD[4:1]<br>4XOUT         | CL                                 |                                                | 90<br>200<br>30                                | pF<br>pF<br>pF |

$V_{DD}$  = 5.0 Vdc ± 5%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted

| Characteristic                                                 | Symbol           | 2 MHz | 3 MHz | 4 MHz | Unit |

|----------------------------------------------------------------|------------------|-------|-------|-------|------|

| Maximum Total Supply Current (Note 3)<br>RUN:<br>Expanded Mode | I <sub>DD</sub>  | 27    | 38    | 50    | mA   |

| WAIT: (All Peripheral Functions Shut Down)<br>Expanded Mode    | W <sub>IDD</sub> | 15    | 20    | 25    | mA   |

| STOP:<br>No Clocks, Expanded Mode                              | S <sub>IDD</sub> | 50    | 50    | 50    | μA   |

| Maximum Power Dissipation<br>Expanded Mode                     | PD               | 149   | 209   | 275   | mW   |

NOTES:

**TECHNICAL DATA**

1. V<sub>OH</sub> specification for RESET and MODA is not applicable because they are open-drain pins. V<sub>OH</sub> specification not applicable to ports C and D in wired-OR mode.

2. Refer to A/D specification for leakage current for port E.

3. EXTAL is driven with a square wave, and

$t_{cvc}$  = 500 ns for 2 MHz rating;

$t_{cyc} = 333 \text{ ns for 3 MHz rating;} \\ t_{cyc} = 333 \text{ ns for 3 MHz rating;} \\ t_{cyc} = 250 \text{ ns for 4 MHz rating;} \\ V_{IL} \le 0.2 \text{ V; } V_{IH} \ge V_{DD} - 0.2 \text{ V; No dc loads.}$

### **ELECTRICAL CHARACTERISTICS**