# E·XFI

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | HC11                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 2MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | POR, WDT                                                              |

| Number of I/O              | 30                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | 512 x 8                                                               |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                                         |

| Data Converters            | A/D 8x8b                                                              |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 68-LCC (J-Lead)                                                       |

| Supplier Device Package    | 68-PLCC (24.21x24.21)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchc11f1cfne2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Freescale Semiconductor, Inc.

#### TABLE OF CONTENTS (Continued) Title

#### Paragraph

Page

| 3.2   | Data Types      |  |

|-------|-----------------|--|

| 3.3   |                 |  |

| 3.4   |                 |  |

| 3.4.1 | Immediate       |  |

| 3.4.2 | Direct          |  |

| 3.4.3 | Extended        |  |

| 3.4.4 | Indexed         |  |

| 3.4.5 | Inherent        |  |

| 3.4.6 | Relative        |  |

| 3.5   | Instruction Set |  |

|       |                 |  |

#### SECTION 40PERATING MODES AND ON-CHIP MEMORY

| 4.1     | Operating Modes                             | 4-1  |

|---------|---------------------------------------------|------|

| 4.1.1   | Single-Chip Operating Mode                  | 4-1  |

| 4.1.2   | Expanded Operating Mode                     |      |

| 4.1.3   | Special Test Mode                           |      |

| 4.1.4   | Special Bootstrap Mode                      |      |

| 4.2     | On-Chip Memory                              |      |

| 4.2.1   | Mapping Allocations                         | 4-2  |

| 4.2.2   | Memory Map                                  | 4-3  |

| 4.2.2.1 | RAM                                         | 4-3  |

| 4.2.2.2 | Bootloader ROM                              | 4-4  |

| 4.2.2.3 | EEPROM                                      | 4-4  |

| 4.2.3   | Registers                                   | 4-4  |

| 4.3     | System Initialization                       | 4-6  |

| 4.3.1   | Mode Selection                              | 4-7  |

| 4.3.1.1 | HPRIO Register                              | 4-8  |

| 4.3.2   | Initialization                              | 4-9  |

| 4.3.2.1 | CONFIG Register                             | 4-9  |

| 4.3.2.2 | INIT Register                               | 4-10 |

| 4.3.2.3 | OPTION Register                             | 4-11 |

| 4.3.2.4 | OPT2 Register                               | 4-12 |

| 4.3.2.5 | Block Protect Register (BPROT)              | 4-13 |

| 4.4     | EEPROM and CONFIG Register                  | 4-14 |

| 4.4.1   | EEPROM                                      | 4-14 |

| 4.4.1.1 | EEPROM Programming                          | 4-14 |

| 4.4.1.2 | EEPROM Bulk Erase                           | 4-15 |

| 4.4.1.3 | EEPROM Row Erase                            | 4-15 |

| 4.4.1.4 | EEPROM Byte Erase                           | 4-16 |

| 4.4.2   | PPROG EEPROM Programming Control Register . | 4-16 |

| 4.4.3   | CONFIG Register Programming                 | 4-17 |

TECHNICAL DATA

#### 2.5 Four Times E-Clock Frequency Output (4XOUT)

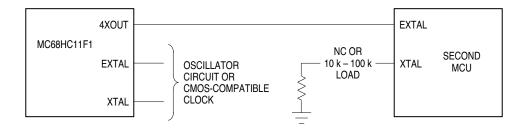

Although the circuit shown in **Figure 2-6** will work for any M68HC11 MCU, the MC68HC11F1 has an additional clock output that is four times the E-clock frequency. This output (4XOUT) can be used to directly drive the EXTAL input of another M68HC11 MCU. Refer to **Figure 2-7**. The 4XOUT output is enabled after reset and can be disabled by clearing the CLK4X bit in the OPT2 register.

Figure 2-7 4XOUT Signal Driving a Second MCU

#### 2.6 Interrupt Request (IRQ)

The  $\overline{IRQ}$  input provides a means of generating asynchronous interrupt requests for the CPU. Either falling-edge triggering or low-level triggering is selected by the IRQE bit in the OPTION register.  $\overline{IRQ}$  is always configured for level-sensitive triggering at reset. Connect an external pull-up resistor, typically 4.7 k $\Omega$ , to V<sub>DD</sub> when  $\overline{IRQ}$  is used in a level-sensitive wired-OR configuration. Refer to **SECTION 5 RESETS AND INTER-RUPTS**.

#### 2.7 Non-Maskable Interrupt (XIRQ)

The  $\overline{XIRQ}$  input provides a means of requesting a non-maskable interrupt after reset initialization. During reset, the X bit in the condition code register (CCR) is set and any interrupt is masked until MCU software enables it. Because the  $\overline{XIRQ}$  input is level sensitive, it can be connected to a multiple-source wired-OR network with an external pull-up resistor to V<sub>DD</sub>.  $\overline{XIRQ}$  is often used as a power loss detect interrupt.

Whenever  $\overline{XIRQ}$  or  $\overline{IRQ}$  are used with multiple interrupt sources ( $\overline{IRQ}$  must be configured for level-sensitive operation if there is more than one source of  $\overline{IRQ}$  interrupt), each source must drive the interrupt input with an open-drain type of driver to avoid contention between outputs. There should be a single pull-up resistor near the MCU interrupt input pin (typically 4.7 k $\Omega$ ). There must also be an interlock mechanism at each interrupt source so that the source holds the interrupt line low until the MCU recognizes and acknowledges the interrupt request. If one or more interrupt sources are still pending after the MCU services a request, the interrupt line will still be held low and the MCU will be interrupted again as soon as the interrupt mask bit in the condition code register (CCR) is cleared (normally upon return from an interrupt). Refer to **SEC-TION 5 RESETS AND INTERRUPTS**.

#### 2.8 MODA and MODB (MODA/LIR and MODB/VSTBY)

During reset, MODA and MODB select one of the four operating modes. Refer to **SEC-TION 4 OPERATING MODES AND ON-CHIP MEMORY**.

After the operating mode has been selected, the  $\overline{\text{LIR}}$  pin provides an open-drain output to indicate that execution of an instruction has begun. The LIR pin is configured for wired-OR operation (only pulls low). A series of E-clock cycles occurs during execution of each instruction. The  $\overline{\text{LIR}}$  signal is asserted (drives low) during the first E-clock cycle of each instruction (opcode fetch). This output is provided for assistance in program debugging.

The V<sub>STBY</sub> pin is used to input RAM standby power. The MCU is powered from the V<sub>DD</sub> signal unless the difference between the level of V<sub>STBY</sub> and V<sub>dd</sub> is greater than one MOS threshold (about 0.7 volts). When these voltages differ by more than 0.7 volts, the internal 768-byte RAM and part of the reset logic are powered from V<sub>STBY</sub> rather than V<sub>DD</sub>. This allows RAM contents to be retained without V<sub>DD</sub> power applied to the MCU. Reset must be driven low before V<sub>DD</sub> is removed and must remain low until V<sub>DD</sub> has been restored to a valid level.

#### 2.9 $V_{RH}$ and $V_{RL}$

These pins provide the reference voltage for the analog-to-digital converter. Bypass capacitors should be used to minimize noise on these signals. Any noise on V<sub>RH</sub> and V<sub>RL</sub> will directly affect A/D accuracy.

#### 2.10 R/W

In expanded and test modes, R/W indicates the direction of transfers on the external data bus. A logic level one on this pin indicates that a read cycle is in progress. A logic zero on this pin indicates that a write cycle is in progress and that no external device should drive the data bus.

The E-clock can be used to enable external devices to drive data onto the data bus during the second half of a read bus cycle (E clock high). R/W can then be used to control the direction of data transfers. R/W drives low when data is being written to the external data bus. R/W will remain low during consecutive data bus write cycles, such as when a double-byte store occurs.

#### 2.11 Port Signals

For the MC68HC11F1, 54 pins are arranged into six 8-bit ports: A, B, C, E, F, and G, and one 6-bit port (D). Each of these seven ports serves a purpose other than I/O, depending on the operating mode or peripheral functions selected. Note that ports B, C, and F are available for I/O functions only in single-chip and bootstrap modes. The pins of ports A, C, D, and G are fully bidirectional. Ports B and F are output-only ports. Port E is an input-only port. Refer to **Table 2-1** for details about the 54 port signals' functions within different operating modes.

PIN DESCRIPTIONS

MC68HC11F1 TECHNICAL DATA

#### 4.3.2 Initialization

Because bits in the following registers control the basic configuration of the MCU, an accidental change of their values could cause serious system problems. The protection mechanism, overridden in special operating modes, requires a write to the protected bits only within the first 64 bus cycles after any reset, or only once after each reset. **Table 4-2** summarizes the write access limited registers.

#### 4.3.2.1 CONFIG Register

CONFIG controls the presence and position of the EEPROM in the memory map. CONFIG also enables the COP watchdog timer.

| CONFIG | <b>6</b> — Syst | em Confi | iguration | Register |   |       |   |       | \$103F       |

|--------|-----------------|----------|-----------|----------|---|-------|---|-------|--------------|

|        | Bit 7           | 6        | 5         | 4        | 3 | 2     | 1 | Bit 0 |              |

|        | EE3             | EE2      | EE1       | EE0      | — | NOCOP | _ | EEON  | ]            |

| RESET: | 1               | 1        | 1         | 1        | 1 | Р     | 1 | 1     | Single Chip  |

|        | 1               | 1        | 1         | 1        | 1 | P(L)  | 1 | 1     | Bootstrap    |

|        | Р               | Р        | Р         | Р        | 1 | Р     | 1 | Р     | Expanded     |

|        | Р               | Р        | Р         | Р        | 1 | P(L)  | 1 | 0     | Special Test |

P indicates a previously programmed bit. P(L) indicates that the bit resets to the logic level held in the latch prior to reset, but the function of COP is controlled by DISR bit in TEST1 register.

The CONFIG register consists of an EEPROM byte and static latches that control the start-up configuration of the MCU. The contents of the EEPROM byte are transferred into static working latches during reset sequences. The operation of the MCU is controlled directly by these latches and not by CONFIG itself. In normal modes, changes to CONFIG do not affect operation of the MCU until after the next reset sequence. When programming, the CONFIG register itself is accessed. When the CONFIG register is read, the static latches are accessed.

These bits can be read at any time. The value read is the one latched into the register from the EEPROM cells during the last reset sequence. A new value programmed into this register cannot be read until after a subsequent reset sequence. Unused bits always read as ones.

In special test mode, the static latches can be written directly at any time. In all modes, CONFIG bits can only be programmed using the EEPROM programming sequence, and are neither readable nor active until latched via the next reset. Refer to **4.4.3 CON-FIG Register Programming**.

EE[3:0] — EEPROM Mapping Control

EE[3:0] select the upper four bits of the EEPROM base address. In single-chip and bootstrap modes, EEPROM is forced to \$FE00-\$FFFF regardless of the value of EE[3:0].

| EE[3:0] | EEPROM Position |

|---------|-----------------|

| 0000    | \$0E00 – \$0FFF |

| 0001    | \$1E00 – \$1FFF |

| 0010    | \$2E00 – \$2FFF |

| 0011    | \$3E00 – \$3FFF |

| 0100    | \$4E00 – \$4FFF |

| 0101    | \$5E00 – \$5FFF |

| 0110    | \$6E00 – \$6FFF |

| 0111    | \$7E00 – \$7FFF |

| 1000    | \$8E00 – \$8FFF |

| 1001    | \$9E00 – \$9FFF |

| 1010    | \$AE00 – \$AFFF |

| 1011    | \$BE00 – \$BFFF |

| 1100    | \$CE00 – \$CFFF |

| 1101    | \$DE00 – \$DFFF |

| 1110    | \$EE00 - \$EFFF |

| 1111    | \$FE00 – \$FFFF |

#### **Table 4-4 EEPROM Mapping**

Bit 3 — Not implemented Always reads one

NOCOP — COP System Disable

0 = COP system enabled (forces reset on time-out)

1 = COP system disabled

Bit 1 — Not implemented Always reads one

EEON — EEPROM Enable

In single-chip modes EEON is forced to one (EEPROM enabled).

0 = 512 bytes of EEPROM is disabled from the memory map

1 = 512 bytes of EEPROM is present in the memory map

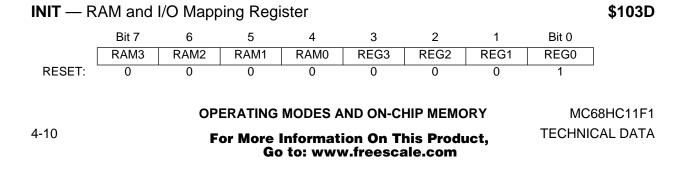

#### 4.3.2.2 INIT Register

The internal registers used to control the operation of the MCU can be relocated on 4-Kbyte boundaries within the memory space with the use of INIT. This 8-bit special-purpose register can change the default locations of the RAM and control registers within the MCU memory map. It can be written only once within the first 64 E-clock cycles after a reset. It then becomes a read-only register.

| Size (Bytes)   | Valid Starting Address<br>Bits |  |  |  |

|----------------|--------------------------------|--|--|--|

| 0 K (Disabled) | None                           |  |  |  |

| 1 K            | GA[15:10]                      |  |  |  |

| 2 K            | GA[15:11]                      |  |  |  |

| 4 K            | GA[15:12]                      |  |  |  |

| 8 K            | GA[15:13]                      |  |  |  |

| 16 K           | GA[15:14]                      |  |  |  |

| 32 K           | GA15                           |  |  |  |

| 64 K           | None                           |  |  |  |

#### Table 4-10 General-Purpose Chip Select Starting Address

#### CSGSIZ — General-Purpose Chip Select Size Control

\$105F

|        | Bit 7 | 6     | 5 | 4     | 3     | 2     | 1     | Bit 0 |

|--------|-------|-------|---|-------|-------|-------|-------|-------|

|        | IO1AV | IO2AV |   | GNPOL | GAVLD | GSIZA | GSIZB | GSIZC |

| RESET: | 0     | 0     | 0 | 0     | 0     | 1     | 1     | 1     |

IO1AV — I/O Chip Select 1 Address Valid

0 = I/O chip select 1 is active during E-clock valid time (E-clock high)

1 = I/O chip select 1 is active during address valid time

#### IO2AV — I/O Chip Select 2 Address Valid

0 = I/O chip select 1 is active during E-clock valid time (E-clock high)

1 = I/O chip select 1 is active during address valid time

#### GNPOL — General-Purpose Chip Select Polarity Select

0 = CSGEN is active low

1 = CSGEN is active high

#### GAVLD — General-Purpose Chip Select Address Valid Select

0 = CSGEN is valid during E-clock valid time (E-clock high)

1 = CSGEN is valid during address valid time

G1SZA–G1SZC — General-Purpose Chip Select Size Refer to **Table 4-11**.

| GSIZA | GSIZB | GSIZC | Size (Bytes)   |

|-------|-------|-------|----------------|

| 0     | 0     | 0     | 64 K           |

| 0     | 0     | 1     | 32 K           |

| 0     | 1     | 0     | 16 K           |

| 0     | 1     | 1     | 8 K            |

| 1     | 0     | 0     | 4 K            |

| 1     | 0     | 1     | 2 K            |

| 1     | 1     | 0     | 1 K            |

| 1     | 1     | 1     | 0 K (Disabled) |

#### Table 4-11 General-Purpose Chip Select Size Control

**OPERATING MODES AND ON-CHIP MEMORY**

MC68HC11F1 TECHNICAL DATA

#### Freescale Semiconductor, Inc.

The illegal opcode trap mechanism works for all unimplemented opcodes on all four opcode map pages. The address stacked as the return address for the illegal opcode interrupt is the address of the first byte of the illegal opcode. Otherwise, it would be almost impossible to determine whether the illegal opcode had been one or two bytes. The stacked return address can be used as a pointer to the illegal opcode so the illegal opcode service routine can evaluate the offending opcode.

#### 5.4.4 Software Interrupt

SWI is an instruction, and thus cannot be interrupted until complete. SWI is not inhibited by the global mask bits in the CCR. Because execution of SWI sets the I mask bit, once an SWI interrupt begins, other interrupts are inhibited until SWI is complete, or until user software clears the I bit in the CCR.

#### 5.4.5 Maskable Interrupts

The maskable interrupt structure of the MCU can be extended to include additional external interrupt sources through the IRQ pin. The default configuration of this pin is a low-level sensitive wired-OR network. When an event triggers an interrupt, a software accessible interrupt flag is set. When enabled, this flag causes a constant request for interrupt service. After the flag is cleared, the service request is released.

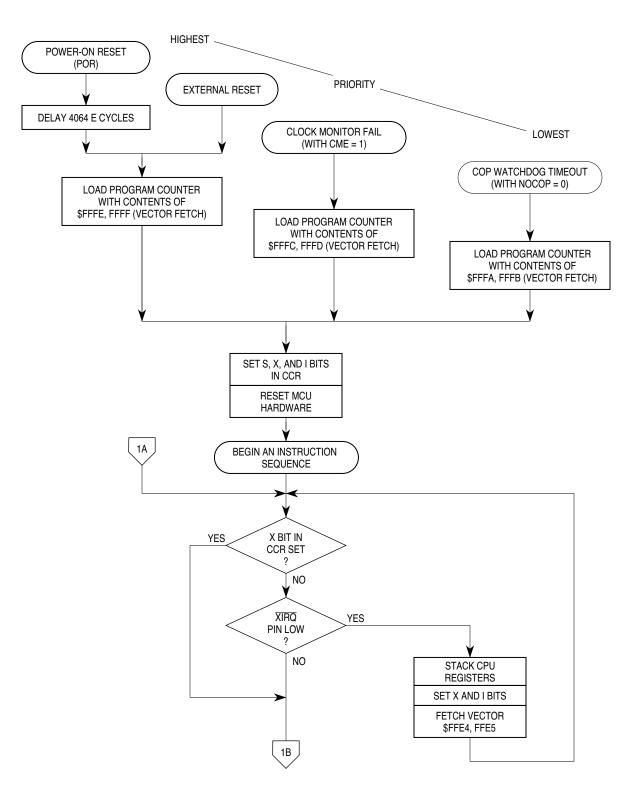

#### 5.4.6 Reset and Interrupt Processing

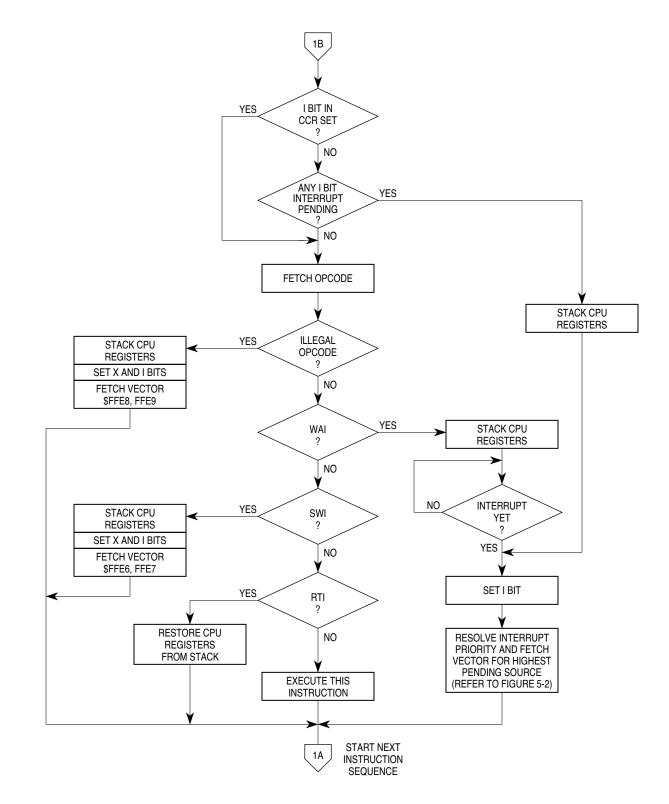

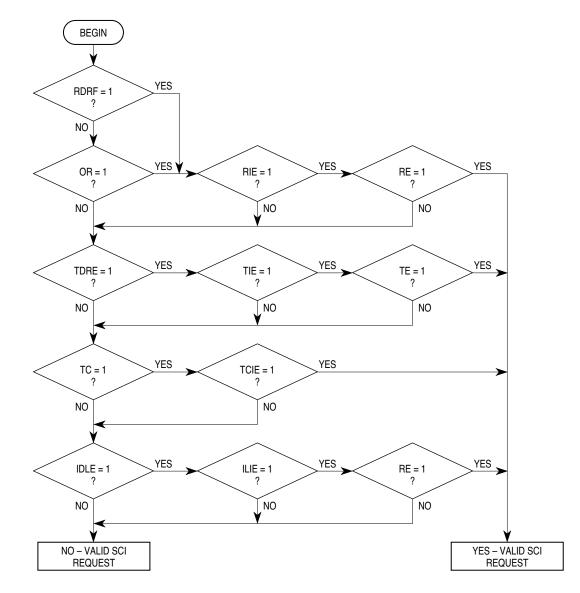

Figure 5-1 and Figure 5-3 illustrate the reset and interrupt process. Figure 5-1 illustrates how the CPU begins from a reset and how interrupt detection relates to normal opcode fetches. Figure 5-3 is an expansion of a block in Figure 5-1 and illustrates interrupt priorities. Figure 5-5 shows the resolution of interrupt sources within the SCI subsystem.

Figure 5-1 Processing Flow Out of Reset (1 of 2)

Go to: www.freescale.com

MC68HC11F1 TECHNICAL DATA

5-12

Figure 5-2 Processing Flow Out of Reset (2 of 2)

**RESETS AND INTERRUPTS**

Figure 5-5 Interrupt Source Resolution Within SCI

#### 5.5 Low Power Operation

Both STOP and WAIT suspend CPU operation until a reset or interrupt occurs. The WAIT condition suspends processing and reduces power consumption to an intermediate level. The STOP condition turns off all on-chip clocks and reduces power consumption to an absolute minimum while retaining the contents of all 1024 bytes of RAM.

**RESETS AND INTERRUPTS**

#### **Freescale Semiconductor, Inc.**

impedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port C can only be configured for wired-OR operation when the MCU is in single-chip or bootstrap modes.

| PORTC — Port C Data   \$10           |                                                  |       |       |       |       |       |       |       | \$1006 |

|--------------------------------------|--------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------|

|                                      | Bit 7                                            | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |        |

|                                      | PC7                                              | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |        |

| S. Chip or<br>Boot:                  | PC7                                              | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |        |

| RESET:                               | I                                                | I     | I     | Ι     | I     | I     | I     | I     |        |

| Expan. or<br>Test:                   | DATA7                                            | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |        |

| DDRC —                               | DDRC — Data Direction Register for Port C \$1007 |       |       |       |       |       |       |       |        |

|                                      | Bit 7                                            | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |        |

|                                      | DDC7                                             | DDC6  | DDC5  | DDC4  | DDC3  | DDC2  | DDC1  | DDC0  |        |

| RESET:                               | 0                                                | 0     | 0     | 0     | 0     | 0     | 0     | 0     |        |

| DDC[7:0] — Data Direction for Port C |                                                  |       |       |       |       |       |       |       |        |

0 = Input

1 = Output

#### 6.4 Port D

In all modes, port D bits [5:0] can be used either for general-purpose I/O, or with the SCI and SPI subsystems. During reset, port D pins are configured as high impedance inputs (DDRD bits cleared).

The DWOM control bit in the SPCR register disables port D's P-channel output drivers. Because the N-channel driver is not affected by DWOM, setting DWOM causes port D to become an open-drain-type output port suitable for wired-OR operation. In wired-OR mode, (PORTD bits are at logic level zero), pins are actively driven low by the Nchannel driver. When a port D bit is at logic level one, the associated pin is in a highimpedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port D can be configured for wired-OR operation in any operating mode.

| -                  |       |   |     |     |      |      |     |       |

|--------------------|-------|---|-----|-----|------|------|-----|-------|

|                    | Bit 7 | 6 | 5   | 4   | 3    | 2    | 1   | Bit 0 |

|                    | _     |   | PD5 | PD4 | PD3  | PD2  | PD1 | PD0   |

| RESET:             | 0     | 0 | I   |     | I    |      |     | I     |

| Alt. Pin<br>Func.: | _     | _ | SS  | SCK | MOSI | MISO | TxD | RxD   |

#### **PORTD** — Port D Data

\$1008

Semiconductor, Inc

0

eescal

#### Freescale Semiconductor, Inc.

R8 — Receive Data Bit 8

If M bit is set, R8 stores the ninth bit in the receive data character.

T8 — Transmit Data Bit 8

If M bit is set, T8 stores the ninth bit in the transmit data character.

- M Mode (Select Character Format)

- 0 = Start bit, 8 data bits, 1 stop bit

- 1 = Start bit, 9 data bits, 1 stop bit

- WAKE Wakeup by Address Mark/Idle

- 0 = Wakeup by IDLE line recognition

- 1 = Wakeup by address mark (most significant data bit set)

#### 7.6.3 Serial Communications Control Register 2

The SCCR2 register provides the control bits that enable or disable individual SCI functions.

#### SCCR2 — SCI Control Register 2

#### Bit 7 6 5 4 3 2 Bit 0 1 RE TIE TCIE RIE ILIE TE RWU SBK RESET: 0 0 0 0 0 0 0 0

#### TIE — Transmit Interrupt Enable

0 = TDRE interrupts disabled

1 = SCI interrupt requested when TDRE status flag is set

#### TCIE — Transmit Complete Interrupt Enable

- 0 = TC interrupts disabled

- 1 = SCI interrupt requested when TC status flag is set

- RIE Receiver Interrupt Enable

- 0 = RDRF and OR interrupts disabled

- 1 = SCI interrupt requested when RDRF flag or the OR status flag is set

#### ILIE — Idle-Line Interrupt Enable

- 0 = IDLE interrupts disabled

- 1 = SCI interrupt requested when IDLE status flag is set

#### TE — Transmitter Enable

When TE goes from zero to one, one unit of idle character time (logic one) is queued as a preamble.

- 0 = Transmitter disabled

- 1 = Transmitter enabled

- RE Receiver Enable

- 0 = Receiver disabled

- 1 = Receiver enabled

#### 8.3.1 Master In Slave Out

MISO is one of two unidirectional serial data signals. It is an input to a master device and an output from a slave device. The MISO line of a slave device is placed in the high-impedance state if the slave device is not selected.

#### 8.3.2 Master Out Slave In

The MOSI line is the second of the two unidirectional serial data signals. It is an output from a master device and an input to a slave device. The master device places data on the MOSI line a half-cycle before the clock edge that the slave device uses to latch the data.

#### 8.3.3 Serial Clock

SCK, an input to a slave device, is generated by the master device and synchronizes data movement in and out of the device through the MOSI and MISO lines. Master and slave devices are capable of exchanging a byte of information during a sequence of eight clock cycles.

There are four possible timing relationships that can be chosen by using control bits CPOL and CPHA in the serial peripheral control register (SPCR). Both master and slave devices must operate with the same timing. The SPI clock rate select bits, SPR[1:0], in the SPCR of the master device, select the clock rate. In a slave device, SPR[1:0] have no effect on the operation of the SPI.

#### 8.3.4 Slave Select

The slave select  $(\overline{SS})$  input of a slave device must be externally asserted before a master device can exchange data with the slave device.  $\overline{SS}$  must be low before data transactions and must stay low for the duration of the transaction.

The  $\overline{SS}$  line of the master must be held high. If it goes low, a mode fault error flag (MODF) is set in the serial peripheral status register (SPSR). To disable the mode fault circuit, write a one in bit 5 of the port D data direction register. This sets the  $\overline{SS}$  pin to act as a general-purpose output rather than the dedicated input to the slave select circuit, thus inhibiting the mode fault flag. The other three lines are dedicated to the SPI whenever the serial peripheral interface is on.

The state of the master and slave CPHA bits affects the operation of  $\overline{SS}$ . CPHA settings should be identical for master and slave. When CPHA = 0, the shift clock is the OR of  $\overline{SS}$  with SCK. In this clock phase mode,  $\overline{SS}$  must go high between successive characters in an SPI message. When CPHA = 1,  $\overline{SS}$  can be left low between successive SPI characters. In cases where there is only one SPI slave MCU, its  $\overline{SS}$  line can be tied to V<sub>ss</sub> as long as only CPHA = 1 clock mode is used.

#### 8.4 SPI System Errors

Two system errors can be detected by the SPI system. The first type of error arises in a multiple-master system when more than one SPI device simultaneously tries to be a master. This error is called a mode fault. The second type of error, write collision, indicates that an attempt was made to write data to the SPDR while a transfer was in progress.

SERIAL PERIPHERAL INTERFACE

MC68HC11F1 TECHNICAL DATA

For More Information On This Product, Go to: www.freescale.com

|                                | 4.0 MHz             | 8.0 MHz             | 12.0 MHz              | 16.0 MHz            | Other Rates                    |

|--------------------------------|---------------------|---------------------|-----------------------|---------------------|--------------------------------|

|                                | 1.0 MHz             | 2.0 MHz             | 3.0 MHz               | 4.0 MHz             | (E)                            |

| Control Bits                   | 1000 ns             | 500 ns              | 333 ns                | 250 ns              | (1/E)                          |

| PR1, PR0                       |                     | Mai                 | n Timer Count Ra      | ates                |                                |

| 0 0<br>1 count —<br>overflow — | 1.0 μs<br>65.536 ms | 500 ns<br>32.768 ms | 333 ns<br>21.845 ms   | 250 ns<br>16.384 ms | (1/E)<br>(2 <sup>16/</sup> E)  |

| 0 1<br>1 count —<br>overflow — | 4.0 μs<br>262.14 ms | 2.0 μs<br>131.07 ms | 1.333 μs<br>87.381 ms | 1.0 μs<br>65.536 ms | (4/E)<br>(2 <sup>18</sup> /E)  |

| 1 0<br>1 count —<br>overflow — | 8.0 μs<br>524.29 ms | 4.0 μs<br>262.14 ms | 2.667 μs<br>174.76 ms | 2.0 μs<br>131.07 ms | (8/E)<br>(2 <sup>19</sup> /E)  |

| 1 1<br>1 count —<br>overflow — | 16.0 μs<br>1.049 s  | 8.0 μs<br>524.29 ms | 5.333 μs<br>349.52 ms | 4.0 μs<br>262.14 ms | (16/E)<br>(2 <sup>20/</sup> E) |

#### Table 9-1 Timer Summary

#### 9.1 Timer Structure

**Figure 9-2** shows the capture/compare system block diagram. The port A pin control block includes logic for timer functions and for general-purpose I/O. For pins PA3, PA2, PA1, and PA0, this block contains both the edge-detection logic and the control logic that enables the selection of which edge triggers an input capture. The digital level on PA[3:0] can be read at any time (read PORTA register), even if the pin is being used for the input capture function. Pins PA[6:3] are used for either general-purpose I/O, or as output compare pins. When one of these pins is being used for an output compare function, it cannot be written directly as if it were a general-purpose output. Each of the output compare functions (OC[5:2]) is related to one of the port A output pins. Output compare one (OC1) has extra control logic, allowing it optional control of any combination of the PA[7:3] pins. The PA7 pin can be used as a general-purpose I/O pin, as an input to the pulse accumulator, or as an OC1 output pin.

| RTR[1:0] | E = 1 MHz | E = 2 MHz | E = 3 MHz | E = 4 MHz | E = X MHz            |

|----------|-----------|-----------|-----------|-----------|----------------------|

| 0 0      | 8.192 ms  | 4.096 ms  | 2.731 ms  | 2.048 ms  | (2 <sup>13</sup> /E) |

| 0 1      | 16.384 ms | 8.192 ms  | 5.461 ms  | 4.096 ms  | (2 <sup>14</sup> /E) |

| 10       | 32.768 ms | 16.384 ms | 10.923 ms | 8.192 ms  | (2 <sup>15</sup> /E) |

| 1 1      | 65.536 ms | 32.768 ms | 21.845 ms | 16.384 ms | (216/E)              |

Table 9-4 RTI Rate Selection

The clock source for the RTI function is a free-running clock that cannot be stopped or interrupted except by reset. This clock causes the time between successive RTI timeouts to be a constant that is independent of the software latencies associated with flag clearing and service. For this reason, an RTI period starts from the previous time-out, not from when RTIF is cleared.

Every time-out causes the RTIF bit in TFLG2 to be set, and if RTII is set, an interrupt request is generated. After reset, one entire RTI period elapses before the RTIF flag is set for the first time. Refer to the TMSK2, TFLG2, and PACTL registers.

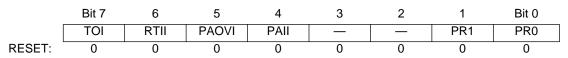

#### 9.4.1 Timer Interrupt Mask Register 2

This register contains the real-time interrupt enable bits.

**TMSK2** — Timer Interrupt Mask Register 2

\$1024

- TOI Timer Overflow Interrupt Enable

- 0 = TOF interrupts disabled

- 1 = Interrupt requested when TOF is set to one

- RTII Real-Time Interrupt Enable

- 0 = RTIF interrupts disabled

- 1 = Interrupt requested when RTIF set to one

- PAOVI Pulse Accumulator Overflow Interrupt Enable Refer to **9.6 Pulse Accumulator**.

- PAII Pulse Accumulator Input Edge Refer to **9.6 Pulse Accumulator**.

- PR[1:0] Timer Prescaler Select Refer to **Table 9-4**.

#### NOTE

Bits in TMSK2 correspond bit for bit with flag bits in TFLG2. Ones in TMSK2 enable the corresponding interrupt sources.

TIMING SYSTEM

### **APPENDIX A ELECTRICAL CHARACTERISTICS**

This appendix contains electrical parameters for the MC68HC11F1 microcontroller.

| Rating                                                                                                                           | Symbol           | Value                                                                                           | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------|------|

| Supply Voltage                                                                                                                   | V <sub>DD</sub>  | – 0.3 to + 7.0                                                                                  | V    |

| Input Voltage                                                                                                                    | V <sub>in</sub>  | - 0.3 to + 7.0                                                                                  | V    |

| Operating Temperature Range<br>MC68HC11F1<br>MC68HC11F1C<br>MC68HC11F1V<br>MC68HC11F1V                                           | T <sub>A</sub>   | T <sub>L</sub> to T <sub>H</sub><br>0 to + 70<br>- 40 to + 85<br>- 40 to + 105<br>- 40 to + 125 | °C   |

| Storage Temperature Range                                                                                                        | T <sub>stg</sub> | – 55 to + 150                                                                                   | °C   |

| Current Drain per Pin*<br>Excluding V <sub>DD</sub> , V <sub>SS</sub> , AV <sub>DD</sub> , V <sub>RH</sub> , and V <sub>RL</sub> | ۱ <sub>D</sub>   | 25                                                                                              | mA   |

#### Table A-1 Maximum Ratings

\*One pin at a time, observing maximum power dissipation limits.

Internal circuitry protects the inputs against damage caused by high static voltages or electric fields; however, normal precautions are necessary to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. Extended operation at the maximum ratings can adversely affect device reliability. Tying unused inputs to an appropriate logic voltage level (either GND or V<sub>DD</sub>) enhances reliability of operation.

Semiconductor, Inc.

Freescale

#### Freescale Semiconductor, Inc.

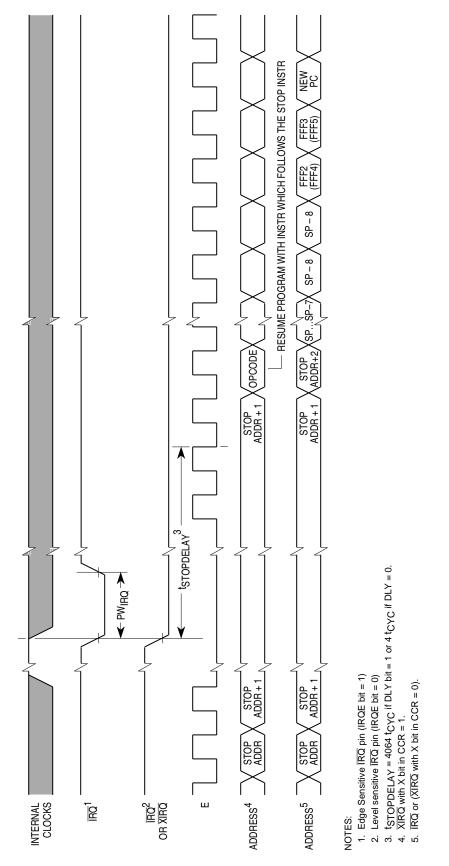

Figure A-4 STOP Recovery Timing Diagram

#### Table A-6 Analog-To-Digital Converter Characteristics

$V_{DD}$  = 5.0 Vdc ± 5%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , 750 kHz  $\leq$  E  $\leq$  3.0 MHz, unless otherwise noted

| Characteristic             | Parameter                                                                                                                                      | Min                  | Absolute   | 2.0 MHz                   | Unit                      |                           |                        |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|---------------------------|---------------------------|---------------------------|------------------------|

|                            |                                                                                                                                                |                      |            | Max                       | Max                       | Max                       |                        |

| Resolution                 | Number of Bits Resolved by A/D Converter                                                                                                       | —                    | 8          | —                         |                           | —                         | Bits                   |

| Non-Linearity              | Maximum Deviation from the Ideal A/D Transfer Characteristics                                                                                  | _                    | —          | ± 1                       | ± 1                       | ± 1                       | LSB                    |

| Zero Error                 | Difference Between the Output of an Ideal and an Actual for Zero Input Voltage                                                                 | —                    |            | ± 1                       | ± 1                       | ± 1                       | LSB                    |

| Full Scale Error           | Difference Between the Output of an Ideal and an Actual A/D for Full-Scale Input Voltage                                                       | _                    |            | ± 1                       | ± 1                       | ± 1                       | LSB                    |

| Total Unadjusted<br>Error  | Maximum Sum of Non-Linearity, Zero Error, and Full-Scale Error                                                                                 | —                    |            | ± 1/2                     | ± 1 1/2                   | ± 1 1/2                   | LSB                    |

| Quantization<br>Error      | Uncertainty Because of Converter Resolution                                                                                                    | —                    |            | ± 1/2                     | ± 1/2                     | ± 1/2                     | LSB                    |

| Absolute<br>Accuracy       | Difference Between the Actual Input Voltage and<br>the Full-Scale Weighted Equivalent of the Binary<br>Output Code, All Error Sources Included |                      | —          | ± 1                       | ± 2                       | ± 2                       | LSB                    |

| Conversion<br>Range        | Analog Input Voltage Range                                                                                                                     | V <sub>RL</sub>      |            | V <sub>RH</sub>           | V <sub>RH</sub>           | V <sub>RH</sub>           | V                      |

| V <sub>RH</sub>            | Maximum Analog Reference Voltage<br>(Note 2)                                                                                                   | V <sub>RL</sub>      |            | V <sub>DD</sub> + 0.1     | V <sub>DD</sub> +<br>0.1  | V <sub>DD</sub> +<br>0.1  | V                      |

| V <sub>RL</sub>            | Minimum Analog Reference Voltage<br>(Note 2)                                                                                                   | V <sub>SS</sub> –0.1 |            | V <sub>RH</sub>           | V <sub>RH</sub>           | V <sub>RH</sub>           | V                      |

| $\Delta V_R$               | Minimum Difference between V <sub>RH</sub> and V <sub>RL</sub><br>(Note 2)                                                                     | 3                    |            | —                         | _                         | _                         | V                      |

| Conversion<br>Time         | Total Time to Perform a Single<br>Analog-to-Digital Conversion:<br>E Clock<br>Internal RC Oscillator                                           |                      | 32<br>—    | <br>t <sub>cvc</sub> + 32 | <br>t <sub>cvc</sub> + 32 | <br>t <sub>cyc</sub> + 32 | t <sub>cyc</sub><br>μs |

| Monotonicity               | Conversion Result Never Decreases with an<br>Increase in Input Voltage and has no Missing<br>Codes                                             |                      | Guaranteed |                           |                           |                           |                        |

| Zero Input<br>Reading      | Conversion Result when V <sub>in</sub> = V <sub>RL</sub>                                                                                       | 00                   |            | —                         | _                         | _                         | Hex                    |

| Full Scale<br>Reading      | Conversion Result when V <sub>in</sub> = V <sub>RH</sub>                                                                                       | —                    |            | FF                        | FF                        | FF                        | Hex                    |

| Sample<br>Acquisition Time | Analog Input Acquisition Sampling Time:<br>E Clock<br>Internal RC Oscillator                                                                   | _                    | 12         | <u>_</u><br>12            |                           |                           | t <sub>cyc</sub><br>μs |

| Sample/Hold<br>Capacitance | Input Capacitance during Sample PE[7:0]                                                                                                        | —                    | 20 (Тур)   | -                         | —                         | —                         | pF                     |

| Input Leakage              | Input Leakage on A/D Pins PE[7:0]<br>V <sub>RL</sub> , V <sub>RH</sub>                                                                         | —                    |            | 400<br>1.0                | 400<br>1.0                | 400<br>1.0                | nA<br>μA               |

NOTES:

- 1. For  $f_{op} < 2$  MHz, source impedances should equal approximately 10 k $\Omega$ . For  $f_{op} \ge 2$  MHz, source impedances should equal approximately 5 k $\Omega$  10 k $\Omega$ . Source impedances greater than 10 k $\Omega$  affect accuracy adversely because of input leakage.

- 2. Performance verified down to 2.5 V  $\Delta V_R$ , but accuracy is tested and guaranteed at  $\Delta V_R$  = 5 V  $\pm$  10%

## Freescale Semiconductor, Inc.

#### **Table A-8 Serial Peripheral Interface Timing**

|     | $V_{DD}$ = 5.0 Vdc ± 5%, $V_{SS}$ = 0 Vdc, $T_A$ = $T_L$ to $T_H$                                                                                             |                                                |            |            |            |            |            |            |                        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------|------------|------------|------------|------------|------------|------------------------|

| Num | Characteristic                                                                                                                                                | Symbol                                         | 2.0 MHz    |            | 3.0 MHz    |            | 4.0 MHz    |            | Unit                   |

|     |                                                                                                                                                               |                                                | Min        | Max        | Min        | Max        | Min        | Max        |                        |

|     | Operating Frequency<br>Master<br>Slave                                                                                                                        | f <sub>op(m)</sub><br>f <sub>op(s)</sub>       | dc<br>dc   | 1.0<br>2.0 | dc<br>dc   | 1.5<br>3.0 | dc<br>dc   | 2.0<br>4.0 | MHz<br>MHz             |

| 1   | Cycle Time<br>Master<br>Slave                                                                                                                                 | t <sub>cyc(m)</sub><br>t <sub>cyc(s)</sub>     | 2.0<br>500 | _          | 2.0<br>333 | _          | 2.0<br>250 | _          | t <sub>cyc</sub><br>ns |

| 2   | Enable Lead Time<br>Master (Note 2)<br>Slave                                                                                                                  | t <sub>lead(m)</sub><br>t <sub>lead(s)</sub>   | <br>250    | _          | <br>240    | _          | <br>200    | _          | ns<br>ns               |

| 3   | Enable Lag Time<br>Master (Note 2)<br>Slave                                                                                                                   | t <sub>lag(m)</sub><br>t <sub>lag(s)</sub>     | <br>250    |            | <br>240    |            | <br>200    |            | ns<br>ns               |

| 4   | Clock (SCK) High Time<br>Master<br>Slave                                                                                                                      | t <sub>w(SCKH)m</sub><br>t <sub>w(SCKH)s</sub> | 340<br>190 | _          | 227<br>127 |            | 130<br>85  | _          | ns<br>ns               |

| 5   | Clock (SCK) Low Time<br>Master<br>Slave                                                                                                                       | t <sub>w(SCKL)m</sub><br>t <sub>w(SCKL)s</sub> | 340<br>190 | _          | 227<br>127 | _          | 130<br>85  | _          | ns<br>ns               |

| 6   | Data Setup Time (Inputs)<br>Master<br>Slave                                                                                                                   | t <sub>su(m)</sub><br>t <sub>su(s)</sub>       | 100<br>100 | =          | 100<br>100 | _          | 100<br>100 | _          | ns<br>ns               |

| 7   | Data Hold Time (Inputs)<br>Master<br>Slave                                                                                                                    | t <sub>h(m)</sub><br>t <sub>h(s)</sub>         | 100<br>100 | _          | 100<br>100 | _          | 100<br>100 | _          | ns<br>ns               |

| 8   | Access Time (Time to Data Active from<br>High-Impedance State)<br>Slave                                                                                       | t <sub>a</sub>                                 | 0          | 120        | 0          | 120        | 0          | 120        | ns                     |

| 9   | Disable Time (Hold Time to High-Impedance State)<br>Slave                                                                                                     | t <sub>dis</sub>                               |            | 240        | _          | 167        |            | 125        | ns                     |

| 10  | Data Valid (After Enable Edge) (Note 3)                                                                                                                       | t <sub>v(s)</sub>                              | —          | 240        | —          | 167        | —          | 125        | ns                     |

| 11  | Data Hold Time (Outputs) (After Enable Edge)                                                                                                                  | t <sub>ho</sub>                                | 0          | -          | 0          | —          | 0          | —          | ns                     |

| 12  | Rise Time (20% V <sub>DD</sub> to 70% V <sub>DD</sub> , C <sub>L</sub> = 200 pF)<br>SPI Outputs (SCK, MOSI, and MISO)<br>SPI Inputs (SCK, MOSI, MISO, and SS) | t <sub>rm</sub><br>t <sub>rs</sub>             |            | 100<br>2.0 |            | 100<br>2.0 |            | 100<br>2.0 | ns<br>µs               |

| 13  | Fall Time (70% V <sub>DD</sub> to 20% V <sub>DD</sub> , C <sub>L</sub> = 200 pF)<br>SPI Outputs (SCK, MOSI, and MISO)<br>SPI Inputs (SCK, MOSI, MISO, and SS) | t <sub>fm</sub><br>t <sub>fs</sub>             | _          | 100<br>2.0 | _          | 100<br>2.0 | _          | 100<br>2.0 | ns<br>μs               |

$V_{DD}$  = 5.0 Vdc ± 5%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$

NOTES:

1. All timing is shown with respect to 20%  $V_{\text{DD}}$  and 70%  $V_{\text{DD}},$  unless otherwise noted.

2. Signal production depends on software.

3. Assumes 200 pF load on all SPI pins.

**ELECTRICAL CHARACTERISTICS**

## **APPENDIX CDEVELOPMENT SUPPORT**

#### C.1 MC68HC11F1 Development Tools

The following table and text provide a reference to development tools for the MC68HC11F1 microcontrollers. For more complete information refer to the appropriate manual for each system.

#### Table C-1 MC68HC11F1 Development Tools

| Device     | Evaluation Systems | Modular Development Systems |

|------------|--------------------|-----------------------------|

| MC68HC11F1 | M68HC11F1EVS       | MMDS11*                     |

\* For MC68HC11F1 support, the MMDS11 must be used with an MC68HC11F1 emulator module.

#### C.2 MC68HC11EVS — Evaluation System

The EVS is an economical tool for designing, debugging, and evaluating target systems based on the MC68HC11F1 MCU. The two printed circuit boards that comprise the EVS are the MC68HC11F1EM emulator module (EM) and the M68HC11PFB platform board (PFB).

- Monitor/debugger firmware

- One-line assembler/disassembler

- Host computer download capability

- Dual memory maps:

- 64 Kbyte monitor map that includes 16 Kbytes of monitor EPROM

- MC68HC11F1 user map that includes 64 Kbytes of emulation RAM

- OTPROM, EPROM, and EEPROM MCU programmer

- MCU extension I/O port for single-chip, expanded, and special-test operation modes

- RS-232C terminal and host I/O ports

- Logic analyzer connector

#### C.3 M68MMDS11 — Modular Development System for M68HC11 Devices

The M68MMDS11 Freescale Modular Development System (MMDS11) is a tool for developing embedded systems based on M68HC11 MCUs. The MMDS11 is an emulator system that provides an on-screen bus state analyzer and real-time memory monitoring windows. An integrated design environment includes an editor, an assembler, the user interface, and source-level debug capability. These features significantly reduce the time necessary to develop and debug an embedded MCU system. The compact unit requires minimum space.

- Real-time, non-intrusive, in-circuit emulation

- Assembly-language source-level debugging