Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                   |

|----------------------------|------------------------------------------------------------|

| Core Processor             | HC11                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 5MHz                                                       |

| Connectivity               | SCI, SPI                                                   |

| Peripherals                | POR, WDT                                                   |

| Number of I/O              | 30                                                         |

| Program Memory Size        | -                                                          |

| Program Memory Type        | ROMIess                                                    |

| EEPROM Size                | 512 x 8                                                    |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.75V ~ 5.25V                                              |

| Data Converters            | A/D 8x8b                                                   |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 68-LCC (J-Lead)                                            |

| Supplier Device Package    | 68-PLCC (24.21x24.21)                                      |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchc11f1cfne5 |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Home Page: www.freescale.com email: support@freescale.com USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

# **SECTION 2 PIN DESCRIPTIONS**

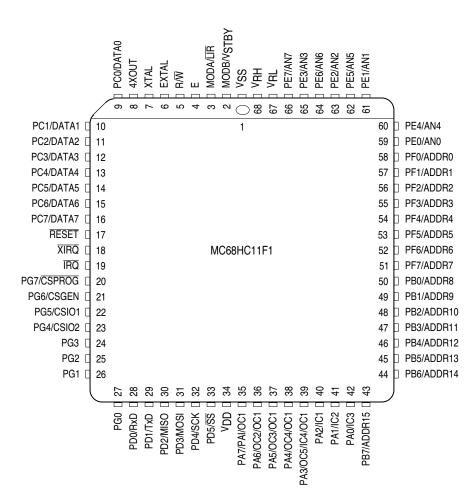

The MC68HC11F1 MCU is available in a 68-pin plastic leaded chip carrier (PLCC) and an 80-pin plastic quad flat pack (QFP). Most pins on this MCU serve two or more functions, as described in the following paragraphs. **Figure 2-1** shows the pin assignments for the PLCC. **Figure 2-2** shows the pin assignments for the QFP.

Figure 2-1 Pin Assignments for MC68HC11F1 68-Pin PLCC

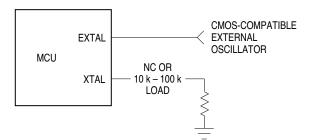

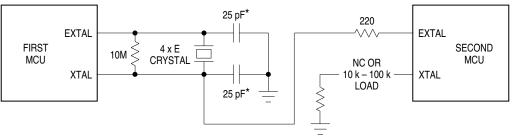

The XTAL pin is normally left unterminated when an external CMOS compatible clock is connected to the EXTAL pin. However, a 10 k $\Omega$  to 100 k $\Omega$  load resistor connected from the XTAL output to ground can be used to reduce RFI noise emission.

The XTAL output is normally used to drive a crystal. The XTAL output can be buffered with a high-impedance buffer, or it can be used to drive the EXTAL input of another M68HC11 device. Refer to **Figure 2-6**.

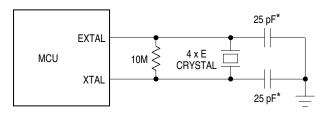

In all cases, use caution when designing circuitry associated with the oscillator pins. Load capacitances shown in the oscillator circuits include all stray layout capacitances. Refer to **Figure 2-4**, **Figure 2-5**, and **Figure 2-6**.

\* Values include all stray capacitances.

# Figure 2-4 Common Crystal Connections

\* Values include all stray capacitances.

# Figure 2-6 One Crystal Driving Two MCUs

MC68HC11F1 TECHNICAL DATA

# 2.11.2 Port B

Port B is an 8-bit output-only port. In single-chip modes, port B pins are general-purpose output pins (PB[7:0]). In expanded modes, port B pins act as the high-order address lines (ADDR[15:8]) of the address bus.

PORTB can be read at any time. Reads of PORTB return the pin driver input level. If PORTB is written, the data is stored in internal latches. It drives the pins only in singlechip or bootstrap mode. In expanded operating modes, port B pins are the high-order address outputs (ADDR[15:8]).

Refer to SECTION 6 PARALLEL INPUT/OUTPUT.

# 2.11.3 Port C

Port C is an 8-bit general-purpose I/O port with a data register (PORTC) and a data direction register (DDRC). In single-chip modes, port C pins are general-purpose I/O pins (PC[7:0]). In expanded modes, port C pins are configured as data bus pins (DA-TA[7:0]).

PORTC can be read at any time. Inputs return the pin level; outputs return the pin driver input level. If PORTC is written, the data is stored in internal latches. It drives the pins only if they are configured as outputs in single-chip or bootstrap mode. Port C pins are general-purpose inputs out of reset in single-chip and bootstrap modes. In expanded and test modes, these pins are data bus lines out of reset.

The CWOM control bit in the OPT2 register disables port C's P-channel output drivers. Because the N-channel driver is not affected by CWOM, setting CWOM causes port C to become an open-drain-type output port suitable for wired-OR operation. In wired-OR mode, (PORTC bits are at logic level zero), pins are actively driven low by the Nchannel driver. When a port C bit is at logic level one, the associated pin is in a highimpedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port C can only be configured for wired-OR operation when the MCU is in single-chip or bootstrap modes.

Refer to SECTION 6 PARALLEL INPUT/OUTPUT.

# 2.11.4 Port D

Port D, a 6-bit general-purpose I/O port, has a data register (PORTD) and a data direction register (DDRD). The six port D lines (D[5:0]) can be used for general-purpose I/O, for the serial communications interface (SCI) and serial peripheral interface (SPI) subsystems.

PORTD can be read at any time. Inputs return the pin level; outputs return the pin driver input level. If PORTD is written, the data is stored in internal latches and can be driven only if port D is configured for general-purpose output.

The DWOM control bit in the SPCR register disables port D's P-channel output drivers. Because the N-channel driver is not affected by DWOM, setting DWOM causes port D to become an open-drain-type output port suitable for wired-OR operation. In wired-

PIN DESCRIPTIONS

A normal mode is selected when MODB is logic one during reset. One of three reset vectors is fetched from address \$FFFA-\$FFFF, and program execution begins from the address indicated by this vector. If MODB is logic zero during reset, the special mode reset vector is fetched from addresses \$BFFA-\$BFFF and software has access to special test features. Refer to **SECTION 5 RESETS AND INTERRUPTS** for information regarding reset vectors.

## 4.3.1.1 HPRIO Register

Bits in the HPRIO register select the highest priority interrupt level, select whether bootstrap ROM is present, and control visibility of internal reads by the CPU. After reset, MDA and SMOD select the operating mode.

| HPRIO  | — Highe | st Priority | / I-Bit Inte | errupt an | d Miscell | aneous |       |       | \$103C       |

|--------|---------|-------------|--------------|-----------|-----------|--------|-------|-------|--------------|

|        | Bit 7   | 6           | 5            | 4         | 3         | 2      | 1     | Bit 0 |              |

|        | RBOOT*  | SMOD*       | MDA*         | IRV       | PSEL3     | PSEL2  | PSEL1 | PSEL0 | ]            |

| RESET: | 0       | 0           | 0            | 0         | 0         | 1      | 1     | 0     | Single Chip  |

|        | 0       | 0           | 1            | 0         | 0         | 1      | 1     | 0     | Expanded     |

|        | 1       | 1           | 0            | 1         | 0         | 1      | 1     | 0     | Bootstrap    |

|        | 0       | 1           | 1            | 1         | 0         | 1      | 1     | 0     | Special Test |

\*Reset states of RBOOT, SMOD, and MDA bits depend on hardware mode selection. Refer to Table 4-3.

#### RBOOT — Read Bootstrap ROM

Set to one out of reset in bootstrap mode. Valid while in special modes only. Can be read anytime. Can only be written in special modes.

- 0 = Bootloader ROM disabled and not in map

- 1 = Bootloader ROM enabled and in map at \$BF00-\$BFFF

#### SMOD and MDA — Special Mode Select and Mode Select A

The initial value of SMOD is the inverse of the logic level present on the MODB pin at the rising edge of reset. The initial value of MDA equals the logic level present on the MODA pin at the rising edge of reset. These two bits can be read at any time. They can be written at any time in special modes. Neither bit can be written is normal modes. SMOD cannot be set once it has been cleared. Refer to **Table 4-3**.

#### IRV — Internal Read Visibility

IRV can be written at any time in special modes (SMOD = 1). In normal modes (SMOD = 0) IRV can be written only once. In expanded and test modes, IRV determines whether internal read visibility is on or off. In single-chip and bootstrap modes, IRV has no meaning or effect.

0 = No internal read visibility on external bus

1 = Data from internal reads is driven out the external data bus.

PSEL[3:0] — Priority Select Bits [3:0]

Refer to 5.3.1 Highest Priority Interrupt and Miscellaneous Register.

#### 4.3.2 Initialization

Because bits in the following registers control the basic configuration of the MCU, an accidental change of their values could cause serious system problems. The protection mechanism, overridden in special operating modes, requires a write to the protected bits only within the first 64 bus cycles after any reset, or only once after each reset. **Table 4-2** summarizes the write access limited registers.

## 4.3.2.1 CONFIG Register

CONFIG controls the presence and position of the EEPROM in the memory map. CONFIG also enables the COP watchdog timer.

| CONFIG | <b>6</b> — Syst | em Confi | iguration | Register |   |       |   |       | \$103F       |

|--------|-----------------|----------|-----------|----------|---|-------|---|-------|--------------|

|        | Bit 7           | 6        | 5         | 4        | 3 | 2     | 1 | Bit 0 |              |

|        | EE3             | EE2      | EE1       | EE0      | — | NOCOP | _ | EEON  | ]            |

| RESET: | 1               | 1        | 1         | 1        | 1 | Р     | 1 | 1     | Single Chip  |

|        | 1               | 1        | 1         | 1        | 1 | P(L)  | 1 | 1     | Bootstrap    |

|        | Р               | Р        | Р         | Р        | 1 | Р     | 1 | Р     | Expanded     |

|        | Р               | Р        | Р         | Р        | 1 | P(L)  | 1 | 0     | Special Test |

P indicates a previously programmed bit. P(L) indicates that the bit resets to the logic level held in the latch prior to reset, but the function of COP is controlled by DISR bit in TEST1 register.

The CONFIG register consists of an EEPROM byte and static latches that control the start-up configuration of the MCU. The contents of the EEPROM byte are transferred into static working latches during reset sequences. The operation of the MCU is controlled directly by these latches and not by CONFIG itself. In normal modes, changes to CONFIG do not affect operation of the MCU until after the next reset sequence. When programming, the CONFIG register itself is accessed. When the CONFIG register is read, the static latches are accessed.

These bits can be read at any time. The value read is the one latched into the register from the EEPROM cells during the last reset sequence. A new value programmed into this register cannot be read until after a subsequent reset sequence. Unused bits always read as ones.

In special test mode, the static latches can be written directly at any time. In all modes, CONFIG bits can only be programmed using the EEPROM programming sequence, and are neither readable nor active until latched via the next reset. Refer to **4.4.3 CON-FIG Register Programming**.

EE[3:0] — EEPROM Mapping Control

EE[3:0] select the upper four bits of the EEPROM base address. In single-chip and bootstrap modes, EEPROM is forced to \$FE00-\$FFFF regardless of the value of EE[3:0].

**OPERATING MODES AND ON-CHIP MEMORY**

MC68HC11F1 TECHNICAL DATA

# 5.1.3 Computer Operating Properly (COP) Reset

The MCU includes a COP system to help protect against software failures. When the COP is enabled, the software is responsible for keeping a free-running watchdog timer from timing out. When the software is no longer being executed in the intended sequence, a system reset is initiated.

The state of the NOCOP bit in the CONFIG register determines whether the COP system is enabled or disabled. To change the enable status of the COP system, change the contents of the CONFIG register and then perform a system reset. In the special test and bootstrap operating modes, the COP system is initially inhibited by the disable resets (DISR) control bit in the TEST1 register. The DISR bit can subsequently be written to zero to enable COP resets.

The COP timer rate control bits CR[1:0] in the OPTION register determine the COP time-out period. The system E clock is divided by the values shown in **Table 5-1**. After reset, these bits are zero, which selects the fastest time-out period. In normal operating modes, these bits can only be written once within 64 bus cycles after reset.

| CR[1:0] | Divide<br>E By | XTAL = 8.0 MHz Time-<br>out<br>-0 ms, +16.4 ms | XTAL = 12.0 MHz<br>Time-out<br>–0 ms, +10.9 ms | XTAL = 16.0 MHz<br>Time-out<br>–0 ms, +8.2 ms |

|---------|----------------|------------------------------------------------|------------------------------------------------|-----------------------------------------------|

| 0 0     | 215            | 16.384 ms                                      | 10.923 ms                                      | 8.192 ms                                      |

| 0 1     | 217            | 65.536 ms                                      | 43.691 ms                                      | 32.768 ms                                     |

| 1 0     | 219            | 262.14 ms                                      | 174.76 ms                                      | 131.07 ms                                     |

| 11      | 221            | 1.049 s                                        | 699.05 ms                                      | 524.29 ms                                     |

|         | E =            | 2.0 MHz                                        | 3.0 MHz                                        | 4.0 MHz                                       |

# Table 5-1 COP Timer Rate Selection

#### **COPRST** — Arm/Reset COP Timer Circuitry

#### Bit 7 6 5 4 2 Bit 0 3 1 3 2 6 5 4 1 0 7 0 RESET: 0 0 0 0 0 0 0

Complete the following reset sequence to service the COP timer. Write \$55 to CO-PRST to arm the COP timer clearing mechanism. Then write \$AA to COPRST to clear the COP timer. Performing instructions between these two steps is possible as long as both steps are completed in the correct sequence before the timer times out.

# 5.1.4 Clock Monitor Reset

The clock monitor circuit is based on an internal RC time delay. If no MCU clock edges are detected within this RC time delay, the clock monitor can optionally generate a system reset. The clock monitor function is enabled or disabled by the CME and FCME control bits in the OPTION register. The presence of a time-out is determined by the RC delay, which allows the clock monitor to operate without any MCU clocks.

Clock monitor is used as a backup for the COP system. Because the COP needs a clock to function, it is disabled when the clocks stop. Therefore, the clock monitor system can detect clock failures not detected by the COP system.

**RESETS AND INTERRUPTS**

MC68HC11F1 TECHNICAL DATA

\$103A

## 5.2.6 Pulse Accumulator

The pulse accumulator system is disabled at reset so that the pulse accumulator input (PAI) pin defaults to being a general-purpose input pin.

# 5.2.7 Computer Operating Properly (COP)

The COP watchdog system is enabled if the NOCOP control bit in the CONFIG register is cleared, and disabled if NOCOP is set. The COP rate is set for the shortest duration time-out.

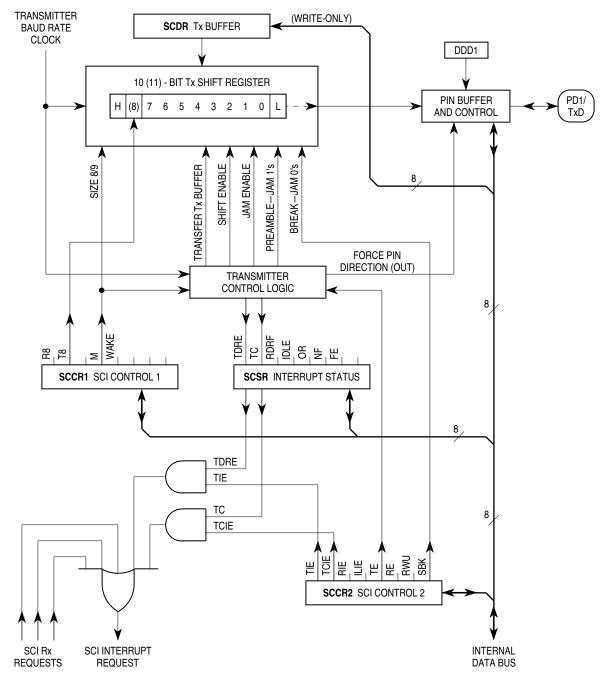

# 5.2.8 Serial Communications Interface (SCI)

The reset condition of the SCI system is independent of the operating mode. All transmit and receive interrupts are masked and both the transmitter and receiver are disabled so the port pins default to being general-purpose I/O lines. The SCI frame format is initialized to an 8-bit character size. The send break and receiver wakeup functions are disabled. The TDRE and TC status bits in the SCI status register are both set, indicating that there is no transmit data in either the transmit data register or the transmit serial shift register. The RDRF, IDLE, OR, NF, FE, PF, and RAF receive-related status bits are cleared.

# 5.2.9 Serial Peripheral Interface (SPI)

The SPI system is disabled by reset. The port pins associated with this function default to being general-purpose I/O lines.

# 5.2.10 Analog-to-Digital Converter

The A/D converter configuration is indeterminate after reset. The ADPU bit is cleared by reset, which disables the A/D system. The conversion complete flag is cleared by reset.

# 5.2.11 System

The EEPROM programming controls are disabled, so the memory system is configured for normal read operation. PSEL[3:0] are initialized with the binary value %0101, causing the external IRQ pin to have the highest I-bit interrupt priority. The IRQ pin is configured for level-sensitive operation (for wired-OR systems). The RBOOT, SMOD, and MDA bits in the HPRIO register reflect the status of the MODB and MODA inputs at the rising edge of reset. The DLY control bit is set to specify that an oscillator startup delay is imposed upon recovery from STOP mode. The clock monitor system is disabled because CME and FCME are cleared.

# 5.3 Reset and Interrupt Priority

Resets and interrupts have a hardware priority that determines which reset or interrupt is serviced first when simultaneous requests occur. Any maskable interrupt can be given priority over other maskable interrupts.

The first six interrupt sources are not maskable. The priority arrangement for these sources is as follows:

**RESETS AND INTERRUPTS**

MC68HC11F1 TECHNICAL DATA

| Vector Address      | Interrupt Source                       | CCR<br>Mask Bit | Local Mask |

|---------------------|----------------------------------------|-----------------|------------|

| FFC0, C1 – FFD4, D5 | Reserved                               | _               | _          |

| FFD6, D7            | SCI Serial System                      | I               |            |

|                     | SCI Receive Data Register Full         | _               | RIE        |

|                     | SCI Receiver Overrun                   | -               | RIE        |

|                     | SCI Transmit Data Register Empty       |                 | TIE        |

|                     | SCI Transmit Complete                  |                 | TCIE       |

|                     | SCI Idle Line Detect                   | -               | ILIE       |

| FFD8, D9            | SPI Serial Transfer Complete           | I               | SPIE       |

| FFDA, DB            | Pulse Accumulator Input Edge           | I               | PAII       |

| FFDC, DD            | Pulse Accumulator Overflow             | I               | PAOVI      |

| FFDE, DF            | Timer Overflow                         | I               | TOI        |

| FFE0, E1            | Timer Input Capture 4/Output Compare 5 | I               | I4/05I     |

| FFE2, E3            | Timer Output Compare 4                 | I               | OC4I       |

| FFE4, E5            | Timer Output Compare 3                 | I               | OC3I       |

| FFE6, E7            | Timer Output Compare 2                 | I               | OC2I       |

| FFE8, E9            | Timer Output Compare 1                 | I               | OC1I       |

| FFEA, EB            | Timer Input Capture 3                  | I               | IC3I       |

| FFEC, ED            | Timer Input Capture 2                  | I               | IC2I       |

| FFEE, EF            | Timer Input Capture 1                  | I               | IC1I       |

| FFF0, F1            | Real-Time Interrupt                    | I               | RTII       |

| FFF2, F3            | IRQ                                    | I               | None       |

| FFF4, F5            | XIRQ Pin                               | X               | None       |

| FFF6, F7            | Software Interrupt                     | None            | None       |

| FFF8, F9            | Illegal Opcode Trap                    | None            | None       |

| FFFA, FB            | COP Failure                            | None            | NOCOP      |

| FFFC, FD            | Clock Monitor Fail                     | None            | CME        |

| FFFE, FF            | RESET                                  | None            | None       |

#### Table 5-4 Interrupt and Reset Vector Assignments

For some interrupt sources, such as the SCI interrupts, the flags are automatically cleared during the normal course of responding to the interrupt requests. For example, the RDRF flag in the SCI system is cleared by the automatic clearing mechanism consisting of a read of the SCI status register while RDRF is set, followed by a read of the SCI data register. The normal response to an RDRF interrupt request would be to read the SCI status register to check for receive errors, then to read the received data from the SCI data register. These two steps satisfy the automatic clearing mechanism without requiring any special instructions.

# 5.4.1 Interrupt Recognition and Register Stacking

An interrupt can be recognized at any time after it is enabled by its local mask, if any, and by the global mask bit in the CCR. Once an interrupt source is recognized, the CPU responds at the completion of the instruction being executed. Interrupt latency varies according to the number of cycles required to complete the current instruction. When the CPU begins to service an interrupt, the contents of the CPU registers are pushed onto the stack in the order shown in **Table 5-5**. After the CCR value is stacked, the I bit and the X bit (if XIRQ is pending) are set to inhibit further interrupts. The interrupt vector for the highest priority pending source is fetched, and execution continues

#### **RESETS AND INTERRUPTS**

impedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port C can only be configured for wired-OR operation when the MCU is in single-chip or bootstrap modes.

| PORTC -             | – Port C | Data      |            |           |       |       |       |       | \$1006 |

|---------------------|----------|-----------|------------|-----------|-------|-------|-------|-------|--------|

|                     | Bit 7    | 6         | 5          | 4         | 3     | 2     | 1     | Bit 0 |        |

|                     | PC7      | PC6       | PC5        | PC4       | PC3   | PC2   | PC1   | PC0   |        |

| S. Chip or<br>Boot: | PC7      | PC6       | PC5        | PC4       | PC3   | PC2   | PC1   | PC0   |        |

| RESET:              | I        | I         | I          | I         | I     | I     | I     | I     |        |

| Expan. or<br>Test:  | DATA7    | DATA6     | DATA5      | DATA4     | DATA3 | DATA2 | DATA1 | DATA0 |        |

| DDRC —              | Data Di  | ection R  | egister fo | or Port C |       |       |       |       | \$1007 |

|                     | Bit 7    | 6         | 5          | 4         | 3     | 2     | 1     | Bit 0 |        |

|                     | DDC7     | DDC6      | DDC5       | DDC4      | DDC3  | DDC2  | DDC1  | DDC0  |        |

| RESET:              | 0        | 0         | 0          | 0         | 0     | 0     | 0     | 0     |        |

| DDC[7:0]            | — Data   | Directior | for Port   | С         |       |       |       |       |        |

0 = Input

1 = Output

## 6.4 Port D

In all modes, port D bits [5:0] can be used either for general-purpose I/O, or with the SCI and SPI subsystems. During reset, port D pins are configured as high impedance inputs (DDRD bits cleared).

The DWOM control bit in the SPCR register disables port D's P-channel output drivers. Because the N-channel driver is not affected by DWOM, setting DWOM causes port D to become an open-drain-type output port suitable for wired-OR operation. In wired-OR mode, (PORTD bits are at logic level zero), pins are actively driven low by the Nchannel driver. When a port D bit is at logic level one, the associated pin is in a highimpedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port D can be configured for wired-OR operation in any operating mode.

| -                  |       |   |     |     |      |      |     |       |

|--------------------|-------|---|-----|-----|------|------|-----|-------|

|                    | Bit 7 | 6 | 5   | 4   | 3    | 2    | 1   | Bit 0 |

|                    | _     |   | PD5 | PD4 | PD3  | PD2  | PD1 | PD0   |

| RESET:             | 0     | 0 | I   |     | I    |      |     | I     |

| Alt. Pin<br>Func.: | _     | _ | SS  | SCK | MOSI | MISO | TxD | RxD   |

#### **PORTD** — Port D Data

\$1008

| PORTF -             | – Port F | Data  |       |       |       |       |       |       |  |

|---------------------|----------|-------|-------|-------|-------|-------|-------|-------|--|

|                     | Bit 7    | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |

|                     | PF7      | PF6   | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |  |

| S. Chip<br>or Boot: | PF7      | PF6   | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |  |

| RESET:              | 0        | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| Expan.<br>or Test:  | ADDR7    | ADDR6 | ADDR5 | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |  |

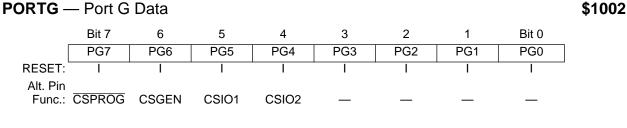

# 6.7 Port G

Port G pins reset to high-impedance inputs except in expanded modes where reset causes PG7 to become the CSPROG output. Alternate functions for port G bits [7:4] are chip select outputs. All port G bits are bidirectional and have corresponding data direction bits.

The GWOM control bit in the OPT2 register disables port G's P-channel output drivers. Because the N-channel driver is not affected by GWOM, setting GWOM causes port G to become an open-drain-type output port suitable for wired-OR operation. In wired-OR mode, (PORTG bits are at logic level zero), pins are actively driven low by the Nchannel driver. When a port G bit is at logic level one, the associated pin is in a highimpedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port G can be configured for wired-OR operation in any operating mode.

# DDRG — Data Direction Register for Port G

|        | Bit 7 | 6    | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|--------|-------|------|------|------|------|------|------|-------|

|        | DDG7  | DDG6 | DDG5 | DDG4 | DDG3 | DDG2 | DDG1 | DDG0  |

| RESET: | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0     |

DDG[7:0] - Data Direction for Port G

0 = Input

1 = Output

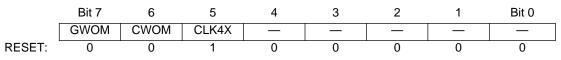

# 6.8 System Configuration Options 2

The system configuration options 2 register controls several configuration parameters. Bit 6, CWOM, is the only bit in this register that directly affects parallel I/O.

\$1003

\$1005

**OPT2** — System Configuration Options 2

\$1038

- GWOM Port G Wired-OR Mode

- 0 = Port G operates normally

- 1 = Port G outputs are open drain

- CWOM Port C Wired-OR Mode

- 0 = Port C operates normally

- 1 = Port C outputs are open drain

- CLK4X 4XOUT Clock Enable Refer to **SECTION 2 PIN DESCRIPTIONS**.

- Bits [4:0] Not implemented Always read zero

Figure 7-1 SCI Transmitter Block Diagram

# 7.3 Receive Operation

During receive operations, the transmit sequence is reversed. The serial shift register receives data and transfers it to a parallel receive data register (SCDR) as a complete word. This double buffered operation allows a character to be shifted in serially while another character is already in the SCDR. An advanced data recovery scheme distinguishes valid data from noise in the serial data stream. The data input is selectively sampled to detect receive data, and a majority voting circuit determines the value and integrity of each bit.

SERIAL COMMUNICATIONS INTERFACE

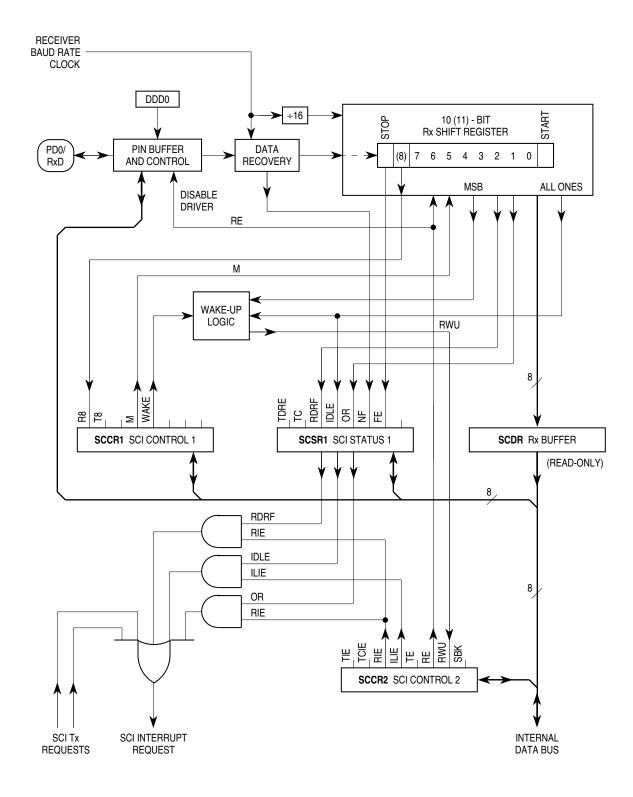

Figure 7-2 SCI Receiver Block Diagram

SERIAL COMMUNICATIONS INTERFACE

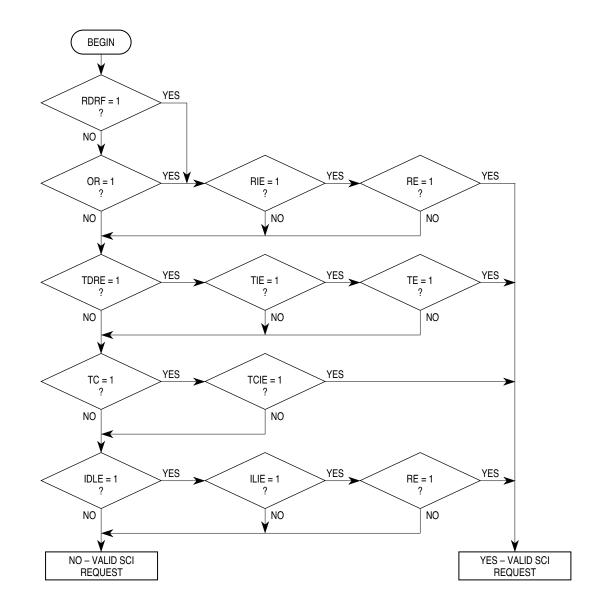

Figure 7-4 Interrupt Source Resolution Within SCI

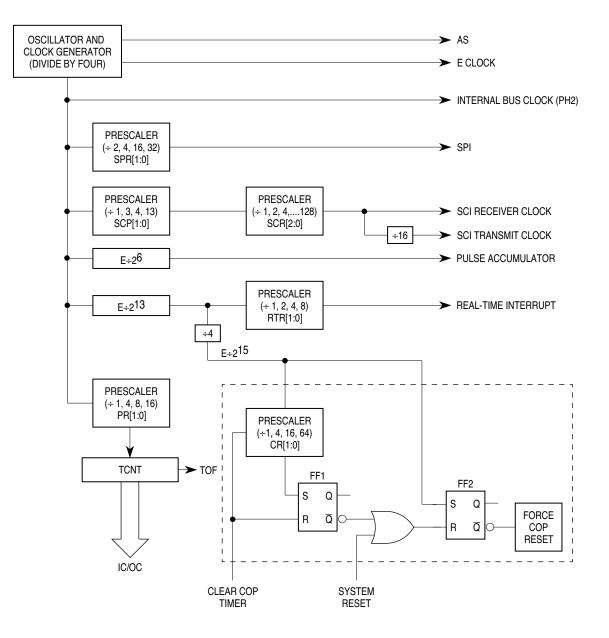

Figure 9-1 Timer Clock Divider Chains

indicates when valid data is present in the result registers. The result registers are written during a portion of the system clock cycle when reads do not occur, so there is no conflict.

# 10.1.5 A/D Converter Clocks

The CSEL bit in the OPTION register selects whether the A/D converter uses the system E clock or an internal RC oscillator for synchronization. When the A/D system is operating with the MCU E clock, all switching and comparator functions are synchronized to the MCU clocks. This allows the comparator results to be sampled at relatively quiet clock times to minimize noise errors.

When E-clock frequency is below 750 kHz, charge leakage in the capacitor array can cause errors, and the internal oscillator should be used. The RC clock is asynchronous to the MCU internal E clock. Therefore, when the RC clock is used, additional errors can occur because the comparator is sensitive to the additional system clock noise.

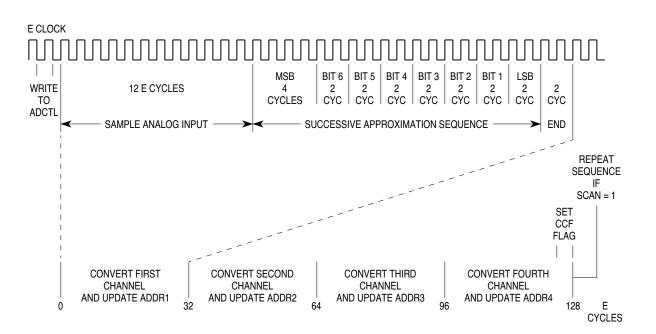

## **10.1.6 Conversion Sequence**

A/D converter operations are performed in sequences of four conversions each. A conversion sequence can repeat continuously or stop after one iteration. The conversion complete flag (CCF) is set after the fourth conversion in a sequence to show the availability of data in the result registers. **Figure 10-3** shows the timing of a typical sequence. Synchronization is referenced to the system E clock.

Figure 10-3 A/D Conversion Sequence

ANALOG-TO-DIGITAL CONVERTER

For More Information On This Product, Go to: www.freescale.com

# **APPENDIX A ELECTRICAL CHARACTERISTICS**

This appendix contains electrical parameters for the MC68HC11F1 microcontroller.

| Rating                                                                                                                           | Symbol           | Value                                                                                           | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------|------|

| Supply Voltage                                                                                                                   | V <sub>DD</sub>  | – 0.3 to + 7.0                                                                                  | V    |

| Input Voltage                                                                                                                    | V <sub>in</sub>  | - 0.3 to + 7.0                                                                                  | V    |

| Operating Temperature Range<br>MC68HC11F1<br>MC68HC11F1C<br>MC68HC11F1V<br>MC68HC11F1V<br>MC68HC11F1M                            | T <sub>A</sub>   | T <sub>L</sub> to T <sub>H</sub><br>0 to + 70<br>- 40 to + 85<br>- 40 to + 105<br>- 40 to + 125 | °C   |

| Storage Temperature Range                                                                                                        | T <sub>stg</sub> | – 55 to + 150                                                                                   | °C   |

| Current Drain per Pin*<br>Excluding V <sub>DD</sub> , V <sub>SS</sub> , AV <sub>DD</sub> , V <sub>RH</sub> , and V <sub>RL</sub> | ۱ <sub>D</sub>   | 25                                                                                              | mA   |

# Table A-1 Maximum Ratings

\*One pin at a time, observing maximum power dissipation limits.

Internal circuitry protects the inputs against damage caused by high static voltages or electric fields; however, normal precautions are necessary to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. Extended operation at the maximum ratings can adversely affect device reliability. Tying unused inputs to an appropriate logic voltage level (either GND or V<sub>DD</sub>) enhances reliability of operation.